TIDUF71A March 2024 – November 2024

- 1

- Description

- Resources

- Features

- Applications

- 6

- 1System Description

- 2System Overview

- 3Hardware, Software, Testing Requirements, and Test Results

- 4Design and Documentation Support

- 5About the Author

- 6Revision History

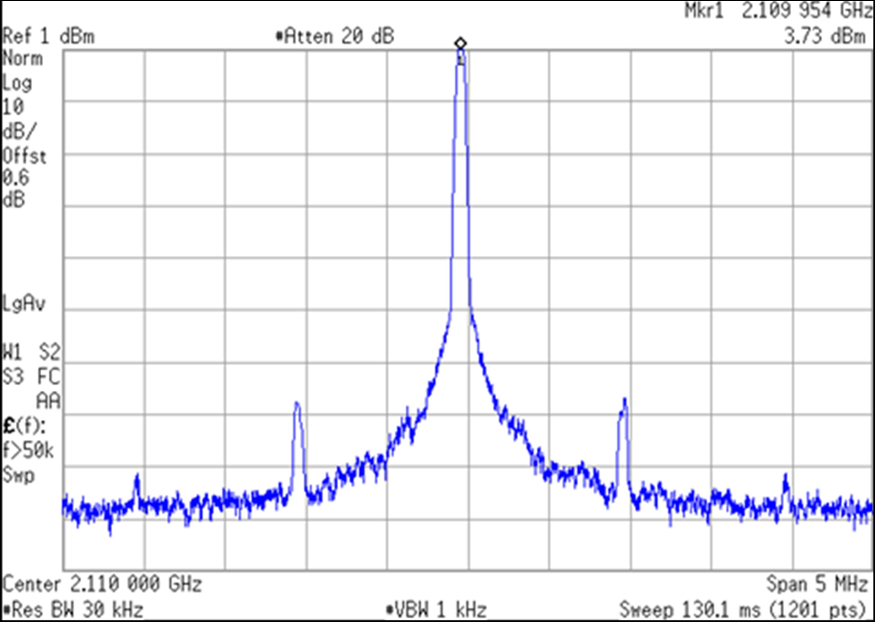

3.7.2 Internal TCXO Operation

The default test procedure outlines uses an external high-quality reference oscillator at 491.52MHz which is buffered or divided by the LMK04832-SEP in bypass mode. Alternatively, the reference design has an on-board 30.72MHz TCXO. This TCXO can serve as the reference for the LMK internal PLL/VCO. With this approach, the internal PLL/VCO is locked to 2949.12MHz. That output signal is divided down to supply the necessary clocks to the AFE, LMX, and FPGA.

Implement this approach by executing the following config file during the bring-up of the LMK04832:

- LMK04832-SEP: LMK04832-SEP_TICsPro_2949p12M_VCO_30p72_TCXO.tcs

The disadvantage of this approach is the degraded phase noise performance of the AFE reference signal that is derived from the LMK VCO compared to a high quality TCXO like a Wenzel Oscillator. Figure 3-9 shows performance of the AFE7950-SP with internal PLL/VCO clock where the reference is derived from the LMK VCO.

Figure 3-9 TXA Output With LMX Reference

Derived From TCXO

Figure 3-9 TXA Output With LMX Reference

Derived From TCXO