TIDUF73 September 2024

3.3 Test Results

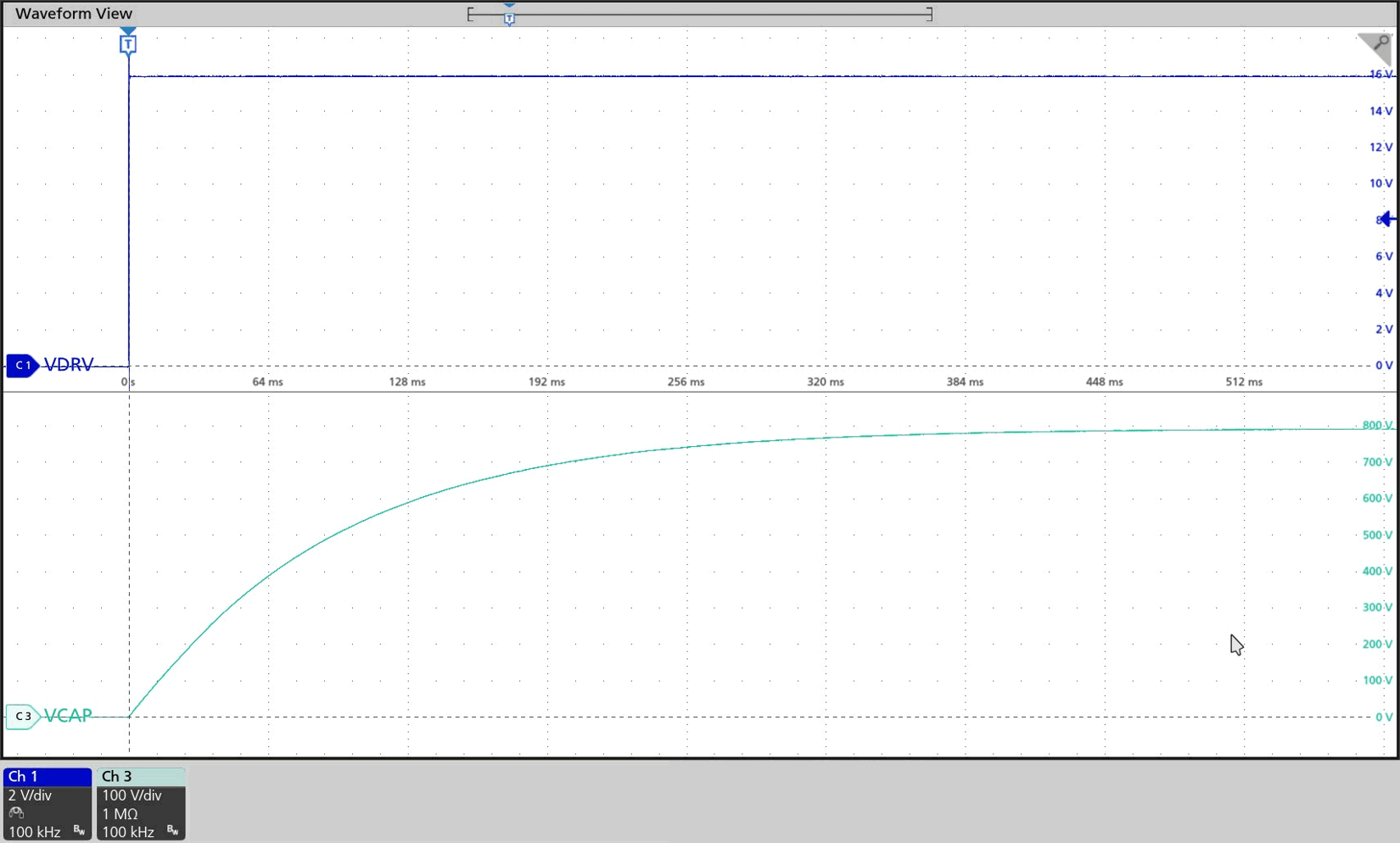

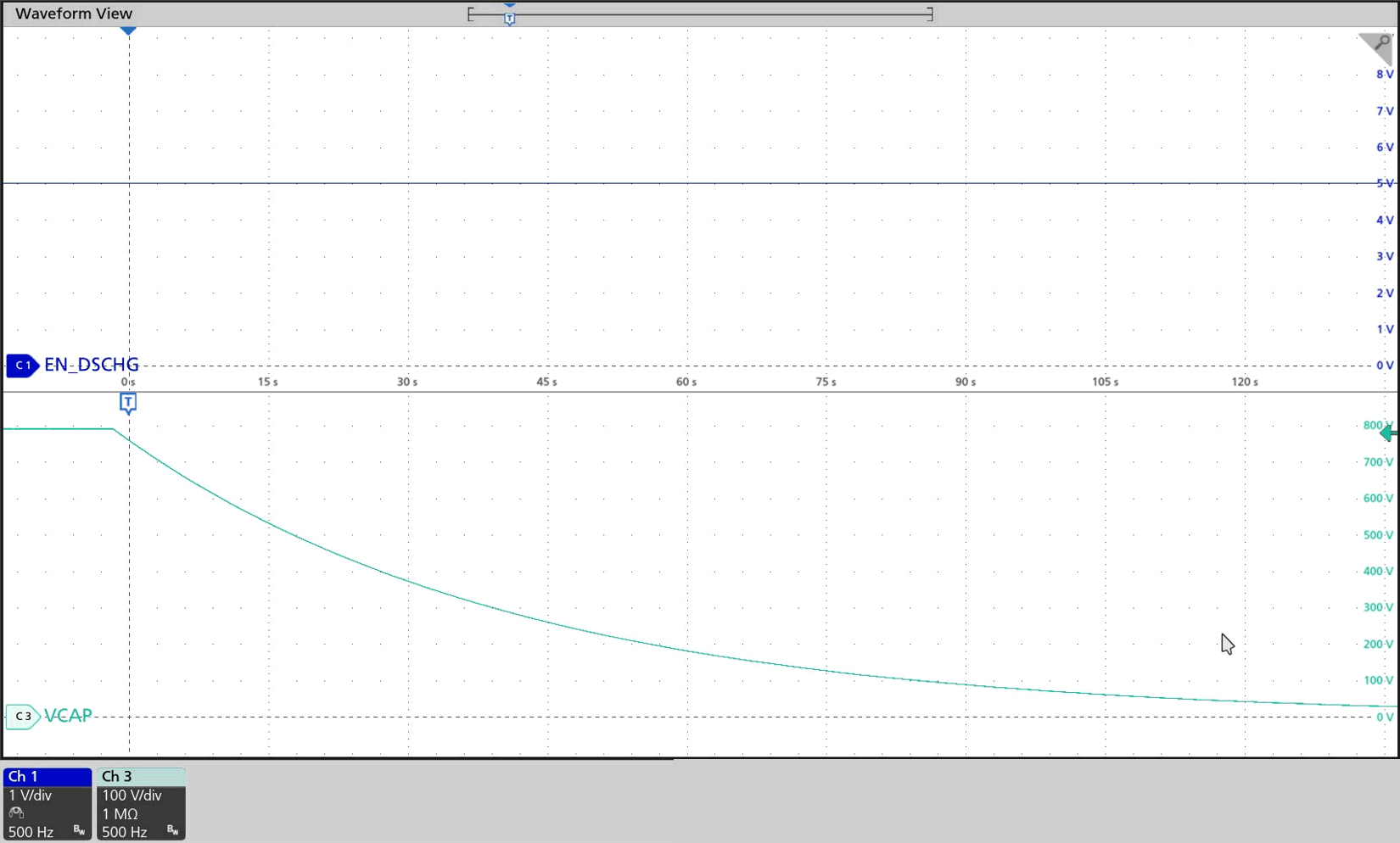

Figure 3-3 shows a typical precharge cycle and Figure 3-4 a discharge cycle.

- VDRV is the drive pin on the secondary side of TPSI3100-Q1

- VCAP is the voltage across the capacitor bank

- EN_DSHCG is the enable signal for the TPSI2140-Q1

Figure 3-3 Precharge Cycle

Figure 3-3 Precharge Cycle Figure 3-4 Discharge Cycle

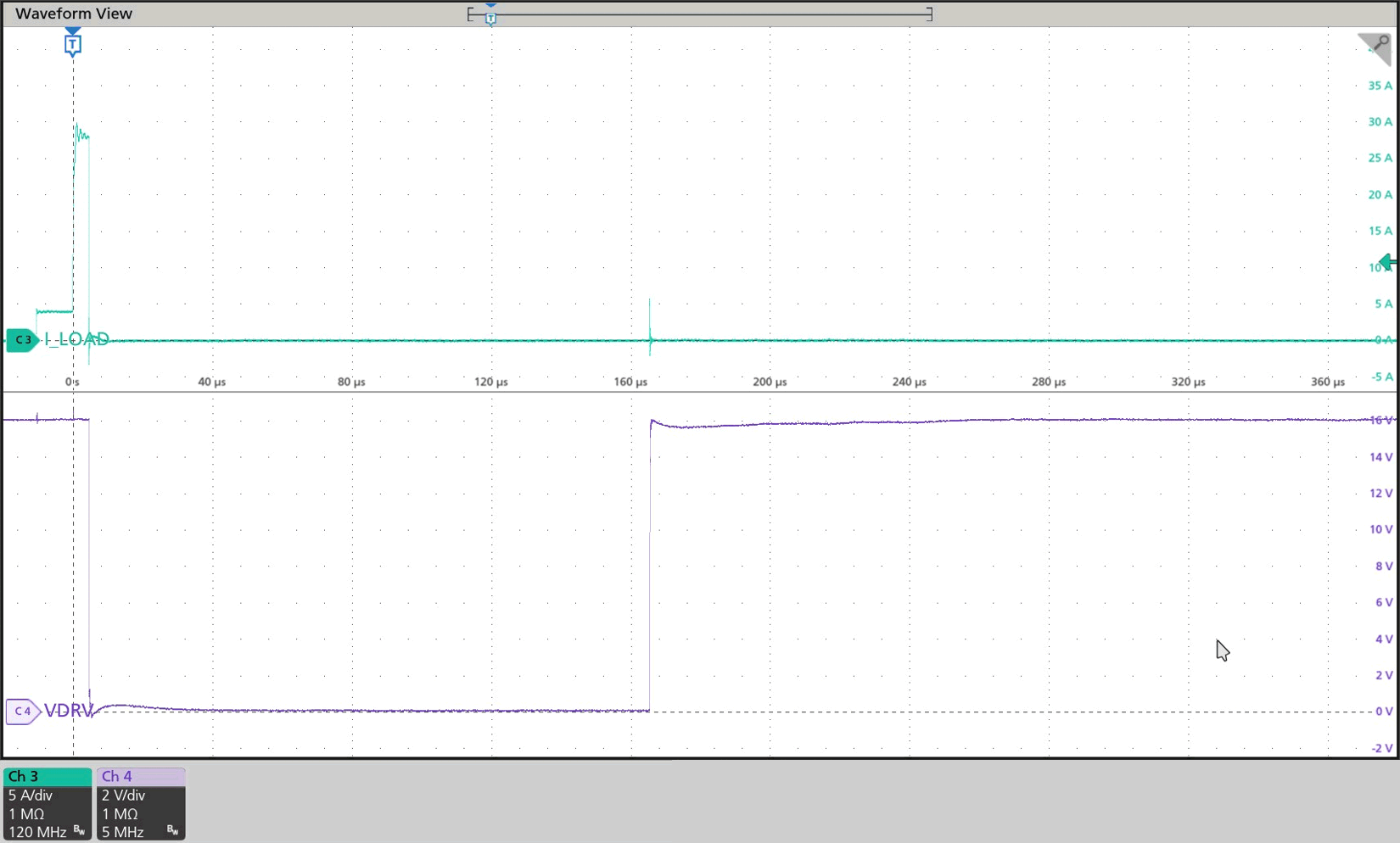

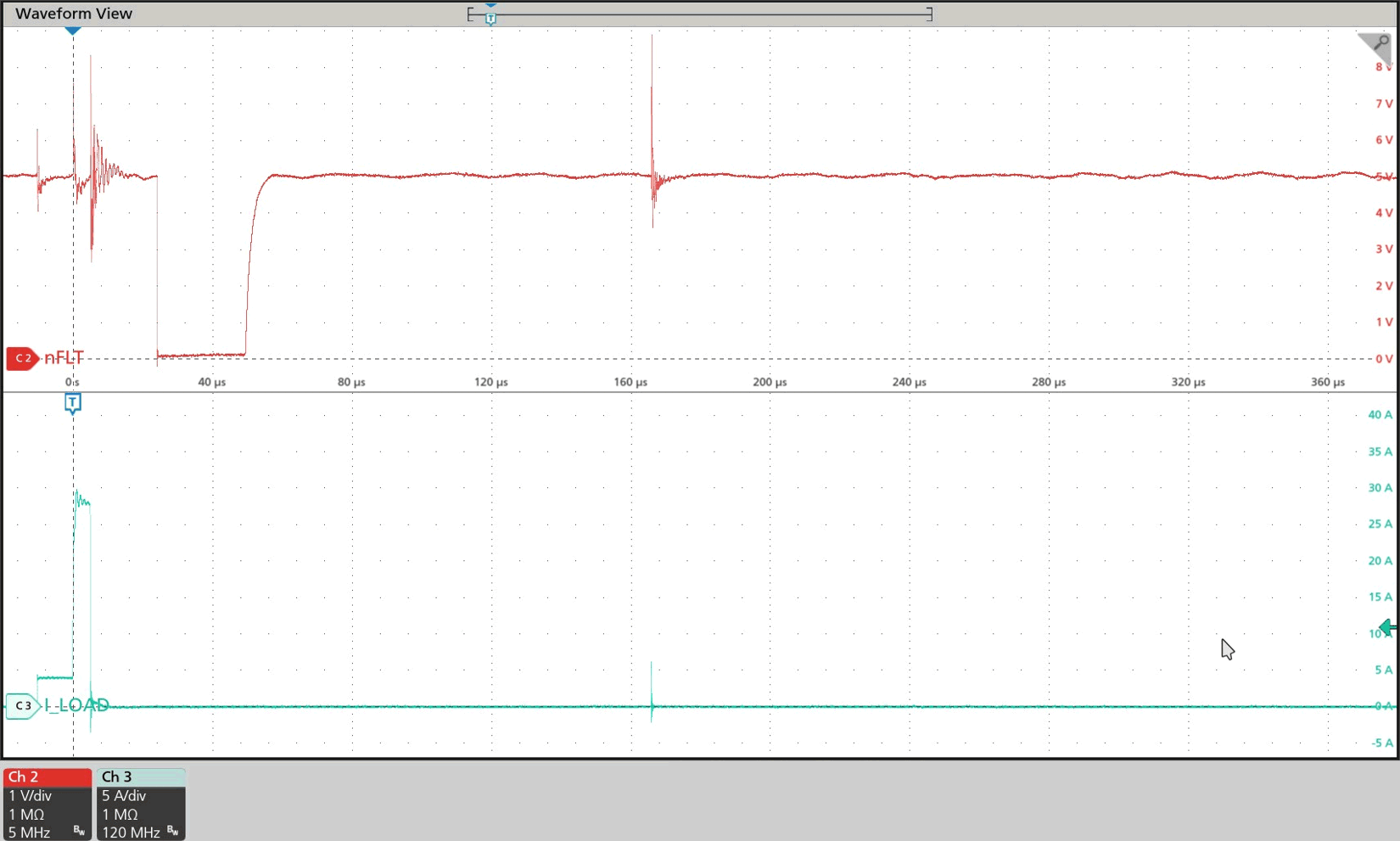

Figure 3-4 Discharge CycleFigure 3-5 shows the VDRV pin disabling after the current has exceeded the 25A limit. After the auto-recovery period has passed, the drive pin re-asserts. Similarly, in Figure 3-6, the nFLT pin on the primary side reports the fault by pulling down after 30μs passes. This pin is pulled back up after another 30μs passes.

Figure 3-5 VDRV Disable and

Re-enable

Figure 3-5 VDRV Disable and

Re-enable Figure 3-6 Primary Side Fault

Reporting

Figure 3-6 Primary Side Fault

Reporting