TIDUFA8 November 2024

- 1

- Description

- Resources

- Features

- Applications

- 6

- 1System Description

- 2System Overview

- 3System Design Theory

- 4Link Budget

- 5Hardware, Software, Testing Requirements and Test Results

- 6Design and Documentation Support

- 7About the Authors

5.4.4 Angle Resolution

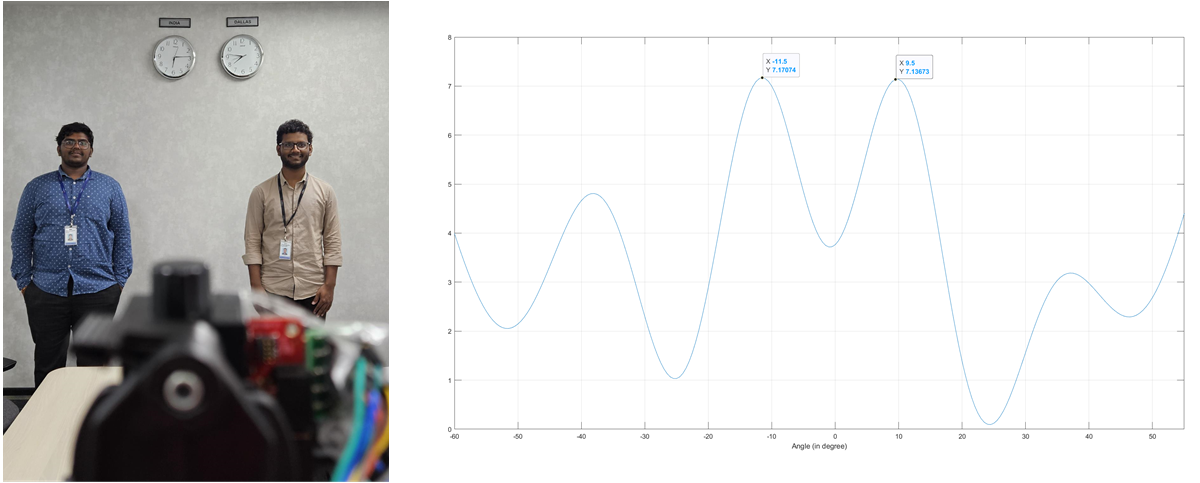

Theoretical angular resolution in azimuth plane for 6-antenna elements is 19°. In this test, two people at a 20° angle with respect to the sensor are tested and two distinct peaks in the angle plot have been observed.

This measurement is done with the 2D antenna variant. The distance of the target human beings from the sensor is 3 meters with 1 meter mutual distance that creates around a 20° angle with respect to the sensor. Two peaks have been observed 21° apart that correspond to the target human beings.

Figure 5-10 Angle Resolution Test