TIDUFA8 November 2024

- 1

- Description

- Resources

- Features

- Applications

- 6

- 1System Description

- 2System Overview

- 3System Design Theory

- 4Link Budget

- 5Hardware, Software, Testing Requirements and Test Results

- 6Design and Documentation Support

- 7About the Authors

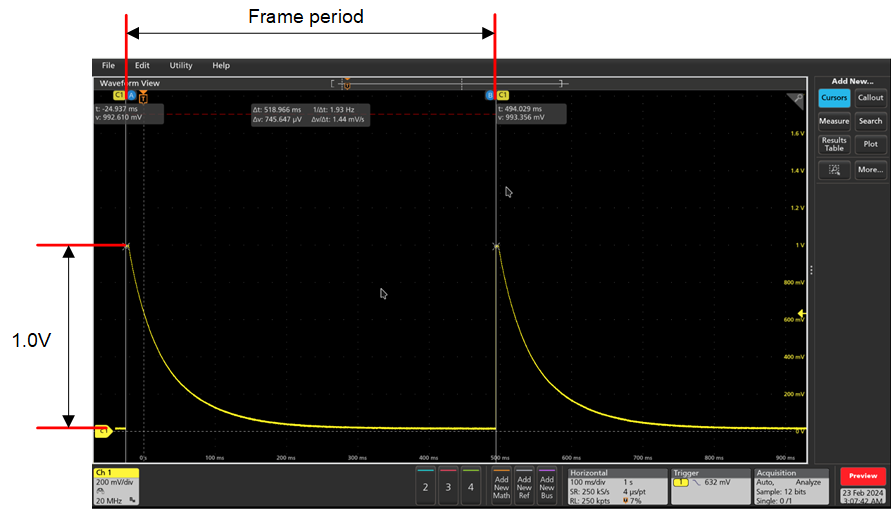

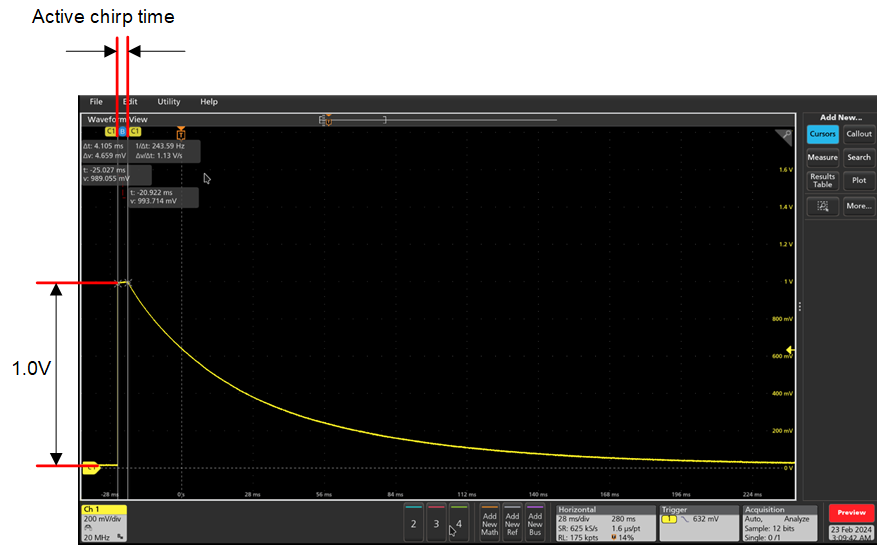

2.4.3.4 RF 1.0V Power Supply

The IWRL6432 uses a 1.0V supply line for certain RF and analog operations. This supply line stays at 1.0V for the active chirping time and then drops to 0V until the next frame starts. Similar to the other internal LDO outputs, the 1.0V supply also needs to be provided with required decoupling capacitors externally. This supply behaves the same irrespective of the device low power mode status.

Figure 2-16 and Figure 2-17 show the characteristics of the 1.0V RF supply.

The following chirp configuration have been used to capture the waveforms.

- Refresh rate: 2Hz

- Number of chirps per frame: 32

- Burst period: 10ms

- Active chirp time: 4ms

Figure 2-16 1.0V RF Supply - Wide Window

Figure 2-17 1.0V RF Supply - Close Window

The 1.0V RF supply stays at 1V for the entire active chirping duration, 4ms, for this case. After that, the voltage drops to 0V until the next frame starts.