TIDUFA8 November 2024

- 1

- Description

- Resources

- Features

- Applications

- 6

- 1System Description

- 2System Overview

- 3System Design Theory

- 4Link Budget

- 5Hardware, Software, Testing Requirements and Test Results

- 6Design and Documentation Support

- 7About the Authors

2.4.3.2.2 SYNTHESIZER 1.4V

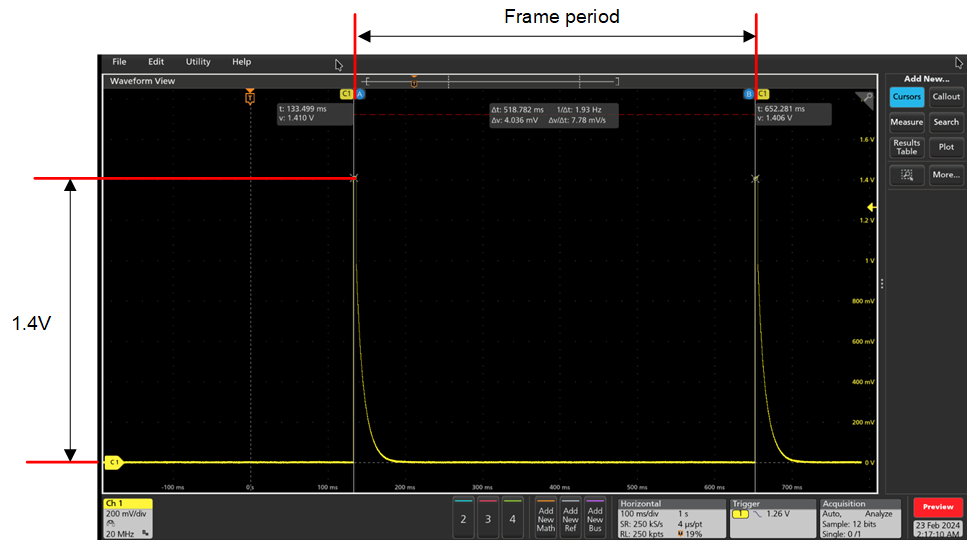

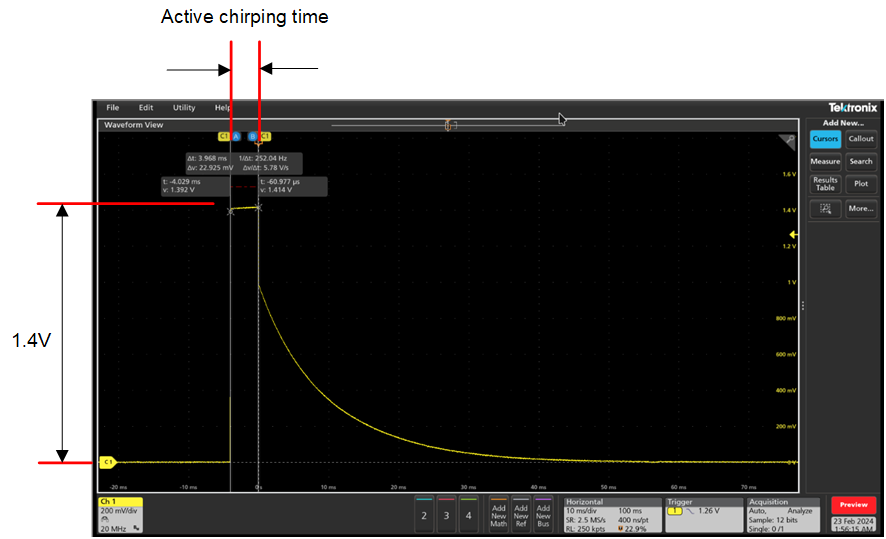

The 1.4V SYNTH supply stays at 0V after the device power up, until the device starts chirping. The supply rises to 1.4V sharply once chirping starts, and stays at the same voltage level until chirping ends in every frame. After that the supply drops to 0V until the next frame starts. Figure 2-13 and Figure 2-14 show the behavior of the 1.4V SYNTH supply.

Irrespective of low power mode, the synthesizer supply displays the same behavior.

Figure 2-13 1.4V SYNTH - Wide Window

Figure 2-14 1.4V SYNTH - Close Window

The 1.4V SYNTH supply in low power operation, stays at 1.4V for the active chirp duration, 4ms for this case. After that the supply drops down to 0V until the next frame starts.