TIDUFA8 November 2024

- 1

- Description

- Resources

- Features

- Applications

- 6

- 1System Description

- 2System Overview

- 3System Design Theory

- 4Link Budget

- 5Hardware, Software, Testing Requirements and Test Results

- 6Design and Documentation Support

- 7About the Authors

3.3 PCB

The reference design uses a 4-layer stack-up for the PCB. The stack-up is extremely critical for antenna performance. This section elaborates on the existing stack up and a couple of layout related cost reduction techniques implied.

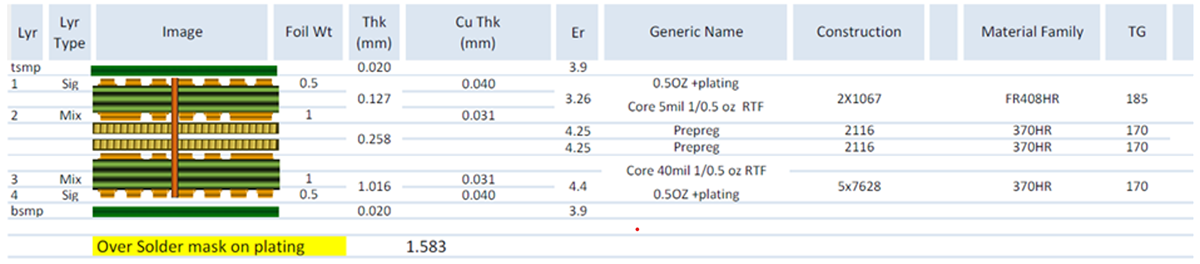

Figure 3-22 shows the stack-up details of the PCB.

Figure 3-22 PCB Stack-Up

The antenna resides on the top layer (Lyr 1) of the PCB. This layer has FR408HR dielectric material. Below are a few critical properties of the dielectric:

- The dielectric has 2 x 1067 (dual ply) spread glass construction. This structure helps reducing the glass weave effect that helps reducing losses.

- Thickness of the dielectric is 5mils (127um). This thickness value is adjusted for impedance matching.

- The Dk value of the dielectric is 3.3

- This is core material.

- The dielectric thickness must not be altered as this can cause impedance mismatch and more reflection of the radiated power.

- Pre-preg material must not be used for the antenna layer. For the layers in between other than antenna, pre-preg can be used.

Grounded coplanar waveguide (GCPW) transmission lines have been used to carry the RF signals to the antenna. Below are some critical considerations for the antenna layer and the ground layer followed by the same:

- Finished copper thickness on the antenna layer is 40um.

- Ground plane (below the antenna plane, Layer 2) thickness is 1oz (0.5oz can also be used if 1oz is not available).

- PCB surface finish is OSP or

immersion silver.Note: ENIG surface finish is NOT recommended as this can potentially cause higher insertion losses for the mmWave frequency range.

The overall PCB thickness of the reference design is 1.6mm.

Following are some of the techniques implied to reduce the cost of PCB design: