TIDUFA8 November 2024

- 1

- Description

- Resources

- Features

- Applications

- 6

- 1System Description

- 2System Overview

- 3System Design Theory

- 4Link Budget

- 5Hardware, Software, Testing Requirements and Test Results

- 6Design and Documentation Support

- 7About the Authors

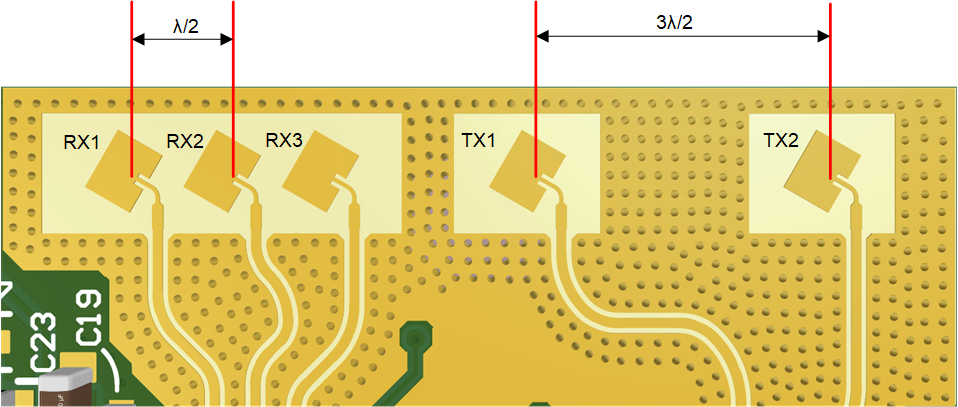

3.2.2 1D Antenna Array With 2D Detection Capability

The 1D antenna variant has all the Tx and Rx antennas in one single line. Two Tx antennas separated by 3λ/2, three Rx antennas, all separated by λ/2 as shown in Figure 3-20. This geometry generates a single line six element virtual array. Although in azimuth direction the virtual array has six elements, in elevation direction the array has one element as shown in Figure 3-21, resulting in a 2-dimension detection capability for the antenna variant in only azimuth plane. This means that targets cannot be localized in the elevation and cannot be resolvable in the elevation. That objects still in the FOV can all be projected into the 2D space.

Figure 3-20 1D Antenna Patch Array Geometry

Figure 3-21 shows the geometry of the virtual antenna array with each index depicting spacing factor of λ/2. Position 0, 1, and 2 represents placement of virtual antenna originated from combination of all 3 Rx (Rx1, Rx2, Rx3) and Tx1. Position 3, 4, and 5 represents placement of virtual antenna originated from combination of all 3 Rx (Rx1, Rx2, Rx3) and Tx2.

Figure 3-21 1D Antenna - Virtual Array

The virtual antenna forms a single line with six elements. Six elements in azimuth direction yields an angular resolution of 19 degrees. Although the 1D antenna has poor angular resolution in the elevation direction, reason having a 2D detection capability in the azimuth direction only.