TIDUFA8 November 2024

- 1

- Description

- Resources

- Features

- Applications

- 6

- 1System Description

- 2System Overview

- 3System Design Theory

- 4Link Budget

- 5Hardware, Software, Testing Requirements and Test Results

- 6Design and Documentation Support

- 7About the Authors

3.5.2.3 Trace Width of High Current Carrying Traces

Follow this design practice for all the on-chip LDO outputs to maintain shortest ground return path.

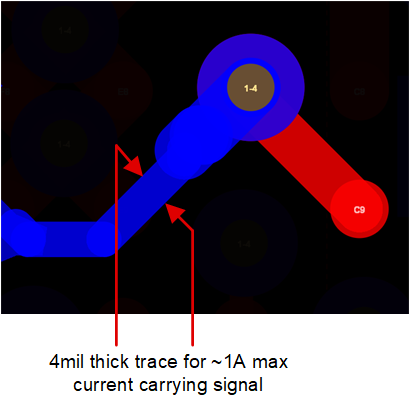

Figure 3-32 Trace width: Non-Best Practice

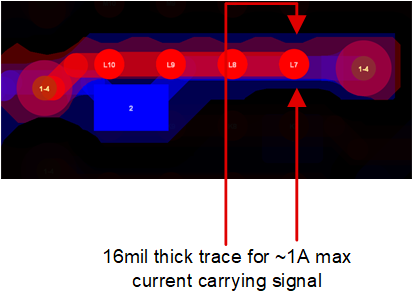

Figure 3-33 Trace Width: Best Practice

The PCB trace width must be sufficient to support the max current requirement of the respective signal. The following are examples of good and bad design practices for a trace carrying a high current signal.

Figure 3-32 shows a trace of width 4mils for a signal that can carry a max. of 1A current. This trace can not support this much of a max current.

Figure 3-33 shows a trace of width 16mils for a signal that can carry a max of 1A current. This is a good design as the trace is thick enough to support this current.

Consider the max current and selecting the trace thickness accordingly. Usually 12-15mils thick trace is enough to carry 1A max current.