TIDUFA8 November 2024

- 1

- Description

- Resources

- Features

- Applications

- 6

- 1System Description

- 2System Overview

- 3System Design Theory

- 4Link Budget

- 5Hardware, Software, Testing Requirements and Test Results

- 6Design and Documentation Support

- 7About the Authors

3.5.2.1 Decoupling Capacitor Placement

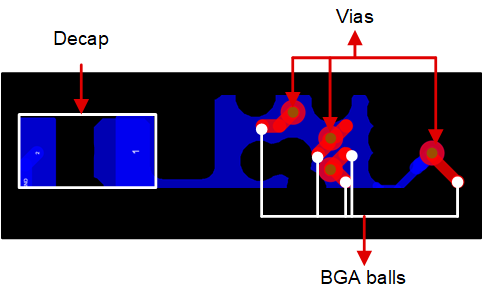

Figure 3-29 Decoupling Capacitor Placement: Non-Best Practice

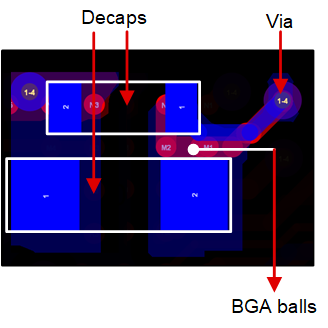

Figure 3-30 Decoupling Capacitor Placement: Best Practice

On-chip LDOs require external capacitors for dominant pole compensation. For this, the capacitor placement and the output path traces become PCB design constraint dependent. The parasitic components contributed by the output path play a vital role in determining the system stability. In the previous section we have listed specific parasitic inductance and resistance values for each of the high bandwidth sensitive LDOs to make sure the stability of the power supplies. Here we are going to observe an example of good and bad practices while designing the PCB layout.

Figure 3-29 shows a design where the decap is placed far from the respective LDO-output BGA-balls. Considering the length of the complete trace connecting the balls to the capacitor lead by adding:

- The trace connecting the BGA balls to the respective vias in the top layer (traces marked in red are on the top layer of the PCB)

- Via length

- The trace connecting the vias to the capacitor lead (traces marked in blue are in the bottom layer of the PCB), we get a very long path. The combined parasitic of such long path can potentially alter the parasitic spec provided in data sheet, which can affect the LDO system stability.

Figure 3-30 shows a design where the capacitor is places very close to the BGA balls. Considering the possibilities of system instability involved with the previous example, this design is much better as the parasitic values are within the data sheet spec.