-

What’s Not in the Power MOSFET Data Sheet Part 2: Voltage-dependent Leakage Currents

What’s Not in the Power MOSFET Data Sheet Part 2: Voltage-dependent Leakage Currents

John Wallace1

In part 1 of this series, I reviewed power metal-oxide semiconductor field-effect transistor (MOSFET) data sheets and explained what’s in the data sheet and more importantly, what’s not, while specifically looking at the temperature dependence of some key MOSFET parameters. In part 2, I’ll focus on voltage-dependent leakage currents – the drain-to-source leakage (IDSS) and the gate-to-source leakage (IGSS).

Why leakage currents? There are two fundamental reasons why leakage currents are important when selecting a power MOSFET for your application. First, in electronic systems, there is a green campaign to reduce wasted power, especially when the system is operating in standby mode. And second, in battery-operated systems low leakage helps maximize both battery life for primary cells and the run time between charges for secondary cells.

MOSFET Leakage Currents

As shown in Figure 1, the MOSFET data sheet for the CSD15380F3 specifies two leakage currents: IDSS and IGSS.

Figure 1 Leakage Current Specifications from the CSD15380F3 Data Sheet

Figure 1 Leakage Current Specifications from the CSD15380F3 Data SheetThe maximum leakage is specified at one voltage: IDSS at 80% of BVDSS (VGS = 0 V) and IGSS at the absolute maximum VGS (VDS = 0 V). I’m often asked how these parameters vary with voltage, and the answer depends not only on the applied voltage but also on the gate electrostatic discharge (ESD) structure, as detailed in the technical article, “What type of ESD protection does your MOSFET include?” As a refresher, the three types of ESD protection used in TI MOSFETs are none (lowest leakage), single-ended (lowest leakage) and back-to-back (highest leakage).

IGSS Current

In this section, I’ll present graphs showing IGSS variation with voltage for several TI N- and P-channel NexFET™ power MOSFETs with the three types of gate ESD protection. These are typical curves for design guidance only and not a guarantee of performance. TI only guarantees leakage as specified in the MOSFET data sheet.

Figure 2 shows sweeps of IGSS vs. VGS for a 30-V N-channel FET (NFET) and a –20-V P-channel FET (PFET) that have no gate ESD protection. The leakage is relatively flat until VGS gets close to its positive and negative absolute maximum limits.

Figure 2 IGSS Vs. vGS With No ESD Protection: 30-v NFET (a); and –20-v PFET (b)

Figure 2 IGSS Vs. vGS With No ESD Protection: 30-v NFET (a); and –20-v PFET (b)Figure 3 shows IGSS for a 20-V N-channel FET and a –20-V P-channel FET with a single-ended gate ESD protection structure. The leakage current increases exponentially when the gate ESD diode becomes forward-biased. If this is likely to occur in an application, then you must use an external gate resistor to limit the current and prevent damage to the MOSFET.

Figure 3 IGSS vs. VGS with single-ended ESD protection: 20-V NFET (a); and –20-V PFET (b)

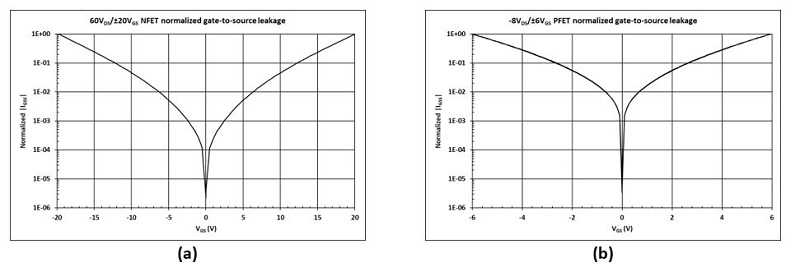

Figure 3 IGSS vs. VGS with single-ended ESD protection: 20-V NFET (a); and –20-V PFET (b)The plots in Figure 4 display IGSS for a 60-V NFET and a –8-V PFET with a back-to-back gate ESD protection structure. These devices display a symmetric leakage characteristic around VGS = 0 V because of the back-to-back gate ESD diodes.

Figure 4 IGSS vs. VGS with back-to-back ESD protection: 60-V NFET (a); and –8-V PFET (b)

Figure 4 IGSS vs. VGS with back-to-back ESD protection: 60-V NFET (a); and –8-V PFET (b)IDSS Current

The other MOSFET leakage current, IDSS, is from drain-to-source when the FET is off. The next several graphs show IDSS vs. VDS for TI NFETs and PFETs with the three types of ESD protection. These are typical curves for design guidance only and not a guarantee of performance. TI only guarantees leakage as specified in the MOSFET data sheet.

Figure 5 plots IDSS for a 30-V NFET and a –20-V PFET with no ESD protection.

Figure 5 IDSS Vs. vDS With No ESD Protection: 30-v NFET (a); and –20-v PFET (b)

Figure 5 IDSS Vs. vDS With No ESD Protection: 30-v NFET (a); and –20-v PFET (b)Figure 6 shows IDSS for a 20-V N-channel MOSFET and a –20-V P-channel FET, with a single-ended gate ESD protection diode.

Figure 6 IDSS Vs. vDS With Single-ended ESD Protection: 20-v NFET (a); and –20-v PFET (b)

Figure 6 IDSS Vs. vDS With Single-ended ESD Protection: 20-v NFET (a); and –20-v PFET (b)The plots in Figure 7 display IDSS for a 12-V N-channel MOSFET and a –20-V P-channel MOSFET with the back-to-back gate ESD protection structure.

Figure 7 IDSS Vs. vDS With Back-to-back ESD Protection: 12-v NFET (a); and –20-v PFET (b)

Figure 7 IDSS Vs. vDS With Back-to-back ESD Protection: 12-v NFET (a); and –20-v PFET (b)Conclusion

I hope that the typical curves of IGSS current and IGSS vs. VGS, and IDSS current and IDSS vs. VDS will help you understand how MOSFET leakage currents vary with voltage. TI specifies and tests the maximum leakage currents at the conditions in the Electrical Characteristics data sheet. As a reminder, always use the data-sheet limits when designing with TI FETs, and if you don’t see it in the data sheet, request it from your FET vendor.

Additional Resources

- Visit the TI MOSFET support and training center.

- Check out these technical articles

IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES “AS IS” AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI’s products are provided subject to TI’s Terms of Sale (www.ti.com/legal/termsofsale.html) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI’s provision of these resources does not expand or otherwise alter TI’s applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2023, Texas Instruments Incorporated