-

LM25037/-Q1 Dual-Mode PWM Controller With Alternating Outputs

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Detailed Description

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

- IMPORTANT NOTICE

Package Options

Mechanical Data (Package|Pins)

- PW|16

Thermal pad, mechanical data (Package|Pins)

Orderable Information

LM25037/-Q1 Dual-Mode PWM Controller With Alternating Outputs

1 Features

- Qualified for Automotive Applications

- AEC-Q100 Qualified With the Following Results:

- Device Temperature Grade 1: –40°C to +125°C Operating Junction Temperature

- Device HBM ESD Classification Level 2

- Device CDM ESD Classification Level C4B

- Alternating Outputs for Double-Ended Topologies

- Ultra Wide Input Operating Range from 5.5 V to 75 V

- Current-Mode or Feed-Forward Voltage-Mode Control

- Programmable Maximum Duty Cycle Limit

- 2% Feedback Reference Accuracy

- High Gain-Bandwidth Error Amplifier

- Programmable Line Undervoltage Lockout (UVLO) With Adjustable Hysteresis

- Versatile Dual Mode Overcurrent Protection With Hiccup Delay Timer

- Programmable Soft-Start

- Precision 5-V Reference Output

- Current Sense Leading Edge Blanking

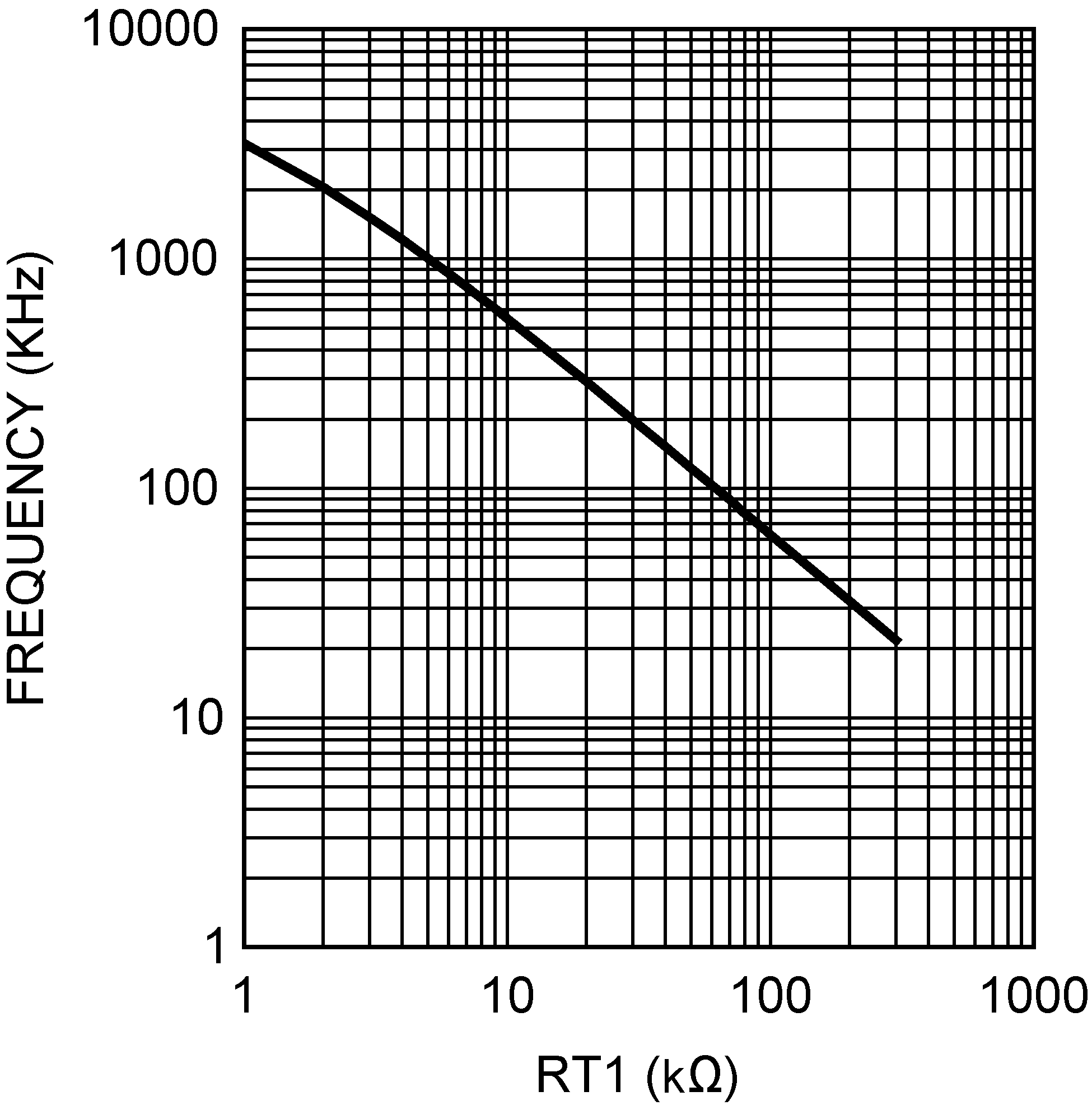

- Resistor Programmed 2-MHz Capable Oscillator

- Oscillator Synchronization Capability With Low-Frequency Lockout Protection

- 16-Pin TSSOP

2 Applications

- Telecom Power Converters

- Industrial Power Converters

- Automotive Power Converters (Q1 Version)

3 Description

The LM25037 PWM controller contains all the features necessary to implement balanced double-ended power converter topologies, such as push-pull, half-bridge and full-bridge. These double-ended topologies allow for higher efficiencies and greater power densities compared to common single-ended topologies such as the flyback and forward. The LM25037 can be configured for either voltage mode or current mode control with minimum external components. Two alternating gate drive outputs are provided, each capable of 1.2-A peak output current. The LM25037 can be configured to operate directly from the input voltage rail over an ultra-wide range of 5.5 V to 75 V. Additional features include programmable maximum duty cycle limit, line undervoltage lockout, cycle-by-cycle current limit and a hiccup mode fault protection with adjustable timeout delay, soft-start and a 2-MHz capable oscillator with synchronization capability, precision reference and thermal shutdown.

Device Information(1)

| PART NUMBER | PACKAGE | BODY SIZE (NOM) |

|---|---|---|

| LM25037 LM25037-Q1 |

TSSOP (16) | 5.00 mm × 4.40 mm |

- For all available packages, see the orderable addendum at the end of the data sheet.

Simplified Push-Pull Power Converter

4 Revision History

Changes from D Revision (March 2013) to E Revision

- Added ESD Ratings table, Feature Description section, Device Functional Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device and Documentation Support section, and Mechanical, Packaging, and Orderable Information section Go

- Deleted Typical Application Circuit Efficiency (previously Figure 1.) graph from Typical Characteristics Go

Changes from C Revision (March 2013) to D Revision

- Changed layout of National Data Sheet to TI formatGo

5 Pin Configuration and Functions

Pin Functions

| PIN | I/O | DESCRIPTION | APPLICATION INFORMATION | |

|---|---|---|---|---|

| NO. | NAME | |||

| 1 | RAMP | I | Pulse width modulator ramp | Modulation ramp for the PWM comparator. This ramp can be a representative of the primary current (current mode) or proportional to input voltage (feed-forward voltage mode). This pin is reset to ground at the conclusion of every cycle by an internal FET. |

| 2 | UVLO | I | Line undervoltage lockout | An external voltage divider from the power source sets the shutdown and standby comparator threshold levels. When UVLO exceeds the 0.45V shutdown threshold, the VCC and REF regulators are enabled. When UVLO exceeds the 1.25V standby threshold, the SS pin is released and the device enters the active mode. |

| 3 | COMP | I/O | Input to the pulse width modulator | Output of the error amplifier and input to the PWM comparator. |

| 4 | FB | I | Feedback | Connected to inverting input of the error amplifier. An internal 1.25-V reference is connected to the noninverting input of the error amplifier. In isolated applications using an external error amplifier, this pin should be connected to the AGND pin. |

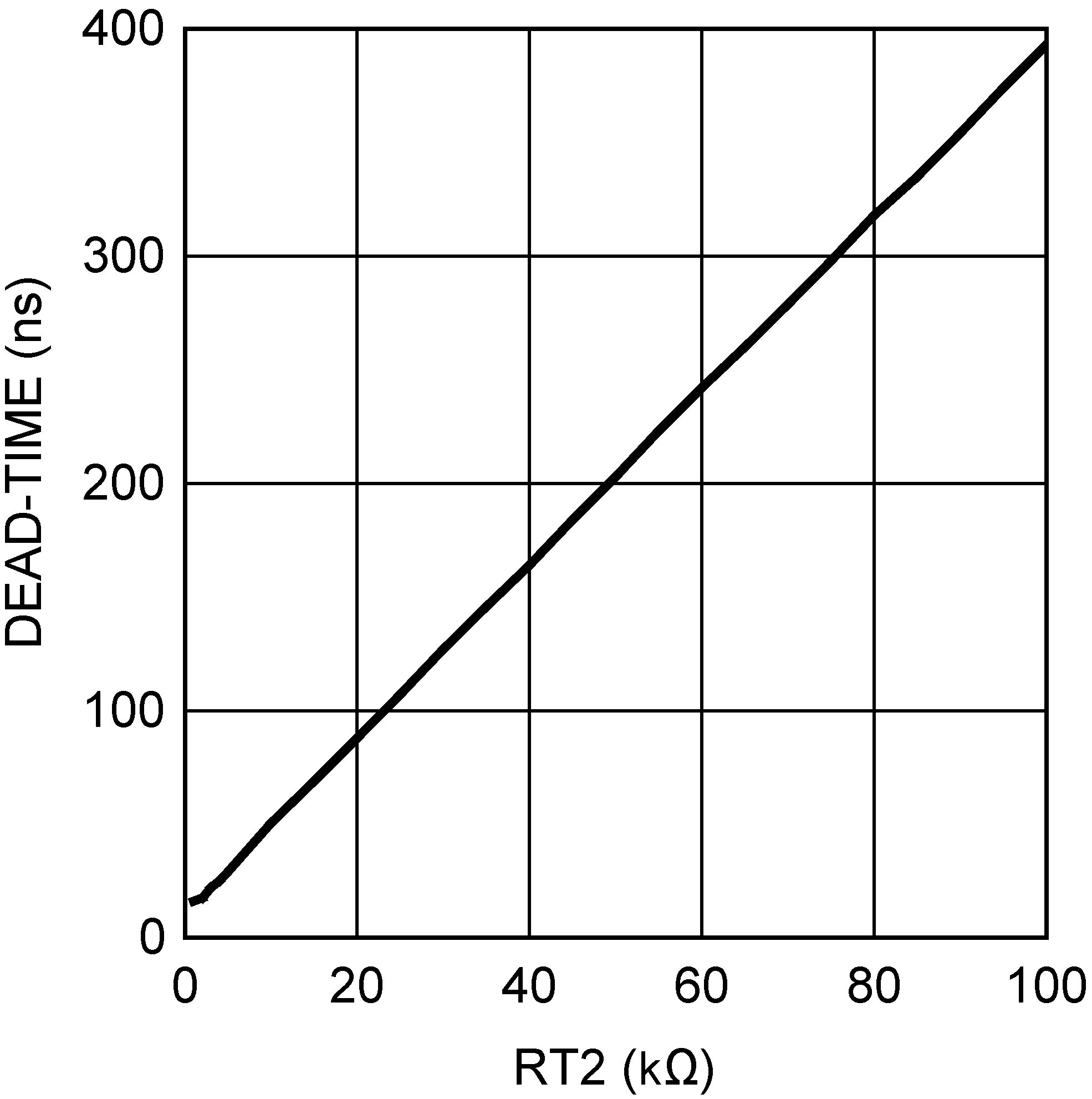

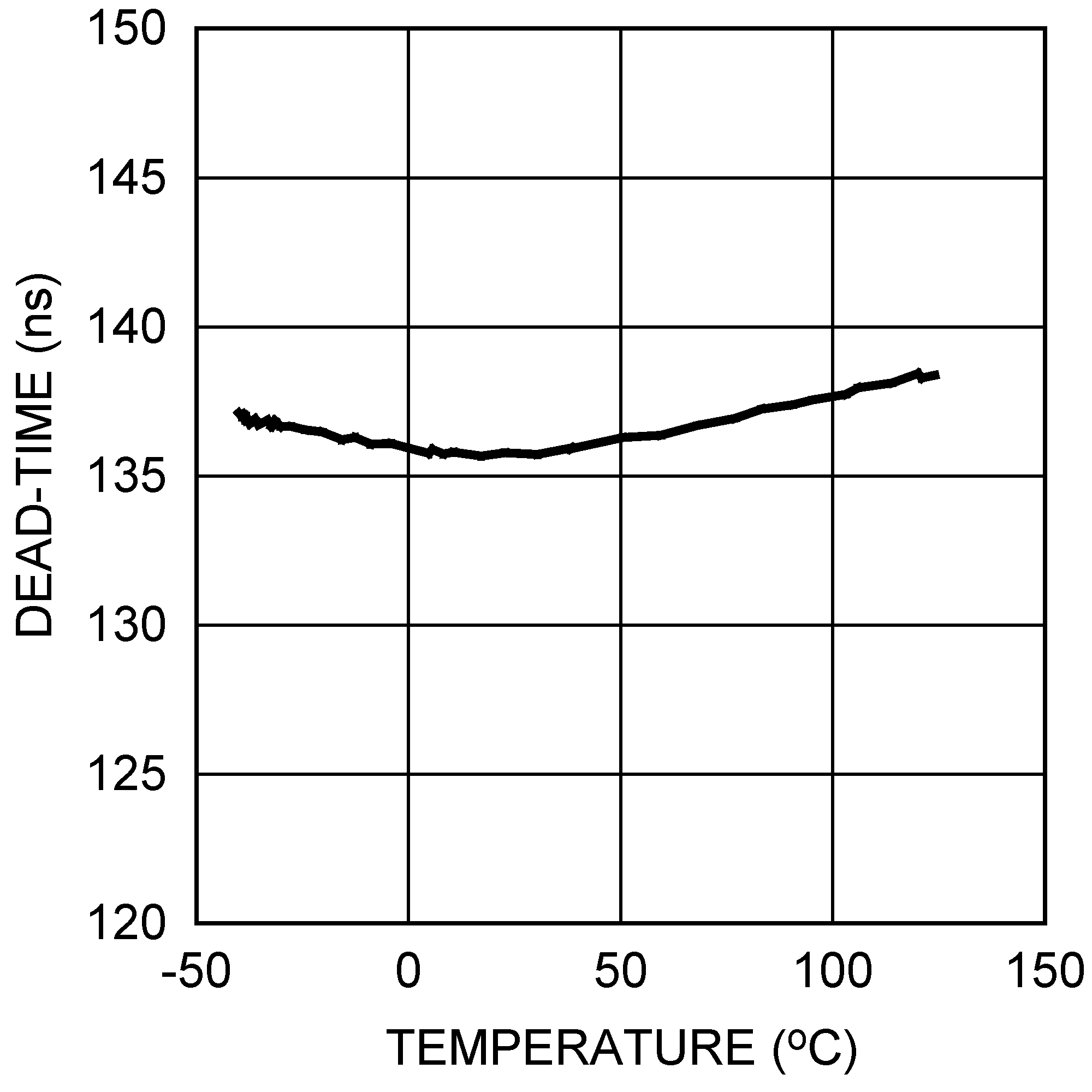

| 5 | RT2 | I | Oscillator dead-time control | The resistance connected between RT2 and AGND sets the forced dead-time between switching periods of the alternating outputs. |

| 6 | AGND | — | Analog ground | Connect directly to Power Ground. |

| 7 | RT1 | I | Oscillator maximum on-time control | The resistance connected between RT1 and AGND sets the oscillator maximum on-time. The sum of this maximum on-time and the forced dead-time (set by RT2) sets the oscillator period. |

| 8 | CS | I | Current sense input | If CS exceeds 250 mV the output pulse will be terminated, entering cycle-by-cycle current limit. An internal switch holds CS low for 65 nS after either output switches high to blank leading edge transients. |

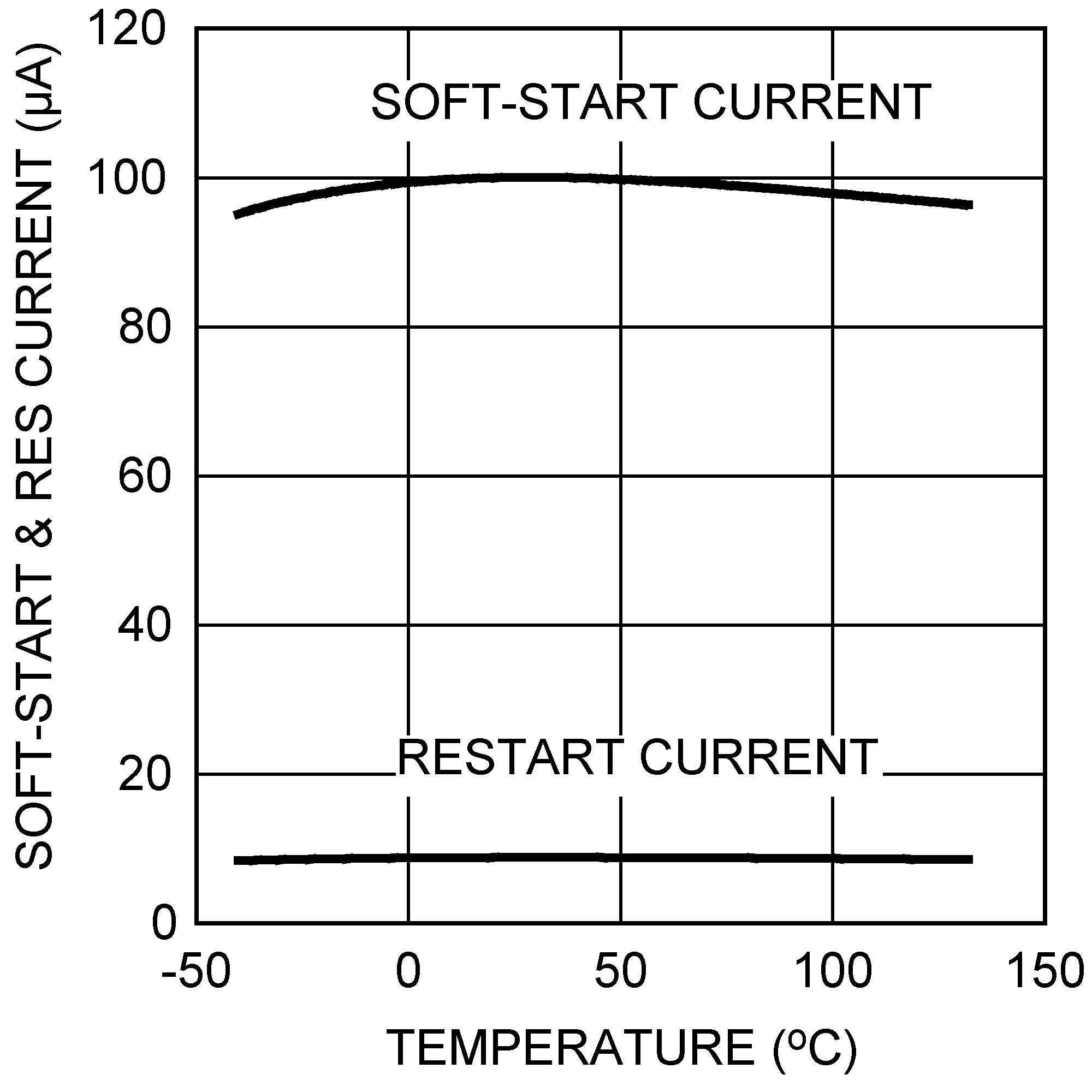

| 9 | RES | I/O | Restart timer | If cycle-by-cycle current limit is reached during any cycle, a 18-µA current is sourced to the external RES pin capacitor. If the RES capacitor voltage reaches 2 V, the soft-start capacitor will be fully discharged and then released with a pullup current of 1 uA. After the first output pulse (when SS = 1V), the SS pin charging current will increase to the normal level of 100 µA. |

| 10 | SS | I | Soft-start | An external capacitor and an internal 100uA current source set the soft-start ramp. The SS current source is reduced to 1 µA following a restart event (RES pin high). |

| 11 | PGND | — | Power ground | Connect directly to Analog Ground |

| 12 | OUTB | O | Output driver | Alternating gate drive output of the pulse width modulator. Capable of 1.2-A peak source and sink current. |

| 13 | OUTA | O | Output driver | Alternating gate drive output of the pulse width modulator. Capable of 1.2-A peak source and sink current. |

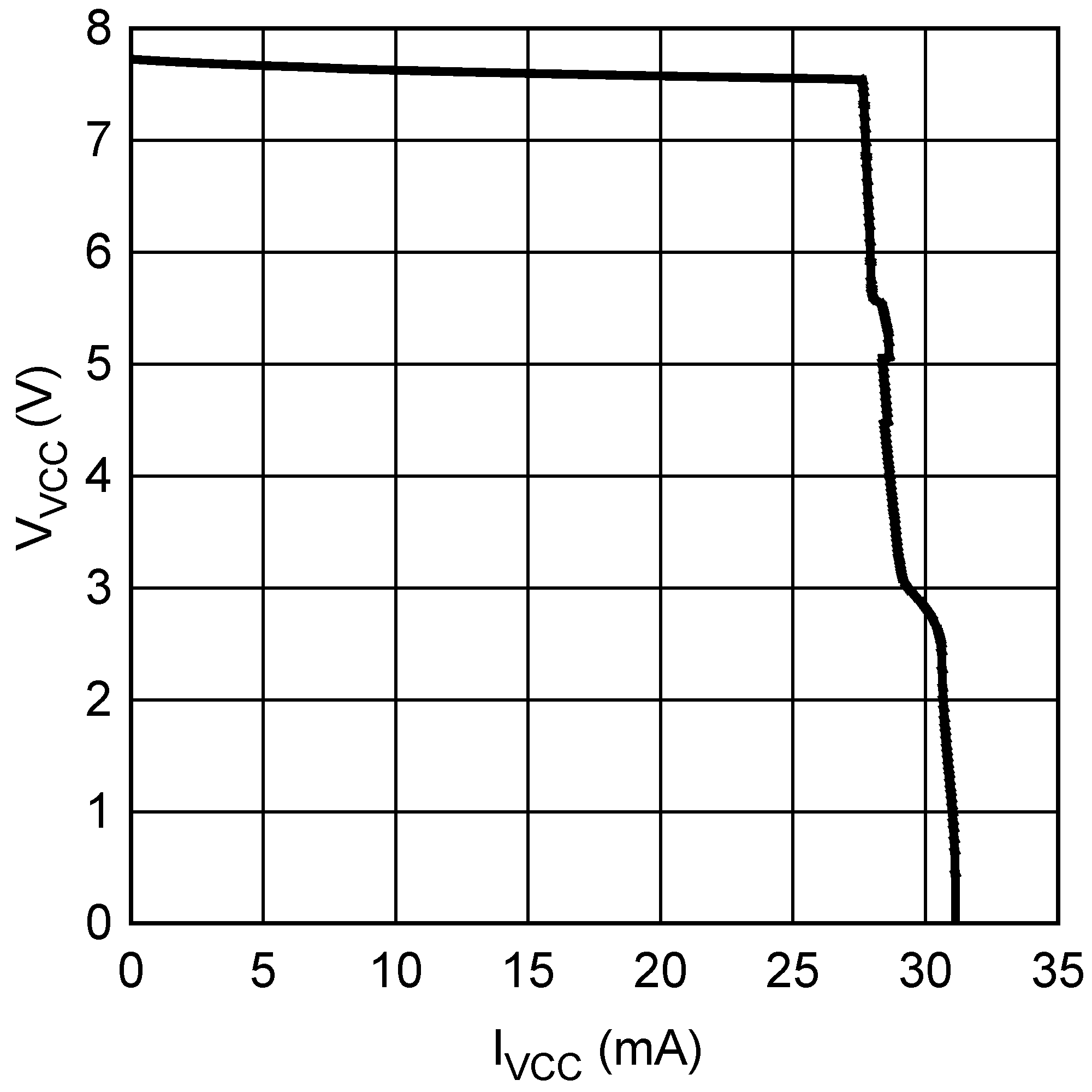

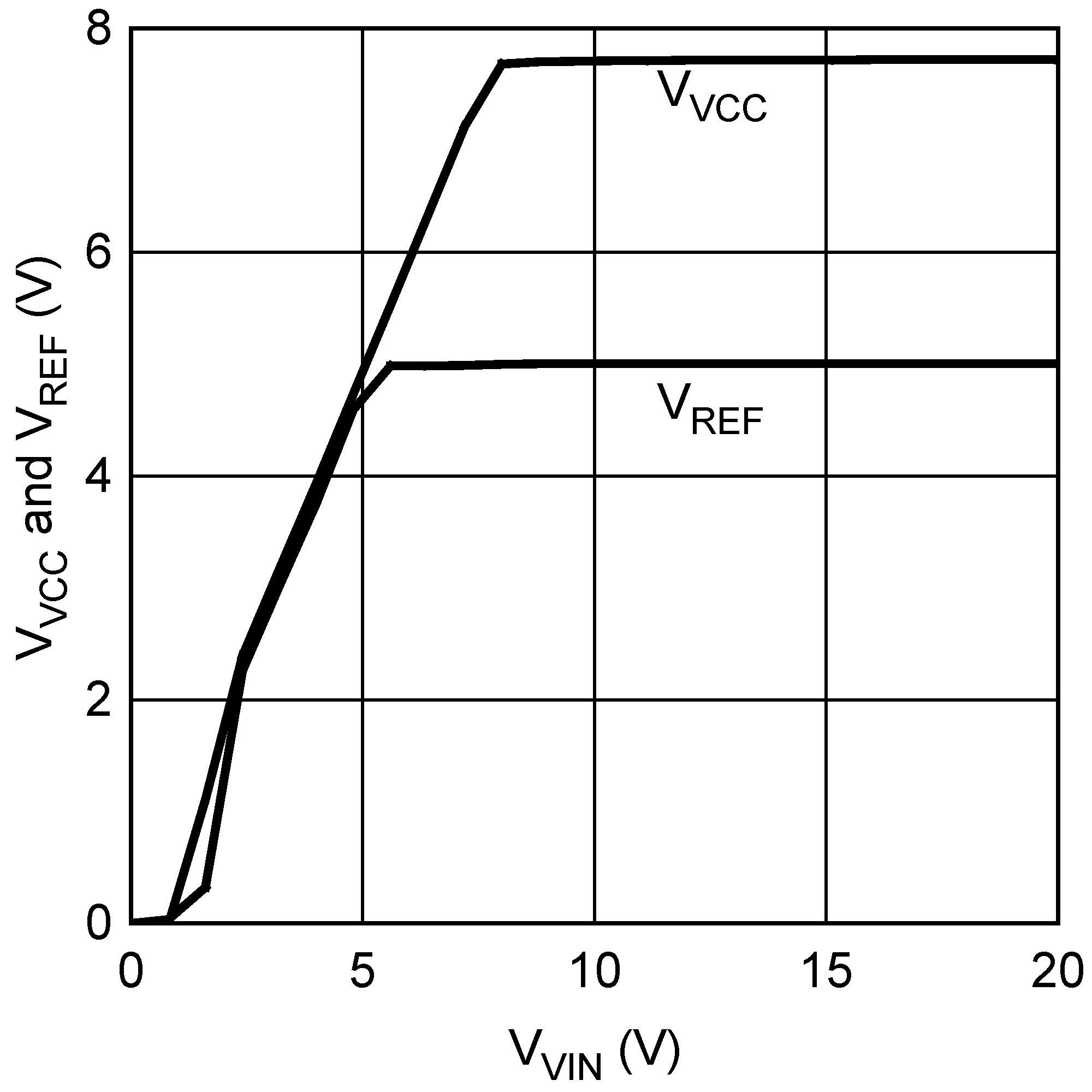

| 14 | VCC | I/O | Output of the high voltage start-up regulator. The VCC voltage is regulated to 7.7 V. | If an auxiliary winding raises the voltage on this pin above the regulation set point, the internal start-up regulator will shutdown thus reducing the IC power dissipation. Locally decouple VCC with a 0.47 µF or greater capacitor. |

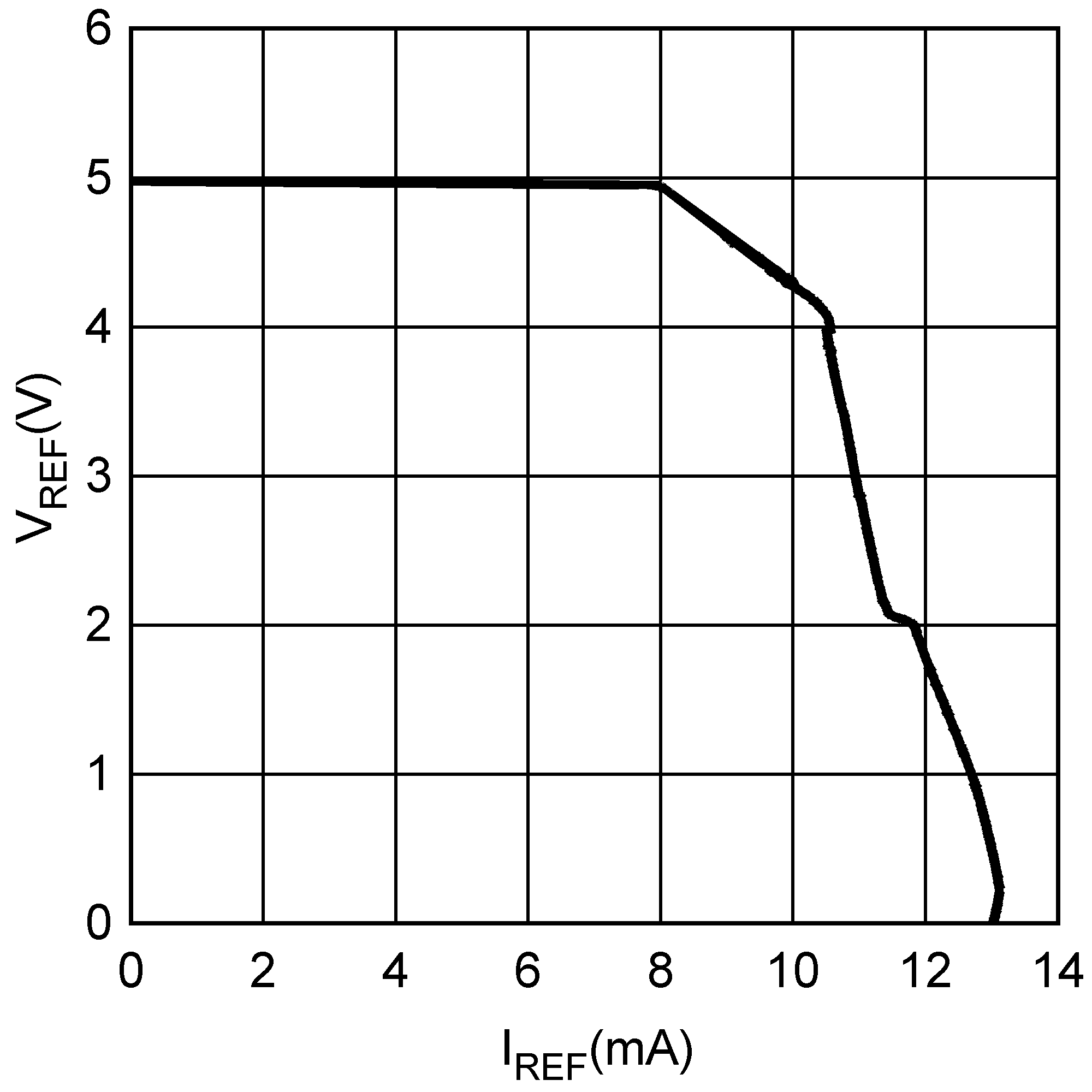

| 15 | REF | O | Output of a 5-V reference | Locally decouple with a 0.1 µF or greater capacitor. Maximum output current is 10 mA (typical). |

| 16 | VIN | I | Input voltage source | Input to the VCC Start-up regulator. Operating input range is 5.5 V to 75 V. For power sources outside of this range, the LM25037 can be biased directly at VCC by an external regulator. |

6 Specifications

6.1 Absolute Maximum Ratings

over operating junction temperature range (unless otherwise noted)(1)(2)| MIN | MAX | UNIT | ||

|---|---|---|---|---|

| VIN to GND | –0.3 | 76 | V | |

| VCC, RAMP , OUTA, OUTB to GND | –0.3 | 16 | V | |

| CS to GND | –0.3 | 1 | V | |

| UVLO, FB, RT2, RT1, SS, REF to GND | –0.3 | 7 | V | |

| COMP, RES(3) | ||||

| Junction temperature | 150 | °C | ||

| Storage temperature | –65 | 150 | °C | |

6.2 ESD Ratings: LM25037

| VALUE | UNIT | |||

|---|---|---|---|---|

| V(ESD) | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001(1) | ±2000 | V |

| Charged-device model (CDM), per JEDEC specification JESD22-C101(2) | ±750 | |||

6.3 ESD Ratings: LM25037-Q1

| VALUE | UNIT | ||||

|---|---|---|---|---|---|

| V(ESD) | Electrostatic discharge | Human-body model (HBM), per AEC Q100-002(1) | ±2000 | V | |

| Charged-device model (CDM), per AEC Q100-011 | All pins | ±750 | |||

| Corner pins (1, 8, 9, 16) | ±750 | ||||

6.4 Recommended Operating Conditions

over operating junction temperature range (unless otherwise noted)| MIN | NOM | MAX | UNIT | ||

|---|---|---|---|---|---|

| VIN voltage | 5.5 | 75 | V | ||

| External voltage applied to VCC | 8 | 14 | V | ||

| Operating junction temperature | −40 | 125 | °C | ||

6.5 Thermal Information

| THERMAL METRIC(1) | LM25037/LM25037-Q1 | UNIT | |

|---|---|---|---|

| PW (TSSOP) | |||

| 16 PINS | |||

| RθJA | Junction-to-ambient thermal resistance | 99.9 | °C/W |

| RθJC(top) | Junction-to-case (top) thermal resistance | 32.6 | °C/W |

| RθJB | Junction-to-board thermal resistance | 45.8 | °C/W |

| ψJT | Junction-to-top characterization parameter | 2 | °C/W |

| ψJB | Junction-to-board characterization parameter | 45.1 | °C/W |

| RθJC(bot) | Junction-to-case (bottom) thermal resistance | N/A | °C/W |

6.6 Electrical Characteristics

VVIN = 12V, VVCC = 10V, RRT1 = 30.1 kΩ, RRT2 = 30.1 kΩ, VUVLO = 3 V, TJ =−40°C to +125° unless otherwise stated.(1)(2)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | ||

|---|---|---|---|---|---|---|---|

| START-UP REGULATOR (VCC PIN) | |||||||

| VVCC | VCC voltage | IVCC = 10 mA | 7.2 | 7.7 | 8.1 | V | |

| IVCC(Lim) | VCC current limit | VVCC = 7 V | 20 | mA | |||

| VVCC(UV) | VCC Undervoltage threshold | 4.6 | 5 | 5.4 | V | ||

| Hysteresis | 0.5 | V | |||||

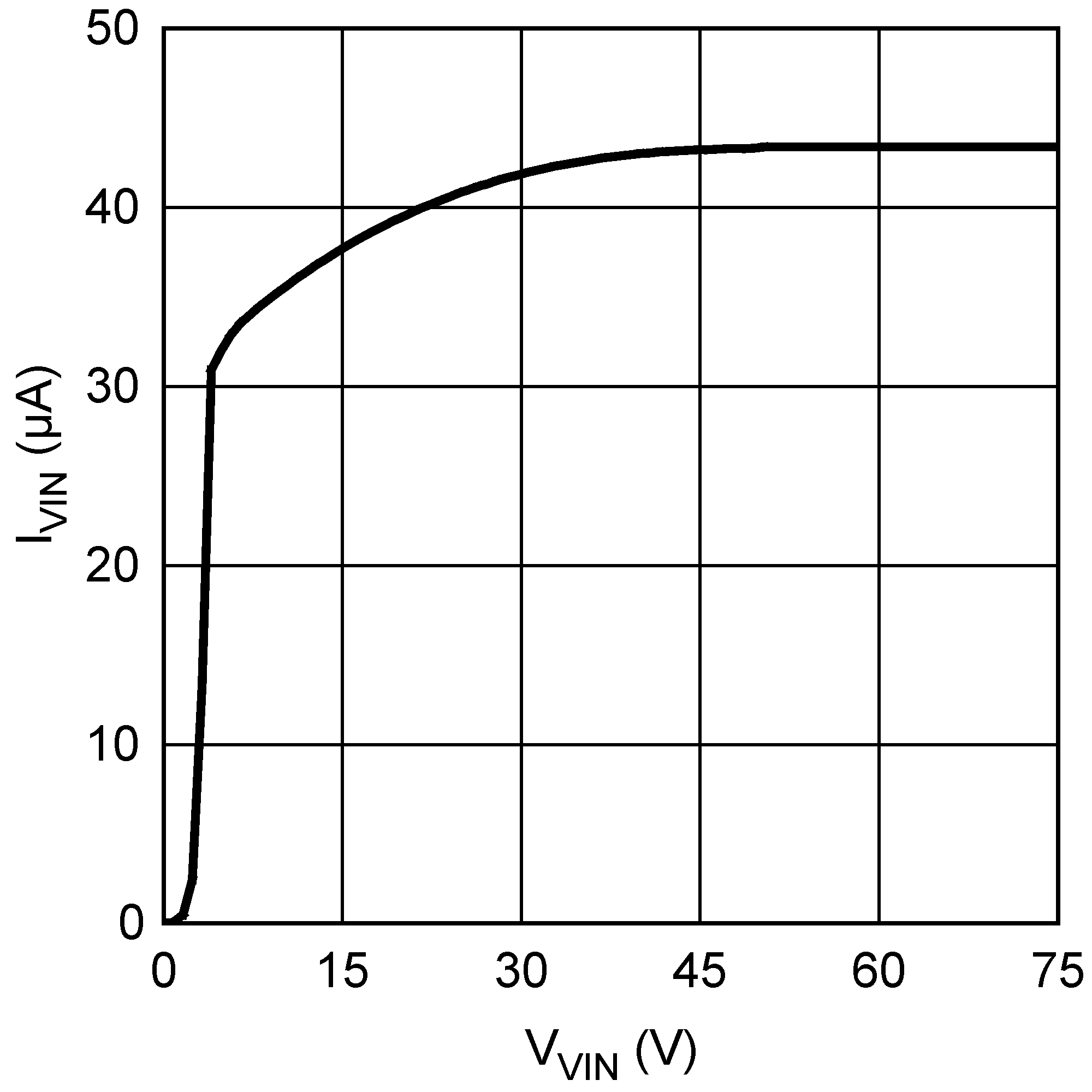

| IVIN | Start-up regulator current | VVIN = 20 V, VUVLO = 0 V | 35 | 58 | µA | ||

| VVIN = 75 V, VUVLO = 0 V | 45 | 80 | µA | ||||

| Supply current into VCC from external source | Outputs and COMP open, VVCC = 10 V, Outputs switching | 4 | mA | ||||

| VOLTAGE REFERENCE REGULATOR (REF PIN) | |||||||

| VREF | REF Voltage | IREF = 0 mA | 4.75 | 5 | 5.15 | V | |

| REF Voltage Regulation | IREF = 0 to 2.5 mA | 7 | 25 | mV | |||

| IREF(Lim) | REF Current Limit | VREF = 4.5 V | 5 | 10 | mA | ||

| VREF Undervoltage threshold | 3.7 | 4 | 4.3 | V | |||

| VREF(UV) | Hysteresis | 0.4 | V | ||||

| UNDERVOLTAGE LOCKOUT AND SHUTDOWN (UVLO PIN) | |||||||

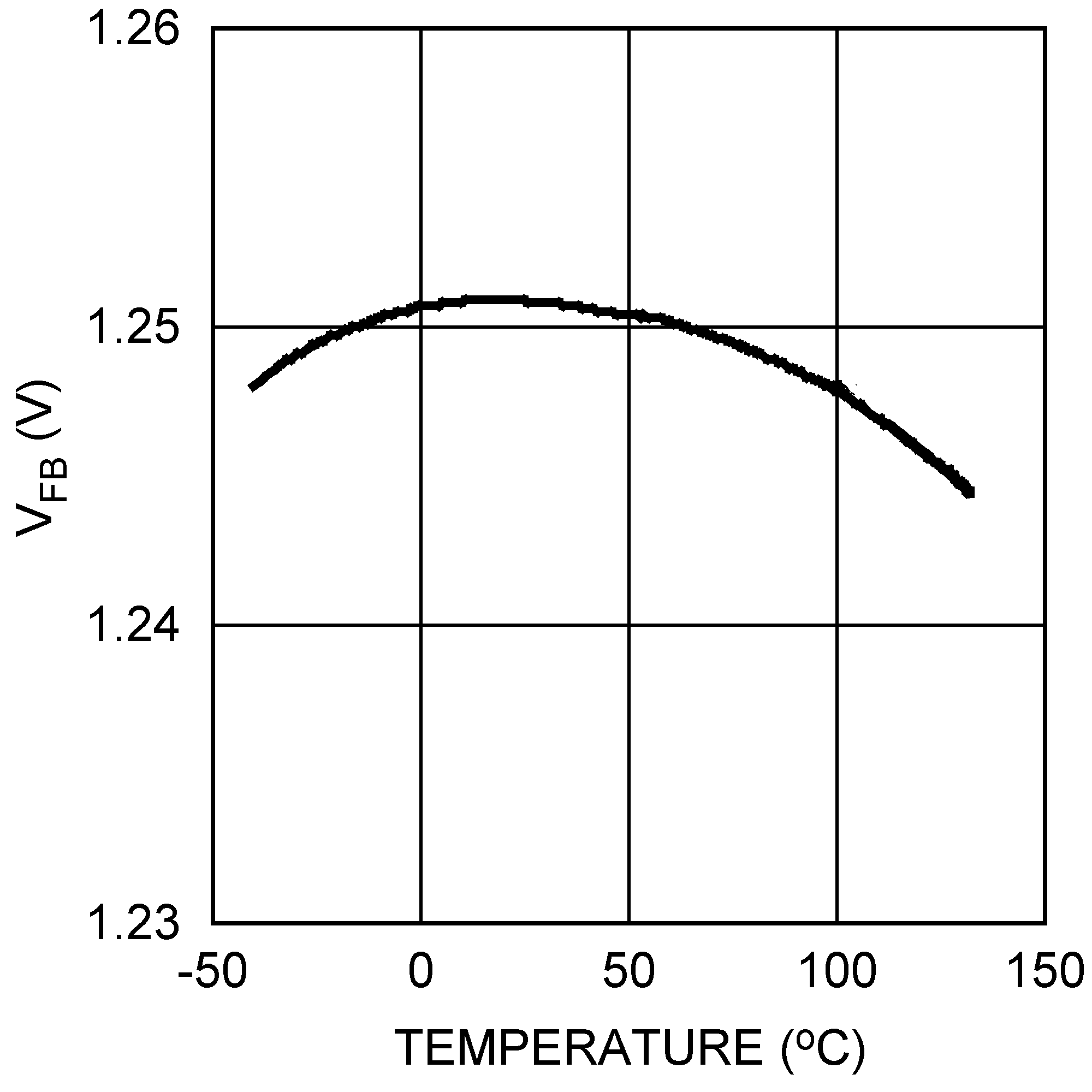

| VUVLO | Undervoltage threshold | 1.20 | 1.25 | 1.295 | V | ||

| IUVLO | Hysteresis current | UVLO pin sinking | 17 | 22 | 26 | µA | |

| Undervoltage shutdown threshold | UVLO voltage rising | 0.35 | 0.45 | 0.6 | V | ||

| Hysteresis | 0.1 | V | |||||

| CURRENT SENSE INPUT (CS PIN) | |||||||

| VCS | Current limit threshold | 0.22 | 0.255 | 0.29 | V | ||

| CS delay to output | CS from 0 V to 1 V. Time for OUTA and OUTB to fall to 90% of VCC. Output load = 0 pF. | 27 | ns | ||||

| Leading edge blanking time at CS | 65 | ns | |||||

| CS sink impedance (clocked) | Internal FET sink impedance | 21 | 45 | Ω | |||

| CURRENT LIMIT RESTART (RES PIN) | |||||||

| VRES | RES threshold | 1.9 | 2 | 2.2 | V | ||

| Charge source current | VRES = 1.5 V | 14 | 18 | 21 | µA | ||

| Discharge sink current | VRES = 1 V | 5 | 8 | 11 | µA | ||

| SOFT-START (SS PIN) | |||||||

| ISS | Charging current in normal operation | VSS = 0 | 70 | 100 | 130 | µA | |

| Charging current during a hiccup mode restart | VSS = 0 | 0.6 | 1 | 1.4 | µA | ||

| Soft-stop current sink | VSS = 2 V | 70 | 100 | 130 | µA | ||

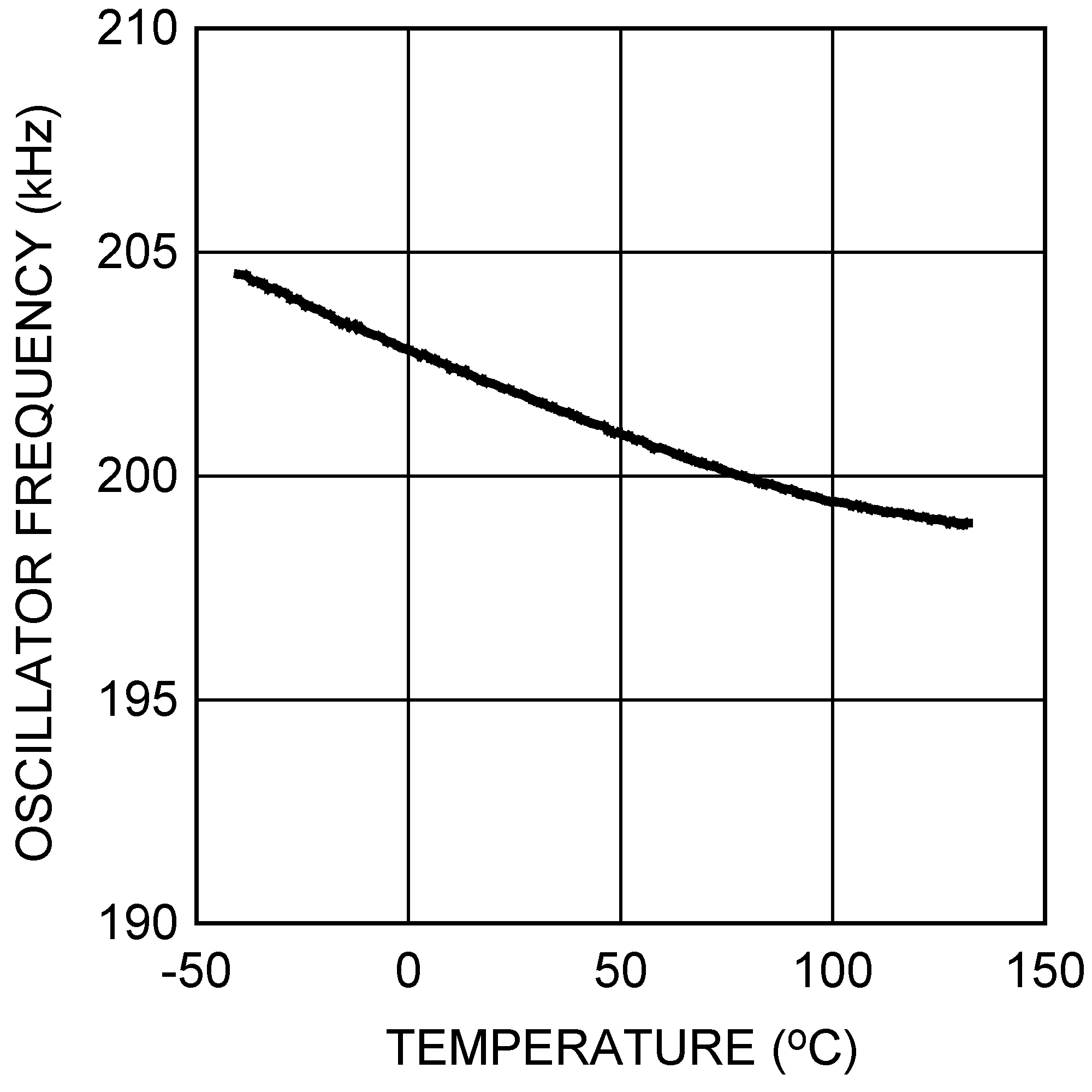

| OSCILLATOR (RT1 AND RT2 PINS) | |||||||

| DT1 | Dead-time 1 | RRT2 = 15 kΩ | 40 | 75 | 105 | ns | |

| DT2 | Dead-time 2 | RRT2 = 50 kΩ | 250 | ns | |||

| FSW1 | Frequency 1 (at OUTA, half oscillator frequency) | RRT1 = 30.1 kΩ, RRT2 = 30.1 kΩ, | 178 | 200 | 222 | kHz | |

| FSW2 | Frequency 2 (at OUTA, half oscillator frequency) | RRT1 = 11 kΩ, RRT2 = 30.1 kΩ, | 448 | 515 | 578 | kHz | |

| DC level | 2 | V | |||||

| Input sync threshold | 2.5 | 3 | 3.4 | V | |||

| PWM CONTROLLER (COMP PIN) | |||||||

| Delay to output | 65 | ns | |||||

| VPWM-OS | SS to RAMP offset | 0.7 | 1 | 1.2 | V | ||

| Minimum duty cycle | VSS = 0 V | TJ = 25°C | 0% | ||||

| COMP open-circuit voltage | VFB = 0 V | 4.5 | 4.75 | 5 | V | ||

| COMP short-circuit current | VFB = 0 V, COMP = 0 V | 0.5 | 1 | 1.5 | mA | ||

| VOLTAGE FEED-FORWARD (RAMP PIN) | |||||||

| RAMP sink impedance (clocked) | 5 | 20 | Ω | ||||

| ERROR AMPLIFIER | |||||||

| GBW | Gain bandwidth | 4 | MHz | ||||

| DC gain | 75 | dB | |||||

| Input voltage | VFB = COMP | 1.22 | 1.245 | 1.27 | V | ||

| COMP sink capability | VFB = 1.5 V COMP = 1 V | TJ = 25°C | 5 | 13 | mA | ||

| FB bias current | 10 | nA | |||||

| MAIN OUTPUT DRIVERS (OUTA and OUTB Pins) | |||||||

| Output high voltage | IOUT = 50 mA, (source) | Vcc-0.5 | Vcc-0.25 | V | |||

| Output low voltage | IOUT = 100 mA (sink) | 0.2 | 0.5 | V | |||

| Rise time | CLOAD = 1 nF | 17 | ns | ||||

| Fall time | CLOAD = 1 nF | 18 | ns | ||||

| Peak source current | VVCC = 10 V | 1.2 | A | ||||

| Peak sink current | VVCC = 10 V | 1.2 | A | ||||

| THERMAL SHUTDOWN | |||||||

| TSD | Thermal shutdown threshold | 165 | °C | ||||

| Thermal shutdown hysteresis | 25 | °C | |||||

6.7 Typical Characteristics