SBOS477B December 2011 – December 2016 OPA1652 , OPA1654

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Detailed Description

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

Thermal pad, mechanical data (Package|Pins)

- DRG|8

Orderable Information

1 Features

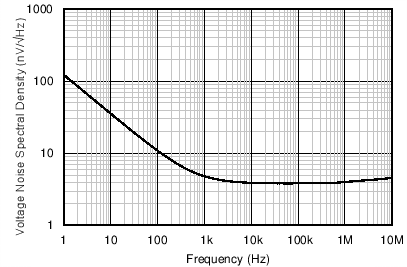

- Low Noise:

4.5 nV/√Hz at 1 kHz

3.8 nV/√Hz at 10 kHz - Low Distortion: 0.00005% at 1 kHz

- Low Quiescent Current:

2 mA per Channel - Low Input Bias Current: 10 pA

- Slew Rate: 10 V/μs

- Wide Gain Bandwidth: 18 MHz (G = 1)

- Unity-Gain Stable

- Rail-to-Rail Output

- Wide Supply Range:

±2.25 V to ±18 V, or 4.5 V to 36 V - Dual and Quad Versions Available

- Small Package Sizes:

Dual: SO-8 and MSOP-8

Quad: SO-14 and TSSOP-14

2 Applications

- Analog and Digital Mixers

- Audio Effects Processors

- Musical Instruments

- A/V Receivers

- DVD and Blu-Ray™ Players

- Car Audio Systems

3 Description

The OPA1652 (dual) and OPA1654 (quad) FET-input operational amplifiers achieve a low 4.5-nV/√Hz noise density with an ultra-low distortion of 0.00005% at 1 kHz. The OPA1652 and OPA1654 op amps offer rail-to-rail output swing to within 800 mV with a 2-kΩ load, which increases headroom and maximizes dynamic range. These devices also have a high output drive capability of ±30 mA.

These devices operate over a very-wide-supply range of ±2.25 V to ±18 V, or 4.5 V to 36 V, on only 2 mA of supply current per channel. The OPA1652 and OPA1654 op amps are unity-gain stable and provide excellent dynamic behavior over a wide range of load conditions.

These devices also feature completely independent circuitry for lowest crosstalk and freedom from interactions between channels, even when overdriven or overloaded.

The OPA1652 and OPA1654 temperature ranges are specified from –40°C to +85°C.

Device Information(1)

| PART NUMBER | PACKAGE | BODY SIZE (NOM) |

|---|---|---|

| OPA1652 | SOIC (8) | 4.90 mm × 3.91 mm |

| VSSOP (8) | 3.00 mm × 3.00 mm | |

| WSON (8) | 3.00 mm × 3.00 mm | |

| OPA1654 | SOIC (14) | 8.65 mm × 3.91 mm |

| TSSOP (14) | 5.00 mm × 4.40 mm |

- For all available packages, see the orderable addendum at the end of the data sheet.

Input Voltage Noise Spectral Density