-

SN74ACT564 Octal D-Type Edge-Triggered Flip-Flops with 3-State Outputs

Package Options

Refer to the PDF data sheet for device specific package drawings

Mechanical Data (Package|Pins)

- NS|20

- N|20

- DW|20

- PW|20

Thermal pad, mechanical data (Package|Pins)

Orderable Information

SN74ACT564 Octal D-Type Edge-Triggered Flip-Flops with 3-State Outputs

1 Features

- Operation of 4.5V to 5.5V VCC

- Inputs accept voltages to 5.5V

- Max tpd of 8.5ns at 5V

- Inputs are TTL-voltage compatible

- 3-state inverted outputs drive bus lines directly

- Flow-through architecture to optimize PCB layout

- Full parallel access for loading

2 Description

The ’ACT564 devices are octal D-type edge-triggered flip-flops that feature 3-state outputs designed specifically for driving highly capacitive or relatively low-impedance loads. They are particularly suitable for implementing buffer registers, I/O ports, bidirectional bus drivers, and working registers.

Package

Information

| PART NUMBER | PACKAGE(1) | PACKAGE SIZE(2) | BODY SIZE(3) |

|---|---|---|---|

| SN74ACT564 | DW ( SOIC, 20) | 12.8mm × 10.3mm | 12.8mm × 7.5mm |

| N (PDIP, 20) | 24.33mm × 9.4mm | 24.33mm × 6.35mm | |

| NS (SOP, 20) | 12.6mm × 7.8mm | 12.6mm × 5.3mm | |

| PW (TSSOP, 20) | 6.5mm × 6.4mm | 6.5mm × 4.4mm |

(1) For more information, see Section

10.

(2) The package size (length × width) is a

nominal value and includes pins, where applicable.

(3) The body size (length × width) is a

nominal value and does not include pins.

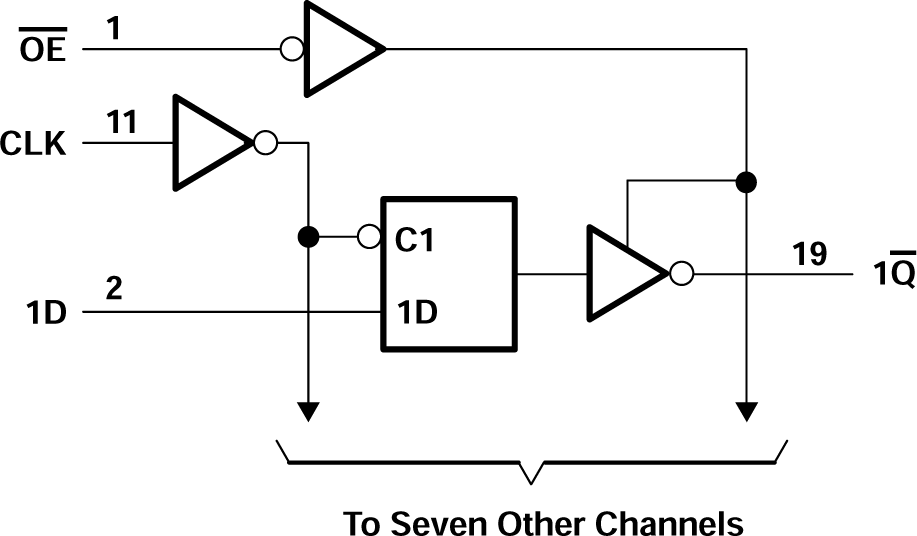

Logic Diagram (Positive

Logic)

Logic Diagram (Positive

Logic)3 Pin Configuration and Functions

Figure 3-1 SN74ACT564 DB, DW, N, NS,

or PW Package (Top View)

Figure 3-1 SN74ACT564 DB, DW, N, NS,

or PW Package (Top View)Table 3-1 Pin Functions

| PIN | TYPE | Description | ||

|---|---|---|---|---|

| NO. | NAME | |||

| 1 | OE | I | Clear all channels, active low | |

| 2 | 1D | I | Channel 1, D input | |

| 3 | 2D | I | Channel 2, D input | |

| 4 | 3D | I | Channel 3, D input | |

| 5 | 4D | I | Channel 4, D input | |

| 6 | 5D | I | Channel 5, D input | |

| 7 | 6D | I | Channel 6, D input | |

| 8 | 7D | I | Channel 7, D input | |

| 9 | 8D | I | Channel 8, D input | |

| 10 | GND | — | Ground | |

| 11 | CLK | I | Clock Pin | |

| 12 | 8Q | O | Channel 8, Q output | |

| 13 | 7Q | O | Channel 7, Q output | |

| 14 | 6Q | O | Channel 6, Q output | |

| 15 | 5Q | O | Channel 5, Q output | |

| 16 | 4Q | O | Channel 4, Q output | |

| 17 | 3Q | O | Channel 3, Q output | |

| 18 | 2Q | O | Channel 2, Q output | |

| 19 | 1Q | O | Channel 1, Q output | |

| 20 | VCC | — | Power Pin | |