-

SNx4HC241 Octal Buffers and Line Drivers With 3-State Outputs

Package Options

Refer to the PDF data sheet for device specific package drawings

Mechanical Data (Package|Pins)

- NS|20

- N|20

- DW|20

- PW|20

Thermal pad, mechanical data (Package|Pins)

Orderable Information

SNx4HC241 Octal Buffers and Line Drivers With 3-State Outputs

1 Features

- Wide operating voltage range of 2 V to 6 V

- High-current outputs drive up to 15 LSTTL loads

- Low power consumption, 80-μA max ICC

- Typical tpd =11 ns

- ±6-mA output drive at 5 V

- Low input current of 1 μA max

- 3-state outputs drive bus lines or buffer memory address registers

2 Description

These octal buffers and line drivers are designed specifically to improve both the performance and density of 3-state memory address drivers, clock drivers, and bus-oriented receivers and transmitters. The ’HC241 devices are organized as two 4-bit buffers/drivers with separate output-enable (1OE and 2OE) inputs. When 1OE is low or 2OE is high, the device passes noninverted data from the A inputs to the Y outputs. When 1OE is high or 2OE is low, the outputs for the respective buffers/drivers are in the high-impedance state.

| PART NUMBER | PACKAGE(1) | BODY SIZE (NOM) |

|---|---|---|

| SN74HC241DW | SOIC (20) | 12.80 mm × 7.50 mm |

| SN74HC241N | PDIP (20) | 25.40 mm × 6.35 mm |

| SN74HC241NSR | SO (20) | 15.00 mm × 5.30 mm |

| SN74HC241PW | TSSOP (20) | 6.50 mm × 4.40 mm |

| SN54HC241J | CDIP (20) | 26.92 mm × 6.92 mm |

| SNJ54HC241FK | LCCC (20) | 8.89 mm × 8.45 mm |

Functional Block Diagram

Functional Block Diagram3 Revision History

Changes from Revision D (January 2022) to Revision E (May 2022)

- Junction-to-ambient thermal resistance values increased. DW was 58 is now 109.1, N was 69 is now 84.6, NS was 60 is now 113.4, PW was 83 is now 131.8Go

Changes from Revision C (August 2003) to Revision D (January 2022)

- Updated the numbering, formatting, tables, figures, and cross-references throughout the document to reflect modern data sheet standardsGo

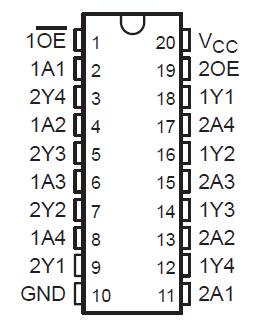

4 Pin Configuration and Functions

J, DW, N, NS, or PW

package

J, DW, N, NS, or PW

package20-Pin CDIP, SOIC, PDIP, SO, or TSSOP

Top View

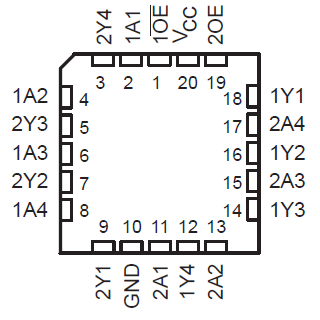

FK Package

FK Package20-Pin LCCC

Top View