-

TPS51604 Synchronous Buck FET Driver for High-Frequency CPU Core Power

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Detailed Description

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

- IMPORTANT NOTICE

Package Options

Mechanical Data (Package|Pins)

- DSG|8

Thermal pad, mechanical data (Package|Pins)

- DSG|8

Orderable Information

TPS51604 Synchronous Buck FET Driver for High-Frequency CPU Core Power

1 Features

- Reduced Dead-Time Drive Circuit for Optimized CCM

- Automatic Zero Crossing Detection for Optimized DCM Efficiency

- Multiple Low-Power Modes for Optimized Light-Load Efficiency

- Optimized Signal Path Delays for High-Frequency Operation

- Integrated BST Switch Drive Strength Optimized for Ultrabook FETs

- Optimized for 5-V FET Drive

- Conversion Input Voltage Range (VIN): 4.5 to 28 V

- 2-mm × 2-mm, 8-Pin, WSON Thermal Pad Package

2 Applications

- Tablets Using High-Frequency CPUs With the Following Power Input:

- Adapter

- Battery

- NVDC

- 5-V or 12-V Rails

3 Description

The TPS51604 drivers are optimized for high-frequency CPU VCORE applications. Advanced features such as reduced dead-time drive and auto zero crossing are used to optimize efficiency over the entire load range.

The SKIP pin provides the option of CCM operation to support controlled management of the output voltage. In addition, the TPS51604 supports two low-power modes. With the PWM input in tri-state, quiescent current is reduced to 130 µA, with immediate response. When SKIP is held at tri-state, the current is reduced to 8 µA (typically 20 µs is required to resume switching). Paired with the appropriate TI controller, the drivers deliver an exceptionally high performance power supply system.

The TPS51604 device is packaged in a space saving, thermally-enhanced 8-pin, 2-mm x 2-mm WSON package and operates from –40°C to 105°C.

Device Information(1)

| PART NUMBER | PACKAGE | BODY SIZE (NOM) |

|---|---|---|

| TPS51604 | WSON (8) | 2.00 mm × 2.00 mm |

- For all available packages, see the orderable addendum at the end of the data sheet.

Simplified Schematic

4 Revision History

Changes from A Revision (August 2013) to B Revision

- Added ESD Ratings table, Feature Description section, Device Functional Modes section, Application and Implementation section, Power Supply Recommendations section, Layout section, Device and Documentation Support section, and Mechanical, Packaging, and Orderable Information section Go

5 Pin Configuration and Functions

Pin Functions

| PIN | I/O(1) | DESCRIPTION | |

|---|---|---|---|

| NAME | NO. | ||

| BST | 1 | I | High-side N-channel FET bootstrap voltage input; power supply for high-side driver |

| DRVH | 8 | O | High-side N-channel gate drive output |

| DRVL | 5 | O | Synchronous low-side N-channel gate drive output |

| GND | 6 | G | Synchronous low-side N-channel gate drive return and device reference |

| PWM | 2 | I | PWM input. A tri-state voltage on this pin turns off both the high-side (DRVH) and low-side drivers (DRVL) |

| SKIP | 3 | I | When SKIP is LO, the zero crossing comparator is active. The power chain enters discontinuous conduction mode when the inductor current reaches zero. When SKIP is HI, the zero crossing comparator is disabled, and the driver outputs follow the PWM input. A tri-state voltage on SKIP puts the driver into a very-low power state. |

| SW | 7 | I/O | High-side N-channel gate drive return. Also, zero-crossing sense input |

| VDD | 4 | I | 5-V power supply input; decouple to GND with a ceramic capacitor with a value of 1 µF or greater |

| Thermal Pad | G | Tie to system GND plane with multiple vias | |

6 Specifications

6.1 Absolute Maximum Ratings(1) (2)

over operating free-air temperature (unless otherwise noted)| MIN | MAX | UNIT | ||

|---|---|---|---|---|

| Input voltage | VDD | –0.3 | 6 | V |

| PWM, SKIP | –0.3 | 6 | ||

| Output voltage | BST | –0.3 | 35 | V |

| BST (transient <20 ns) | –0.3 | 38 | ||

| BST to SW; DRVH to SW | –0.3 | 6 | ||

| SW | –2 | 30 | ||

| DRVH, SW (transient <20 ns) | –5 | 38 | ||

| DRVL | –0.3 | 6 | ||

| Ground pins | GND to PAD | –0.3 | 0.3 | V |

| Operating junction temperature, TJ | –40 | 125 | °C | |

| Storage temperature range, Tstg | –55 | 150 | °C | |

6.2 ESD Ratings

| VALUE | UNIT | |||

|---|---|---|---|---|

| V(ESD) | Electrostatic discharge | Human body model (HBM), per AEC Q100-002(1) | ±2000 | V |

| Charged device model (CDM), per AEC Q100-011 | ±750 | |||

6.3 Recommended Operating Conditions

Over operating free-air temperature range (unless otherwise noted)| MIN | NOM | MAX | UNIT | ||

|---|---|---|---|---|---|

| Input voltage | VDD | 4.5 | 5 | 5.5 | V |

| PWM, SKIP | –0.1 | 5.5 | |||

| Output voltage | BST | –0.1 | 34 | V | |

| BST to SW; DRVH to SW | –0.1 | 5.5 | |||

| SW | –1 | 28 | |||

| DRVL | –0.1 | 5.5 | |||

| Ground pins | GND to PAD | –0.1 | 0.1 | V | |

| Operating junction temperature, TJ | –40 | 105 | °C | ||

6.4 Thermal Information

| THERMAL METRIC(1) | TPS51604 | UNIT | |

|---|---|---|---|

| WSON (DSG) | |||

| 8 PINS | |||

| RθJA | Junction-to-ambient thermal resistance | 63.1 | °C/W |

| RθJC(top) | Junction-to-case (top) thermal resistance | 74.1 | °C/W |

| RθJB | Junction-to-board thermal resistance | 34.3 | °C/W |

| ψJT | Junction-to-top characterization parameter | 2.0 | °C/W |

| ψJB | Junction-to-board characterization parameter | 34.9 | °C/W |

| RθJC(bot) | Junction-to-case (bottom) thermal resistance | 11.7 | °C/W |

6.5 Electrical Characteristics

These specifications apply for –40°C ≤ TJ ≤ 105°C, and VVDD = 5 V unless otherwise specified.| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| VDD INPUT SUPPLY | ||||||

| ICC | Supply current (operating) | VSKIP = VVDD or VSKIP = 0 V, PWM = High |

160 | 600 | µA | |

| VSKIP = VVDD or VSKIP = 0 V, PWM = Low |

250 | |||||

| VSKIP = VVDD or VSKIP = 0 V, PWM = Float |

130 | |||||

| VSKIP = Float | 8 | |||||

| VDD UNDERVOLTAGE LOCKOUT (UVLO) | ||||||

| VUVLO | UVLO threshold | Rising threshold | 4.15 | V | ||

| Falling threshold | 3.7 | |||||

| VUVHYS | UVLO hysteresis | 0.2 | V | |||

| PWM AND SKIP I/O SPECIFICATIONS | ||||||

| RI | Input impedance | Pullup to VDD | 1.7 | MΩ | ||

| Pulldown (to GND) | 800 | kΩ | ||||

| VIL | Low-level input voltage | 0.6 | V | |||

| VIH | High-level input voltage | 2.65 | V | |||

| VIHH | Hysteresis | 0.2 | V | |||

| VTS | Tri-state voltage | 1.3 | 2.0 | V | ||

| tTHOLD(off1) | Tri-state activation time (falling) PWM | 60 | ns | |||

| tTHOLD(off2) | Tri-state activation time (rising) PWM | 60 | ns | |||

| tTSKF | Tri-state activation time (falling) SKIP | 1 | µs | |||

| tTSKR | Tri-state activation time (rising) SKIP | 1 | µs | |||

| t3RD(PWM) | Tri-state exit time PWM | 100 | ns | |||

| t3RD(SKIP) | Tri-state exit time SKIP | 50 | µs | |||

| HIGH-SIDE GATE DRIVER (DRVH) | ||||||

| tR(DRVH) | Rise time | DRVH rising, CDRVH = 3.3 nF; 20% to 80% | 30 | ns | ||

| tRPD(DRVH) | Rise time propogation delay | CDRVH = 3.3 nF | 40 | ns | ||

| RSRC | Source resistance | Source resistance, (VBST– VSW) = 5 V, high state, (VBST – VDRVH) = 0.1 V |

4 | 8 | Ω | |

| tF(DRVH) | Fall time | DRVH falling, CDRVH = 3.3 nF | 8 | ns | ||

| tFPD(DRVH) | Fall-time propagation delay | CDRVH = 3.3 nF | 25 | ns | ||

| RSNK | Sink resistance | Sink resistance, (VBST – VSW) forced to 5 V, low state (VDRVH – VSW) = 0.1 V |

0.5 | 1.6 | Ω | |

| RDRVH | DRVH to SW resistance(1) | 100 | kΩ | |||

| LOW-SIDE GATE DRIVER (DRVL) | ||||||

| tR(DRVL) | Rise time | DRVL rising, CDRVL = 3.3 nF; 20% to 80% | 15 | ns | ||

| tRPD(DRVL) | Rise time propagation delay | CDRVL = 3.3 nF | 35 | ns | ||

| RSRC | Source resistance | Source resistance, (VVDD–GND) = 5 V, high state, (VVDD – VDRVL) = 0.1 V |

1.5 | 3 | Ω | |

| tF(DRVL) | Fall time | DRVL falling, CDRVL = 3.3 nF | 10 | ns | ||

| tFPD(DRVL) | Fall-time propagation delay | CDRVL= 3.3 nF | 15 | ns | ||

| RSNK | Sink resistance | Sink resistance, (VVDD– GND) = 5 V, low state, (VDRVL – GND) = 0.1 V |

0.4 | 1.6 | Ω | |

| RDRVL | DRVL to GND resistance(1) | 100 | kΩ | |||

| GATE DRIVER DEAD-TIME | ||||||

| tR(DT) | Rising edge | 0 | 20 | 35 | ns | |

| tF(DT) | Falling edge | 0 | 10 | 25 | ns | |

| ZERO CROSSING COMPARATOR | ||||||

| VZX | Zero crossing offset | SW voltage rising | –2.25 | 0 | 2.00 | mV |

| BOOTSTRAP SWITCH | ||||||

| VFBST | Forward voltage | IF = 10 mA | 120 | 240 | mV | |

| IRLEAK | Reverse leakage | (VBST – VVDD) = 25 V | 2 | µA | ||

| RDS(on) | On-resistance | 12 | 24 | Ω | ||

6.6 Typical Characteristics

| VIN = 8 V | ||

| VIN = 20 V | ||

6.7 Typical Power Block MOSFET Characteristics

Power block MOSFET: CSD87330, Inductor: 0.22 µF, 1.1-mΩ DCR

| FCCM | VOUT = 1.8 V |

| VIN = 7.4 V | fSW = 800 kHz |

| Skip Mode | VOUT = 1.8 V |

| VIN = 7.4 V | fSW = 800 kHz |

7 Detailed Description

7.1 Overview

The TPS51604 device is a synchronous-buck MOSFET driver designed to drive both high-side and low-side MOSFETs. It allows high-frequency operation with current driving capability matched to the application. The integrated boost switch is internal. The TPS51604 device employs dead-time reduction control and shoot-through protection, which helps avoid simultaneous conduction of high-side and low-side MOSFETs. Also, the drivers improve light-load efficiency with integrated DCM-mode operation using adaptive crossing detection. Typical applications yield a steady-state duty cycle of 60% or less. For high steady-state duty cycle applications, including a small external Schottky diode may help to ensure sufficient charging of the bootstrap capacitor.

7.2 Functional Block Diagram

7.3 Feature Description

7.3.1 UVLO Protection

The UVLO comparator evaluates the VDD voltage level. As VVDD rises, both DRVH and DRVL hold actively low at all times until VVDD reaches the higher UVLO threshold (VUVLO_H). Then, the driver becomes operational and responds to PWM and SKIP commands. If VDD falls below the lower UVLO threshold (VUVLO_L = VUVLO_H – Hysteresis), the device disables the driver and drives the outputs of DRVH and DRVL actively low. Figure 15 shows this function.

CAUTION

Do not start the driver in the very low power mode (SKIP = Tri-state).

Figure 15. UVLO Operation

Figure 15. UVLO Operation

7.3.2 PWM Pin

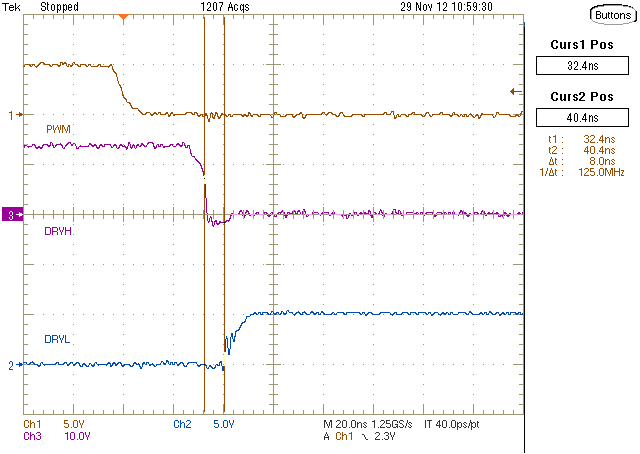

The PWM pin incorporates an input tri-state function. The device forces the gate driver outputs to low when PWM is driven into the tri-state window and the driver enters a low power state with zero exit latency. The pin incorporates a weak pullup to maintain the voltage within the tri-state window during low-power modes. Operation into and out of a tri-state condition follows the timing diagram outlined in Figure 16.

When VDD reaches the UVLO_H level, a tri-state voltage range (window) is set for the PWM input voltage. The window is defined as the PWM voltage range between PWM logic high (VIH) and logic low (VIL) thresholds. The device sets high-level input voltage and low-level input voltage threshold levels to accommodate both 3.3-V (typical) and 5-V (typical) PWM drive signals.

When the PWM exits the tri-state condition, the driver enters CCM for a period of 4 µs, regardless of the state of the SKIP pin. Typical operation requires this time period in order for the auto-zero comparator to resume.

Figure 16. PWM Tri-State Timing Diagram

Figure 16. PWM Tri-State Timing Diagram

7.3.3 SKIP Pin

The SKIP pin incorporates the input tri-state buffer as PWM. The function is somewhat different. When SKIP is low, the zero crossing (ZX) detection comparator is enabled, and DCM mode operation occurs if the load current is less than the critical current. When SKIP is high, the ZX comparator disables, and the converter enters FCCM mode. When the SKIP pin is in a tri-state condition, typical operation forces the gate driver outputs low and the driver enters a very-low-power state. In the low-power state, the UVLO comparator remains off to reduce quiescent current. When the SKIP pin voltage is pulled either low or high, the driver wakes up and is able to accept PWM pulses in less than 50 µs.

Table 1 shows the logic functions of UVLO, PWM, SKIP, DRVH, and DRVL.

Table 1. Logic Functions of the TPS51604

| UVLO | PWM | SKIP | DRVL | DRVH | MODE |

|---|---|---|---|---|---|

| Active | — | — | Low | Low | Disabled |

| Inactive | Low | Low | High(1) | Low | DCM(1) |

| Inactive | Low | High | High | Low | FCCM |

| Inactive | High | H or L | Low | High | |

| Inactive | Tri-state | H or L | Low | Low | Low power |

| Inactive | — | Tri-state | Low | Low | Very-low power |

7.3.3.1 Zero Crossing (ZX) Operation

The zero crossing comparator is adaptive for improved accuracy. As the output current decreases from a heavy load condition, the inductor current also reduces and eventually arrives at a valley, where it touches zero current, which is the boundary between continuous conduction and discontinuous conduction modes. The SW pin detects the zero-current condition. When this zero inductor current condition occurs, the ZX comparator turns off the rectifying MOSFET.

7.3.4 Adaptive Dead-Time Control and Shoot-Through Protection

The driver utilizes an anti-shoot-through and adaptive dead-time control to minimize low-side body diode conduction time and maintain high efficiency. When the PWM input voltage becomes high, the low-side MOSFET gate voltage begins to fall after a propagation delay. At the same time, DRVL voltage is sensed, and high-side driving voltage starts to increase after DRVL voltage is lower than a proper threshold.

Figure 17. Rise and Fall Timing and Propagation Delay Definitions

Figure 17. Rise and Fall Timing and Propagation Delay Definitions

Typical operation manages to near zero the dead-time between the low-side gate turn-off to high-side gate voltage turn-on, and high-side gate turn-off to low-side gate turn-on, in order to avoid simultaneous conduction of both MOSFETs, as well as to reduce body diode conduction and recovery losses. This operation also reduces ringing on the leading edge of the SW waveform.

Figure 18. Dead-Time Definitions

Figure 18. Dead-Time Definitions

7.3.5 Integrated Boost-Switch

To maintain a BST-SW voltage close to VDD (to get lower conduction losses on the high-side FET), the conventional diode between the VDD pin and BST pin is replaced by a FET, which is gated by the DRVL signal.

7.4 Device Functional Modes

The TPS51604 device operates in CCM mode when the SKIP pin is high, and it enters DCM mode when the SKIP pin is low. When both the SKIP pin and the PWM pin are in a tri-state condition, it forces the gate driver outputs low and the driver enters a very-low-power state.