**TPSM82866C** JAJSSQ9 - JUNE 2024

# TPSM8286xx 2.4V~5.5V 入力、4A/6A、降圧 MagPack™ パワー モジュール、イ ンダクタ内蔵、I<sup>2</sup>C インターフェイス搭載

# 1 特長

- 最大 96% の効率

- 優れた放熱対策

- I<sup>2</sup>C 互換インターフェイス:最高 3.4Mbps

- 出力電圧精度:1%

- DCS-Controlトポロジにより、高速過渡応答を実現

- I<sup>2</sup>C プログラマブル:

- 出力電圧

- 0.4~1.675V (5mV 刻み)

- 0.8~3.35V (10mV 刻み)

- 強制 PWM またはパワー セーブ モード

- 出力電圧放電

- I<sup>2</sup>C デバイス ステータス読み戻し:

- 過熱警告

- ヒカップ電流制限

- Vin が UVLO 未満

- 抵抗を選択可能:

- I<sup>2</sup>C アドレス

- 16 のスタートアップ出力電圧オプション

- 低 EMI 要件に対して最適化

- ボンドワイヤパッケージなし

- MagPack テクノロジーはインダクタと IC をシール

- 最適化されたピン配置によるレイアウトの簡素化

- 動作時の静止電流 4µA

- -40°C~125°Cの動作温度範囲

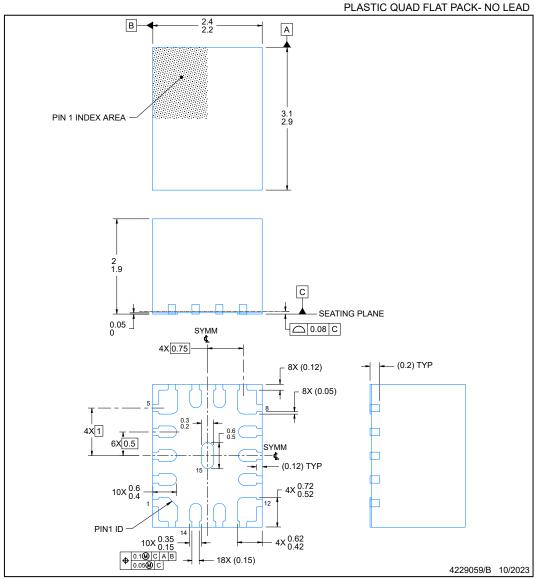

- 2.3mm × 3.0mm × 1.95mm の QFN パッケージ

- 28mm<sup>2</sup> の設計サイズ

- $I^2C$  インターフェイスなしでも供給可能:TPSM82866A

# 2 アプリケーション

- FPGA、CPU、ASIC のコア電源

- 光モジュール

- 医療用画像処理

- ファクトリ オートメーション / 制御

- 航空宇宙および防衛

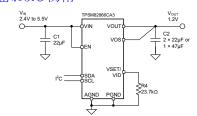

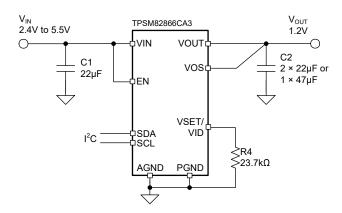

代表的なアプリケーション回路図

# 3 概要

TPSM8286xx デバイス ファミリは、小さいソリューション サイズと高い効率を実現できるように設計された 4A およ び 6A 降圧コンバータ パワー モジュールで構成されてい ます。このパワー モジュールにはテキサス・インスツルメン ツの MagPack テクノロジーを使用して同期整流降圧コン バータとインダクタが組み込まれているため、設計の簡素 化、外付け部品の低減、PCB 面積の削減が可能です。コ ンパクトな設計なので、標準的な表面実装機による自動組 み立てに適しています。 DCS-Control アーキテクチャと優 れた負荷過渡性能を活用して、小さな出力コンデンサで も、厳密な出力電圧精度を実現しています。中負荷から重 負荷では PWM モードで動作し、軽負荷時には自動的に 省電力モードへ移行するため、負荷電流の全範囲にわた って高効率が維持されます。このデバイスは、強制的に PWM モードで動作させて、出力電圧リップルを最小化す ることもできます。I<sup>2</sup>C インターフェイスにより、出力電圧の 調整、新しい設定ポイントへの遷移時の Vour ランプ レー トの設定、熱警告や電流制限フラグなどのステータス情報 の読み出しの効果的な方法が提供されます。内蔵のソフト スタートにより、入力電源からの突入電流が減少します。 過熱保護およびヒカップ短絡保護機能により、堅牢で信頼 性の高い設計を実現できます。

| 部品番号 <sup>(3)</sup>        | 出力電流 | パッケージ(1)   | 本体サイズ<br>(公称) |  |  |  |  |

|----------------------------|------|------------|---------------|--|--|--|--|

| TPSM82864xx <sup>(2)</sup> | 4A   | RCF (QFN-  | 2.30mm ×      |  |  |  |  |

| TPSM82866xx                | 6A   | FCMOD, 15) | 3.00mm        |  |  |  |  |

- 詳細については、セクション 12 を参照してください。 (1)

- プレビュー情報 (事前情報ではありません)。

- 「デバイスのオプション」表を参照してください。

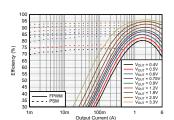

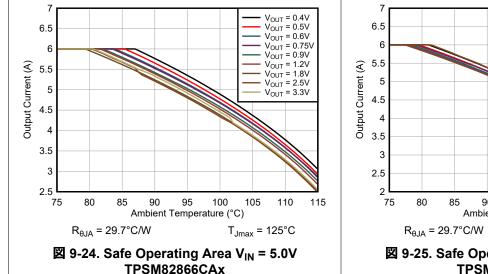

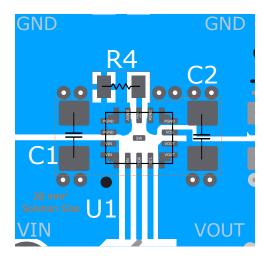

TPSM82866C の効率 (V<sub>IN</sub> = 5.0V)

# **Table of Contents**

| 1 特長                                                  | 8.2 Register Address Byte             | 19              |

|-------------------------------------------------------|---------------------------------------|-----------------|

| 2 アプリケーション                                            |                                       | 19              |

| 3 概要                                                  |                                       | <mark>20</mark> |

| 4 Device Options                                      | 0 F OONTDOL D:!-4                     | 21              |

| 5 Pin Configuration and Functions                     |                                       | 21              |

| 6 Specifications                                      | 0 A modication and localous autation  | 22              |

| 6.1 Absolute Maximum Ratings                          | O 4 A l' t' l. f t'                   | <mark>22</mark> |

| 6.2 ESD Ratings                                       |                                       | 22              |

| 6.3 Recommended Operating Conditions                  |                                       | <mark>28</mark> |

| 6.4 Thermal Information                               | <sub>5</sub> 9.4 Layout               |                 |

| 6.5 Electrical Characteristics                        | 6 10 Device and Documentation Support |                 |

| 6.6 I <sup>2</sup> C Interface Timing Characteristics | 7 10.1 Device Support                 | 31              |

| 6.7 Typical Characteristics                           |                                       | 31              |

| 7 Detailed Description1                               |                                       | 31              |

| 7.1 Overview1                                         |                                       | 31              |

| 7.2 Functional Block Diagram1                         |                                       | 31              |

| 7.3 Feature Description1                              |                                       | 31              |

| 7.4 Device Functional Modes1                          |                                       | 31              |

| 7.5 Programming1                                      |                                       |                 |

| 8 Register Map1                                       |                                       |                 |

| 8.1 Target Address Byte1                              | 9 Information                         | 32              |

# **4 Device Options**

| ORDERABLE PART NUMBER(1)         | OUTPUT CURRENT | OPERATING<br>FREQUENCY | OUTPUT VOLTAGE<br>RANGE | DEVICE HEIGHT |

|----------------------------------|----------------|------------------------|-------------------------|---------------|

| TPSM82864CA2PRCFR <sup>(2)</sup> | 4A             |                        | 0.4V - 1.675V           |               |

| TPSM82864CA3PRCFR <sup>(2)</sup> | 44             | 2 4MHz                 | 0.8V - 3.35V            | 1.95mm        |

| TPSM82866CA2PRCFR <sup>(2)</sup> | 6A             | 2.4WITZ                | 0.4V - 1.675V           | 1.9511111     |

| TPSM82866CA3PRCFR                | OA .           |                        | 0.8V - 3.35V            |               |

- (1) For more information see セクション 12.

- (2) Preview information (not Advance Information).

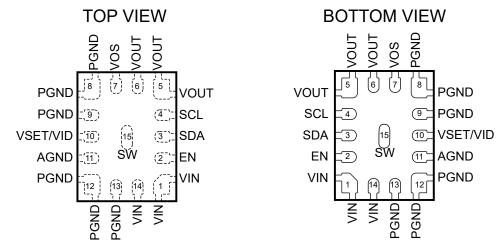

# **5 Pin Configuration and Functions**

図 5-1. TPSM82864x, TPSM82866x - RCF (15 Pin) QFN-FCMOD

### 表 5-1. Pin Functions

| PIN                                                                                    |              | TYPE(1)                                                                                | DESCRIPTION                                                                                                                                                                                                                                                                                                            |

|----------------------------------------------------------------------------------------|--------------|----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                                                                                   | RCF          | ITPE                                                                                   | DESCRIPTION                                                                                                                                                                                                                                                                                                            |

| AGND                                                                                   | 11           | Р                                                                                      | Analog ground pin. Must be connected to a common GND plane.                                                                                                                                                                                                                                                            |

| EN                                                                                     | 2            | I                                                                                      | Device enable pin. To enable the device, this pin must be pulled high. Pulling this pin low disables the device. Do not leave floating.                                                                                                                                                                                |

| SDA                                                                                    | 3            | I/O                                                                                    | I <sup>2</sup> C serial data pin. Do not leave floating. Connect a pullup resistor to a logic high level. If the I <sup>2</sup> C interface is not used, connect the pin to GND.                                                                                                                                       |

| SCL                                                                                    | 4            | I                                                                                      | I <sup>2</sup> C serial clock pin. Do not leave this pin floating. Connect a pullup resistor to a logic high level. If the I <sup>2</sup> C interface is not used, connect the pin to GND.                                                                                                                             |

| VSET/VID                                                                               | 10           | I                                                                                      | Connecting a resistor to GND selects one of the Start-up output voltages and I <sup>2</sup> C device address. After start-up, the pin can be used to switch between the $V_{OUT}$ registers for the output voltage selection. (Low = $V_{OUT}$ Register 1; High = $V_{OUT}$ Register 2). See $20.4$ 7.4.3 for details. |

| PGND                                                                                   | 8, 9, 12, 13 | Р                                                                                      | Power ground pin. Must be connected to common GND plane.                                                                                                                                                                                                                                                               |

| SW                                                                                     | 15           | 0                                                                                      | Switch pin of the power stage. This pin can be left floating.                                                                                                                                                                                                                                                          |

| VIN 1, 14 P Power                                                                      |              | Р                                                                                      | Power supply input voltage pin                                                                                                                                                                                                                                                                                         |

| VOS 7 I Output voltage sense pin. This pin must be directly connected to the output of |              | Output voltage sense pin. This pin must be directly connected to the output capacitor. |                                                                                                                                                                                                                                                                                                                        |

| VOUT 5, 6                                                                              |              | Р                                                                                      | Output voltage pin                                                                                                                                                                                                                                                                                                     |

(1) I = Input, O = Output, P = Power

# 6 Specifications

# 6.1 Absolute Maximum Ratings

Over operating free-air temperature range (unless otherwise noted) (1)

|                           |                                        | MIN  | MAX                   | UNIT |

|---------------------------|----------------------------------------|------|-----------------------|------|

|                           | VIN, EN, VOS, FB, PG, VSET/VID         | -0.3 | 6                     |      |

| Voltage <sup>(2)</sup>    | SW (DC), VOUT                          | -0.3 | V <sub>IN</sub> + 0.3 | V    |

|                           | SW (AC, less than 10ns) <sup>(3)</sup> | -2.5 | 10                    |      |

| I <sub>SINK_SDA_SCL</sub> | Sink current at SDA, SCL               |      | 2                     | mA   |

| TJ                        | Junction temperature                   | -40  | 125                   | °C   |

| T <sub>stg</sub>          | Storage temperature                    | -40  | 125                   | °C   |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

- All voltage values are with respect to network ground terminal.

- (3) While switching.

# 6.2 ESD Ratings

|                    |                         |                                                                       |                                                                   | VALUE | UNIT |

|--------------------|-------------------------|-----------------------------------------------------------------------|-------------------------------------------------------------------|-------|------|

|                    | V                       |                                                                       | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup> | ±2000 | V    |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per ANSI/ESDA/JEDEC JS-002 <sup>(2)</sup> | ±500                                                              | V     |      |

- (1) JEDEC document JEP155 states that 500V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250V CDM allows safe manufacturing with a standard ESD control process.

# 6.3 Recommended Operating Conditions

|                    |                                                                                        | MIN | NOM MAX                  | UNIT   |

|--------------------|----------------------------------------------------------------------------------------|-----|--------------------------|--------|

| V <sub>IN</sub>    | Supply voltage range                                                                   | 2.4 | 5.5                      | V      |

| V <sub>OUT</sub>   | Output voltage range                                                                   | 0.6 | V <sub>IN</sub> or 3.35V | V      |

| t <sub>F_VIN</sub> | Falling transition time at VIN (1)                                                     |     | 10                       | mV/μs  |

|                    | Output current, TPSM82864xx                                                            |     | 4                        | А      |

| IOUT               | Output current, TPSM82866xx                                                            |     | 6                        |        |

|                    | Nominal resistance range for external voltage selection resistor (E96 resistor series) | 10  | 249                      | kΩ     |

| R <sub>VSET</sub>  | External voltage selection resistor tolerance                                          |     | 1%                       |        |

|                    | External voltage selection resistor temperature coefficient                            |     | ±200                     | ppm/°C |

| T <sub>J</sub>     | Junction temperature                                                                   | -40 | 125                      | °C     |

(1) The falling slew rate of V<sub>IN</sub> must be limited if V<sub>IN</sub> goes below V<sub>UVLO</sub> (see Power Supply Recommendations).

資料に関するフィードバック(ご意見やお問い合わせ)を送信

# **6.4 Thermal Information**

|                       |                                              | TPSM8286x         | TPSM8286x          |      |

|-----------------------|----------------------------------------------|-------------------|--------------------|------|

|                       | THERMAL METRIC(1)                            | 15 PINS           | 15 PINS            | UNIT |

|                       |                                              | RCF<br>JEDEC 51-7 | RCF<br>EVM         | -    |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 66.8              | 29.7               | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 41.5              | n/a <sup>(2)</sup> | °C/W |

| R <sub>0JB</sub>      | Junction-to-board thermal resistance         | 19.6              | n/a <sup>(2)</sup> | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 1.8               | 0.1                | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 19                | 15.1               | °C/W |

<sup>(1)</sup> (2) For more information about thermal metrics, see the Semiconductor and IC Package Thermal Metrics application note.

Not applicable to an EVM.

# 6.5 Electrical Characteristics

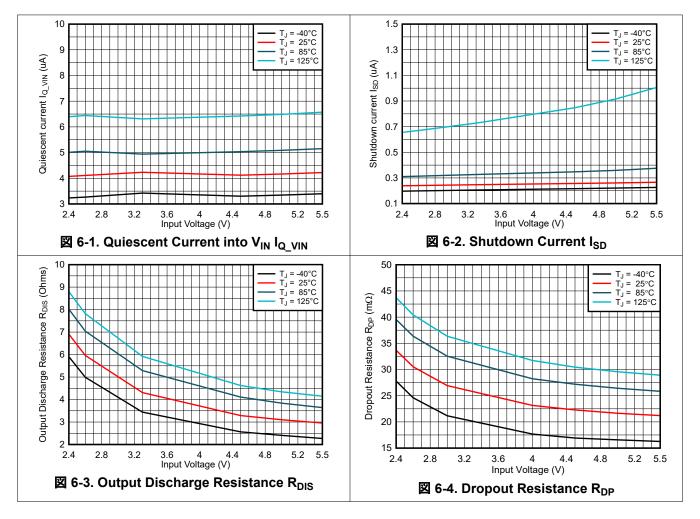

$T_1 = -40^{\circ}$ C to 125°C, and  $V_{IN} = 2.4$ V to 5.5V. Typical values are at  $T_1 = 25^{\circ}$ C and  $V_{IN} = 5$ V, unless otherwise noted.

|                                       | PARAMETER                                                       | TEST CONDITIONS                                                                                               | MIN  | TYP  | MAX  | UNIT |

|---------------------------------------|-----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|------|------|------|------|

| SUPPLY                                |                                                                 |                                                                                                               |      |      |      |      |

| I <sub>Q_VIN</sub>                    | Quiescent current into VIN pin                                  | EN = High, no load, device not switching                                                                      |      | 4    | 10   | μA   |

| I <sub>Q_VOS</sub>                    | Quiescent current into VOS pin                                  | EN = High, no load, device not switching, V <sub>VOS</sub> = 1.8V                                             |      | 18   |      | μΑ   |

| I <sub>SD</sub>                       | Shutdown current                                                | EN = Low, T <sub>J</sub> = -40°C to 85°C                                                                      |      | 0.24 | 1    | μA   |

| · · · · · · · · · · · · · · · · · · · | Lindow sales as In also set the sales and                       | V <sub>IN</sub> rising                                                                                        | 2.2  | 2.3  | 2.4  | V    |

| $V_{UVLO}$                            | Undervoltage lockout threshold                                  | V <sub>IN</sub> falling                                                                                       | 2.1  | 2.2  | 2.3  | V    |

| т                                     | Thermal warning threshold                                       | T <sub>J</sub> rising                                                                                         |      | 130  |      | °C   |

| $T_JW$                                | Thermal warning hysteresis                                      | T <sub>J</sub> falling                                                                                        | ,    | 20   |      | °C   |

|                                       | Thermal shutdown threshold                                      | T <sub>J</sub> rising                                                                                         | ı    | 150  |      | °C   |

| $T_{JSD}$                             | Thermal shutdown hysteresis                                     | T <sub>J</sub> falling                                                                                        |      | 20   |      | °C   |

| LOGIC II                              | NTERFACE                                                        |                                                                                                               |      |      |      |      |

| V <sub>IH</sub>                       | High-level input threshold voltage at EN, SCL, SDA and VSET/VID |                                                                                                               | 0.84 |      |      | V    |

| V <sub>IL</sub>                       | Low-level input threshold voltage at EN, SCL, SDA and VSET/VID  |                                                                                                               |      |      | 0.4  | V    |

| I <sub>SCL,LKG</sub>                  | Input leakage current into SCL pin                              |                                                                                                               |      | 0.01 | 0.8  | μA   |

| I <sub>SDA,LKG</sub>                  | Input leakage current into SDA pin                              |                                                                                                               | 1    | 0.01 | 0.1  | μA   |

| I <sub>EN,LKG</sub>                   | Input leakage current into EN pin                               |                                                                                                               |      | 0.01 | 0.1  | μA   |

| C <sub>SCL</sub>                      | Parasitic capacitance at SCL                                    |                                                                                                               |      | 1    |      | pF   |

| C <sub>SDA</sub>                      | Parasitic capacitance at SDA                                    |                                                                                                               | ,    | 2.4  |      | pF   |

| START-L                               | JP, POWER GOOD                                                  |                                                                                                               |      |      |      |      |

| t <sub>Delay</sub>                    | Enable delay time                                               | Time from EN high to device starts switching with a 249k $\Omega$ resistor connected between VSET/VID and GND | 420  | 650  | 1100 | μs   |

| ОИТРИТ                                | T .                                                             |                                                                                                               |      |      |      |      |

| \/                                    | Output valtage ecouracy                                         | FPWM, no Load, T <sub>J</sub> = 0°C to 85°C                                                                   | -1   |      | 1    | %    |

| V <sub>OUT</sub>                      | Output voltage accuracy                                         | FPWM, no Load                                                                                                 | -2   |      | 2    | %    |

| I <sub>VOS,LKG</sub>                  | Input leakage current into VOS pin                              | EN = Low, Output discharge disabled, V <sub>VOS</sub> = 1.8V                                                  |      | 0.2  | 2.5  | μΑ   |

| R <sub>DIS</sub>                      | Output discharge resistor at VOS pin                            |                                                                                                               |      | 3.5  |      | Ω    |

|                                       | Load regulation                                                 | V <sub>OUT</sub> = 0.9V, FPWM                                                                                 |      | 0.04 |      | %/A  |

| POWER                                 | SWITCH                                                          |                                                                                                               |      |      |      |      |

| R <sub>DP</sub>                       | Dropout resistance                                              | 100% mode. V <sub>IN</sub> = 3.3V, T <sub>J</sub> = 25°C                                                      |      | 22   |      | mΩ   |

|                                       | High side FET forms 1 1 1 1                                     | TPSM82864xx                                                                                                   | 5    | 5.5  | 6    | Α    |

|                                       | High-side FET forward current limit                             | TPSM82866xx                                                                                                   | 7    | 7.9  | 9    | Α    |

| I <sub>LIM</sub>                      |                                                                 | TPSM82864xx                                                                                                   |      | 4.5  |      | Α    |

|                                       | Low-side FET forward current limit                              | TPSM82866xx                                                                                                   |      | 6.5  |      | Α    |

|                                       | Low-side FET negative current limit                             |                                                                                                               |      | -3   |      | Α    |

| f <sub>SW</sub>                       | PWM switching frequency                                         | I <sub>OUT</sub> = 1A, V <sub>OUT</sub> = 0.9V                                                                |      | 2.4  |      | MHz  |

資料に関するフィードバック (ご意見やお問い合わせ) を送信

Copyright © 2024 Texas Instruments Incorporated

6

# 6.6 I<sup>2</sup>C Interface Timing Characteristics

|                                    | PARAMETER                                        | TEST CONDITIONS                                               | MIN | MAX  | UNIT |

|------------------------------------|--------------------------------------------------|---------------------------------------------------------------|-----|------|------|

|                                    |                                                  | Standard mode                                                 |     | 100  | kHz  |

|                                    |                                                  | Fast mode                                                     |     | 400  | kHz  |

|                                    |                                                  | Fast mode plus                                                |     | 1    | MHz  |

| f <sub>(SCL)</sub>                 | SCL clock frequency                              | High-speed mode (write operation), C <sub>B</sub> – 100pF max |     | 3.4  | MHz  |

|                                    |                                                  | High-speed mode (read operation), C <sub>B</sub> – 100pF max  |     | 3.4  | MHz  |

|                                    |                                                  | High-speed mode (write operation), C <sub>B</sub> – 400pF max |     | 1.7  | MHz  |

|                                    |                                                  | High-speed mode (read operation), C <sub>B</sub> – 400pF max  |     | 1.7  | MHz  |

|                                    |                                                  | Standard mode                                                 | 4.7 |      | μs   |

| t <sub>BUF</sub>                   | Bus free time between a STOP and START condition | Fast mode                                                     | 1.3 |      | μs   |

|                                    | CITACT CONGINETY                                 | Fast mode plus                                                | 0.5 |      | μs   |

|                                    |                                                  | Standard mode                                                 | 4   |      | μs   |

|                                    | Light time (reported) START condition            | Fast mode                                                     | 600 |      | ns   |

| t <sub>HD</sub> , t <sub>STA</sub> | Hold time (repeated) START condition             | Fast mode plus                                                | 260 |      | ns   |

|                                    |                                                  | High-speed mode                                               | 160 |      | ns   |

|                                    | LOW period of the SCL clock                      | Standard mode                                                 | 4.7 |      | μs   |

|                                    |                                                  | Fast mode                                                     | 1.3 |      | μs   |

| $t_{LOW}$                          |                                                  | Fast mode plus                                                | 0.5 |      | μs   |

|                                    |                                                  | High-speed mode, C <sub>B</sub> – 100pF max                   | 160 |      | ns   |

|                                    |                                                  | High-speed mode, C <sub>B</sub> – 400pF max                   | 320 |      | ns   |

|                                    |                                                  | Standard mode                                                 | 4   |      | μs   |

|                                    |                                                  | Fast mode                                                     | 600 |      | ns   |

| t <sub>HIGH</sub>                  | HIGH period of the SCL clock                     | Fast mode plus                                                | 260 |      | ns   |

|                                    |                                                  | High-speed mode, C <sub>B</sub> – 100pF max                   | 60  |      | ns   |

|                                    |                                                  | High-speed mode, C <sub>B</sub> – 400pF max                   | 120 |      | ns   |

|                                    |                                                  | Standard mode                                                 | 4.7 |      | μs   |

|                                    | Setup time for a repeated START                  | Fast mode                                                     | 600 |      | ns   |

| t <sub>SU</sub> , t <sub>STA</sub> | condition                                        | Fast mode plus                                                | 260 |      | ns   |

|                                    |                                                  | High-speed mode                                               | 160 |      | ns   |

|                                    |                                                  | Standard mode                                                 | 250 |      | ns   |

|                                    | Data a stan time                                 | Fast mode                                                     | 100 |      | ns   |

| t <sub>SU</sub> , t <sub>DAT</sub> | Data setup time                                  | Fast mode plus                                                | 50  |      | ns   |

|                                    |                                                  | High-speed mode                                               | 10  |      | ns   |

|                                    |                                                  | Standard mode                                                 | 0   | 3.45 | μs   |

|                                    |                                                  | Fast mode                                                     | 0   | 0.9  | μs   |

| t <sub>HD</sub> , t <sub>DAT</sub> | Data hold time                                   | Fast mode plus                                                | 0   |      | μs   |

|                                    |                                                  | High-speed mode, C <sub>B</sub> – 100pF max                   | 0   | 70   | ns   |

|                                    |                                                  | High-speed mode, C <sub>B</sub> – 400pF max                   | 0   | 150  | ns   |

# 6.6 I<sup>2</sup>C Interface Timing Characteristics (続き)

|                  | PARAMETER                                                             | TEST CONDITIONS                             | MIN                        | MAX  | UNIT |

|------------------|-----------------------------------------------------------------------|---------------------------------------------|----------------------------|------|------|

|                  |                                                                       | Standard mode                               |                            | 1000 | ns   |

| RCL              |                                                                       | Fast mode                                   | 20 +<br>0.1 C <sub>B</sub> | 300  | ns   |

|                  | Rise time of SCL signal                                               | Fast mode plus                              |                            | 120  | ns   |

|                  |                                                                       | High-speed mode, C <sub>B</sub> – 100pF max | 10                         | 40   | ns   |

|                  |                                                                       | High-speed mode, C <sub>B</sub> – 400pF max | 20                         | 80   | ns   |

|                  |                                                                       | Standard mode                               | 20 +<br>0.1 C <sub>B</sub> | 1000 | ns   |

| RCL1             | Rise time of SCL signal after a repeated START condition and after an | Fast mode                                   | 20 +<br>0.1 C <sub>B</sub> | 300  | ns   |

|                  | acknowledge BIT                                                       | Fast mode plus                              |                            | 120  | ns   |

|                  |                                                                       | High-speed mode, C <sub>B</sub> – 100pF max | 10                         | 80   | ns   |

|                  |                                                                       | High-speed mode, C <sub>B</sub> – 400pF max | 20                         | 160  | ns   |

|                  |                                                                       | Standard mode                               | 20 +<br>0.1 C <sub>B</sub> | 300  | ns   |

|                  | Fall time of SCL signal                                               | Fast mode                                   |                            | 300  | ns   |

| FCL              |                                                                       | Fast mode plus                              |                            | 120  | ns   |

|                  |                                                                       | High-speed mode, C <sub>B</sub> – 100pF max | 10                         | 40   | ns   |

|                  |                                                                       | High-speed mode, C <sub>B</sub> – 400pF max | 20                         | 80   | ns   |

|                  | Rise time of SDA signal                                               | Standard mode                               |                            | 1000 | ns   |

|                  |                                                                       | Fast mode                                   | 20 +<br>0.1 C <sub>B</sub> | 300  | ns   |

| RDA              |                                                                       | Fast mode plus                              |                            | 120  | ns   |

|                  |                                                                       | High-speed mode, C <sub>B</sub> – 100pF max | 10                         | 80   | ns   |

|                  |                                                                       | High-speed mode, C <sub>B</sub> – 400pF max | 20                         | 160  | ns   |

|                  |                                                                       | Standard mode                               |                            | 300  | ns   |

|                  |                                                                       | Fast mode                                   | 20 +<br>0.1 C <sub>B</sub> | 300  | ns   |

| FDA              | Fall time of SDA signal                                               | Fast mode plus                              |                            | 120  | ns   |

|                  |                                                                       | High-speed mode, C <sub>B</sub> – 100pF max | 10                         | 80   | ns   |

|                  |                                                                       | High-speed mode, C <sub>B</sub> – 400pF max | 20                         | 160  | ns   |

|                  |                                                                       | Standard mode                               | 4                          |      | μs   |

|                  | Saturations of STOR condition                                         | Fast mode                                   | 600                        |      | ns   |

| su, <b>t</b> sto | Setup time of STOP condition                                          | Fast mode plus                              | 260                        |      | ns   |

|                  |                                                                       | High-Speed mode                             | 160                        |      | ns   |

|                  |                                                                       | Standard mode                               |                            | 400  | pF   |

| _                | Conscitive lead for CDA === 1 CC/                                     | Fast mode                                   |                            | 400  | pF   |

| C <sub>B</sub>   | Capacitive load for SDA and SCL                                       | Fast mode plus                              |                            | 550  | pF   |

|                  |                                                                       | High-Speed mode                             |                            | 400  | pF   |

# 6.7 Typical Characteristics

# 7 Detailed Description

### 7.1 Overview

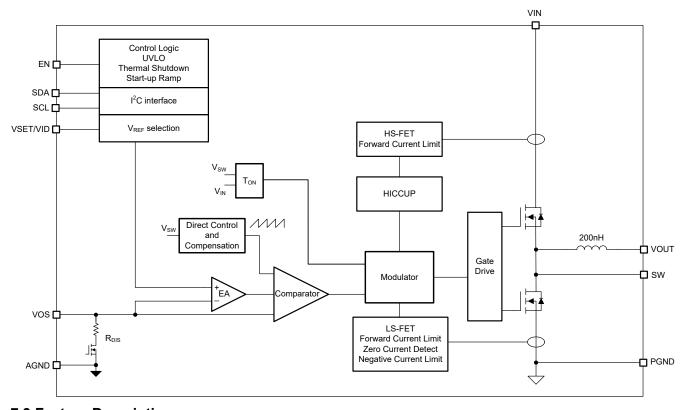

The TPSM8286xx synchronous, step-down converter power module uses the DCS-Control (Direct Control with seamless transition into power save mode) topology. This topology is an advanced regulation topology that combines the advantages of hysteretic, voltage, and current mode control. The DCS-Control topology operates in PWM (pulse width modulation) mode for medium-to-heavy load conditions and in PSM (power save mode) at light load currents. In PWM, the converter operates with the nominal switching frequency of 2.4MHz, having a controlled frequency variation over the input voltage range. As the load current decreases, the converter enters power save mode, reducing the switching frequency and minimizing the quiescent current of the IC to achieve high efficiency over the entire load current range. DCS-Control supports both operation modes using a single building block and, therefore, has a seamless transition from PWM to PSM without effects on the output voltage. The TPSM8286xx offers excellent DC voltage regulation and load transient regulation, combined with low output voltage ripple, minimizing interference with RF circuits.

The TPSM8286xxxxP versions in the RCF package use MagPack technology to deliver the highest-performance power module design. Leveraging our proprietary integrated-magnetics packaging technology, MagPack (magnetics in package) power modules deliver industry-leading power density, high efficiency, good thermal performance, ease of use, and reduced EMI emissions.

# 7.2 Functional Block Diagram

# 7.3 Feature Description

# 7.3.1 Power Save Mode

As the load current decreases, the device seamlessly enters power save mode (PSM) operation. In PSM, the converter operates with a reduced switching frequency and a minimum quiescent current to maintain high efficiency. Power save mode is based on a fixed on-time architecture, as shown in  $\pm$  1. The inductance used in the TPSM8286xx is 200nH typical.

バック (ご意見やお問い合わせ) を送信 Copyright © 2024 Texas Instruments Incorporated

$$t_{ON} = \frac{V_{OUT}}{V_{IN} \times f_{SW}} \tag{1}$$

For very small output voltages, an absolute minimum on time of approximately 50ns is kept to limit switching losses. The operating frequency is thereby reduced from the nominal value, which keeps efficiency high. The switching frequency in PSM is estimated as:

$$f_{PSM} = \frac{2 \times I_{OUT}}{t_{ON}^2 \times \frac{V_{IN}}{V_{OUT}} \times \frac{V_{IN} - V_{OUT}}{L}}$$

(2)

The load current at which PSM is entered is at one half of the ripple current of the inductor and can be estimated as:

$$I_{Load(PSM-entry)} = \frac{V_{IN} \times t_{ON}}{2} \times \frac{1 - \frac{V_{OUT}}{V_{IN}}}{L}$$

(3)

In power save mode, the output voltage rises slightly above the nominal output voltage. This effect is minimized by increasing the output capacitance.

#### 7.3.2 Forced PWM Mode

When setting the Enable FPWM Mode bit = 1 in the Control register, the device enters forced PWM (FPWM) mode and operates with a constant switching frequency over the entire load range, even at very light loads. This action reduces the output voltage ripple and allows simple filtering of the switching frequency for noise-sensitive applications but lowers efficiency at light loads.

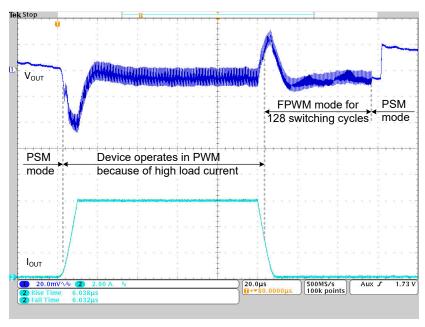

### 7.3.3 Optimized Transient Performance from PWM to PSM Operation

For most converters, the load transient response in PWM mode is improved compared to PSM, because the converter reacts faster on the load step and actively sinks energy on the load release. As an additional feature, the TPSM8286xx automatically stays in PWM mode for 128 cycles after a heavy load release to bring the output voltage back to the regulation level faster. After these 128 cycles of PWM mode, the device automatically returns to PSM (if the Enable FPWM Mode bit = 0). See  $\boxtimes$  7-1. Without this optimization, the output voltage overshoot is higher.

図 7-1. Optimized Transient Performance from PWM to PSM

### 7.3.4 Low Dropout Operation (100% Duty Cycle)

The device offers a low dropout operation by entering 100% duty cycle mode if the input voltage comes close to the target output voltage. In this mode, the high-side MOSFET switch is constantly turned on. This constant is particularly useful in battery-powered applications to achieve the longest operation time by taking full advantage of the whole battery voltage range. The minimum input voltage to maintain a minimum output voltage is given by:

$$V_{IN (min)} = V_{OUT (min)} + I_{OUT (max)} \times R_{DP}$$

(4)

#### where

- V<sub>OUT (min)</sub> = Minimum output voltage the load can accept

- I<sub>OUT (max)</sub> = Maximum output current

- R<sub>DP</sub> = Resistance from VIN to VOUT (high-side R<sub>DS(on)</sub> + R<sub>DC</sub> of the inductor)

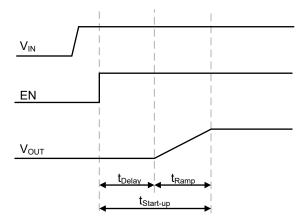

### 7.3.5 Enable and Soft-Start Ramp

After enabling the device, there is a 650 $\mu$ s enable delay ( $t_{Delay}$ ) before the  $I^2C$  interface is active. The  $t_{Delay}$  time varies with the VSET/MODE resistor used and is longest with a resistance of  $249k\Omega$ . After the enable delay, all registers can be read and written by the  $I^2C$  interface. The Voltage Ramp Speed bits in the Control register set the slope of the Output Voltage soft start ramp (default =  $1mV / \mu s$ ). This action avoids excessive inrush current and creates a smooth output voltage ramp up. This action also prevents excessive voltage drop of batteries or prior voltage regulators which have a high internal impedance.

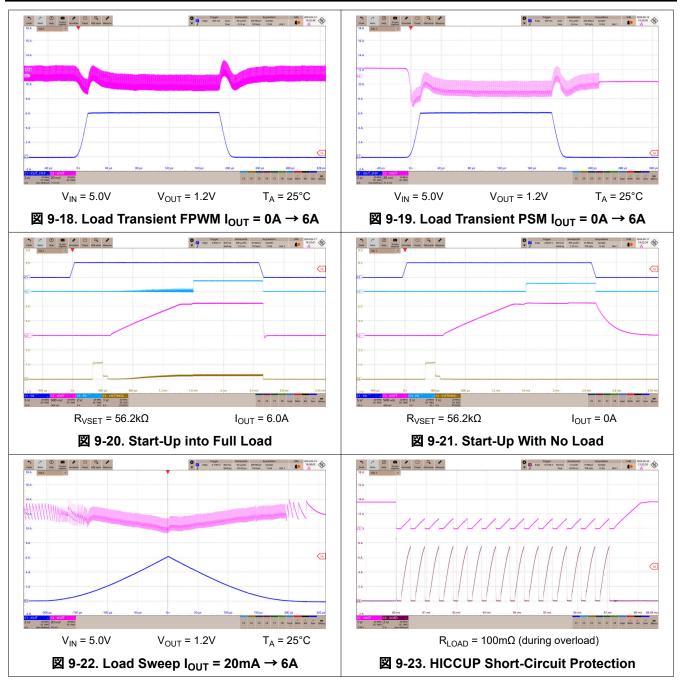

7-2 shows the start-up sequence.

図 7-2. Start-Up Sequence

The device is able to start into a prebiased output capacitor. The device starts with the applied bias voltage and ramps the output voltage to the nominal value.

# 7.3.6 Switch Current Limit and HICCUP Short-Circuit Protection

The switch current limit prevents the device from high inductor current and from drawing excessive current from the battery or input voltage rail. Excessive current can occur with a heavy load or shorted output circuit condition. If the inductor current reaches the threshold I<sub>LIM</sub>, cycle by cycle, the high-side MOSFET is turned off and the low-side MOSFET is turned on until the inductor current ramps down to the low-side MOSFET current limit.

When the high-side MOSFET current limit is triggered 32 times, the device stops switching. The device then automatically re-starts with soft start after a typical delay time of 128µs has passed. The device repeats this mode until the high load condition disappears. This HICCUP short-circuit protection reduces the current consumed from the input supply during an overload condition.  $\boxtimes$  9-23 shows the hiccup short-circuit protection.

The HICCUP can be disabled by the CONTROL register bit Enable HICCUP. Disabling HICCUP changes the overcurrent protection to latching protection. The device stops switching after the high-side MOSFET current

limit is triggered 32 times. Toggling the EN pin, removing and reapplying the input voltage, or writing to the CONTROL register bit Software Enable Device unlatches the device.

The low-side MOSFET also contains a negative current limit to prevent excessive current from flowing back through the inductor to the input. If the low-side sinking current limit is exceeded, the low-side MOSFET is turned off. In this scenario, both MOSFETs are off until the start of the next cycle. The negative current limit is only active in forced PWM mode.

### 7.3.7 Undervoltage Lockout

To avoid misoperation of the device at low input voltages, undervoltage lockout (UVLO) disables the device when the input voltage is lower than  $V_{UVLO}$ . When the input voltage recovers, the device automatically returns to operation with soft start. The UVLO bit in the STATUS Register is set when the input voltage is below the UVLO falling threshold.

In case the input voltage falls below 1.8V (typical), all registers are reset.

### 7.3.8 Thermal Warning and Shutdown

The module features a thermal warning indicator bit in the Status register. This bit is set to 1 if the junction temperature exceeds the rising  $T_{JW}$  temperature and is reset when the junction temperature falls below the threshold by the hysteresis. The device continues operating.

In case the junction temperature exceeds  $T_{JSD}$ , the device goes into thermal shutdown, stops switching, and activates the output voltage discharge (in case this is enabled). When the device temperature falls below the threshold by the hysteresis, the device returns to normal operation automatically with soft start.

### 7.4 Device Functional Modes

### 7.4.1 Enable and Disable (EN)

The device is enabled by setting the EN pin to a logic high. Accordingly, shutdown mode is forced if the EN pin is pulled low. In shutdown mode, the internal power switches as well as the entire control circuitry are turned off and all the registers are reset to the default values, except for the Enable Output Discharge bit. An internal switch smoothly discharges the output through the VOS pin if the Enable Output Discharge bit is set to 1.

In shutdown mode (EN = Low), the  $I^2C$  interface is disabled to reduce the current consumption of the module. Thus no registers can be accessed.

The typical enable threshold value of the EN pin is 0.66V for rising input signals and the typical shutdown threshold is 0.52V for falling input signals. Do not leave the EN pin floating.

The device can also be enabled or disabled by setting the Software Enable Device bit in the CONTROL register while EN = High. After being disabled or enabled by this bit, the device stops switching and initiates a new start-up ramp. There is no additional T<sub>Delay</sub> time and the registers are not reset.

## 7.4.2 Output Discharge

The purpose of the output discharge function is to make sure of a defined down-ramp of the output voltage when the device is disabled and to keep the output voltage close to 0V. The output discharge is active when the Enable Output Discharge bit is set to 1 and the EN pin is pulled low, when the Input voltage is below the UVLO threshold or during thermal shutdown. The discharge is active down to an input voltage of 1.6V (typical). The Enable Output Discharge bit is reset on the rising edge of the EN pin.

### 7.4.3 Start-Up Output Voltage and I<sup>2</sup>C Target Address Selection (VSET)

表 7-1. Start-up Output Voltage and I<sup>2</sup>C Target Address Options

| RESISTOR (E96 SERIES, ±1%<br>ACCURACY) AT VSET/VID | TPSM8286xCA2<br>START-UP OUTPUT VOLTAGE | TPSM8286xCA3<br>START-UP OUTPUT VOLTAGE | I <sup>2</sup> C TARGET ADDRESS |

|----------------------------------------------------|-----------------------------------------|-----------------------------------------|---------------------------------|

| 249kΩ                                              | 1.15V                                   | 2.30V                                   | 1000 110 (0x46)                 |

| 205kΩ                                              | 1.10V                                   | 2.20V                                   | 1000 101 (0x45)                 |

| 162kΩ                                              | 1.05V                                   | 2.10V                                   | 1000 100 (0x44)                 |

| 133kΩ                                              | 1.00V                                   | 2.00V                                   | 1000 011 (0x43)                 |

| 105kΩ                                              | 0.95V                                   | 1.90V                                   | 1000 010 (0x42)                 |

| 86.6kΩ                                             | 0.90V                                   | 1.80V                                   | 1000 001 (0x41)                 |

| 68.1kΩ                                             | 0.85V                                   | 1.70V                                   | 1001 000 (0x48)                 |

| 56.2kΩ                                             | 0.80V                                   | 1.60V                                   | 1001 001 (0x49)                 |

| 44.2kΩ                                             | 0.75V                                   | 1.50V                                   | 1001 010 (0x4A)                 |

| 36.5kΩ                                             | 0.70V                                   | 1.40V                                   | 1001 011 (0x4B)                 |

| 28.7kΩ                                             | 0.65V                                   | 1.30V                                   | 1001 100 (0x4C)                 |

| 23.7kΩ                                             | 0.60V                                   | 1.20V                                   | 1001 101 (0x4D)                 |

| 18.7kΩ                                             | 0.55V                                   | 1.10V                                   | 1001 110 (0x4E)                 |

| 15.4kΩ                                             | 0.50V                                   | 1.00V                                   | 1001 111 (0x4F)                 |

| 12.1kΩ                                             | 0.45V                                   | 0.90V                                   | 1000 000 (0x40)                 |

資料に関するフィードバック(ご意見やお問い合わせ)を送信

### 表 7-1. Start-up Output Voltage and I<sup>2</sup>C Target Address Options (続き)

| RESISTOR (E96 SERIES, ±1%<br>ACCURACY) AT VSET/VID | TPSM8286xCA2<br>START-UP OUTPUT VOLTAGE | TPSM8286xCA3<br>START-UP OUTPUT VOLTAGE | I <sup>2</sup> C TARGET ADDRESS |

|----------------------------------------------------|-----------------------------------------|-----------------------------------------|---------------------------------|

| 10k $Ω$ or lower                                   | 0.40V                                   | 0.80V                                   | 1000 111 (0x47)                 |

The R2D converter has an internal current source, which applies current through the external resistor, and an internal ADC, which reads back the resulting voltage level. Depending on the level, the correct start-up output voltage and I<sup>2</sup>C target address are set. After this R2D conversion is finished, the current source is turned off to avoid current flowing through the external resistor. Make sure that there is no additional current path or capacitance greater than 30pF from this pin to GND during R2D conversion. Otherwise, a false value is set.

During the ramp-up period ( $t_{Ramp}$ ), the output voltage ramps to the target value set by VSET first, then ramps up or down to the new value when the value of the output register is changed by  $I^2C$  interface commands.

### 7.4.4 Select Output Voltage Registers (VID)

After the start-up period ( $t_{Startup}$ ), the output voltage can be selected between two output voltage registers by the VID pin. When VID is pulled low, the output voltage is set by  $\frac{1}{8}$  8-2. When VID is pulled high, the output voltage is set by  $\frac{1}{8}$  8-3. This is also called dynamic voltage scaling (DVS). If the VID function is not used, the VSET resistor keeps the VSET/VID pin low and the  $V_{OUT}$  Register 1 sets the Output voltage.

During an output voltage change through I<sup>2</sup>C or the VSET/VID pin, the device can be configured to operate in FPWM by setting the Enable FPWM Mode during Output Voltage Change bit in CONTROL register to 1. In FPWM Mode, the ramp-up and ramp-down speeds are controlled by the device. In PSM Mode the ramp-up speed is controlled by the device, but the ramp-down speed is determined by the load current and the output capacitance. The output voltage change speed is set by the Voltage Ramp Speed bit.

# 7.5 Programming

### 7.5.1 Serial Interface Description

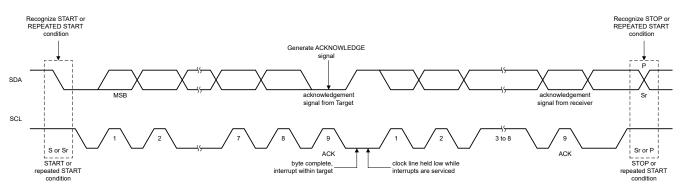

I<sup>2</sup>C is a 2-wire serial interface developed by Philips Semiconductor, now NXP Semiconductors. The bus consists of a data line (SDA) and a clock line (SCL) with pullup structures. When the bus is *idle*, both the SDA and SCL lines are pulled high. All the I<sup>2</sup>C-compatible devices connect to the I<sup>2</sup>C bus through open-drain I/O pins, SDA and SCL. A *controller* device, usually a microcontroller or a digital signal processor, controls the bus. The controller is responsible for generating the SCL signal and device addresses. The controller also generates specific conditions that indicate the START and STOP of data transfer. A *target* device receives or transmits data on the bus under control of the controller device, or both.

The TPSM8286xx module works as a *target* and supports the following data transfer *modes*, as defined in the I<sup>2</sup>C-Bus Specification: standard mode (100kbps) and fast mode (400kbps), fast mode plus (1Mbps) and high-speed mode (3.4Mbps). The interface adds flexibility to the power supply solution, enabling most functions to be programmed to new values depending on the instantaneous application requirements. Register contents remain intact as long as the input voltage remains above 1.8V.

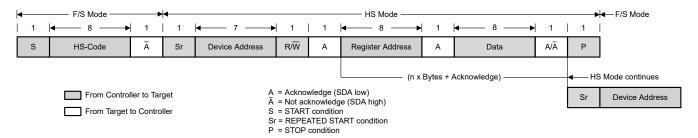

The data transfer protocol for standard and fast modes is exactly the same, therefore, standard and fast modes are referred to as F/S-mode in this document. The protocol for high-speed mode is different from F/S-mode, and is referred to as HS mode.

TI recommends that the  $I^2C$  controller initiates a STOP condition on the  $I^2C$  bus after the initial power up of the SDA and SCL pullup voltages to make sure of a reset of the  $I^2C$  engine.

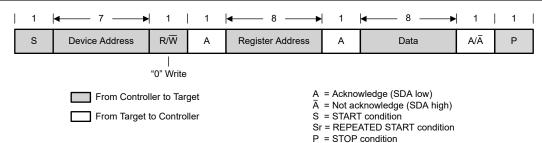

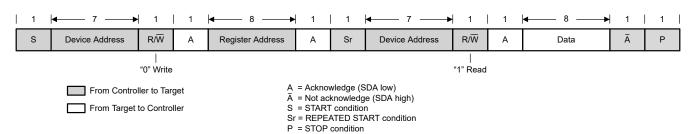

### 7.5.2 Standard-Mode, Fast-Mode, and Fast-Mode Plus Protocol

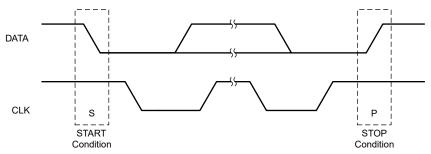

The controller initiates data transfer by generating a start condition. The start condition is when a high-to-low transition occurs on the SDA line while SCL is high, as shown in  $\boxtimes$  7-3. All I<sup>2</sup>C-compatible devices recognize a start condition.

Copyright © 2024 Texas Instruments Incorporated

資料に関するフィードバック(ご意見やお問い合わせ)を送信

15

図 7-3. START and STOP Conditions

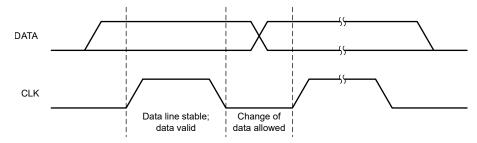

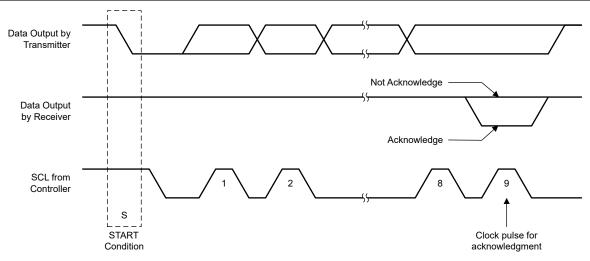

The controller then generates the SCL pulses, and transmits the 7-bit address and the read/write direction bit  $R/\overline{W}$  on the SDA line. During all transmissions, the controller makes sure that data is valid. A valid data condition requires the SDA line to be stable during the entire high period of the clock pulse (see  $\boxed{X}$  7-4). All devices recognize the address sent by the controller and compare the address to the internal fixed addresses. Only the target device with a matching address generates an acknowledge (see  $\boxed{X}$  7-5) by pulling the SDA line low during the entire high period of the ninth SCL cycle. Upon detecting this acknowledge, the controller knows that a communication link with the target has been established.

図 7-4. Bit Transfer on the Serial Interface

The controller generates further SCL cycles to either transmit data to the target (R/W bit 0) or receive data from the target (R/W bit 1). In either case, the receiver needs to acknowledge the data sent by the transmitter. So an acknowledge signal can either be generated by the controller or by the target, depending on which one is the receiver. 9-bit valid data sequences consisting of 8-bit data and 1-bit acknowledge can continue as long as necessary.

To signal the end of the data transfer, the controller generates a stop condition by pulling the SDA line from low to high while the SCL line is high (see  $\boxtimes$  7-3). This action releases the bus and stops the communication link with the addressed target. All I<sup>2</sup>C-compatible devices must recognize the stop condition. Upon the receipt of a stop condition, all devices know that the bus is released, and the devices wait for a start condition followed by a matching address.

Attempting to read data from register addresses not listed in this section results in 0x00 being read out.

図 7-5. Acknowledge on the I<sup>2</sup>C Bus

図 7-6. Bus Protocol

### 7.5.3 HS-Mode Protocol

The controller generates a start condition followed by a valid serial byte containing HS controller code 00001XXX. This transmission is made in F/S-mode at no more than 400kbps. No device is allowed to acknowledge the HS controller code, but all devices must recognize the HS controller code and switch the internal setting to support 3.4Mbps operation.

The controller then generates a *repeated start condition* (a repeated start condition has the same timing as the start condition). After this repeated start condition, the protocol is the same as F/S-mode, except that transmission speeds up to 3.4Mbps are allowed. A stop condition ends the HS-mode and switches all the internal settings of the target devices to support the F/S-mode. Instead of using a stop condition, repeated start conditions must be used to secure the bus in HS-mode.

Attempting to read data from register addresses not listed in this section results in 0x00 being read out.

### 7.5.4 I<sup>2</sup>C Update Sequence

The sequence requires a start condition, a valid I<sup>2</sup>C target address, a register address byte, and a data byte for a single update. After the receipt of each byte, the device acknowledges by pulling the SDA line low during the high period of a single clock pulse. A valid I<sup>2</sup>C address selects the device. The device performs an update on the falling edge of the acknowledge signal that follows the LSB byte.

### 図 7-7. Write Data Transfer Format in Standard Modes, Fast Modes, and Fast-Plus Modes

### 図 7-8. Read Data Transfer Format in Standard Modes, Fast Modes, and Fast-Plus Modes

図 7-9. Data Transfer Format in HS Mode

# 7.5.5 I<sup>2</sup>C Register Reset

The I<sup>2</sup>C registers can be reset by:

- Pulling the input voltage below 1.8V (typical)

- A high-to-low transition on EN

- Setting the Reset bit in the CONTROL register. When Reset is set to 1, all registers are reset to the default values and a new start-up is begun immediately. After t<sub>Delay</sub>, the I<sup>2</sup>C registers can be programmed again.

資料に関するフィードバック(ご意見やお問い合わせ)を送信

# 8 Register Map

# 表 8-1. Register Map

| REGISTER ADDRESS<br>(HEX) | REGISTER NAME               | FACTORY DEFAULT<br>(HEX) | DESCRIPTION                                          |

|---------------------------|-----------------------------|--------------------------|------------------------------------------------------|

| 0x01                      | V <sub>OUT</sub> Register 1 | Set through VSET/VID pin | Sets the target output voltage when VSET/VID is low  |

| 0x02                      | V <sub>OUT</sub> Register 2 | 0x64                     | Sets the target output voltage when VSET/VID is high |

| 0x03                      | CONTROL Register            | 0x6F                     | Sets miscellaneous configuration bits                |

| 0x05                      | STATUS Register             | 0x00                     | Returns status flags                                 |

# 8.1 Target Address Byte

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0   |

|---|---|---|---|---|---|---|-----|

| 1 | х | х | х | х | х | х | R/W |

The target address byte is the first byte received following the START condition from the controller device. The target  $I^2C$  address is assigned by the VSET/VID resistor; see  $\frac{1}{2}$  7-1.

# 8.2 Register Address Byte

| 7 | 6 | 5 | 4 | 3 | 2  | 1  | 0  |

|---|---|---|---|---|----|----|----|

| 0 | 0 | 0 | 0 | 0 | D2 | D1 | D0 |

Following the successful acknowledgment of the target address, the bus controller sends a byte to the device, which contains the address of the register to be accessed.

# 8.3 V<sub>OUT</sub> Register 1

### 表 8-2. V<sub>OUT</sub> Register 1 Description

|     | REGISTER ADDRESS 0X01 READ/WRITE |                            |                                          |                                          |  |  |  |  |  |  |

|-----|----------------------------------|----------------------------|------------------------------------------|------------------------------------------|--|--|--|--|--|--|

| BIT | FIELD                            | VALUE <sup>(1)</sup> (HEX) | TPSM8286xCA2 OUTPUT<br>VOLTAGE (TYPICAL) | TPSM8286xCA3 OUTPUT<br>VOLTAGE (TYPICAL) |  |  |  |  |  |  |

|     |                                  | 0x00                       | 400mV                                    | 800mV                                    |  |  |  |  |  |  |

|     | VO1_SET                          | 0x01                       | 405mV                                    | 810mV                                    |  |  |  |  |  |  |

|     |                                  |                            |                                          |                                          |  |  |  |  |  |  |

| 7:0 |                                  | 0x64                       | 900mV                                    | 1800mV                                   |  |  |  |  |  |  |

|     |                                  |                            |                                          |                                          |  |  |  |  |  |  |

|     |                                  | 0xFE                       | 1670mV                                   | 3340mV                                   |  |  |  |  |  |  |

|     |                                  | 0xFF                       | 1675mV                                   | 3350mV                                   |  |  |  |  |  |  |

(1) The start-up value is assigned by the VSET/VID resistor; see 表 7-1.

# 8.4 V<sub>OUT</sub> Register 2

# 表 8-3. V<sub>OUT</sub> Register 2 Description

| REGISTER ADDRESS 0X02 READ/WRITE |         |             |                                          |                                          |  |  |  |  |

|----------------------------------|---------|-------------|------------------------------------------|------------------------------------------|--|--|--|--|

| BIT                              | FIELD   | VALUE (HEX) | TPSM8286xCA2 OUTPUT<br>VOLTAGE (TYPICAL) | TPSM8286xCA3 OUTPUT<br>VOLTAGE (TYPICAL) |  |  |  |  |

|                                  |         | 0x00        | 400mV                                    | 800mV                                    |  |  |  |  |

|                                  |         | 0x01        | 405mV                                    | 810mV                                    |  |  |  |  |

|                                  |         |             |                                          |                                          |  |  |  |  |

| 7:0                              | VO2_SET | 0x64        | 900mV (default value)                    | 1800mV (default value)                   |  |  |  |  |

|                                  |         |             |                                          |                                          |  |  |  |  |

|                                  |         | 0xFE        | 1670mV                                   | 3340mV                                   |  |  |  |  |

|                                  |         | 0xFF        | 1675mV                                   | 3350mV                                   |  |  |  |  |

# 8.5 CONTROL Register

# 表 8-4. CONTROL Register Description

|     | REGISTER ADDRESS 0X03 READ/WRITE              |                          |    |                                                                                                                                                      |  |  |  |  |  |  |  |

|-----|-----------------------------------------------|--------------------------|----|------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| BIT | FIELD                                         | FIELD TYPE DEFAULT DESCR |    | DESCRIPTION                                                                                                                                          |  |  |  |  |  |  |  |

| 7   | Reset                                         | R/W                      | 0  | 1 - Reset all registers to default.                                                                                                                  |  |  |  |  |  |  |  |

| 6   | Enable FPWM Mode during Output Voltage Change | R/W                      | 1  | 0 - Keep the current mode status during output voltage change 1 - Force the device in FPWM during output voltage change.                             |  |  |  |  |  |  |  |

| 5   | Software Enable Device                        | R/W                      | 1  | O - Disable the device. All registers values are still kept.     1 - Re-enable the device with a new start-up without the t <sub>Delay</sub> period. |  |  |  |  |  |  |  |

| 4   | Enable FPWM Mode                              | R/W                      | 0  | Set the device in power save mode at light loads.     Set the device in forced PWM mode at light loads.                                              |  |  |  |  |  |  |  |

| 3   | Enable Output Discharge                       | R/W                      | 1  | 0 - Disable output discharge<br>1 - Enable output discharge                                                                                          |  |  |  |  |  |  |  |

| 2   | Enable HICCUP                                 | R/W                      | 1  | O - Disable HICCUP. Enable latching protection.     1 - Enable HICCUP. Disable latching protection.                                                  |  |  |  |  |  |  |  |

| 0:1 | Voltage Ramp Speed                            | R/W                      | 11 | 00 - 20mV/μs (0.25μs/step)<br>01 - 10mV/μs (0.5μs/step)<br>10 - 5mV/μs (1μs/step)<br>11 - 1mV/μs (5μs/step)                                          |  |  |  |  |  |  |  |

# 8.6 STATUS Register

# 表 8-5. STATUS Register Description

| REGISTE | REGISTER ADDRESS 0X05 READ ONLY <sup>(1)</sup> |      |         |                                                                  |  |  |  |  |  |  |  |

|---------|------------------------------------------------|------|---------|------------------------------------------------------------------|--|--|--|--|--|--|--|

| BIT     | FIELD                                          | TYPE | DEFAULT | DESCRIPTION                                                      |  |  |  |  |  |  |  |

| 7:5     | Reserved                                       |      |         |                                                                  |  |  |  |  |  |  |  |

| 4       | Thermal Warning                                | R    | 0       | 1: Junction temperature is higher than 130°C.                    |  |  |  |  |  |  |  |

| 3       | HICCUP                                         | R    | 0       | 1: Device has HICCUP status once.                                |  |  |  |  |  |  |  |

| 2       | Reserved                                       |      |         |                                                                  |  |  |  |  |  |  |  |

| 1       | Reserved                                       |      |         |                                                                  |  |  |  |  |  |  |  |

| 0       | UVLO                                           | R    | 0       | 1: The input voltage is less than UVLO threshold (falling edge). |  |  |  |  |  |  |  |

| 1       | 1                                              | 1    | 1       | T =                                                              |  |  |  |  |  |  |  |

(1) All bit values are latched until the device is reset, or the STATUS register is read. Then, the STATUS register is reset to the default values.

# 9 Application and Implementation

注

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes, as well as validating and testing their design implementation to confirm system functionality.

# 9.1 Application Information

The TPSM8286xx is a synchronous, step-down converter, power module family. The following section discusses the selection of the external components to complete the power supply design. The required power inductor is integrated inside the TPSM8286xx. The integrated shielded inductor has a value of 0.20µH with a ±20% tolerance. The TPSM82864x and TPSM82866x are pin-to-pin and BOM-to-BOM compatible. The 4A and 6A version give the same efficiency and performance and are different only in the rated output current.

# 9.2 Typical Application

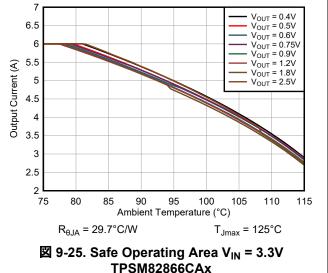

図 9-1. Typical Application

### 9.2.1 Design Requirements

For this design example, use 表 9-1 as the input parameters.

#### 表 9-1. Design Parameters

| DESIGN PARAMETER       | EXAMPLE VALUE |  |  |

|------------------------|---------------|--|--|

| Input voltage          | 2.4V to 5.5V  |  |  |

| Output voltage         | 1.2V          |  |  |

| Maximum output current | 6A            |  |  |

### 表 9-2 lists the components used for the example.

#### 表 9-2. List of Components

| REFERENCE         | CE DESCRIPTION                                                    |        |  |  |  |  |  |

|-------------------|-------------------------------------------------------------------|--------|--|--|--|--|--|

| C1                | 22μF, ceramic capacitor, 6.3V, X7R, size 0805, GRM21BZ70J226ME44  | Murata |  |  |  |  |  |

| C2                | 47μF, ceramic capacitor, 6.3V, X6S, size 0805, GRM21BC80J476ME01L | Murata |  |  |  |  |  |

| R4 <sup>(2)</sup> | Depending on the output voltage, Chip resistor, 1/16W, 1%         | Std    |  |  |  |  |  |

- (1) See the Third-Party Products disclaimer.

- (2) See 表 7-1 for the VSET/VID resistor values.

### 9.2.2 Detailed Design Procedure

### 9.2.2.1 Input and Output Capacitor Selection

For the best output and input voltage filtering, low-ESR ceramic capacitors are required. The input capacitor minimizes input voltage ripple, suppresses input voltage spikes, and provides a stable system rail for the device. The input capacitor must be placed between VIN and PGND as close as possible to those pins. For most applications,  $22\mu F$  is sufficient, though a larger value reduces input current ripple. The input capacitor plays an important role in the EMI performance of the system as explained in the Simplify Low EMI Design With Power Modules white paper.

The architecture of the device allows the use of tiny ceramic output capacitors with low equivalent series resistance (ESR). These capacitors provide low output voltage ripple and are recommended. The capacitor value can range from  $2 \times 22\mu F$  up to  $150\mu F$ . The recommended typical output capacitors are  $2 \times 22\mu F$  or  $1 \times 47\mu F$  with an X5R or better dielectric. Values over  $150\mu F$  can degrade the loop stability of the converter.

Ceramic capacitors have a DC-Bias effect, which has a strong influence on the final effective capacitance. Choose the right capacitor carefully in combination with considering ith package size and voltage rating. Make sure that the effective input capacitance is at least  $10\mu F$  and the effective output capacitance is at least  $22\mu F$ .

23

English Data Sheet: SLUSFL6

Product Folder Links: TPSM82866C

### 9.2.3 Application Curves

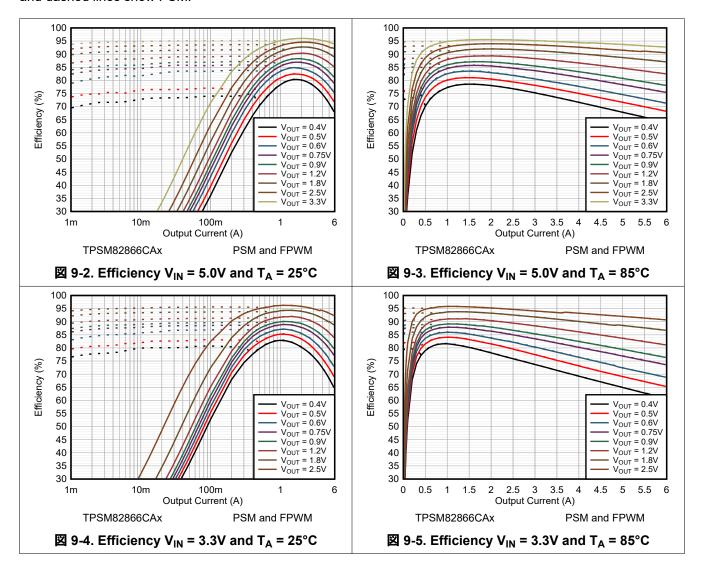

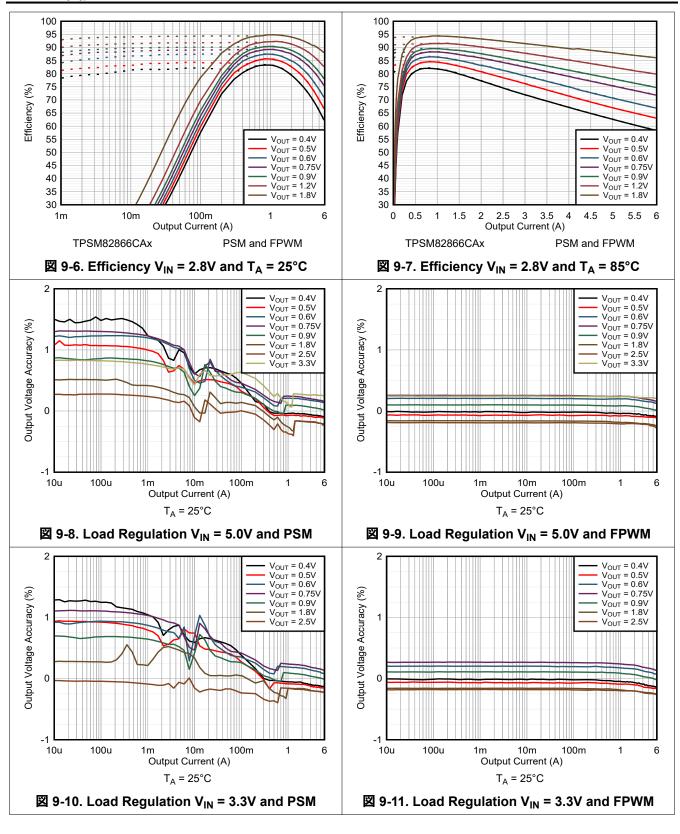

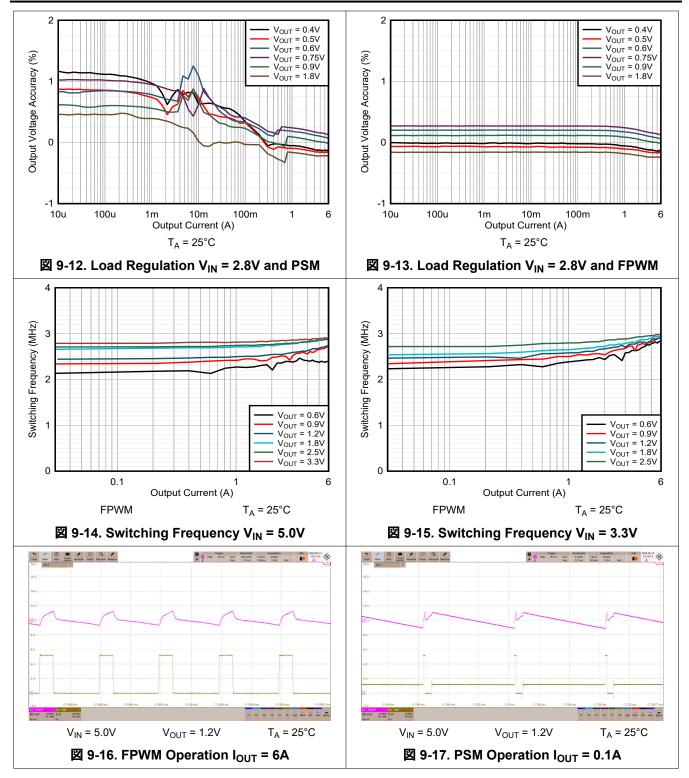

$V_{IN}$  = 5.0V,  $V_{OUT}$  = 1.2V,  $T_A$  = 25°C, BOM =  $\frac{1}{8}$  9-2, unless otherwise noted. Solid lines show the FPWM mode and dashed lines show PSM.

# 9.3 Power Supply Recommendations

The device is designed to operate from an input voltage supply range from 2.4V to 5.5V. The average input current of the TPSM8286xx is calculated as:

$$I_{IN} = \frac{1}{\eta} \times \frac{V_{OUT} \times I_{OUT}}{V_{IN}} \tag{5}$$

Make sure that the input power supply has a sufficient current rating for the application. The power supply must avoid a fast ramp down. The falling ramp speed must be slower than 10mV/µs if the input voltage drops below  $V_{UVLO}$ .

### 9.4 Layout

**ADVANCE INFORMATION**

### 9.4.1 Layout Guidelines

A proper layout is critical for the operation of any switched mode power supply, especially at high switching frequencies. Therefore, the PCB layout of the TPSM8286xx demands careful attention to make sure of best performance. A poor layout can lead to issues like the following:

- Bad line and load regulation

- Instability

- Increased EMI radiation

- Noise sensitivity

Refer to the Five Steps to a Great PCB Layout for a Step-Down Converter analog design journal for a detailed discussion of general best practices. The following are specific recommendations for the TPSM8286xx: