# **ADC12DL040**

ADC12DL040 Dual 12-Bit, 40 MSPS, 3V, 210mW A/D Converter

Literature Number: JAJSA71

National Semiconductor 2005年11月

# ADC12DL040

12 ビット、40MSPS、3V、210mW、デュアル A/D コンバータ

#### 概要

ADC12DL040 は、アナログ入力信号を 40MSPS のサンプリング・レートで 12 ビットのデジタル・ワードに変換できる、低消費電力のモノリシック CMOS デュアル A/D コンバータです。差動信号方式のパイプライン・アーキテクチャを採用し、デジタル誤差補正とオンチップ・サンプル / ホールド回路を備え、消費電力の低減を図る一方で優れた動的性能とフルパワー帯域 250MHz を実現しています。+3.0V の単電源で動作し、ナイキスト周波数での有効ビット数は 11.1 です。また、40MSPS での消費電力は、リファレンス電流を含めてわずか 210mW です。消費電力を 36mW に低減するパワーダウン機能を備えています。

差動入力には、VREFの2倍の振幅を持った信号をフルスケール差動入力として与えられるほか、シングルエンド入力として使用することも可能です。ただし、最適の性能を得るには完全な差動入力信号の使用を推奨します。2つのA/Dコンバータからのデジタル出力は、両方を多重化して1本のバスから出力することも、またはそれぞれ別々のバスから出力することもできます。デューティ・サイクル安定化機能および出力データ・フォーマットは、クワッド・ステートの機能ピンによって選択可能です。出力データは、オフセット・バイナリまたは2の補数のいずれかに設定できます。

低電圧システムとのインタフェースを容易にするために、ADC12DL040のデジタル出力ドライバの電源電圧ピンは、アナログ電源とは別の電源電圧に接続可能で、その範囲は 2.4V からそのアナログ電源電圧までです。

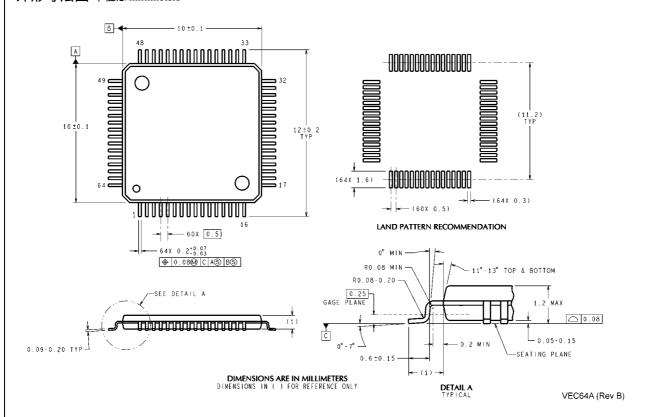

本デバイスは 64 ピンの TQFP パッケージで供給可能で、動作温度範囲は、工業用機器に適用される - 40 ~ + 85 です。評価を支援する評価ボードもかます。

## 特長

+ 3.0V 単電源動作 サンプル/ホールド回路内蔵 リファレンス電圧源内蔵 出力は 2.4V ~ 3.6V に対応 パワーダウン・モード デューティ・サイクル安定化回路 マルチプレクス出力モード

#### 主な仕様

分解能 12 ビット DNL  $\pm$  0.3LSB (typ) S/N 比 ( $f_{\rm IN}$  = 10MHz) 69dB (typ) SFDR ( $f_{\rm IN}$  = 10MHz) 85dB (typ) データ・レイテンシ 7 クロック・サイクル 消費電力

動作時 210mW (typ)パワーダウン・モード 36mW (typ)

# アプリケーション

超音波映像装置 計測機器 受信機 ソナー、レーダ xDSL ケーブル・モデム DSP のフロントエンド

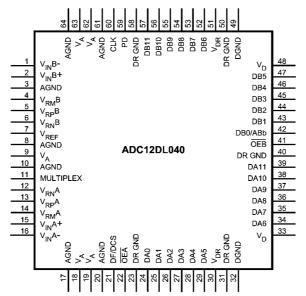

#### ピン配置図

TRI-STATE® はナショナル セミコンダクターの登録商標です

# 製品情報

| Industrial (-40°C ≤ T <sub>A</sub> ≤ +85°C) | Package          |

|---------------------------------------------|------------------|

| ADC12DL040CIVS                              | 64 Pin TQFP      |

| ADC12DL040EVAL                              | Evaluation Board |

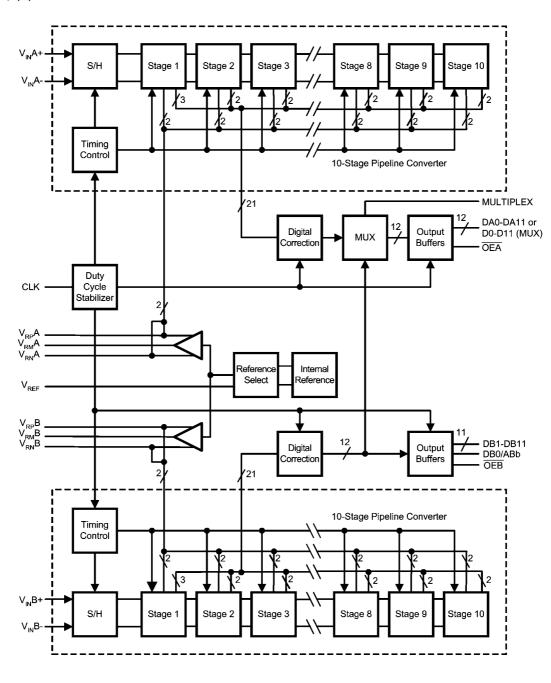

# ブロック図

# ピン説明および等価回路

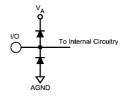

| ピン番号            | シンボル                                           | 等価回路                                                  | 説明                                                                                                                                                                                                                                                                                                                                                                  |

|-----------------|------------------------------------------------|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| アナログ <b>I/O</b> |                                                |                                                       |                                                                                                                                                                                                                                                                                                                                                                     |

| 15 2            | $V_{\rm IN}A$ + $V_{\rm IN}B$ +                |                                                       | 差動アナログ入力ピン。リファレンス電圧が 1.0V のとき、各入力ピンの電圧の中心がコモンモード電圧 $V_{CM}$ の場合、差動入力信号のフルスケール・レベルは、2.0 $V_{P-P}$ です。シングルエンド動作の場合は負極性入力ピンに $V_{CM}$ を接続しますが、最高性能を得る                                                                                                                                                                                                                  |

| 16<br>1         | V <sub>IN</sub> A -<br>V <sub>IN</sub> B -     | AGND                                                  | には差動信号を入力してください。                                                                                                                                                                                                                                                                                                                                                    |

| 7               | $ m V_{REF}$                                   | V <sub>A</sub> AGND                                   | リファレンス選択および外部リファレンス入力のためのピン。 $(V_A - 0.3V) < V_{REF} < V_A$ の場合、内部 $1.0V$ リファレンスが選択されます。 AGND $< V_{REF} < (AGND + 0.3V)$ の場合、内部 $0.5V$ リファレンスが選択されます。 このピンに $0.8V \sim 1.2V$ の電圧を印加した場合は、その印加した電圧がリファレンス電圧として使用されます。 外部リファレンスを使用する場合は、 $0.1\mu$ F のコンデンサを用いて $V_{REF}$ を AGND にバイパスしてください。                                                                         |

| 21              | DF/DCS                                         | V <sub>A</sub> V <sub>Float</sub>                     | クワッド・ステートのピン。 DF/DCS = V <sub>A</sub> の場合、出力データのフォーマットはオフセット・バイナリになり、入力クロックにデューティ・サイクル安定化機能が適用されます。 DF/DCS = AGND の場合、出力データのフォーマットは2の補数となり、入力クロックにデューティ・サイクル安定化機能が適用されます。 DF/DCS = V <sub>RM</sub> A または V <sub>RM</sub> B の場合、出力データのフォーマットは2の補数となり、入力クロックにはデューティ・サイクル安定化機能が適用されません。 DF/DCS がフローティングの場合、出力データのフォーマットはオフセット・バイナリとなり、入力クロックにはデューティ・サイクル安定化機能が適用されません。 |

| 13 5            | $ m V_{RP}A \ V_{RP}B$                         |                                                       | ハイ・インピーダンスのリファレンス電圧用バイパス・ピン。これらの                                                                                                                                                                                                                                                                                                                                    |

| 14              | $V_{RM}A$ $V_{RM}B$                            |                                                       | ピンのすべてとグラウンドの間に $0.1\mu F$ のコンデンサを各 $1$ 個ずつ挿入してください。 $V_{RP}A$ ピンと $V_{RN}A$ ピンとの間、 $V_{RP}B$ ピンと $V_{RN}B$ ピンとの間に $10\mu F$ のコンデンサを各 $1$ 個ずつ挿入してください。                                                                                                                                                                                                              |

| 12<br>6         | $egin{aligned} V_{RN}A\ V_{RN}B \end{aligned}$ | V <sub>A</sub> T V <sub>A</sub> T V <sub>A</sub> AGND | $V_{RM}A$ と $V_{RM}B$ は、温度的に安定した $1.5V$ リファレンスとして、 $1mA$ までの負荷に対応できます。 他のピンには負荷を接続しないでください。                                                                                                                                                                                                                                                                         |

| デジタル I/O        |                                                |                                                       |                                                                                                                                                                                                                                                                                                                                                                     |

| 60              | CLK                                            | \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\                | デジタル・クロック入力。この入力の周波数範囲は「電気的特性」の表に記載されており、性能は40MHzで保証されています。このクロック・パルスの立ち上がりエッジでアナログ入力信号がサンプリングされます。                                                                                                                                                                                                                                                                 |

| 22<br>41        | OEA<br>OEB                                     | AGND DGND                                             | OEAとOEB は出力イネーブル・ピンです。Low にすると、対応するデータ出力ピンがアクティブな状態に保持されます。 いずれかのピンを High にすると、対応する出力系統がハイ・インピーダンスになります。                                                                                                                                                                                                                                                            |

| ピン番号                        | シンボル             | 等価回路                           | 説明                                                                                                                                                                                                                                                                                                                                                                               |                                                                          |

|-----------------------------|------------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

| 59                          | PD               | ν <sub>Δ</sub> Υ               | PD はパワーダウン・モード制御用の入力ピン。このピンが High L<br>ベルのときはパワーダウン・モードになります。 Low レベルのときは<br>通常動作になります。                                                                                                                                                                                                                                                                                          |                                                                          |

| 11                          | MULTIPLEX        | AGND DGND                      | このピンを Low レベルにすると、"A" チャネル・データおよび "B チャネル・データがそれぞれのデータ出力ラインから出力されます (パラレル・モード)。<br>このピンを High レベルにすると、"A" "B" 両方のチャネル・データが "DA0:DA11" のデジタル出力ピンから出力されます (マルチプレクス・モード)。 DB0/ABb ピンはデータの同期に使用されます。                                                                                                                                                                                 |                                                                          |

| 24–29<br>34–39              | DA0-DA11         |                                | 各コンバータ系統の 12 ビット変換結果を構成するデジタル・データ                                                                                                                                                                                                                                                                                                                                                |                                                                          |

| 43–47<br>52–57              | DB1-DB11         | V <sub>DR</sub> V <sub>A</sub> | V <sub>DR</sub> V <sub>A</sub>                                                                                                                                                                                                                                                                                                                                                   | 出力ピン。DA0とDB0は出力ワードのLSBで、DA11とDB11たMSBです。出力レベルはTTL/CMOS互換です。最適負荷は<10pFです。 |

| 42                          | DB0/ABb          | DR GND                         | MULTIPLEX ピルを Low レベルにすると、DB0/ABb ピルは DB0 と<br>ンとして機能します。<br>MULTIPLEX ピルを High レベルにすると、DB0/ABb ピンからは<br>ABb 信号が出力され、この ABb 信号が多重化データの同期に使<br>用されます。 ABb 信号は、多重化された "A" "B" 両チャネルに追動して変化します。 "A" チャネル・データが有効のときは、ABb は<br>High レベルになります。 "B" チャネル・データが有効のときは、AB<br>は Low レベルになります。                                                                                               |                                                                          |

| アナログ電源                      | 1                |                                |                                                                                                                                                                                                                                                                                                                                                                                  |                                                                          |

| 9, 18, 19, 62,<br>63        | $V_{A}$          |                                | 正電圧のアナログ電源ピン。この各ピンは、共通の安定した+3.0 電源に接続してください。 各電源ピンと AGND の間のバイパスコンデンサとして、各ピンから 1cm 以内の所に 0.1 μF の単体コンランサを 1 つずつ配置し、各ピン共通の 10 μF のコンデンサも 1 つ配置してください。                                                                                                                                                                                                                             |                                                                          |

| 3, 8, 10, 17,<br>20, 61, 64 | AGND             |                                | アナログ電源のグラウンド・リターン。                                                                                                                                                                                                                                                                                                                                                               |                                                                          |

| デジタル電源                      | <u> </u>         |                                |                                                                                                                                                                                                                                                                                                                                                                                  |                                                                          |

| 33, 48                      | $V_{\mathrm{D}}$ |                                | 正電圧のデジタル電源ピン。このピンは、 $V_A$ と同じ安定した + 3.0 電源に接続し、 $10\mu F$ コンデンサと、電源ピンの $1cm$ 以内に配置した $0.1\mu F$ のコンデンサで、 $DGND$ にバイパスしてください。                                                                                                                                                                                                                                                     |                                                                          |

| 32, 49                      | DGND             |                                | デジタル電源のグラウンド・リターン。                                                                                                                                                                                                                                                                                                                                                               |                                                                          |

| 30, 51                      | $ m V_{DR}$      |                                | ADC12DL040 の出力ドライバ用の正電圧のドライバ電源ピン。 + $2.4 \text{V}_{\text{D}}$ の電源に接続してください。DR GND との間にバパス・コンデンサとして $0.1  \mu\text{F}$ のコンデンサを $1$ つ配置してください。 $V_{\text{A}}$ ピン、 $V_{\text{D}}$ ピンと異なる電源を使う場合は、このピンのバイパスコンデンサとしてさらに $10  \mu\text{F}$ のコンデンサを $1$ つ配置してください。 $V_{\text{DR}}$ の電圧は、 $V_{\text{D}}$ の電圧を超えないようにしてください。 $0.1  \mu$ のパイパス・コンデンサはすべて、電源ピンから $1 \text{cm}$ 以内に配置してください。 |                                                                          |

| 23, 31, 40, 50, 58          | DR GND           |                                | ADC12DL040 の出力ドライバ用のデジタル電源のグラウンド・リターン。システム・デジタル・グラウンドに接続してください。 ただし ADC12DL040 の DGND ピンや AGND ピンの近くには接続しないでください。 詳細はセクション 5「レイアウトとグラウンド構成」を参照ください。                                                                                                                                                                                                                              |                                                                          |

40% ~ 60%

#### 絶対最大定格 (Note 1、2)

本データシートには軍用・航空宇宙用の規格は記載されていません。 関連する電気的信頼性試験方法の規格を参照ください。

$V_{A}$ 、 $V_{D}$ 、 $V_{DR}$  4.2V  $|V_{A}-V_{D}|$  100mV 各入出力じの電圧 - 0.3V ~  $(V_{A}$ または

$V_D + 0.3V)$

各入力ピンの入力電流 (Note 3) ± 25mA パッケージの入力電流 (Note 3) ± 50mA T<sub>A</sub> = 25 でのパッケージ損失 Note 4を参照

ESD 耐性

人体モデル (Note 5) 2,500V マシン・モデル (Note 5) 250V

保存温度範囲 - 65 ~ + 150

ハンダ付けのプロセスは、National Semiconductor's Reflow Temperature Profile 規格に準拠してください。www.national.com/JPN/packaging/をご覧ください(Note 6)。

## 動作定格 (Note 1、2)

(DCS オフ)

- 40 T<sub>A</sub> + 85 動作温度範囲 + 2.7V ~ + 3.6V 電源電圧  $(V_A, V_D)$ 出力ドライバ用の電源 (V<sub>DR</sub>)  $+ 2.4V \sim V_D$ CLK, PD, OEA, OEB  $-0.05V \sim (V_D + 0.05V)$ アナログ入力ピン  $0V \sim 2.6V$  $0.5V \sim 2.0V$  $V_{CM}$ |AGND DGND| 100mV クロックのデューティ・サイクル (DCS オン) 20% ~ 80% クロックのデューティ・サイクル

# コンバータの電気的特性

特記のない限り、以下の仕様は、AGND = DGND = DR GND = 0V、 $V_A$  =  $V_D$  = + 3.0V、 $V_{DR}$  = + 2.5V、PD = 0V、外部  $V_{REF}$  = + 1.0V、 $f_{CLK}$  = 40MHz、 $f_{IN}$  = 10MHz、 $f_{I}$  = 10MHz  $f_{I}$  = 10MHz f

| Symbol                                  | Parameter                                            | Conditio                                                              | ns         | Typical   | Limits         | Units      |  |

|-----------------------------------------|------------------------------------------------------|-----------------------------------------------------------------------|------------|-----------|----------------|------------|--|

|                                         |                                                      |                                                                       |            | (Note 10) | (Note 10)      | (Limits)   |  |

| STATIC (                                | CONVERTER CHARACTERISTICS                            |                                                                       |            | ·         | 1 · · ·        |            |  |

|                                         | Resolution with No Missing Codes                     |                                                                       |            |           | 12             | Bits (min) |  |

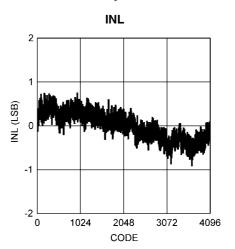

| INL                                     | Integral Non Linearity (Note 11)                     |                                                                       |            | ±0.8      | ± 2.6          | LSB (max)  |  |

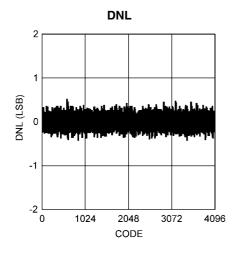

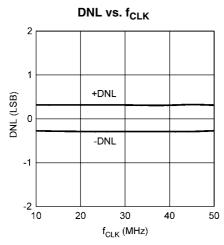

| DNL                                     | Differential Non Linearity                           |                                                                       |            | ±0.3      | +0.96,<br>-0.9 | LSB (max)  |  |

| PGE                                     | Positive Gain Error                                  |                                                                       |            | ±0.2      | +2.5,<br>-3.3  | %FS (max)  |  |

| NGE                                     | Negative Gain Error                                  |                                                                       |            | ±0.2      | ±3.6           | %FS (max)  |  |

| TC GE                                   | Gain Error Tempco                                    | $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +85^{\circ}\text{C}$ |            | 5         |                | ppm/°C     |  |

| V <sub>OFF</sub>                        | Offset Error (V <sub>IN</sub> + = V <sub>IN</sub> -) |                                                                       |            | 0.1       | ±0.8           | %FS (max)  |  |

| TC<br>V <sub>OFF</sub>                  | Offset Error Tempco                                  | -40°C ≤ T <sub>A</sub> ≤ +85°C                                        |            | 3         |                | ppm/°C     |  |

|                                         | Under Range Output Code                              |                                                                       |            | 0         | 0              |            |  |

|                                         | Over Range Output Code                               |                                                                       |            | 4095      | 4095           |            |  |

| REFERE                                  | NCE AND ANALOG INPUT CHARACT                         | TERISTICS                                                             |            | •         |                |            |  |

|                                         |                                                      |                                                                       |            | 1         | 0.5            | V (min)    |  |

| V <sub>CM</sub>                         | Common Mode Input Voltage                            |                                                                       |            | 1.5       | 2.0            | V (max)    |  |

| V <sub>RM</sub> A,<br>V <sub>RM</sub> B | Reference Output Voltage                             | Output load = 1 mA                                                    |            | 1.5       |                | ٧          |  |

|                                         | V <sub>IN</sub> Input Capacitance (each pin to       | V <sub>IN</sub> = 2.5 Vdc                                             | (CLK LOW)  | 8         |                | pF         |  |

| CIN                                     | GND)                                                 | + 0.7 V <sub>rms</sub>                                                | (CLK HIGH) | 7         |                | pF         |  |

|                                         | External Reference Voltage (Note                     |                                                                       | •          | 1.00      | 0.8            | V (min)    |  |

| $V_{REF}$                               | 13)                                                  |                                                                       |            | 1.00      | 1.2            | V (max)    |  |

|                                         | Reference Input Resistance                           |                                                                       |            | 1 1       |                | MΩ (min)   |  |

# コンバータの電気的特性(つづき)

特記のない限り、以下の仕様は、AGND = DGND = DR GND = 0V、 $V_A = V_D = +3.0$ V、 $V_{DR} = +2.5$ V、PD = 0V、外部  $V_{REF} = +1.0$ V、 $f_{CLK} = 40$ MHz、 $f_{IN} = 10$ MHz  $f_{IN} = 10$ M

| Symbol  | Parameter                        | Conditions                                                   | Typical<br>(Note 10) | Limits<br>(Note 10) | Units<br>(Limits) |

|---------|----------------------------------|--------------------------------------------------------------|----------------------|---------------------|-------------------|

| DYNAMIC | CONVERTER CHARACTERISTICS        |                                                              |                      |                     |                   |

| FPBW    | Full Power Bandwidth             | 0 dBFS Input, Output at -3 dB                                | 250                  |                     | MHz               |

|         |                                  | $f_{IN} = 1 \text{ MHz}, V_{IN} = -0.5 \text{ dBFS}$         | 69                   |                     | dB                |

| SNR     | Signal-to-Noise Ratio            | $f_{IN} = 10 \text{ MHz}, V_{IN} = -0.5 \text{ dBFS}$        | 69                   | 67.5                | dB (min)          |

| -       |                                  | $f_{IN} = 20 \text{ MHz}, V_{IN} = -0.5 \text{ dBFS}$        | 68.5                 | 66.5                | dB                |

|         |                                  | $f_{IN} = 1 \text{ MHz}, V_{IN} = -0.5 \text{ dBFS}$         | 68.5                 |                     | dB                |

| SINAD   | Signal-to-Noise and Distortion   | $f_{IN} = 10 \text{ MHz}, V_{IN} = -0.5 \text{ dBFS}$        | 68.5                 | 67                  | dB (min)          |

|         |                                  | $f_{IN} = 20 \text{ MHz}, V_{IN} = -0.5 \text{ dBFS}$        | 68.5                 | 66.5                | dB                |

|         |                                  | $f_{IN} = 1 \text{ MHz}, V_{IN} = -0.5 \text{ dBFS}$         | 11.1                 |                     | Bits              |

| ENOB    | Effective Number of Bits         | $f_{IN} = 10 \text{ MHz}, V_{IN} = -0.5 \text{ dBFS}$        | 11.1                 | 10.8                | Bits (min         |

|         |                                  | $f_{iN} = 20 \text{ MHz}, V_{iN} = -0.5 \text{ dBFS}$        | 11.1                 | 10.75               | Bits              |

|         |                                  | $f_{IN} = 1 \text{ MHz}, V_{IN} = -0.5 \text{ dBFS}$         | -82                  |                     | dB                |

| THD     | Total Harmonic Distortion        | $f_{IN} = 10 \text{ MHz}, V_{IN} = -0.5 \text{ dBFS}$        | -83                  | -75                 | dB (min)          |

|         |                                  | $f_{IN} = 20 \text{ MHz}, V_{IN} = -0.5 \text{ dBFS}$        | -83                  | -75                 | ₫B                |

|         |                                  | $f_{iN} = 1 \text{ MHz}, V_{iN} = -0.5 \text{ dBFS}$         | -88                  |                     | dB                |

| H2      | Second Harmonic Distortion       | $f_{1N} = 10 \text{ MHz}, V_{1N} = -0.5 \text{ dBFS}$        | -86                  | -76                 | dB (min)          |

|         |                                  | $f_{IN} = 20 \text{ MHz}, V_{IN} = -0.5 \text{ dBFS}$        | -86.5                | -75                 | dB                |

| ***     |                                  | $f_{IN} = 1$ MHz, $V_{IN} = -0.5$ dBFS                       | -86                  |                     | dB                |

| НЗ      | Third Harmonic Distortion        | $f_{iN} = 10 \text{ MHz}, V_{iN} = -0.5 \text{ dBFS}$        | -87                  | -77                 | dB (min)          |

|         |                                  | $f_{1N} = 20 \text{ MHz}, V_{1N} = -0.5 \text{ dBFS}$        | -86.5                | -76                 | dB                |

|         |                                  | $f_{1N} = 1 \text{ MHz}, V_{1N} = -0.5 \text{ dBFS}$         | 86                   |                     | dB                |

| SFDR    | Spurious Free Dynamic Range      | $f_{IN} = 10 \text{ MHz}, V_{IN} = -0.5 \text{ dBFS}$        | 85                   | 76                  | dB (min)          |

|         |                                  | $f_{IN} = 20 \text{ MHz}, V_{IN} = -0.5 \text{ dBFS}$        | 84                   | 75                  | dB                |

| IMD     | Intermodulation Distortion       | $f_{IN} = 9.6 \text{ MHz}$ and 10.2 MHz,<br>each = -6.5 dBFS | -75                  |                     | dBFS              |

| INTER-C | HANNEL CHARACTERISTICS           | each = -0.5 dbi 5                                            |                      |                     |                   |

| INTER-O | Channel — Channel Offset Match   |                                                              | ±0.3                 |                     |                   |

|         | Channel — Channel Gain Match     |                                                              | ±4                   |                     | %FS               |

|         | Original Original Original Mator | 10 MHz Tested Channel;                                       | 90                   |                     | dB (min)          |

|         | Crosstalk                        | 20 MHz Other Channel 20 MHz Tested Channel;                  | 90                   |                     | dB· (min)         |

|         |                                  | 10 MHz Other Channel                                         | 30                   |                     | GD (IIIII)        |

www.national.com/jpn/

#### DC およびロジックの電気的特性

特記のない限り、以下の仕様は、AGND = DGND = DR GND = 0V、 $V_A$  =  $V_D$  = + 3.0V、 $V_{DR}$  = + 2.5V、PD = 0V、 $V_{REF}$  = + 1.0V、 $f_{CLK}$  = 40MHz、 $f_{IN}$  = 10MHz、 $t_r$  =  $t_f$  = 2ns、 $C_L$  = 15pF/ ピン、デューティ・サイクル安定化機能オン、パラレル出力モードに対して適用されます。 太字表記のリミット値は  $T_J$  =  $T_{MIN}$  ~  $T_{MAX}$  に対して適用され、その他のリミット値は  $T_J$  = 25 に対して適用されます (Note 7、8、9)。

| Symbol              | Parameter                              | Conditions                                             |                                                | Typical<br>(Note 10) | Limits<br>(Note 10) | Units<br>(Limits) |

|---------------------|----------------------------------------|--------------------------------------------------------|------------------------------------------------|----------------------|---------------------|-------------------|

| CLK, PD             | , OEA, OEB DIGITAL INPUT CHARA         | CTERISTICS                                             |                                                |                      |                     |                   |

| $V_{IN(1)}$         | Logical "1" Input Voltage              | $V_{D} = 3.6V$                                         |                                                |                      | 2.0                 | V (min)           |

| V <sub>IN(0)</sub>  | Logical "0" Input Voltage              | $V_{\rm D} = 3.0 V$                                    |                                                |                      | 1.0                 | V (max)           |

| <sub>IN(1)</sub>    | Logical "1" Input Current              | $V_{IN} = 3.3V$                                        |                                                | 10                   |                     | μΑ                |

| I <sub>IN(0)</sub>  | Logical "0" Input Current              | $V_{IN} = 0V$                                          |                                                | -10                  |                     | μΑ                |

| C <sub>IN</sub>     | Digital Input Capacitance              |                                                        |                                                | 5                    |                     | pF                |

| DA0-DA              | 11, DB0-DB11 DIGITAL OUTPUT CH         | IARACTERISTICS                                         |                                                | •                    |                     |                   |

| ·                   | Legisal "1" Output Valtage             | 0.5 m                                                  | $V_{DR} = 2.5V$                                |                      | 2.3                 | V (min)           |

| $V_{OUT(1)}$        | Logical "1" Output Voltage             | $I_{OUT} = -0.5 \text{ mA}$ $V_{DB} = 3V$              |                                                |                      | 2.7                 | V (min)           |

| V <sub>OUT(0)</sub> | Logical "0" Output Voltage             | $I_{OUT} = 1.6 \text{ mA}, V_{DR} =$                   | 3V                                             |                      | 0.4                 | V (max)           |

|                     | TRI CTATE® Output Output               | $V_{OUT} = 2.5V \text{ or } 3.3V$<br>$V_{OUT} = 0V$    |                                                | 100                  |                     | nA                |

| l <sub>oz</sub>     | TRI-STATE® Output Current              |                                                        |                                                | -100                 |                     | nA                |

| +l <sub>sc</sub>    | Output Short Circuit Source<br>Current | V <sub>OUT</sub> = 0V                                  |                                                | -20                  |                     | mA                |

| -I <sub>sc</sub>    | Output Short Circuit Sink Current      | V <sub>OUT</sub> = V <sub>DR</sub>                     | V <sub>OUT</sub> = V <sub>DB</sub>             |                      |                     | mA                |

| Соит                | Digital Output Capacitance             | 50.                                                    |                                                | 5                    |                     | pF                |

| POWER               | SUPPLY CHARACTERISTICS                 |                                                        |                                                |                      |                     |                   |

|                     | AI Owner I Owner at                    | PD Pin = DGND, V <sub>REE</sub>                        | = V <sub>A</sub>                               | 58                   | 72                  | mA (max)          |

| l <sub>A</sub>      | Analog Supply Current                  | PD Pin = V <sub>D</sub>                                |                                                | 12                   |                     | mA                |

| ı                   | Digital Cumply Current                 | PD Pin = DGND                                          |                                                | 12                   | 14                  | mA (max)          |

| I <sub>D</sub>      | Digital Supply Current                 | PD Pin = $V_D$ , $f_{CLK} = 0$                         | )                                              | 0                    |                     | mA                |

| ı                   | Digital Output Supply Current          | PD Pin = DGND, C <sub>L</sub> =                        | 5 pF (Note 14)                                 | 12                   |                     | mA                |

| I <sub>DR</sub>     | Digital Output Supply Surrent          | PD Pin = V <sub>D</sub> , f <sub>CLK</sub> = 0         |                                                | 0                    |                     | mA                |

|                     | Total Power Consumption                | PD Pin = DGND, C <sub>L</sub> =                        | PD Pin = DGND, C <sub>L</sub> = 5 pF (Note 15) |                      | 258                 | mW (max           |

|                     | Total Tower Condumption                | PD Pin = V <sub>D</sub>                                |                                                | 36                   |                     | mW                |

| PSRR1               | Power Supply Rejection Ratio           | Rejection of Full-Scale $V_A = 2.7V \text{ vs. } 3.6V$ | Error with                                     | 54                   |                     | dB                |

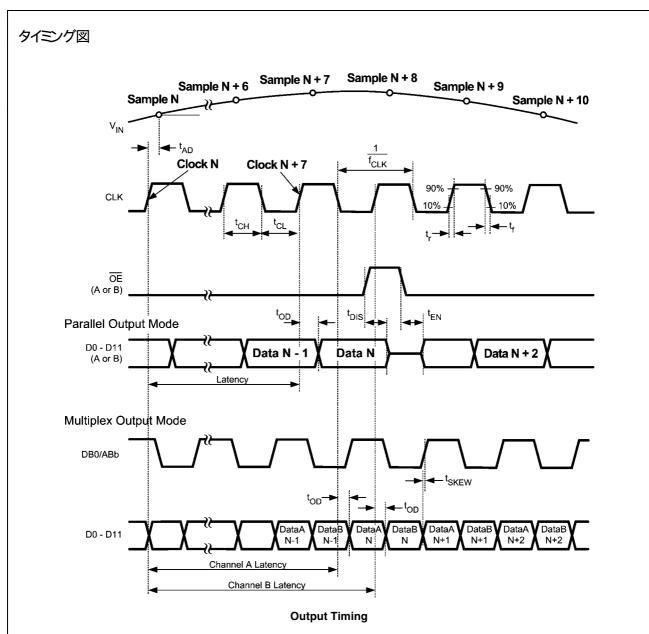

## AC 電気的特性

特記のない限り、以下の仕様は、AGND = DGND = DR GND = 0V、 $V_A = V_D = +3.0$ V、 $V_{DR} = +2.5$ V、PD = 0V、外部  $V_{REF} = +1.0$ V、 $f_{CLK} = 40$ MHz、 $f_{IN} = 10$ MHz  $f_{IN} = 10$ M

| Symbol                          | Parameter                      | Conditions                | Typical<br>(Note 10) | Limits<br>(Note 10) | Units<br>(Limits) |

|---------------------------------|--------------------------------|---------------------------|----------------------|---------------------|-------------------|

| f <sub>CLK</sub> 1              | Maximum Clock Frequency        |                           |                      | 40                  | MHz (min)         |

| f <sub>CLK</sub> <sup>2</sup>   | Minimum Clock Frequency        |                           | 10                   |                     | MHz               |

| t <sub>CH</sub>                 | Clock High Time                | Duty Cycle Stabilizer On  | 12.5                 | 5 ´                 | ns (min)          |

| t <sub>CL</sub>                 | Clock Low Time                 | Duty Cycle Stabilizer On  | 12.5                 | 5                   | ns (min)          |

| t <sub>r</sub> , t <sub>f</sub> | Clock Rise and Fall Times      | Duty Cycle Stabilizer On  | 2                    | 4                   | ns (max)          |

| t <sub>CH</sub>                 | Clock High Time                | Duty Cycle Stabilizer Off | 12.5                 | 10                  | ns (min)          |

| t <sub>CL</sub>                 | Clock Low Time                 | Duty Cycle Stabilizer Off | 12.5                 | 10                  | ns (min)          |

| t <sub>r</sub> , t <sub>f</sub> | Clock Rise and Fall Times      | Duty Cycle Stabilizer Off | 2                    | ·                   | ns (max)          |

|                                 | Conversion Latency             | Parallel mode             |                      | -                   | Clock             |

| t <sub>CONV</sub>               | Conversion Latericy            | Parallel mode             |                      | '                   | Cycles            |

|                                 | Data Output Delay after Rising | Parallel mode             | 6.0                  | 3.5                 | ns (min)          |

| t <sub>OD</sub>                 | Clock Edge                     |                           | 6.0                  | 9.6                 | ns (max)          |

#### AC 電気的特性(つづき)

特記のない限り、以下の仕様は、AGND = DGND = DR GND = 0V、 $V_A = V_D = + 3.0V$ 、 $V_{DR} = + 2.5V$ 、PD = 0V、外部  $V_{REF} = + 1.0V$ 、 $f_{CLK} = 40$ MHz、 $f_{IN} = 10$ MHz、 $f_r = f_f = 2$ ns、 $C_L = 15$ pF/ ピン、デューティ・サイクル安定化機能オン、パラレル出力モードに対して適用されます。 太字表記のリミット値は  $T_J = T_{MIN} \sim T_{MAX}$  に対して適用され、その他のリミット値は  $T_J = 25$  に対して適用されます (Note 7、8、9、12)。

| Symbol            | Parameter                              | Conditions                                                                                            | Typical<br>(Note 10) | Limits<br>(Note 10) | Units<br>(Limits) |

|-------------------|----------------------------------------|-------------------------------------------------------------------------------------------------------|----------------------|---------------------|-------------------|

| t <sub>CONV</sub> | Conversion Latency                     | Multiplex mode, Channel A                                                                             |                      | 7.5                 | Clock<br>Cycles   |

| t <sub>CONV</sub> | Conversion Latency                     | Multiplex mode, Channel B                                                                             |                      | 8                   | Clock<br>Cycles   |

| +                 | Data Output Delay after Clock          | Multipley made                                                                                        | 6.0                  | 3.5                 | ns (min)          |

| t <sub>od</sub>   | Edge                                   | Multiplex mode                                                                                        | 0.0                  | 9                   | ns (max)          |

| t <sub>SKEW</sub> | ABb to Data Skew                       |                                                                                                       | ±0.5                 |                     | ns (max)          |

| t <sub>AD</sub>   | Aperture Delay                         |                                                                                                       | 2                    |                     | ns                |

| t <sub>AJ</sub>   | Aperture Jitter                        |                                                                                                       | 1.2                  |                     | ps rms            |

| t <sub>DIS</sub>  | Data outputs into Hi-Z Mode            |                                                                                                       | 10                   |                     | ns                |

| t <sub>EN</sub>   | Data Outputs Active after Hi-Z<br>Mode |                                                                                                       | 10                   |                     | ns                |

| t <sub>PD</sub>   | Power Down Mode Exit Cycle             | 1.0 μF on pins 4, 14; 0.1 μF on pins<br>5,6,12,13; 10 μF between pins 5, 6<br>and between pins 12, 13 | 1                    |                     | μs                |

- Note 1: 絶対最大定格とは、デバイスに破壊が発生する可能性のあるリミツ・値をいいます。動作定格とはデバイスが機能する条件を示しますが、特定の性能リミツ・値を示すものではありません。保証された仕様、および試験条件については「電気的特性」を参照してください。保証された仕様は「電気的特性」に記載されている試験条件でのみ適用されます。また、記載の試験条件以外でデバイスを動作させると、性能特性が低下することがあります。

- Note 2: 特記のない限り、すべての電圧は GND = AGND = DGND = 0V を基準にして測定されています。

- Note 3: いずれかのピンで入力電圧が電源電圧を超えた場合  $(V_{\rm IN} < {\rm AGND}$  または  $V_{\rm IN} > V_{\rm A}$  の場合 )、そのピンの入力電流を  $25{\rm mA}$  以下に制限しなければ なぼせん。 パッケージの最大入力電流定格  $(50{\rm mA})$  により、電源電圧を超えて  $25{\rm mA}$  の電流を流すことができるピンの数は 2 本に制限されます。

- Note 4: 本デバイスの絶対最大接合部温度  $(T_{J}max)$  は 150 です。最大許容電力消費は  $T_{J}max$ 、接合部と周囲温度間の熱抵抗  $(T_{J}A)$ 、周囲温度  $(T_{A})$  によって規定され、式  $P_{D}MAX$  =  $(T_{J}max)$  によって計算できます。 64 ピン TQFP の場合は、  $T_{J}A$  が 50 /W であるため、  $P_{D}MAX$  は、 25 では 2W となり、最大動作周囲温度 85 では 800mW となます。通常動作時の本デバイスの消費電力は代表値で約 250mW (消費電力の代表値 210mW + TTL 出力負荷時の消費電力 40mW) になます。 上記の最大許容消費電力の値に達するのは、デバイスが何らかの異常な状態で動作しているときのみです (例えば、入力ピンまたは出力ピンを電源電圧を超えて駆動させている場合や電源の極性を逆転させている場合など)。 当然、このような条件になることは解けなければなません。

- Note 5: 人体モデルの場合には、100pF のコンデンサから直列抵抗 1.5k を通して各ピンに放電させます。 マシン・モデルでは 220pF のコンデンサから直列抵抗 0 を通して、各ピンに放電させます。

- Note 6: リフロー温度プロファイルは、鉛フリー・パッケージの場合と、その他のパッケージの場合で異なります。

- Note 7: 以下に示すように、各人力ピンは保護されています。 Note 3 に従って電流制限を行うと、入力電圧が  $V_A$  を上回った場合や GND を下回った場合でも 本デバイスが損傷を受けることはありません。 しかし、入力電圧が  $V_A$  + 100 mV を上回った場合もしくは GND 100 mV を下回った場合は A/D 変換に 誤差を生じる可能性があります。 例えば、 $V_A$  が + 3.3 V の場合には、変換精度を確保するためにはアナログ入力のフルスケールは + 3.4 V 以下にしなければなりません。

- Note 8: 精度を保証するために、各電源電圧差を $|V_{\rm A}-V_{\rm D}|$   $100{

m mV}$  にし、かつ各電源ピンごとのバイバス・コンデンサが必要となります。

- Note 9:  $V_{REF}$  = + 1.0V ( $2V_{P-P}$  差動入力 ) のテスト条件で、12 ビットの LSB は  $488\,\mu V$  になます。

- Note 10: 代表値 (Typical) は、T<sub>J</sub> = 25 で得られる最も標準的な数値です。 テスト・リミット値はナショナル セミコンダクターの平均出荷品質レベル (AOQL) に基づき保証されます。

- Note 11: 積分非直線性 (INL) は LSB 単位で表され、正と負のフルスケールを通る直線からのアナログ値の偏差として定義されます。

- Note 12: タイミング特性は、TTL ロジック・レベル (立ち下が)エッジが  $V_{\rm IL}$  = 0.4V、立ち上が)エッジが  $V_{\rm IH}$  = 2.4V) でテストされます。

- Note 13: 最適な性能は、リファレンス入力が 0.8V ~ 1.2V の場合に得られます。外部リファレンスを使用するアプリケーションには LM4051CIM3-ADJ (SOT-23 パッケージ)を推奨します。

- Note 14:  $I_{DR}$  とは、出力ドライバのスイッチング処理に消費される電流のことです。この値を決める主な要素は、出力ピンの負荷容量、電源電圧の  $V_{DR}$ 、出力のスイッチング・レート(信号に依存)です。  $I_{DR}$  は、 $V_{DR}$  ( $C_0 \times f_0 + C_1 \times f_1 + ... C_{11} \times f_{11}$ ) の式で計算されます。  $V_{DR}$  は出力ドライバ用の電源電圧、 $C_0$  は当該出力ピンの総負荷容量、 $f_0$  は当該出力ピンの平均スイッチング周波数です。

- **Note 15:** I<sub>DR</sub> は含まれていません。 Note 14 を参照ください。

#### 用語の定義

アパーチャ・ディレイ (APERTURE DELAY) は、クロック・パルスが立ち上がってから入力信号が取り込まれるか保持されるかまでの時間です。

アパーチャ・ジッタ(アパーチャ不確定性) (APERTURE JITTER) は、サンプルとサンプルの間のアパーチャ・ディレイのばらつきです。アパーチャ・ジッタは出力のノイズとして現れます。

クロック・デューティ・サイクル (DUTY CYCLE) とは、繰り返し デジタル波形の 1 周期に対する High 期間の割合です。 本仕様 は、A/D コンバータのクロック入力信号に対して適用されます。

コモンモード電圧 (COMMON MODE VOLTAGE: V<sub>CM</sub>) とは A/D コンバータの両方の入力ピンに印加される共通の DC 電圧です。

変換レイテンシ (CONVERSION LATENCY) は、変換開始から その変換データが出力ドライバ段に現れるまでの期間をクロック・ サイクル数で表したものです。所定のサンプリングに対するデータ は、そのサンプリングが行われた後、パイプライン・ディレイに出 カディレイを加算した後に出力ピンに得られます。新しいデータは クロック・サイクル毎に得られますが、その出力データはパイプライ ン・ディレイ分の変換遅延があります。

クロストーク (CROSSTALK) とは、1 つのチャネルから別のチャネルへエネルギーが結合することです。

微分非直線性 (DIFFERENTIAL NON-LINEARITY: DNL) は、ILSB としての理想的なステップ・サイズからの最大偏差として表されます。

有効ビット数 (EFFECTIVE NUMBER OF BITS: ENOB) は、信号 /( ノイズ+ 歪み )または SINAD のもう1 つの規定方法です。 ENOB は (SINAD - 1.76)/6.02 として定義され、この値のビット数を持つ完全な A/D コンバータと等価なコンバータであることを意味します。

フルパワー帯域幅 (FULL POWER BANDWIDTH) は、フルスケール入力に対して再現される出力の基本周波数成分が低周波数帯域の値に対して 3dB 落ちる周波数として測定されます。

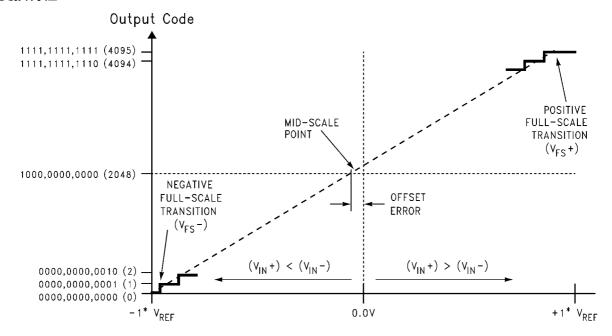

ゲイン誤差 (GAIN ERROR) は、伝達関数の理想カーブからの偏差です。 次の式で計算できます。

ゲイン誤差=正側フルスケール誤差 - 負側フルスケール誤差 ゲイン誤差は、次のように、正のゲイン誤差 (PGE) と負のゲイン 誤差 (NGE) とで表現することもできます。

PGE = 正側フルスケール誤差 - オフセット誤差 NGE = オフセット誤差 - 負側フルスケール誤差

ゲイン誤差マッチング (GAIN ERROR MATCHING) とは、2 つのコンバータ間のゲイン誤差の差を、コンバータの平均ゲインで除した値です。

積分非直線性 (INTEGRAL NON LINEARITY: INL) は、ゼロスケール (最初のコード遷移の 1/2LSB 下) から正のフルスケール (最後のコード遷移の 1/2LSB 上)まで引いた直線からそれぞれ 個々のコードとの偏差として表されます。この直線から任意のコードとの偏差は、各コード値の中央から測定します。

混変調歪み (INTERMODULATION DISTORTION: IMD) は、A/Dコンバータの入力に2つの近接した周波数を同時に入力し、結果として作り出される追加のスペクトラル成分です。 元の周波数のトータル・パワーに対する混変調成分のパワーの比として定義されます。 IMD は通常 dBFS で表されます。

LSB (LEAST SIGNIFICANT BIT) は、全ビットのうち最下位または重み付けの最も小さいビットです。 この値は  $V_{FS}/2^n$  として表されます。 " $V_{FS}$ " はフルスケール入力電圧、"n" は A/D コンバータの分解能 (ビット) です。

ミッシング・コード (MISSING CODE) は、A/D コンバータから出力されることのない出力コードです。 ADC12DL040 は、ミッシング・コードの発生しないことが保証されています。

MSB (MOST SIGNIFICANT BIT) は、全ビットのうちの最上位または重み付けの最も大きいビットです。 MSB の値はフルスケールの半分です。

負側フルスケール誤差 (NEGATIVE FULL SCALE ERROR)とは、最初のコード遷移が生じる実際の値と、負側フルスケールから 1/2LSB 高いところにある理想値との差です。

オフセット誤差 (OFFSET ERROR) とは、コード 2047 から 2048 への遷移を発生させるために必要な、2 つの入力電圧の差  $[(V_{\rm IN}+)-(V_{\rm IN}-)]$ です。

出力ディレイ (OUTPUT DELAY) は、クロック入力の立ち上がり エッジから出力ピンにアップデートされたデータが現われるまでの 遅延時間です。

オーバーレンジ・リカバリ時間 (OVER RANGE RECOVERY TIME) とは、 $V_{\rm IN}$  が通常入力レンジ外のある規定 I された電圧から、通常入力レンジ内の規定された電圧に変わったあとに、コンバータが定格精度で変換を行うようになるまでの時間です。

パイプライン・ディレイ **(PIPELINE DELAY: LATENCY)** については「変換レイテンシ」(CONVERSION LATENCY) を参照ください。

正側フルスケール誤差**(POSITIVE FULL SCALE ERROR)**は、最後のコード遷移点の実測値と(正側フルスケール - 1.5LSB)の理想値とのずれです。

電源電圧除去比 (POWER SUPPLY REJECTION RATIO: PSRR) は、電源電圧の変動を A/D コンバータでどの程度除去できるかを表したものです。 ADC12DL040 では、直流電源電圧の変動によって生じるフルスケール誤差の変動率を PSRR1 で表します。単位は dB です。また PSRR2 は、電源電圧に重畳しているノイズ成分に対して、出力の変化の割合を示した値です。

信号 / ノイズ比 (SIGNAL TO NOISE RATIO: SNR) は、クロック信号の 1/2 以下の周波数における、歪みと DC 成分を除いたその他すべてのスペクトラル成分の実効値に対する入力信号の実効値の比で、dB で表されます。

信号 / ( ノイズ + 歪み ) 比 (SIGNAL TO NOISE PLUS DISTORTION RATIO: S/(N + D) または SINAD) は、クロック 信号の 1/2 以下の周波数における、歪みを含め DC 成分を除いたその他すべてのスペクトラル成分の実効値に対する入力信号の実効値の比として表されます。

スプリアスフリー・ダイナミック・レンジ (SPURIOUS FREE DYNAMIC RANGE: SFDR) は、入力信号の実効値に対するピーク・スプリアス信号との差で、dB で表されます。ここで言うピーク・スプリアス信号とは、出力スペクトラムに現われる任意のスプリアス信号であり、入力に現われるものではありません。

全高調波歪み (TOTAL HARMONIC DISTORTION: THD) は、2 次から 10 次までの歪み成分の実効値の総和に対する入力信号の実効値 (rms 値) の比で、dB で表されます。全高調波歪みTHD は次式から求めます。

THD = 20 x log

$$\sqrt{\frac{f_2^2 + \dots + f_{10}^2}{f_1^2}}$$

$f_1$  は基本周波数 ( 出力 ) パワーの実効値 (RMS 値 ),  $f_2$  から  $f_{10}$  は出力スペクトラムに現れる高調波のうち 2 次から 10 次までの高調波のパワーです。

第 2 次高調波歪み (2ND HARM) は、出力に現れる入力周波数の RMS パワーと 2 次高調波レベルのパワーとの差を dB で表した値です。

第 3 次高調波歪み (3RD HARM) は、出力に現れる入力周波数の RMS パワーと 3 次高調波レベルのパワーとの差を dB で表した値です。

# 变換特性

Analog Input Voltage  $(V_{IN}+) - V_{IN}-)$

FIGURE 1. Transfer Characteristic

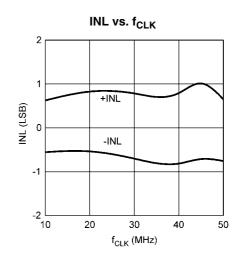

# 代表的な性能特性 (DNL、INL)

特記のない限り、以下の仕様は、AGND = DGND = DR GND = 0V、 $V_A$  =  $V_D$  = + 3.0V、 $V_{DR}$  = + 2.5V、PD = 0V、 $V_{REF}$  = + 1.0V、 $f_{CLK}$  = 40MHz、 $f_{IN}$  = 0、 $t_r$  =  $t_f$  = 2ns、 $C_L$  = 15pF/ ピン、デューティ・サイクル安定化機能オン、パラレル出力モードに対して適用されます。太字表記のリミット値は $T_J$  =  $T_{MIN}$  で  $T_{MAX}$  に対して適用され、その他のリミット値は $T_J$  = 25 に対して適用されます。

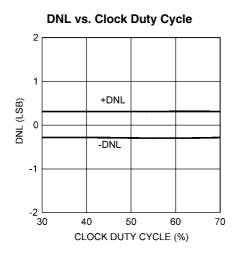

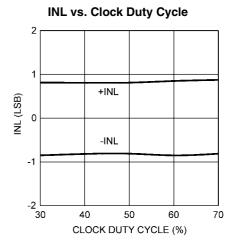

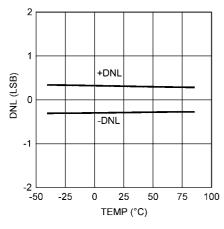

# 代表的な性能特性 (DNL、INL) (つづき)

特記のない限り、以下の仕様は、AGND = DGND = DR GND = 0V、 $V_A$  =  $V_D$  = + 3.0V、 $V_{DR}$  = + 2.5V、PD = 0V、 $V_{REF}$  = + 1.0V、 $f_{CLK}$  = 40MHz、 $f_{IN}$  = 0、 $t_r$  =  $t_f$  = 2ns、 $C_L$  = 15pF/ ピン、デューティ・サイクル安定化機能オン、パラレル出力モードに対して適用されます。太字表記のリミット値は  $T_J$  =  $T_{MIN}$  で  $T_{MAX}$  に対して適用され、その他のリミット値は  $T_J$  = 25 に対して適用されます。

**DNL vs. Temperature**

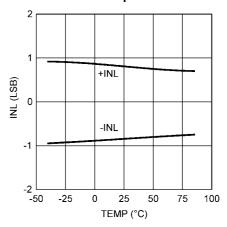

INL vs. Temperature

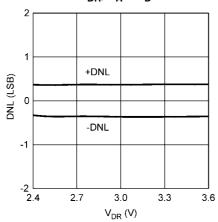

DNL vs.  $V_{DR}$ ,  $V_A = V_D = 3.6V$

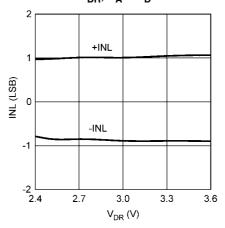

INL vs.  $V_{DR}$ ,  $V_{A} = V_{D} = 3.6V$

特記のない限り、以下の仕様は、AGND = DGND = DR GND = 0V、 $V_A = V_D = +3.0$ V、 $V_{DR} = +2.5$ V、PD = 0V、 $V_{REF} = +1.0$ V、 $f_{CLK} = 40$ MHz、 $f_{IN} = 20$ MHz、 $t_r = t_f = 2$ ns、 $C_L = 15$ pF/ピン、デューティ・サイクル安定化機能オン、パラレル出力モードに対して適用されます。 太字表記のリミット値は  $\mathbf{T_J} = \mathbf{T_{MIN}} \sim \mathbf{T_{MAX}}$ に対して適用され、その他のリミット値は  $T_J = 25$  に対して適用されます。

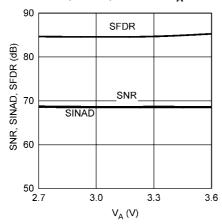

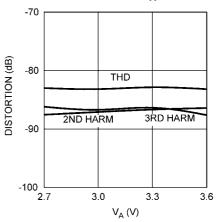

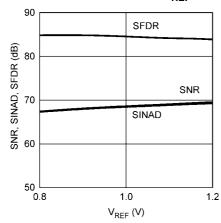

SNR, SINAD, SFDR vs. VA

Distortion vs. V<sub>A</sub>

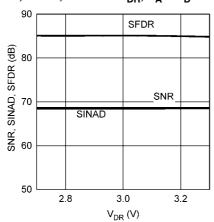

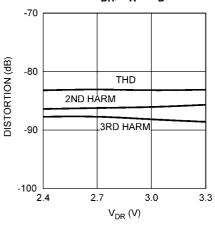

SNR,SINAD,SFDR vs.  $V_{DR}$ ,  $V_{A} = V_{D} = 3.6V$

Distortion vs.  $V_{DR}$ ,  $V_A = V_D = 3.6V$

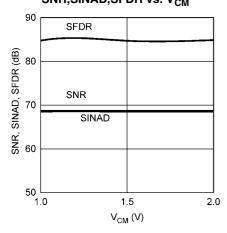

SNR,SINAD,SFDR vs. V<sub>CM</sub>

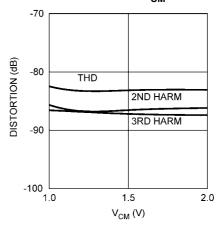

Distortion vs. V<sub>CM</sub>

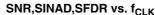

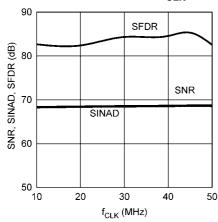

特記のない限り、以下の仕様は、AGND = DGND = DR GND = 0V、 $V_A$  =  $V_D$  = + 3.0V、 $V_{DR}$  = + 2.5V、PD = 0V、 $V_{REF}$  = + 1.0V、 $f_{CLK}$  = 40MHz、 $f_{IN}$  = 20MHz、 $f_T$  =  $f_T$  = 2ns、 $f_T$  = 15pF/ ピン、デューティ・サイクル安定化機能オン、パラレル出力モードに対して適用されます。 太字表記のリミット値は  $f_T$  =  $f_T$  に対して適用され、その他のリミット値は  $f_T$  =  $f_T$  に対して適用されます。

# Distortion vs. f<sub>CLK</sub>

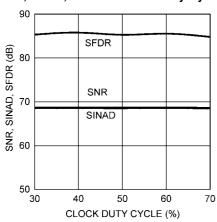

#### SNR, SINAD, SFDR vs. Clock Duty Cycle

**Distortion vs. Clock Duty Cycle**

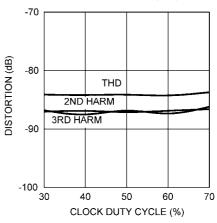

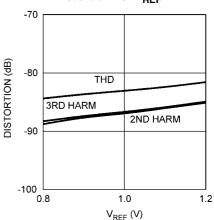

## SNR, SINAD, SFDR vs. V<sub>REF</sub>

#### Distortion vs. V<sub>REF</sub>

特記のない限り、以下の仕様は、AGND = DGND = DR GND = 0V、 $V_A = V_D = +3.0V$ 、 $V_{DR} = +2.5V$ 、PD = 0V、 $V_{REF} = +1.0V$ 、 $f_{CLK} = 40$ MHz、 $f_{IN} = 20$ MHz、 $t_r = t_f = 2$ ns、 $C_L = 15$ pF/ピン、デューティ・サイクル安定化機能オン、パラレル出力モードに対して適用されます。 太字表記のリミット値は  $\mathbf{T_J} = \mathbf{T_{MIN}} \sim \mathbf{T_{MAX}}$ に対して適用され、その他のリミット値は  $T_J = 25$  に対して適用されます。

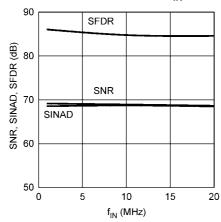

SNR,SINAD,SFDR vs. f<sub>IN</sub>

Distortion vs. f<sub>IN</sub>

-70

-70

-70

3RD HARM

2ND HARM

-100

0 5 10 15 20

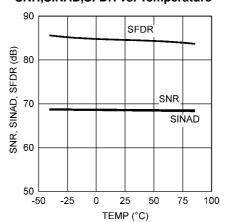

SNR, SINAD, SFDR vs. Temperature

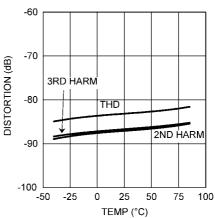

Distortion vs. Temperature

$f_{IN}$  (MHz)

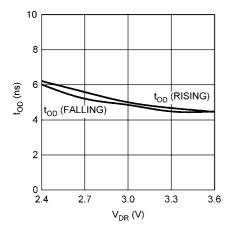

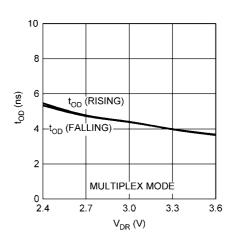

$t_{OD}$  vs.  $V_{DR}$ ,  $V_{A} = V_{D} = 3.6V$ Parallel Output Mode

$t_{OD}$  vs.  $V_{DR}$ ,  $V_{A} = V_{D} = 3.6V$ Multiplex Output Mode

特記のない限り、以下の仕様は、AGND = DGND = DR GND = 0V、 $V_A$  =  $V_D$  = + 3.0V、 $V_{DR}$  = + 2.5V、PD = 0V、 $V_{REF}$  = + 1.0V、 $f_{CLK}$  = 40MHz、 $f_{IN}$  = 20MHz、 $t_r$  =  $t_f$  = 2ns、 $C_L$  = 15pF/ ピン、デューティ・サイクル安定化機能オン、パラレル出力モードに対して適用されます。 太字表記のリミット値は  $T_J$  =  $T_{MIN}$  ~  $T_{MAX}$  に対して適用され、その他のリミット値は  $T_J$  = 25 に対して適用されます。

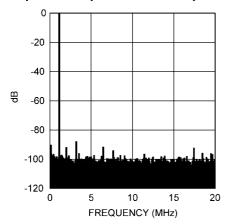

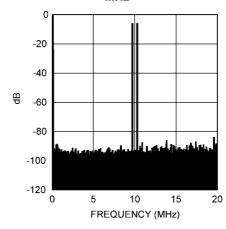

## Spectral Response @ 1 MHz Input

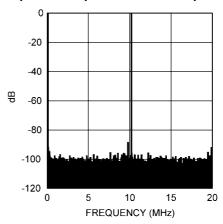

## Spectral Response @ 10 MHz Input

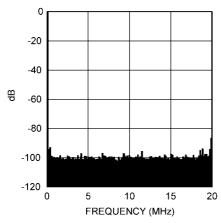

#### Spectral Response @ 20 MHz Input

# Intermodulation Distortion, $f_{IN}1=9.6$ MHz, $f_{IN}2=10.2$ MHz

#### 機能説明

ADC12DL040 は+ 3.0V 単電源で動作します。パイプライン型アーキテクチャを採用し、かつ誤差補正回路を内蔵しているため、性能が最大限に発揮されます。差動アナログ入力信号が12ビットのデジタル信号に変換されます。リファレンス電圧には外部リファレンスか、1.0V または0.5V の安定した内部リファレンスを使います。外部リファレンスはチップ内でバッファされるため、リファレンス・ピンの駆動は容易です。

出力ワード・レートはクロック周波数と同じです。範囲は 10MSPS から 40MSPS (代表値)までで、40MSPS で全仕様を満たします。両方のチャネルのアナログ入力はクロックの立ち下がリエッジで取り込まれ、サンプリングされたデジタル・データは、パイプライン構造のため 7 クロック・サイクル遅れて出力されます。デューティ・サイクル安定化および出力データのフォーマットは、クワッド・ステートの機能ピン DF/DCS によって選択可能です。出力データは、オフセット・バイナリまたは2の補数のいずれかに設定できます。

パワーダウン・ピン (PD) が High レベルの間は消費電力が 36mW まで下がはす。

#### アプリケーション情報

#### 1.0 動作条件

ADC12DL040 の動作条件としては次の各値に従うことを推奨します。

2.7V  $V_A$  3.6V

$V_D = V_A$

$2.4V V_{DR} V_{A}$

10MHz f<sub>CLK</sub> 40MHz

0.8V V<sub>REF</sub> 1.2V (外部リファレンスの場合)

0.5V  $V_{CM}$  2.0V

#### 1.1 アナログ入力

内部リファレンスの選択、または外部からのリファレンス入力を目的としたリファレンス入力ピン  $V_{REF}$  を備えています。 ADC12DL040は 2 組のアナログ信号入力ペアを備え、 $V_{IN}A$  + と $V_{IN}A$  - が一方のコンバータ、 $V_{IN}B$  + と $V_{IN}B$  - が他方のコンバータです。 それぞれの入力ペアは差動入力ペアを構成します。

#### 1.2 基準電圧ピン

ADC12DL040 は内部リファレンス電圧 1.0V または 0.5V、あるいは外部リファレンス電圧 1.0V で動作するよう設計されていますが、外部リファレンス電圧 0.8V ~ 1.2V の範囲であれば問題なく動作します。 基準電圧を下げると ADC12DL040 の信号 / ノイズ比(SNR) が小さくなります。 リファレンス電圧(および入力信号振幅)を 1.2V を超えて大きくすると、特に入力周波数が高い場合に、フルスケール入力の THD 性能を低下させる可能性があります。

リファレンス電圧と入力信号に対するすべてのグラウンドは、グラウンド経路に流れるノイズ電流の影響を抑えるため、アナログ・グラウンド・プレーンに対して 1 点アースで接続するのが極めて重要になります。

パイパス用に 6 本のリファレンス・バイパス・ピン  $(V_{RP}A, V_{RM}A, V_{RN}A, V_{RP}B, V_{RM}B, V_{RN}B)$  が設けられています。 これらの ピンのすべてとグラウンドの間に  $0.1\,\mu\text{F}$  のコンデンサを 1 つずつ挿入してください。 Figure 4 に示したように、 $V_{RP}A$  ピンと  $V_{RN}A$  ピンとの間、 $V_{RP}B$  ピンと  $V_{RN}B$  ピンとの間に  $10\,\mu\text{F}$  のコンデンサを それぞれ 1 つずつ挿入してください。この回路は、SFDR や SNR、またはその両方を悪化させる可能性のあるリファレンスの発振を 防ぐために必要です。

この指定値は

、パワーダウン・

モードからの復帰時間が短くなりますが、

ノイズ性能を低下させる

原因になることがあります。  $V_{RM}A$  と  $V_{RM}B$  を除くこれらのピンに

負荷を接続すると性能劣化を引き起こす場合があります。

リファレンス・バイパス・ピンの公称電圧は次のとおりです。

$V_{RM} = 1.5V$

$V_{RP} = V_{RM} + V_{REF}/2$

$V_{RN} = V_{RM} - V_{REF}/2$

オンチップ・リファレンスを使うか外部リファレンスを使うか選択が可能です。  $V_{REF}$  ピンを  $V_A$  に接続すると、内部リファレンスの 1.0V が使用されます。  $V_{REF}$  ピンを AGND に接続すると、内部リファレンスの 0.5V が使用されます。  $V_{REF}$  に 0.8V ~ 1.2V の範囲の電圧を印加した場合は、その電圧がリファレンスとして使用されます。 外部リファレンスを使用する場合、  $0.1\mu$ F のコンデンサを  $V_{REF}$  ピンの近くに実装してグラウンドに対してバイパスしてください。 内部リファレンスを用いる場合は  $V_{REF}$  ピンのバイパスは不要です。

#### 1.3 信号入力

信号入力は、一方の A/D コンバータが  $V_{\rm IN}A$  +と  $V_{\rm IN}A$  - 、もう一方の A/D コンバータが  $V_{\rm IN}B$  +と  $V_{\rm IN}B$  - です。入力信号  $V_{\rm IN}$ は次のように定義されます。 "A" コンバータの場合は、

$$V_{IN}A = (V_{IN}A + ) - (V_{IN}A - )$$

と定義されます。 "B" コンバータの場合は、

$$V_{IN}B = (V_{IN}B + ) - (V_{IN}B - )$$

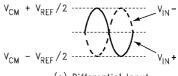

と定義されます。 Figure 2 は、入力信号として予想される範囲を示したものです。 コモンモード入力電圧  $V_{CM}$  は、0.5V から 2.0V の範囲になければなりません。

個々の入力信号のピークは、決して 2.6V を超えてはなりません。

ADC12DL040 は、各入力をコモンモード電圧 V<sub>CM</sub> を中心電圧とする差動信号で使用した場合に、最も良い性能が得られます。各アナログ入力ピンのピーク・ツー・ピーク電圧振幅はリファレンス電圧値を超えてはなりません。出力データにクリッピングが生じてしまいます。

差動信号を構成する2つの入力信号は、位相差をちょうど180°にし、振幅は同じにしてください。単一周波数の入力のときは、位相差があると(つまり差動信号の位相差が正確に180℃なっていないと)実効フルスケール入力の範囲が狭くなってしまいます。複雑な波形では、位相誤差は歪みの原因となります。

(a) Differential Input

$$V_{CM} + V_{REF}$$

$V_{IN} - = V_{CM}$

$V_{CM} - V_{REF}$

(b) Single-Ended Input

#### FIGURE 2. Expected Input Signal Range

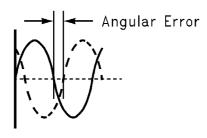

単一周波数の正弦波に対する LSB のフルスケール誤差は次式で近似できます。

$$E_{FS} = 4096 (1 - \sin(90 \degree \text{ dev}))$$

"dev" は、互いに 180 の相対位相差を持つとした場合の 2 つの信号間の位相誤差です (Figure 3 を参照 )。 アナログ入力ピンを駆動する信号源のソース・インピーダンスは 100 未満になるようにしてください。

FIGURE 3. Angular Errors Between the Two Input Signals Will Reduce the Output Level or Cause Distortion

差動入力にする場合は、各アナログ入力信号の振幅(ピーク・ツー・ピーク値)をリファレンス電圧 V<sub>REF</sub> に等しくし、互いに 180 の位相差を持たせるとともに、その中間電位を V<sub>CM</sub> に設定してください。

#### 1.3.1 シングルエンド動作

シングルエンドの信号に比べて、差動入力信号を用いたほうが優れた性能が得られます。この理由により、シングルエンド動作はなるべく使用しないでください。ただし、シングルエンド動作が回路上必要で、かつ、生じる性能低下が許容できる場合は、アナログ入力の一方のピンを信号入力電圧の DC 中心電圧に接続します。入力ピンに与える信号電圧のピーク・ツー・ピークをリファレンス電圧の 2 倍にすると、SNR と SINAD 性能が最大になります (Figure 2b)。 例えば、 $V_{REF}$ を 0.5V に設定したら、 $V_{IN}$  - には 1.0V のバイアスをかけ、 $V_{IN}$  +を 0.5V ~ 1.5V の信号で駆動してください。

入力信号の振幅が非常に大きいと歪みがひどくなる恐れがあるため、シングルエンド動作のときに出力信号を最大幅まで振りたいときは、性能を改善するために基準電圧を下げてください。Table 1~2 に、ADC12DL040の入力と出力との関係を示します。

TABLE 1. Input to Output Relationship – Differential Input

| V <sub>IN</sub> +                        | V <sub>IN</sub> -                        | Binary Output  | 2's Complement<br>Output |

|------------------------------------------|------------------------------------------|----------------|--------------------------|

| V <sub>CM</sub> -<br>V <sub>REF</sub> /2 | V <sub>CM</sub> +<br>V <sub>REF</sub> /2 | 0000 0000 0000 | 1000 0000 0000           |

| V <sub>CM</sub> - V <sub>REF</sub> /4    | V <sub>CM</sub> + V <sub>REF</sub> /4    | 0100 0000 0000 | 1100 0000 0000           |

| V <sub>CM</sub>                          | V <sub>CM</sub>                          | 1000 0000 0000 | 0000 0000 0000           |

| V <sub>CM</sub> + V <sub>REF</sub> /4    | V <sub>CM</sub> -<br>V <sub>REF</sub> /4 | 1100 0000 0000 | 0100 0000 0000           |

| V <sub>CM</sub> + V <sub>REF</sub> /2    | V <sub>CM</sub> –<br>V <sub>REF</sub> /2 | 1111 1111 1111 | 0111 1111 1111           |

TABLE 2. Input to Output Relationship – Single-Ended Input

| V <sub>IN</sub> +                     | V <sub>IN</sub> - | Binary Output  | 2's Complement<br>Output |

|---------------------------------------|-------------------|----------------|--------------------------|

| V <sub>CM</sub><br>V <sub>REF</sub>   | V <sub>CM</sub>   | 0000 0000 0000 | 1000 0000 0000           |

| V <sub>CM</sub> - V <sub>REF</sub> /2 | V <sub>CM</sub>   | 0100 0000 0000 | 1100 0000 0000           |

| V <sub>CM</sub>                       | V <sub>CM</sub>   | 1000 0000 0000 | 0000 0000 0000           |

| V <sub>CM</sub> + V <sub>REF</sub> /2 | V <sub>CM</sub>   | 1100 0000 0000 | 0100 0000 0000           |

| V <sub>CM</sub> + V <sub>REF</sub>    | V <sub>CM</sub>   | 1111 1111 1111 | 0111 1111 1111           |

#### 1.3.2 アナログ入力の駆動

ADC12DL040の  $V_{IN}$  +、 $V_{IN}$  - の各入力ピンの内部回路は、アナログ・スイッチと、それに続くスイッチト・キャパシタ・アンプの構成になっています。 このアナログ入力ピンの容量はクロック・パルスのレベルに応じて変化します。 クロックが Low レベルのときは 8pF であり、High レベルのときは 7pF です。

内蔵の入力サンプリング・スイッチの開閉に伴ってアナログ入力ピンには電流パルスが生じ、結果として信号入力ピンに電圧スパイクが発生します。アナログ入力を駆動するアンプがこのスパイク電圧を打ち消そうとするため、アナログ入力端で減衰振動が見られる場合があります。これらのパルスをフィルタで除去しようとしないでください。スイッチが開いて次のサンプリングが行われる前にスパイクとそのセトリングを吸収できるアンブを用いて、ADC12DL040入力ピンを駆動してください。LMH6702、LMH6628、LMH6622、LMH6655が ADC12DL040の駆動に適している優れたアンプです。

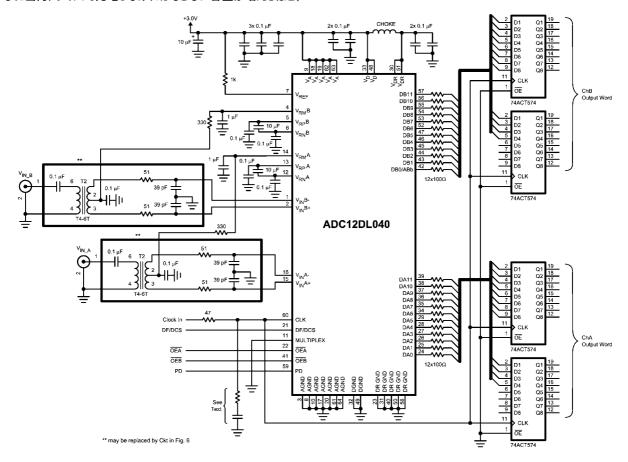

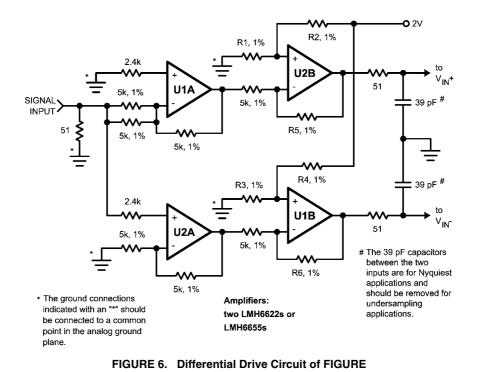

A/D コンバータの入力に現れる電圧スパイクの影響をアンプ出力に与えないようにするには、Figure 4 ~ 6に示すような RC 回路を入力端に設けてください。取り付ける位置は A/D コンバータのすぐ近くにしてください。 A/D コンバータの入力ピンが全体の中でも最も高感度な部分であり、入力信号にフィルタをかけるには最後のポイントであるためです。

ナイキスト・アプリケーションの場合、A/D コンバータのサンプリング・レートに RC のポールを設定します。 サンプリング・モード時の A/D コンバータの入力容量は RC ポールの設定に含めてください。 広帯域アンダーサンプリング・アプリケーションの場合、リニアな遅延応答を維持するために、最高入力周波数の 1.5 倍から 2 倍程度の周波数に RC ポールを設定してください。

シングルエンドから差動信号への変換回路を Figure 6 に示します。ADC12DL040の各差動入力ピンに 1.0V ± 0.5V の入力信号を供給するための抵抗値を Table 3 に示します。

TABLE 3. Resistor Values for Circuit of Figure 6

| SIGNAL<br>RANGE | R1   | R2         | R3   | R4    | R5, R6 |

|-----------------|------|------------|------|-------|--------|

| 0 - 0.25V       | open | $\Omega$ 0 | 124Ω | 1500Ω | 1000Ω  |

| 0 - 0.5V        | 0Ω   | openΩ      | 499Ω | 1500Ω | 499Ω   |

| ±0.25V          | 100Ω | 698Ω       | 100Ω | 698Ω  | 499Ω   |

### 1.3.3 入力コモンモード電圧

入力コモンモード電圧  $V_{CM}$  は  $0.5V\sim2.0V$  の範囲とし、アナログ信号のピーク電圧がグラウンドを下回らないように、かつ、2.6V を上回らないように設定しなければなりません。セクション 1.2 を参照してください。

#### 2.0 デジタル入力

CLK、OEA、OEB、PD、DF/DCS、MULTIPLEX は、TTL/CMOS 互換のデジタル入力信号です。

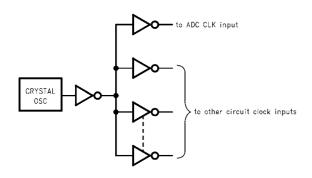

#### 2.1 CLK

CLK 信号はサンプリング・プロセスのタイミングを制御します。このクロック入力ピンは、安定した低ジッタのクロック信号源で駆動してください。クロック周波数の範囲は「電気的特性」の表に示されており、パルスの立ち上がり時間、立ち下がり時間はいずれも 2ns 以下とします。クロック信号の配線パターンは最短とし、アナログ、デジタルを問わず他の一切の信号線と、90 であっても交差しないようにしてください。

CLK 信号は内部のステート・マシンの駆動用としても使われます。 CLK が途切れるか、その周波数が低くなりすぎると、内部キャパシタに充電されていた電位が徐々に下がってきます。この電位がある値以下になると出力データの精度が低下します。 サンプリング・レートの下限が規定されているのはこのためです。

クロック信号ラインはソース端で線路の特性インピーダンスで終端してください。クロック・ラインの全長にわたってインピーダンスを一定に保つように注意してください。特性インピーダンスの求め方はアプリケーション・ノート AN-905 を参照してください。

A/D コンバータの CLK 入力を駆動する信号源は、対象となる CLK ピンのみを駆動するようにしてください。 しかし、クロック源が他の負荷も駆動する場合は、Figure 4 に示すように、クロック・ラインの特性インピーダンスに等しい抵抗と次に示す容量のコンデンサを用いた直列 RC 回路を用いて、グラウンドに AC 終端してください。

$$C \geq \frac{4 \times t_{PD} \times L}{Z_{o}}$$

$t_{PD}$  はクロック配線の信号伝搬遅延時間、"L" は配線長、 $Z_o$  は クロック配線の特性インピーダンスです。この終端回路は A/D コンバータのクロック・ピンのできるだけ近くに、かつ、クロック・ソースから見て遠い側に配置してください。  $t_{PD}$  の代表値は FR-4 基板材料でおよそ 150ps/ インチ (60ps/cm) です。 "L" の単位と  $t_{PD}$  の単位は一致させてください ( インチまたは cm)。

クロック信号のデューティ・サイクルは A/D コンバータの性能に影響を与える場合があります。 正確なデューティ・サイクルにするのは困難なため、ADC12DL040 はデューティ・サイクル安定化回路を搭載しています。 この回路は DF/DCS ピンによってイネーブルすることができます。40MSPS の場合にクロックのデューティ・サイクル20% ~ 80%の範囲で性能を維持するように設計されています。 デューティ・サイクル安定化回路では、急峻なクロック・エッジで内部クロックを発生させる必要があります。 立ち上がり時間と立ち下がり時間の要件が仕様表に載っているのは、そのためです。

#### 2.2 OEA OEB

OEA ピンまたは OEB ピンを High にすると各コンバータ・チャネル に対応した出力ピンがハイ・インピーダンス状態になります。 いずれかのピンを Low にすると、対応する出力がアクティブな状態となります。 OEA/OEB ピンのレベルによらず ADC12DL040 は内部で変換処理を実行しますが、ピンが High のときは出力を読み出すことはできません。

デジタル出力ピンの負荷容量が大きくなると A/D コンバータのノイズが増えるため、ADC12DL040の TRI-STATE 出力はバスの駆動には使用しないでください。それよりた、各出力ピンは 1 個のデジタル入力のみを駆動するようにし、合わせて A/D コンバータの

デジタル出力と駆動するデジタル入力を近づけてください。A/Dコンバータのノイズをさらに低減するには、100 の抵抗を各 A/Dコンバータのデジタル出力ピンの近くに直列に挿入してください。

#### 2.3 PD

コンバータが使用されない場合は、PD ピンを High レベルにすると ADC12DL040 がパワーダウン・モードになります。 これによって、未使用時の消費電力が抑えられます。 このモードでの消費電力は、クロックが 40MHz のときは 36mW であり、PD を High にしクロックを停止したときは 40mW です。 パワーダウン・モードの間、出力データ・ピンは不定となり、パイプライン内のデータは壊れます。

"Power Down Mode Exit Cycle" 時間の長さは、4 ピン、5 ピン、6 ピン、12 ピン、13 ピン、14 ピンの各部品の定数によって決まり、 $V_{RP}$ 、 $V_{RM}$ 、 $V_{RN}$  の各リファレンス・バイパス・ピンに推奨部品を使用した場合はおよそ  $500\,\mu s$  です。これらのコンデンサはパワーダウン・モードで電荷を失うため、変換が正確になる前に内蔵回路による再充電が必要です。小容量のコンデンサを使用するとパワーダウン・モードからの復帰時間が短くなりますが、SNR、SINAD、ENOB 性能が低下します。

#### **2.4 DF/DCS**

デューティ・サイクル安定化および出力データのフォーマットは、このクワッド・ステートの機能ピンによって選択可能です。デューティ・サイクル安定化回路をイネーブルにすると、デューティ・サイクル20%~80%のクロック入力が補償され、安定した内部クロックが生成されるため、デバイスの性能が向上します。デューティ・サイクル安定化回路では、急峻なクロック・エッジで内部クロックを発生させる必要があります。立ち上がり時間と立ち下がり時間の要件が仕様表に載っているのは、そのためです。

DF/DCS =  $V_A$  の場合、出力データのフォーマットはオフセット・バイナリとなり、入力クロックにデューティ・サイクル安定化機能が適用されます。 DF/DCS = 0 の場合、出力データのフォーマットは 2 の補数となり、入力クロックにデューティ・サイクル安定化機能が適用されます。 DF/DCS =  $V_{RM}A$  または  $V_{RM}B$  の場合、出力データのフォーマットは 2 の補数となり、入力クロックにはデューティ・サイクル安定化機能が適用されません。 DF/DCS がフローティングの場合、出力データのフォーマットはオフセット・バイナリとなり、入力クロックにはデューティ・サイクル安定化機能が適用されません。 このピンのロジック・レベルは動作中に変更することも可能ですが、切り換え後は数クロック・サイクルの間、正しくないデータが出力される可能性があるため、推奨はしません。

#### 2.5 MULTIPLEX

MULTIPLEX ピンを Low レベルにすると、チャネル A とチャネル B から出力されるデジタル出力ワードが、それぞれ別々のデジタル出力バスから出力されます (パラレル・モード)。

MULTIPLEX ピンを High レベルにすると、両チャネルのデジタル 出力ワードが多重化されて DAO: DA11 の各ピンから出力されます (マルチプレクス・モード)。 DBO/ABb ピンは、多重化された出 力に連動して変化し、チャネルAのデータが出力されるときは High レベルになり、チャネル B のデータが出力されるときは Low レベル になます。

#### 3.0 出力

ADC12DL040 は、チャネル A、B ともに、TTL/CMOS 互換のデジタル・データ出力ピンを 12 本ずつ備えています。 OE ピンと PD ピンが Low のときに、これらの出力ピンから有効なデータが出力されます。 パラレル・モードの場合は、データは CLK 信号により捕捉するようにしてください。 受信側の回路 (ASIC) のセットアップおよびホールド時間の要件に応じて、CLK 信号の立ち上がほたは立ち下がりエッジのいずれかでデータを取り込むことができます。 通常、立ち上がりエッジで取り込むとセットアップ時間を最大に、

ホールド時間を最小にできます。これに対し、立ち下がりエッジで取り込むとホールド時間を最大に、セットアップ時間を最小にできます。ただし、立ち下がりエッジ取り込みの場合の実際のタイミングは CLK 信号周波数に大きく依存します。またいずれのエッジで取り込む場合も、ASIC内の遅延の影響を受けます。「AC電気的特性」表のTodの仕様を確認してください。

マルチプレクス・モードでは、両方のチャネルの出力が DAO:DA11 から出力されます。 出力バスの多重分離には ABb 信号が使われます。 ABb 信号は、ASIC にデータをラッチするのにも使用できるため、CLK 信号はまったく使わなくても済みます。 ただし ABb 信号のエッジはデータの遷移と位相が揃うため、データ取り込み用ラッチのクロックとして ABb 信号を使用するためには、一般に、ASIC 回路は、取り込むデータよりも ABb 信号を遅らせなければなりません。 前項で述べたように、マルチプレクス・モードの場合は CLK 信号でデータをラッチすることも可能です。

容量の大きいバスを駆動するときは注意が必要です。 変換のたびに出力ドライバで充電しなければならない容量が増えるほど、

V<sub>DR</sub>とDR GND に流れる瞬時デジタル電流の量が増えます。このような大きな充電電流スパイクは、チップ上でのグラウンド・ノイズの原因となり、またアナログ回路部にも結合するため、動的性能が劣化しかねません。これらの問題に対処するには、十分なバイパス、出力容量の制限、適切なグラウンド・プレーン設計などが必要です。また、バス・ラインの負荷容量が仕様値 15pF/ピンを超えるとt<sub>OD</sub> が大きくなり、その結果、A/D コンバータの出力データを正しくラッチするのが難しくなります。その場合、動的性能が劣化する恐れがあります。

デジタル出力のスイッチングによるノイズを最小にするには、デジタル出力の負荷電流を最小にします。具体的にはバッファ(例えば74ACQ541)をA/Dコンバータの出力と他の回路間に接続します。各出力ピンは1つの負荷のみを駆動するようこしてください。さらにおよそ100の抵抗をデジタル出力ピンのすぐ近くに直列に挿入すると、配線パターンやその他回路の持つ容量から出力ピンが分離されて、出力電流が抑えられます。この措置を講じないと性能が低下することになります。 Figure 4を参照してください。

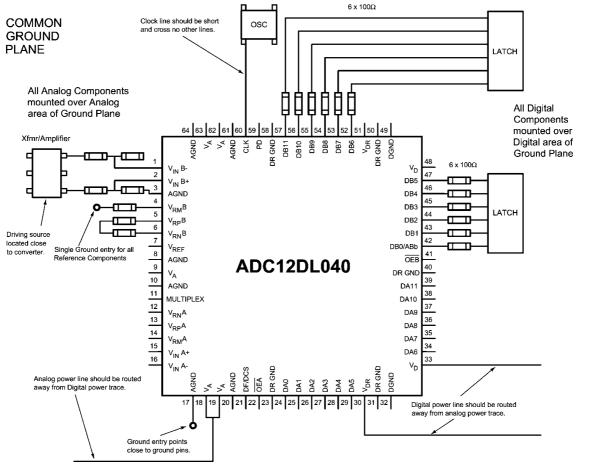

FIGURE 4. Application Circuit using Transformer or Differential Op-Amp Drive Circuit, Parallel mode

# アプリケーション情報(つづき) CLK Channel B Output Word %% % DB1 DB1 DB1 DB2 DB3 DB4 DB3 DB2 DB1 ADC12DL040 51 39 pF CLK DF/DCS DF/DCS Multiplex MULTIPLEX 22 OEA ŌĒĀ ŌEB Œ \*\* may be replaced by Ckt in Fig. 6

FIGURE 5. Application Circuit using Transformer or Differential Op-Amp Drive Circuit, Multiplex mode

\*\*\* The delay through the inverters should be adjusted to allow the correct set-up and hold time for the latches.

#### 4.0 電源について

いずれの電源ピンも当該ピンから 1cm 以内の所にバイパス・コンデンサとして 10μF コンデンサと 0.1μF セラミック・チップ・コンデンサを各 1 個挿入してください。 直列インダクタンスが小さいリードレス・チップ・コンデンサを推奨します。

あらゆる高速コンバータと同じように、ADC12DL040も電源ノイズに敏感です。したがって、アナログ電源ピンのノイズ・レベルは $100 \mathrm{mV_{P-P}}$  以先低く抑えてください。

いずれのピンも、電源電圧より高い電圧を加えることはたとえ瞬時であっても許されません。電源をオンするときと、電源をオフにするときは特に注意してください。

$V_{DR}$  ピンは出力ドライバ用の電源ピンで、 $2.4V \sim V_{D}$  の範囲で動作します。このため、低電圧のデバイスやシステムとのインタフェースが容易です。 ただし、 $V_{DR}$  を低くすると  $t_{OD}$  が長くなる点に注意してください。  $V_{DR}$  ピンには、 $V_{D}$  よりも高い電圧を絶対に印加しないでください。

#### 5.0 レイアウトとグラウンド構成

適切なグラウンド処理とすべての信号ラインの適切な配線は、精度の高い変換を確保するために必須の条件となります。 仕様性能を達成するには、ADC12DL040をアナログ領域とデジタル領域との間に挟み、ボード上でアナログ領域とデジタル領域を分離しておく必要があります。

データ出力用のグラウンド・ピン (DR GND) には、出力ドライバのグラウンド電流が流れます。この出力電流により、変換プロセスにノイズが介入する可能性のある大きなトランジェントを発生することがあります。 このようなことが起こらないように DR GND ピンは、ADC12DL040 のいかなるその他のグラウンド・ピンに近接したシステム・グラウンドにも接続しないでください。

普通はノイズの多いデジタル回路とノイズに高感度なアナログ回路との間の容量性結合により、変換性能が低下する可能性があります。解決方法は、アナログ回路をデジタル回路から十分に分離させたレイアウトとし、クロック信号の配線パターンを最短にすることです。

デジタル回路は電源とグラウンドに相当に大きい過渡電流を発生させます。このように発生するロジック・ノイズがシステムのノイズ特性に大きく影響を及ぼします。A/D コンバータを備えたシステムに使用するのに最適なロジック・ファミリは、ノン・サチュレーティング・トランジスタ(不飽和トランジスタ)設計を採用したものか、または74LS、74HC(T)や74AC(T)Qファミリのような低ノイズ特性を備えたものです。最も良くないノイズの発生源は、74Fや74AC(T)ファミリのようなウロックや信号エッジでの電源電流トランジェントが大きなロジック・ファミリです。

A/D コンバータの出力スイッチングによって生じるノイズの影響は、デジタル・データ出力ラインのそれぞれに 1 つずつ直列に 100 抵抗を挿入すると最小に抑えられます。この抵抗の取り付け位置は A/D コンバータの出力ピンにできる限り近づけてください。

デジタル・スイッチング・トランジェント (デジタル回路の瞬間的スイッチング電圧によるオーバーシュート/アンダーシュート)の高周波成分が大きいため、グラウンド・プレーンの総銅箔重量を増やしても、ロジック回路の生成するノイズにはほとんど影響がありません。これは表皮効果を伴うためで、グラウンド層の全重量より定金表面積のほうが重要となります。

一般に、アナログ、デジタルの配線パターンどうしのクロストークを防ぐには、両者の配線パターンを互いに 90 で交差させるのが望ましいとされています。 高周波 / 高分解能のシステムで精度を最大限にするためには、アナログ信号ラインとデジタル信号ラインが互いに交差する配線は避けなければなりません。 クロック・ラインは最短にし、他のデジタル・ラインを含むすべてのその他のラインからアイソレートすることが重要です。 一般には許容される信号ラインの 90 交差は、クロックラインについても避けるべきです。これは、ごくわずかな結合でも高周波では問題となる可能性があるためです。 これは、他のラインによってクロック・ラインにジッタが発生し、結果的に S/N 比の劣化につながるからです。また、クロックが高速だとアナログ回路にノイズの生じる場合もあります。

高周波/高分解能で最良の性能を得るには、まっすぐな信号配線にすると実現できます。すなわち、いずれの部品を通る信号経路も可能な限り、まっすぐに配線することです。

FIGURE 7. Example of a Suitable Layout

インダクタのレイアウトには特に注意してください。相互インダクタンスにより、インダクタを使用する回路の特性が変わります。 複数のインダクタを使用する場合には、決して並べて配置しないでください。 たとえインダクタ部品全長の一部であっても並べて配置してはおません。

スプリアス信号が入力に結合するのを避けるために、アナログ入力は、ノイズの多い信号経路から十分にアイソレートしてください。 コンバータの入力ピンとアナログ・グラウンドの間、または基準入力 ピンとグラウンドに接続されるすべての外付け部品(例えばフィルタ用のコンデンサ)は、グラウン・ドプレーンの非常にクリーンなノイズの少ない1点で接続してください。

Figure 7 は、適切なレイアウトの例です。すべてのアナログ回路 (入力アンプ、フィルタ、基準電圧生成部品など)はボードのアナログ領域に配置してください。すべてのデジタル回路とデジタル入出力 (I/O) は、ボードのデジタル領域に配置してください。ADC12DL040 は、アナログ領域とデジタル領域との中間に配置してください。さらに、グラウンドに接続されるリファレンス電圧回路と入力信号に関連する回路に含まれているすべての部品は、短い配線で相互に接続し、ノイズのない1点でアナログ・グラウンド・プレーンに落としてください。すべてのグラウンドへの接続は、グラウンドへの経路が低インダクタンスになるように配線してください。

#### 6.0 動的特性

最高の動的特性を実現するために、CLK 入力を駆動するクロック信号源はジッタのないものでなければなりません。 Figure 8 に示されるようなバッファを用いてクロック・ツリーを構成して、A/D のクロック信号をその他のデジタル回路からアイソレートしなければなりません。このクロック・ツリーで使用するゲートは、余分なジッタの追加を防ぐために、クロックの周波数より生はるかに高い周波数に対応した品種でなければなりません。

セクション 1.3.1 とセクション 1.3.2 で説明したように、シングルエンド駆動ではなく差動入力駆動のときに最高性能が得られます。

セクション 5.0 で述べたように、A/D クロック・ラインをできる限り短くかつその他のいずれの信号からも十分に離して置くのは、良い手段です。 別の信号はクロック信号にジッタを招く可能性があり、SNR の性能劣化につながる場合や、クロック信号が原因でほかの配線にノイズを生じることもあります。信号ラインが互いに 90 交差している場合でさえ容量性の結合が生じるため、クロック・ラインは 90 の交差ができないようにしてください。

FIGURE 8. Isolating the ADC Clock from other Circuitry with a Clock Tree

#### 7.0 アプリケーション共通の注意事項

電源範囲を超えてアナログまたはデジタル入力を駆動しないこと適切な動作を行うために、すべての入力は、グラウンド・ピンより100mV以下または、電源ピンより100mV以上にならないようにしてください。トランジェントによる場合でもこれらのリミット値を超えると、システムにとって故障または誤動作を招く可能性があります。電源電圧とそのグラウンド電位を超えるオーバーシュートやアンダーシュートが起こる現象は、高速デジタルIC(例えば、74Fや74ACなどのファミリ・デバイス)では、よくあります。A/Dコンバータのデジタル入力に約47~100の直列抵抗を信号源の近くに挿入すると、この問題を取り除けます。

入力電圧は、たとえ瞬間的であっても電源電圧を超えないようにしてください。 電源の投入時も遮断時も同じです。

ADC12DL040の入力をADC12DL040の電源範囲を超える範囲にまで駆動するようなデバイスで、オーバードライブしないように注意してください。このような過度の入力ドライブは変換精度の悪化を招き、さらにデバイスの破損につながはます。

容量が大きいデジタル・データ・バスの駆動をしないこと変換のたびに出力ドライバで充電しなければならない容量が増えるほど、V<sub>DR</sub>とDR GND に流れる瞬時デジタル電流の量が増えます。これらの大きな充電電流スパイクは、アナログ回路に結合し、動的特性を劣化させる可能性があります。適切なパイパスとボード上のアナログ領域とデジタル領域の分離によって、この問題を低減できます。

また、バス・ラインの負荷容量が仕様値 15pF/ ピンを超えると t<sub>OD</sub> が大きくなり、その結果、A/D コンバータの出力データを正しくラッチするのが難しくなります。 その場合もやはり動的性能は劣化する恐れがあります。

また、デジタル・データ出力は(例えば、74ACQ541で)バッファリングしてください。また、各デジタル出力のできる限り近くに直列抵抗を加えると、出力電流が制限され、コンバータの出力に戻ってくる結合信号のエネルギーが低減されて、動的特性が改善されます。このときに使用する推奨の抵抗値は100です。

不適切なアンプを使ってアナログ入力を駆動しないこと セクション 1.3 で説明したように、アナログ入力ピンの容量はクロック信号のレベルに応じて 8pF になったり 7pF になったりします。このように容量の変動する負荷を駆動するのは、容量の変わらない場合に比べて難しくなります。

ごく小さい信号レベルのときでもオーバーシュートやリンギングといった不安定要素が生じるアンプを使うと、性能を悪化させます。 Figure 5 ~ 6 のように、各アンプ出力には低抵抗を直列に接続し、アナログ入力にはコンデンサを設けると、性能が向上します。 LMH6702 と LMH6628 を使えば ADC12DL040 のアナログ入力 ピンの駆動に問題がなくなります。

また、差動入力信号を構成する 2 つの信号は、振幅が完全に等しく、180 の正確な位相差があることが重要です。この 2 つの信号どうしの実際の位相差は部品配置による影響を受けますが、入力ピンまでを結ぶ配線パターンどうしの長さの違いが特に大きく影響します。オペアンプは非反転回路のほうが反転回路より遅延時間が長くなることに注意してください。

リファレンス・ピンを仕様範囲外の入力で動作させないこと セクション 1.2 で述べたように、V<sub>REF</sub> ピンへの入力は、次の範囲 内になければなりません。

$$0.8V$$

$V_{REF}$   $1.2V$

この範囲外での動作は、性能の劣化につながることがあります。

リファレンス・バイパス・ピン ( $V_{RP}$ A、 $V_{RN}$ A、 $V_{RM}$ A、 $V_{RP}$ B、 $V_{RN}$ B、 $V_{RM}$ B) に不適切なネットワークを接続しないこと セクション 1.2 で述べたように、これらのピンを  $0.1\mu F$  のコンデンサ でグラウンドにバイパスし、 $V_{RP}$ A ピンと  $V_{RN}$ A ピンとの間、 $V_{RP}$ B ピンと  $V_{RN}$ B ピンとの間に  $10.0\mu F$  のコンデンサを接続すると、最 良の性能が得られます。

過度のジッタを持ったクロック信号源を使用したり、異常に長いクロック信号経路や、他の信号がクロック信号経路にカップリングしてしまうレイアウトを使用しないこと

この場合には、サンプリング間隔が変化し、過度の出力ノイズを 発生し、かつ S/N 比と SINAD の劣化を招きます。

#### 外形寸法図 単位は millimeters

64-Lead TQFP Package

Ordering Number ADC12DL040CIVS

NS Package Number VECO64A

このドキュメントの内容はナショナル セミコンダクター社製品の関連情報として提供されます。ナショナル セミコンダクター社は、この発行物の内容の正確性または完全性について、いかなる表明または保証もいたしません。また、仕様と製品説明を予告なく変更する権利を有します。このドキュメントはいかなる知的財産権に対するライセンスも、明示的、黙示的、禁反言による惹起、またはその他を問わず、付与するものではありません。

試験や品質管理は、ナショナル セミコンダクター社が自社の製品保証を維持するために必要と考える範囲に用いられます。政府が 課す要件によって指定される場合を除き、各製品のすべてのパラメータの試験を必ずしも実施するわけではありません。ナショナ ル セミコンダクター社は製品適用の援助や購入者の製品設計に対する義務は負いかねます。ナショナル セミコンダクター社の部品 を使用した製品および製品適用の責任は購入者にあります。ナショナル セミコンダクター社の製品を用いたいかなる製品の使用ま たは供給に先立ち、購入者は、適切な設計、試験、および動作上の安全手段を講じなければなりません。

それら製品の販売に関するナショナル セミコンダクター社との取引条件で規定される場合を除き、ナショナル セミコンダクター社は一切の義務を負わないものとし、また、ナショナル セミコンダクター社の製品の販売か使用、またはその両方に関連する特定目的への適合性、商品の機能性、ないしは特許、著作権、または他の知的財産権の侵害に関連した義務または保証を含むいかなる表明または黙示的保証も行いません。

#### 生命維持装置への使用について

ナショナル セミコンダクター社の製品は、ナショナル セミコンダクター社の最高経営責任者 (CEO) および法務部門 (GENERAL COUNSEL) の事前の書面による承諾がない限り、生命維持装置または生命維持システム内のきわめて重要な部品に使用することは認められていません。

高の方が、生命維持装置またはシステムとは(a)体内に外科的に使用されることを意図されたもの、または(b)生命を維持あるいは支持するものをいい、ラベルにより表示される使用法に従って適切に使用された場合に、これの不具合が使用者に身体的障害を与えると予想されるものをいいます。重要な部品とは、生命維持にかかわる装置またはシステム内のすべての部品をいい、これの不具合が生命維持用の装置またはシステムの不具合の原因となりそれらの安全性や機能に影響を及ぼすことが予想されるものをいいます。

National Semiconductor とナショナル セミコンダクターのロゴはナショナル セミコンダクター コーポレーションの登録商標です。その他のブランド や製品名は各権利所有者の商標または登録商標です。

Copyright © 2007 National Semiconductor Corporation

製品の最新情報については www.national.com をご覧ください。

## ナショナル セミコンダクター ジャパン株式会社

本社 / 〒 135-0042 東京都江東区木場 2-17-16

TEL.(03)5639-7300

技術資料(日本語/英語)はホームページより入手可能です。

www.national.com/jpn/

# ご注意

日本テキサス・インスツルメンツ株式会社(以下TIJといいます)及びTexas Instruments Incorporated(TIJの親会社、以下TIJないしTexas Instruments Incorporatedを総称してTIといいます)は、その製品及びサービスを任意に修正し、改善、改良、その他の変更をし、もしくは製品の製造中止またはサービスの提供を中止する権利を留保します。従いまして、お客様は、発注される前に、関連する最新の情報を取得して頂き、その情報が現在有効かつ完全なものであるかどうかご確認下さい。全ての製品は、お客様とTIJとの間に取引契約が締結されている場合は、当該契約条件に基づき、また当該取引契約が締結されていない場合は、ご注文の受諾の際に提示されるTIJの標準販売契約約款に従って販売されます。

TIは、そのハードウェア製品が、TIの標準保証条件に従い販売時の仕様に対応した性能を有していること、またはお客様とTIJとの間で合意された保証条件に従い合意された仕様に対応した性能を有していることを保証します。検査およびその他の品質管理技法は、TIが当該保証を支援するのに必要とみなす範囲で行なわれております。各デバイスの全てのパラメーターに関する固有の検査は、政府がそれ等の実行を義務づけている場合を除き、必ずしも行なわれておりません。

TIは、製品のアプリケーションに関する支援もしくはお客様の製品の設計について責任を負うことはありません。TI製部品を使用しているお客様の製品及びそのアプリケーションについての責任はお客様にあります。TI製部品を使用したお客様の製品及びアプリケーションについて想定されうる危険を最小のものとするため、適切な設計上および操作上の安全対策は、必ずお客様にてお取り下さい。

TIは、TIの製品もしくはサービスが使用されている組み合せ、機械装置、もしくは方法に関連しているTIの特許権、著作権、回路配置利用権、その他のTIの知的財産権に基づいて何らかのライセンスを許諾するということは明示的にも黙示的にも保証も表明もしておりません。TIが第三者の製品もしくはサービスについて情報を提供することは、TIが当該製品もしくはサービスを使用することについてライセンスを与えるとか、保証もしくは是認するということを意味しません。そのような情報を使用するには第三者の特許その他の知的財産権に基づき当該第三者からライセンスを得なければならない場合もあり、またTIの特許その他の知的財産権に基づきTIからライセンスを得て頂かなければならない場合もあります。

TIのデータ・ブックもしくはデータ・シートの中にある情報を複製することは、その情報に一切の変更を加えること無く、かつその情報と結び付られた全ての保証、条件、制限及び通知と共に複製がなされる限りにおいて許されるものとします。当該情報に変更を加えて複製することは不公正で誤認を生じさせる行為です。TIは、そのような変更された情報や複製については何の義務も責任も負いません。

TIの製品もしくはサービスについてTIにより示された数値、特性、条件その他のパラメーターと異なる、あるいは、それを超えてなされた説明で当該TI製品もしくはサービスを再販売することは、当該TI製品もしくはサービスに対する全ての明示的保証、及び何らかの黙示的保証を無効にし、かつ不公正で誤認を生じさせる行為です。TIは、そのような説明については何の義務も責任もありません。

TIは、TIの製品が、安全でないことが致命的となる用途ないしアプリケーション(例えば、生命維持装置のように、TI製品に不良があった場合に、その不良により相当な確率で死傷等の重篤な事故が発生するようなもの)に使用されることを認めておりません。但し、お客様とTIの双方の権限有る役員が書面でそのような使用について明確に合意した場合は除きます。たとえTIがアプリケーションに関連した情報やサポートを提供したとしても、お客様は、そのようなアプリケーションの安全面及び規制面から見た諸問題を解決するために必要とされる専門的知識及び技術を持ち、かつ、お客様の製品について、またTI製品をそのような安全でないことが致命的となる用途に使用することについて、お客様が全ての法的責任、規制を遵守する責任、及び安全に関する要求事項を満足させる責任を負っていることを認め、かつそのことに同意します。さらに、もし万一、TIの製品がそのような安全でないことが致命的となる用途に使用されたことによって損害が発生し、TIないしその代表者がその損害を賠償した場合は、お客様がTIないしその代表者にその全額の補償をするものとします。

TI製品は、軍事的用途もしくは宇宙航空アプリケーションないし軍事的環境、航空宇宙環境にて使用されるようには設計もされていませんし、使用されることを意図されておりません。但し、当該TI製品が、軍需対応グレード品、若しくは「強化プラスティック」製品としてTIが特別に指定した製品である場合は除きます。TIが軍需対応グレード品として指定した製品のみが軍需品の仕様書に合致いたします。お客様は、TIが軍需対応グレード品として指定して収ない製品を、軍事的用途もしくは軍事的環境下で使用することは、もっぱらお客様の危険負担においてなされるということ、及び、お客様がもっぱら責任をもって、そのような使用に関して必要とされる全ての法的要求事項及び規制上の要求事項を満足させなければならないことを認め、かつ同意します。

TI製品は、自動車用アプリケーションないし自動車の環境において使用されるようには設計されていませんし、また使用されることを意図されておりません。但し、TIがISO/TS 16949の要求事項を満たしていると特別に指定したTI製品は除きます。お客様は、お客様が当該TI指定品以外のTI製品を自動車用アプリケーションに使用しても、TIは当該要求事項を満たしていなかったことについて、いかなる責任も負わないことを認め、かつ同意します。

Copyright © 2011, Texas Instruments Incorporated 日本語版 日本テキサス・インスツルメンツ株式会社

#### 弊社半導体製品の取り扱い・保管について

半導体製品は、取り扱い、保管・輸送環境、基板実装条件によっては、お客様での実装前後に破壊/劣化、または故障を起こすことがあります。

弊社半導体製品のお取り扱い、ご使用にあたっては下記の点を遵守して下さい。 1. 熱電気

- 素手で半導体製品単体を触らないこと。どうしても触る必要がある場合は、リストストラップ等で人体からアースをとり、導電性手袋等をして取り扱うこと。

- 弊社出荷梱包単位(外装から取り出された内装及び個装)又は製品 単品で取り扱いを行う場合は、接地された導電性のテーブル上で(導 電性マットにアースをとったもの等)、アースをした作業者が行う こと。また、コンテナ等も、導電性のものを使うこと。

- マウンタやはんだ付け設備等、半導体の実装に関わる全ての装置類は、静電気の帯電を防止する措置を施すこと。

- 前記のリストストラップ・導電性手袋・テーブル表面及び実装装置 類の接地等の静電気帯電防止措置は、常に管理されその機能が確認 されていること。

#### 2. 温·湿度環境

■ 温度:0~40℃、相対湿度:40~85%で保管・輸送及び取り扱いを行うこと。(但し、結露しないこと。)

- 直射日光があたる状態で保管・輸送しないこと。

- 3. 防湿梱包

- 防湿梱包品は、開封後は個別推奨保管環境及び期間に従い基板実装すること。

- 4. 機械的衝擊

- 梱包品(外装、内装、個装)及び製品単品を落下させたり、衝撃を 与えないこと。

- 5. 熱衝撃

- はんだ付け時は、最低限260℃以上の高温状態に、10秒以上さら さないこと。(個別推奨条件がある時はそれに従うこと。)

- 6. 汚染

- はんだ付け性を損なう、又はアルミ配線腐食の原因となるような汚染物質(硫黄、塩素等ハロゲン)のある環境で保管・輸送しないこと。

- はんだ付け後は十分にフラックスの洗浄を行うこと。(不純物含有率が一定以下に保証された無洗浄タイプのフラックスは除く。)

以上