AMC6821-Q1

JAJSPB8A - JUNE 2009 - REVISED JANUARY 2023

# AMC6821-Q1 インテリジェントな温度監視と PWM ファン・コントローラ

# 1 特長

- 車載アプリケーション向けに認定済み:

- 接合部温度:-40℃~+150℃、T」

- 機能安全対応

- 機能安全システムの設計に役立つ資料を利用可

- リモート温度センサ: ±3℃の精度、0.250℃の分解能

- ローカル温度センサ: ±3℃の精度、0.250℃の分解能

- PWM コントローラ

- PWM 周波数:10Hz~40kHz

- デューティ・サイクル:0%~100%、8ビット

- ファン速度の自動制御ループ

- SMBus インターフェイス

- 電源:2.7V~5.5V

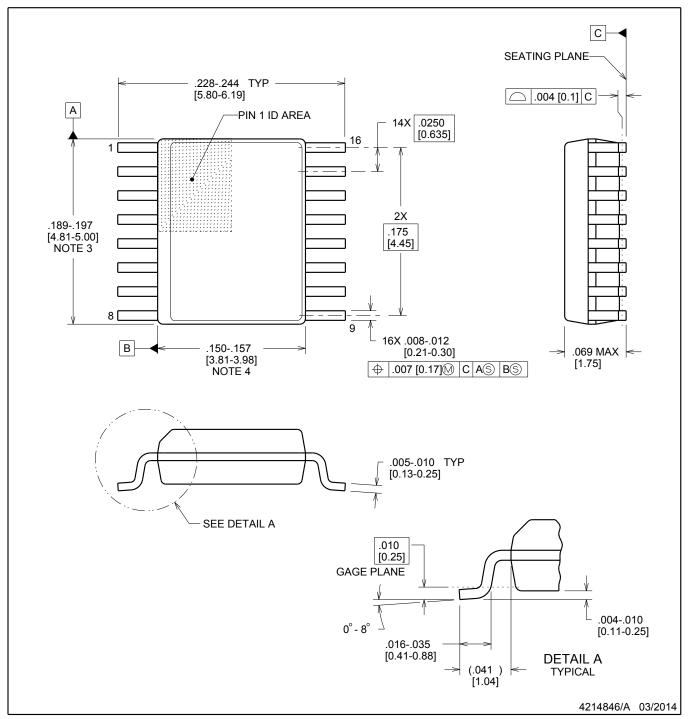

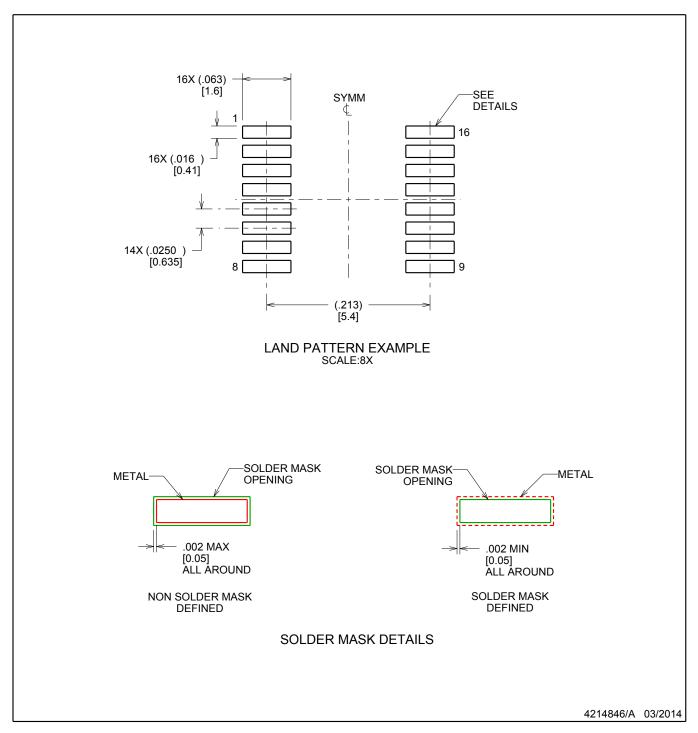

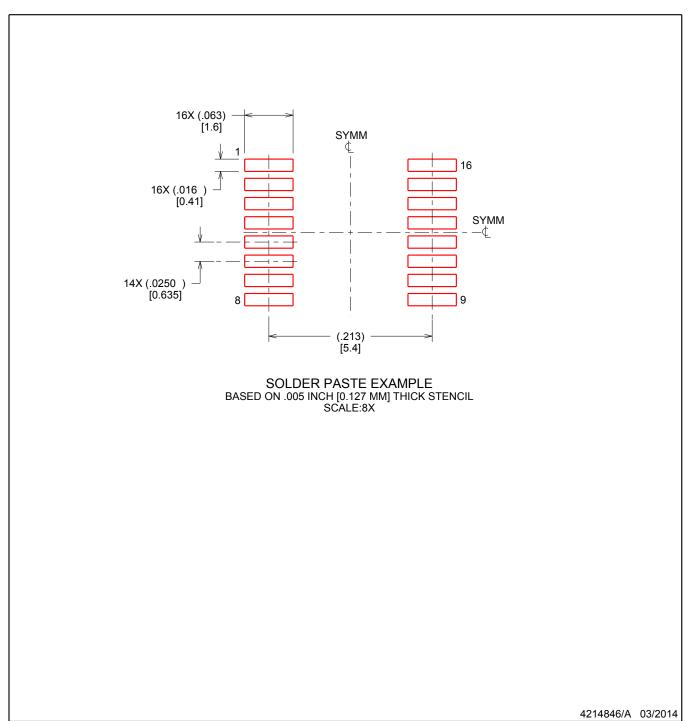

- パッケージ (緑):SSOP-16 (4mm × 5mm)

- RoHS 準拠

- JESD78B Class I 準拠で 100mA 超のラッチアップ

# 2 アプリケーション

- ADAS ドメイン・コントローラ

- 運転支援 ECU

- デジタル・コックピット処理装置

- サラウンド・ビュー・システムの ECU

# 3 概要

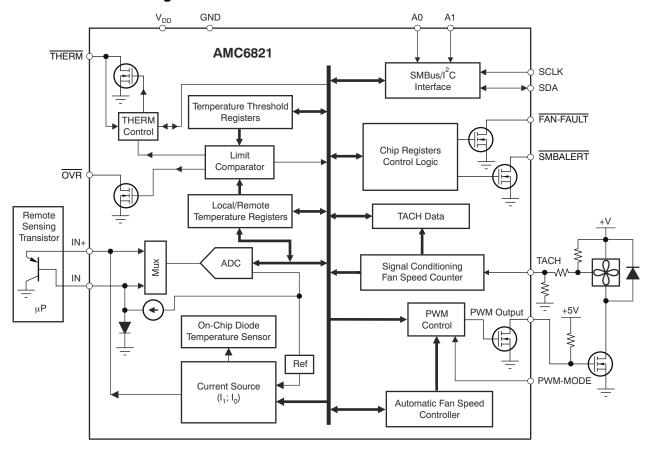

AMC6821-Q1 は、インテリジェントな温度監視およびパル ス幅変調 (PWM) ファン・コントローラです。 アクティブなシ ステム冷却を必要とする、ノイズに敏感なアプリケーション や電力に敏感なアプリケーション向けに設計されていま す。このデバイスは、低周波数または高周波数の PWM 信号を使用して、ファンの駆動、リモート・センサ・ダイオー ド温度の監視、ファン速度の測定と制御を同時に実行でき るため、可能な限り低速で最小の音響ノイズで動作できま す。

# パッケージ情報(1)

| 部品番号       | パッケージ     | 本体サイズ (公称)      |

|------------|-----------|-----------------|

| AMC6821-Q1 | SSOP (16) | 4.90mm × 3.90mm |

利用可能なパッケージについては、このデータシートの末尾にあ る注文情報を参照してください。

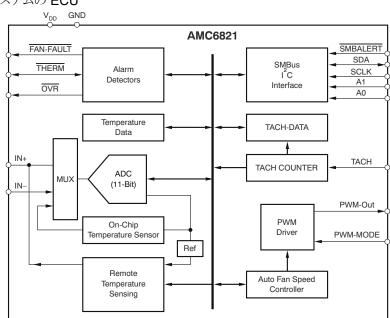

機能ブロック図

#### **Table of Contents**

| 1 特長                                 | 1 | 8.1 Functional Block Diagram            | 8                |

|--------------------------------------|---|-----------------------------------------|------------------|

| 2 アプリケーション                           |   | 8.2 Feature Description                 |                  |

| 3 概要                                 |   | 8.3 Device Functional Modes             | <mark>2</mark> 7 |

| 4 Revision History                   |   | 8.4 Programming                         | 27               |

| 5 概要 (続き)                            |   | 8.5 Register Map                        | <mark>31</mark>  |

| 6 Pin Configuration and Functions    |   | 9 Application and Implementation        |                  |

| 7 Specifications                     |   | 9.1 Power Supply Recommendations        | 48               |

| 7.1 Absolute Maximum Ratings         |   | 10 Device and Documentation Support     | 49               |

| 7.2 ESD Ratings                      |   | 10.1ドキュメントの更新通知を受け取る方法                  | 49               |

| 7.3 Recommended Operating Conditions |   | 10.2 サポート・リソース                          | 49               |

| 7.4 Thermal Information              |   | 10.3 Trademarks                         | 49               |

| 7.5 Electrical Characteristics       |   | 10.4 静電気放電に関する注意事項                      | 49               |

| 7.6 Timing Requirements              |   | 10.5 用語集                                |                  |

| 7.7 Typical Characteristics          |   | 11 Mechanical, Packaging, and Orderable |                  |

| 8 Detailed Description               |   | Information                             | 49               |

| P                                    |   |                                         |                  |

## 4 Revision History

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| C | hanges from Revision * (June 2009) to Revision A (January 2023) | Page                                  |

|---|-----------------------------------------------------------------|---------------------------------------|

| • | ドキュメント全体にわたって表、図、相互参照の採番方法を更新                                   | · · · · · · · · · · · · · · · · · · · |

| • | 「アプリケーション」セクション、「ESD 定格」表、「熱に関する情報」表、「アプリケーションと実装」セクションを追り      | 加 <sup>*</sup>                        |

| • | 「特長」セクションに機能安全の情報を追加                                            |                                       |

| • | 「注文情報」表を削除。注文情報表の内容を「メカニカル、パッケージ、および注文情報」セクションに移動               |                                       |

| • | Added the I/O column to the Pin Functions table                 |                                       |

# 5 概要 (続き)

AMC6821-Q1 には、次の 3 つのファン制御モードがあります。自動温度ファン・モード、ソフトウェア RPM モード、ソフトウェア DCY モード。各モードは、PWM 出力のデューティ・サイクルを変更することで、ファンの速度を制御します。自動温度ファン・モードは、インテリジェントな閉ループ制御であり、ユーザー定義のパラメータに応じてファン速度を最適化します。このモードでは、AMC6821-Q1 を CPU の介在なしでスタンドアロン・デバイスとして動作させることができます。 CPU またはシステムがロックアップした場合でも、(温度測定値に基づいて)ファンを引き続き制御できます。ソフトウェア RPM モードは、2 番目の閉ループ制御です。このモードでは、AMC6821-Q1 は PWM 出力を調整して、ユーザー指定の目標値でファン速度の一貫性を維持します。つまり、このデバイスはファン速度レギュレータとして機能します。ソフトウェア RPM モードを使用して、AMC6821-Q1 をスタンドアロン・デバイスとして動作させることもできます。3 番目のモードであるソフトウェア DCY は開ループです。ソフトウェア DCY モードでは、PWM デューティ・サイクルはデバイスに書き込まれた値によって直接設定されます。

AMC6821-Q1 は、エラー状態を示すプログラム可能な SMBALERT 出力と、ファンの障害を示す専用の FAN-FAULT 出力を備えています。 THERM ピンは、過熱状態に対するフェイルセーフ出力であり、CPU クロックのスロットルに使用できます。また、OVR ピンは過熱制限も示します。 すべてのアラーム・スレッショルドは、デバイスのレジスタで設定します。 AMC6821-Q1 は SSOP-16 パッケージで供給されます。

# **6 Pin Configuration and Functions**

#### SSOP-16 (body size: 5mm x 4mm) SCLK PWM-OUT 16 15 SDA **TACH** OVR SMBALERT NC 4 13 AMC6821 GND 5 12 PWM-MODE $V_{DD}$ 6 THERM 7 10 IN+ FAN-FAULT 8 9 IN-

図 6-1. DBQ Package 16-Pin SSOP Top View

表 6-1. Pin Functions

| PIN             |     | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                        |

|-----------------|-----|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME            | NO. | "0  | DESCRIFTION                                                                                                                                                                                                                                                                                        |

| PWM-OUT         | 1   | 0   | Digital output, open-drain. PWM output to control fan speed.                                                                                                                                                                                                                                       |

| TACH            | 2   | I   | Digital input. Fan tachometer input to measure the fan speed.                                                                                                                                                                                                                                      |

| OVR             | 3   | 0   | Digital output, open-drain, active low. Goes low when temperature reaches the critical shutdown threshold or remote temperature sensor failed. (See the <i>Interrupt</i> section for details.)                                                                                                     |

| NC              | 4   | -   | Not connected. Reserved for manufacturer's testing.                                                                                                                                                                                                                                                |

| GND             | 5   | _   | System ground                                                                                                                                                                                                                                                                                      |

| V <sub>DD</sub> | 6   | I   | Power supply, 3 V to 5 V                                                                                                                                                                                                                                                                           |

| THERM           | 7   | I/O | Digital input/output (open-drain). As an output, an active low output indicates the temperature over the THERM temperature limit. As an input, the pin provides an external fan control. When the pin is pulled low by external signal, the THERM-IN bit is set, and the fan is set to full-speed. |

| FAN-FAULT       | 8   | 0   | Digital open-drain output. Goes low when a fan failure is detected.                                                                                                                                                                                                                                |

| IN-             | 9   | I   | Negative analog differential input. Connected to cathode of external temperature-sensing diode.                                                                                                                                                                                                    |

| IN+             | 10  | I   | Positive analog differential input. Connected to anode of external temperature-sensing diode Pentium-IV <sup>™</sup> substrate transistor or general-purpose 2N3904 type transistor.                                                                                                               |

| PWM-MODE        | 11  | ı   | PWM mode selection. When tied low (GND), the high PWM frequency range (1 kHz to 40 kHz) is selected. When tied to $V_{DD}$ or floated, the low PWM frequency range (10 Hz to 94 Hz) is selected. Checked only on power-up or reset.                                                                |

| A1              | 12  | I   | Device slave address selection pin (see the <i>SMB Interface</i> section for details). Checked only on power-up or reset.                                                                                                                                                                          |

| A0              | 13  | I   | Device slave address selection pin (see the <i>SMB Interface</i> section for details). Checked only on power-up or reset.                                                                                                                                                                          |

| SMBALERT        | 14  | 0   | Digital output, open-drain, SMBALERT, active low. Requires a pullup resistor (2.2 kΩ typical).                                                                                                                                                                                                     |

| SDA             | 15  | I/O | Bidirectional digital I/O pin, SMBus data, open-drain. Requires a pullup resistor (2.2 kΩ typical).                                                                                                                                                                                                |

| SCLK            | 16  | ı   | Digital input, SMBus clock. Requires a pullup resistor (2.2 kΩ typical).                                                                                                                                                                                                                           |

# 7 Specifications

# 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                                           | MIN         | MAX                   | UNIT |

|-------------------------------------------|-------------|-----------------------|------|

| V <sub>DD</sub> to GND                    | -0.3        | 6.5                   | V    |

| Digital input voltage to GND              | -0.3        | 6.5                   | V    |

| Input current                             |             | 10                    | mA   |

| Select pins A0, A1, PWM-MODE to GND       | -0.3        | V <sub>DD</sub> + 0.3 | V    |

| Analog input voltage to GND               | -0.3        | V <sub>DD</sub> + 0.3 | V    |

| Operating temperature                     | -40         | 125                   | °C   |

| Junction temperature (T <sub>J</sub> Max) |             | 150                   | °C   |

| Storage temperature                       | <b>–</b> 65 | 150                   | °C   |

<sup>(1)</sup> Stresses above these ratings may cause permanent damage. Exposure to absolute maximum conditions for extended periods may degrade device reliability. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those specified is not implied.

# 7.2 ESD Ratings

|        |                          |                                                         | VALUE | UNIT |

|--------|--------------------------|---------------------------------------------------------|-------|------|

| V      | Electrostatic discharge  | Human-body model (HBM), per AEC Q100-002 <sup>(1)</sup> | ±2000 | \/   |

| V(ESD) | Lieotrostatic discriarge | Charged-device model (CDM), per AEC Q100-011            | ±1000 | v    |

<sup>(1)</sup> AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

# 7.3 Recommended Operating Conditions

|                           | MIN | NOM | MAX | UNIT |

|---------------------------|-----|-----|-----|------|

| Operating V <sub>DD</sub> | 2.7 | 5   | 5.5 | V    |

| Specified V <sub>DD</sub> | 3   |     | 5   | V    |

| Operating temperature     | -40 |     | 125 | °C   |

## 7.4 Thermal Information

|                       |                                              | AMC6821-Q1 |      |

|-----------------------|----------------------------------------------|------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | DBQ (SSOP) | UNIT |

|                       |                                              | 16 PINS    |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 97.6       | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 44.6       | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 41.2       | °C/W |

| ΨЈТ                   | Junction-to-top characterization parameter   | 5.7        | °C/W |

| ΨЈВ                   | Junction-to-board characterization parameter | 40.7       | °C/W |

| R <sub>θJC(bot)</sub> | Junction-to-case (bottom) thermal resistance | _          | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

Submit Document Feedback

## 7.5 Electrical Characteristics

$T_A = -40$ °C to 100°C and  $V_{DD} = 3$  V or 5 V (unless otherwise noted)

|                 | PARAMETER                                         | TEST CONDITIONS                          | MIN      | TYP   | MAX   | UNIT  |

|-----------------|---------------------------------------------------|------------------------------------------|----------|-------|-------|-------|

| TEM             | PERATURE MEASUREMENT                              |                                          | <u> </u> |       | -     |       |

|                 |                                                   | T <sub>A</sub> = 0°C to 90°C             |          | ±0.5  | ±3    | °C    |

|                 | Local sensor accuracy                             | T <sub>A</sub> = -25°C to 100°C          |          | ±1    | ±4    | °C    |

|                 | Remote sensor accuracy <sup>(1)</sup>             | T <sub>R</sub> = 50°C to 100°C           |          | ±0.5  | ±3    | °C    |

|                 | Remote sensor accuracy(1)                         | T <sub>R</sub> = -40°C to 125°C          |          | ±1    | ±4    | °C    |

|                 | Sensor resolution                                 | Both channels                            |          | 0.125 |       | °C    |

|                 | Conversion time                                   | Two channels                             |          | 62.5  |       | ms    |

| PWN             | CONTROLLER                                        |                                          |          |       | '     |       |

|                 | PWM frequency range (programmable) <sup>(2)</sup> |                                          | 10       |       | 40k   | Hz    |

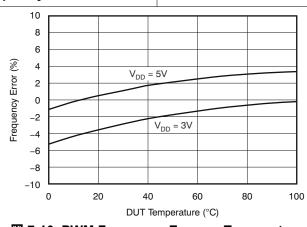

|                 | PWM frequency accuracy                            | T <sub>A</sub> = 25°C to 100°C           | -6%      |       | 7%    |       |

|                 | Duty cycle <sup>(2)</sup>                         | Programmable                             | 0%       |       | 100%  |       |

|                 | Duty cycle resolution                             | 8-bit                                    |          | 0.39  |       | %/bit |

| FAN             | RPM-TO-DIGITAL CONVERTER                          |                                          | 1        | ,     |       |       |

|                 | Accuracy                                          | T <sub>A</sub> = 25°C to 100°C           | -6%      |       | 7%    |       |

|                 | Full-scale count <sup>(2)</sup>                   |                                          |          |       | 65535 |       |

|                 | Nominal input RPM <sup>(2)</sup>                  |                                          | 100      |       | 23000 | RPM   |

|                 | Internal clock frequency for RPM measurement      |                                          |          | 100   |       | kHz   |

| DIGI            | TAL INPUT/OUTPUT                                  |                                          | I        |       |       |       |

| V <sub>OL</sub> | Open-drain output low voltage                     | Sink current 6 mA, V <sub>DD</sub> = 3 V | 0        |       | 0.4   | V     |

| I <sub>OH</sub> | Open-drain high-level output leakage current      |                                          |          | 0.1   | 1     | μΑ    |

| V <sub>IH</sub> | Input high voltage                                |                                          | 2.1      | ,     |       | V     |

| V <sub>IL</sub> | Input low voltage                                 |                                          |          |       | 0.8   | V     |

| I <sub>IH</sub> | Input high current                                |                                          | -1       |       |       | μA    |

| I <sub>IL</sub> | Input low current                                 |                                          |          |       | 1     | μΑ    |

|                 | Input capacitance                                 |                                          |          | 5     |       | pF    |

| POW             | ER SUPPLY                                         |                                          | 1        |       | '     |       |

|                 | Current                                           | V <sub>DD</sub> = 5                      |          | 1.1   | 2     | mA    |

|                 | Power dissipation                                 |                                          |          | 5     |       | mW    |

<sup>(1)</sup> The remote temperature sensor is optimized for the Pentium  $M^{TM}$  thermal diode with diode ideality n = 1.0022 and  $T_A = 0^{\circ}C$  to  $100^{\circ}C$ .

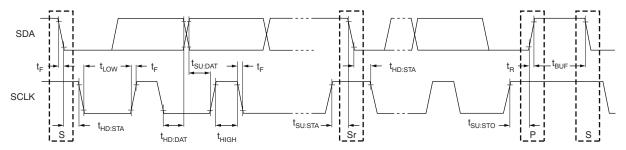

# 7.6 Timing Requirements

At  $V_{DD}$  = 3 V or +5 V, and  $T_A$  = -40°C to +125°C, unless otherwise noted.

|                     | PARAMETER                 | MIN | TYP I | MAX  | UNIT |

|---------------------|---------------------------|-----|-------|------|------|

| f <sub>SCLK</sub>   | Clock frequency           |     |       | 100  | kHz  |

| t <sub>BUF</sub>    | Bus free time             | 4.7 |       |      | μs   |

| t <sub>SU:STA</sub> | Start setup time          | 4.7 |       |      | μs   |

| t <sub>HD:STA</sub> | Start hold time           | 4   |       |      | μs   |

| t <sub>SU:STO</sub> | Stop condition setup time | 4   |       |      | μs   |

| t <sub>LOW</sub>    | SCLK low time             | 4.7 |       |      | μs   |

| t <sub>HIGH</sub>   | SCLK high time            | 4   |       |      | μs   |

| t <sub>R</sub>      | SCLK, SDA rise time       |     |       | 1000 | ns   |

<sup>(2)</sup> Not production tested. Specified by design.

At  $V_{DD}$  = 3 V or +5 V, and  $T_A$  = -40°C to +125°C, unless otherwise noted.

|                     | PARAMETER                                                                                                                   | MIN | TYP | MAX | UNIT |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| t <sub>F</sub>      | SCLK, SDA fall time                                                                                                         |     |     | 300 | ns   |

| t <sub>SU:DAT</sub> | Data setup time                                                                                                             | 350 |     |     | ns   |

| t <sub>HD:DAT</sub> | Data hold time                                                                                                              | 350 |     |     | ns   |

| t <sub>POR</sub>    | Time from software reset command or power-on to normal operation. During this period, I2C™ communication is not recognized. |     |     | 1.5 | ms   |

図 7-1. Timing Specification

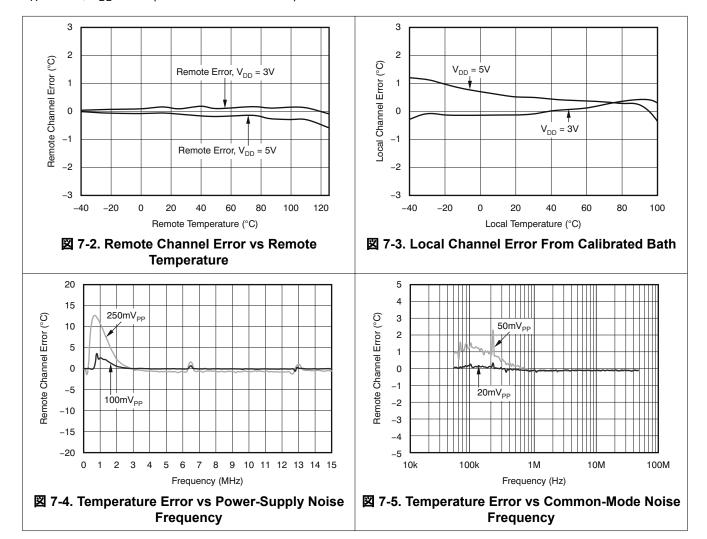

# 7.7 Typical Characteristics

$T_A = 25$ °C,  $V_{DD} = 5$  V (unless otherwise noted)

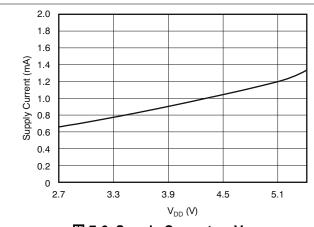

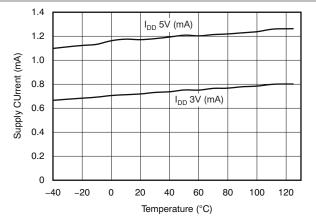

図 7-6. Supply Current vs V<sub>DD</sub>

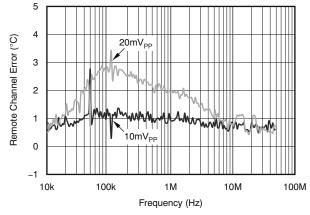

☑ 7-8. Temperature Error vs Differential Mode Noise Frequency

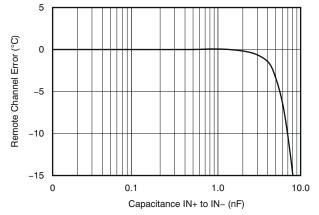

図 7-9. Temperature Error vs Capacitance Between In+ and In-

図 7-10. PWM Frequency Error vs Temperature

# 8 Detailed Description

# 8.1 Functional Block Diagram

## 8.2 Feature Description

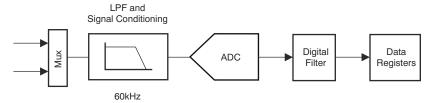

#### 8.2.1 ADC Converter

⊠ 8-1 shows the 11-bit, on-chip analog-to-digital converter (ADC) of the AMC6821-Q1. This ADC converts the analog input into digital format. The analog input is passed through front-end signal conditioning circuitry to remove the noise. The resulting signal is then converted by the ADC. To further reduce the effects of noise, digital filtering is performed by averaging the results of 32 measurement cycles. After digital filtering, the newest result is stored in the temperature data register (low byte and high byte) in two's complement format. The ADC stops when the START bit of Configuration Register 1 is cleared ('0') and runs when START = 1.

図 8-1. On-Chip Analog-to-Digital Converter

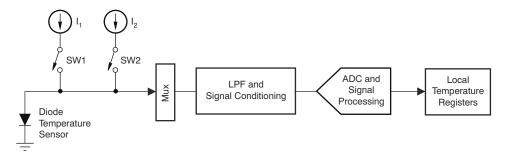

## 8.2.2 Temperature Sensor

The AMC6821-Q1 has an integrated temperature sensor (shown in  $\boxtimes$  8-2) to measure the ambient temperature, and one remote diode sensor (such as a Pentium thermal diode) input to measure external (CPU) temperature. The measurement relies on the characteristics of a semiconductor junction operation at a fixed current level. The

forward voltage of the diode ( $V_{BE}$ ) depends on the current through it and the ambient temperature. The change in  $V_{BE}$  when the diode is operated at two different currents,  $I_1$  and  $I_2$ , is shown in  $\neq 1$ :

$$\Delta V_{BE} = \frac{KT}{q} \times In(N) \tag{1}$$

#### where

- k is Boltzmann's constant,

- · q is the charge of the carrier,

- · T is the absolute temperature in degrees Kelvin, and

- N is the ratio of the two currents.

図 8-2. Integrated Local Temperature Sensor

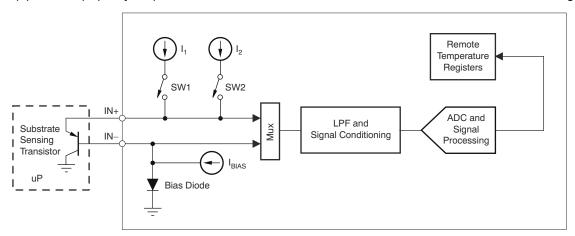

The remote sensing transistor can be a substrate transistor built within the microprocessor (as in a Pentium-IV), or a discrete small-signal type transistor. This architecture is shown in 🗵 8-3. The internal bias diode biases the IN– terminal above ground to prevent the ground noise from interfering with the measurement. An external capacitor (up to 1000pF) may be placed between IN+ and IN– to further reduce the noise from interfering.

図 8-3. Remote Temperature Sensor

The analog sensing signal is pre-processed by a low-pass filter and signal conditioning circuitry, then digitized by the ADC. The resulting digital signal is further processed by the digital filter and processing unit. The final result is stored in the local temperature data register and remote temperature data register, respectively. The eight MSBs are stored in the corresponding Temp-DATA-HByte register, and the three LSBs are stored in the Temperature Data Registers section for details.

The format of the final result is in two's complement; see  $\pm$  8-1. It should be noted that the device measures the temperature from  $-40^{\circ}$ C to  $+125^{\circ}$ C, although the code represents temperature from  $-128^{\circ}$ C to  $+127^{\circ}$ C.

Copyright © 2023 Texas Instruments Incorporated

Submit Document Feedback

#### 8.2.2.1 Series Resistance Cancellation

Parasitic resistance (seen in series with the remote diode) to the IN+ and IN- inputs to the AMC6821-Q1 is caused by a variety of factors, including printed circuit board (PCB) trace resistance and trace length. This series resistance appears as a temperature offset in the remote sensor temperature measurement, and causes more than 0.45°C error per ohm. The AMC6821-Q1 is implemented with a TI-patented technology to automatically cancel out the effect of this series resistance, giving a more accurate result without the need for user characterization of this resistance. With this technology, the AMC6821-Q1 is able to reduce the effects of series resistance to typically less than 0.0025°C per ohm.

# 8.2.2.2 Reading Temperature Data

It is important to note that temperature can be read by an 8-bit value (with 1°C of resolution) from the Temp-DATA-HByte register, or as an 11-bit value (with 0.125°C of resolution) from the Temp-DATA-LByte and Temp-DATA-HByte registers. If only 1°C of resolution is required, the temperature readings can be read back at any time and in no particular order. If reading the 11-bit measurement is required, the process involves a two-register read for each measurement. To get an 11-bit result of the remote sensor, the controller must read the Temp-DATA-LByte register (0x06) first, and then the Remote-Temp-DATA-HByte register (0x0B) to complete the reading. However, to get bit 11 of the local sensor only, or to get both local and remote sensors, the controller must read Temp-DATA-LByte first, Local-Temp-DATA-HByte (0x0A) second, and Remote-Temp-DATA-HByte third. This method causes all associated temperature data registers to be frozen until the Remote-Temp-DATA-HByte register has been read. This process also prevents the high byte data from being updated while the three LSBs are being read, and vice-versa.

表 8-1. Temperature Data Format

| 表 8-1. Temperature Data Format |                               |  |  |  |  |

|--------------------------------|-------------------------------|--|--|--|--|

| TEMPERATURE (°C)               | BINARY DIGITAL CODE (11 BITS) |  |  |  |  |

| +127                           | 01111111000                   |  |  |  |  |

| +125                           | 01111101000                   |  |  |  |  |

| +100                           | 01100100000                   |  |  |  |  |

| +75                            | 01001011000                   |  |  |  |  |

| +50                            | 00110010000                   |  |  |  |  |

| +25                            | 00011001000                   |  |  |  |  |

| +10                            | 00001010000                   |  |  |  |  |

| +1                             | 0000001000                    |  |  |  |  |

| 0                              | 0000000000                    |  |  |  |  |

| -1                             | 11111111000                   |  |  |  |  |

| -25                            | 11100111000                   |  |  |  |  |

| -50                            | 11001110000                   |  |  |  |  |

| <b>-75</b>                     | 10110101000                   |  |  |  |  |

| -100                           | 10011100000                   |  |  |  |  |

| -125                           | 10000011000                   |  |  |  |  |

| -128                           | 1000000000                    |  |  |  |  |

#### 8.2.2.3 Temperature Out-of-Range Detection

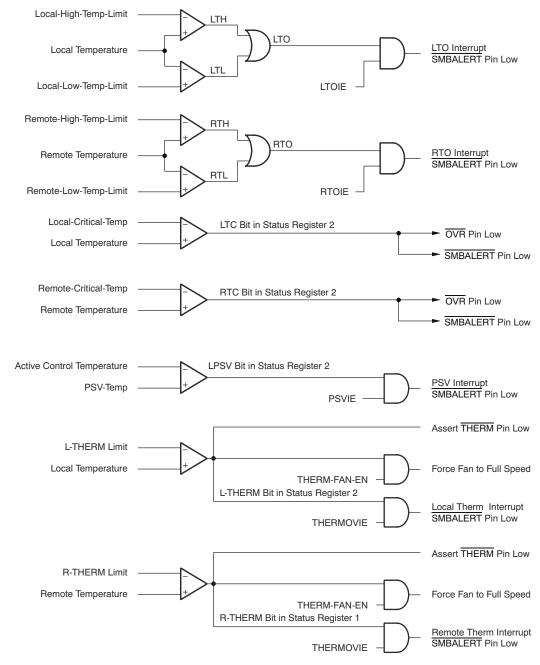

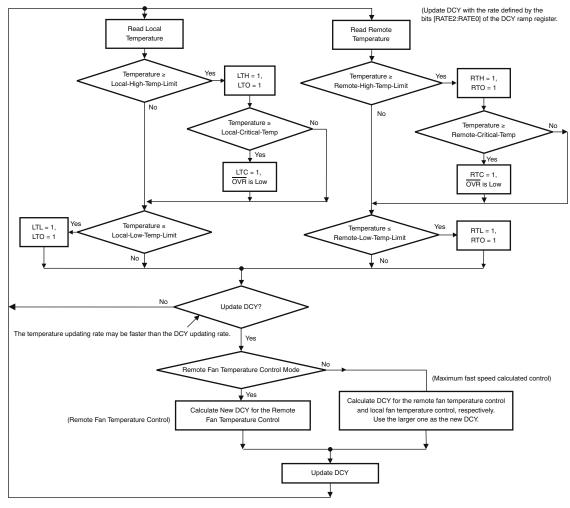

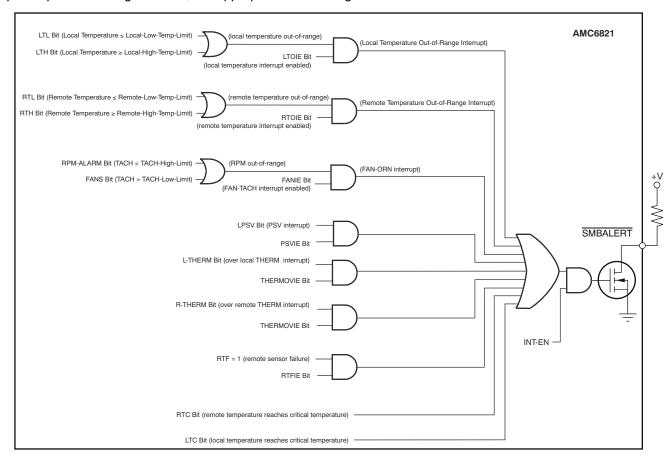

The AMC6821-Q1 has the following temperature limitation detections:

- 1. High and Low Temperature Limit: The value of the High-Temp-Limit and Low-Temp-Limit registers specify the remote or local temperature ranges of normal operation. When the local or remote temperatures are equal to or above the value of the corresponding High-Temp-Limit register, the LTH or RTH bits in the status register are set ('1'). Likewise, when the local or remote temperatures are less than or equal to the corresponding Low-Temp-Limit register, the LTL or RTL bits in the status register are set ('1').

- When the local temperature is out-of-range (LTH = 1 or LTL = 1), the local temperature out-of-range event occurs. The LTO bit in the status register is set ('1'), and the LTO interrupt is generated via the  $\overline{\text{SMBALERT}}$  pin if it is enabled (the LTOIE bit of Configuration Register 2 is set). Similarly, when the remote temperature is out-of range (RTH = 1 or RTL = 1), the remote temperature out-of-range event occurs. The RTO bit in the status register is set ('1'), and the RTO interrupt is generated via the  $\overline{\text{SMBALERT}}$  pin if it is enabled (that is, the RTOIE bit of Configuration Register 2 is set).

- 2. **Critical Limit:** Critical temperature limit is the highest allowed of remote or local temperature. When the temperature is greater than or equal to the corresponding critical temperature, the LTCT or RTCT bit of the status register is set ('1'), the output of the OVR pin goes low, and a non-maskable interrupt is generated through the SMBALERT pin (low).

- 3. Passive Cooling Temperature (PSV) Limit: This limit defines the passive cooling threshold. In the auto remote-temperature-fan control mode, the system enters a passive cooling condition when the remote temperature is equal to or below this limit, and the fan stops. In the maximum fast speed calculated control mode, the fan stops and the system enters a passive cooling condition when both the remote and local temperatures are equal to or below this limit. In passive cooling, the LPSV bit of Status Register 2 (0x03) is set ('1'), and a PSV interrupt is generated on the SMBALERT pin if enabled (PSVIE = 1). Note that reading the Status Register clears the LPSV bit. After reading, if the active control temperature remains equal to or below the PSV temperature, this bit reasserts on next monitoring cycle.

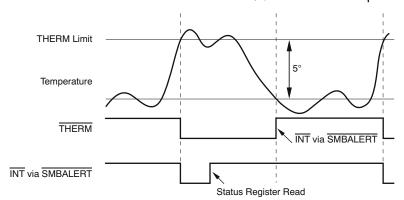

4. **THERM Limit:** This limit is an additional *fail-safe* threshold. When the local or remote temperature is equal to or above this limit, the corresponding L-THERM or R-THERM bit is set ('1'), and the THERM pin is asserted low, which can be used to throttle the CPU clock. Furthermore, the THERM interrupt is generated on the SMBALERT pin if enabled (THERMOVIE = 1). Reading Status Register 1 clears the R-THERM and L-THERM bits. Once cleared, these bits are not reasserted until the temperature falls 5°C below the THERM limit, even if the THERM condition persists. If the THERM-FAN-EN bit of Configuration Register 3 is set ('1'), L-THERM = 1 or R-THERM = 1 forces the fan to run at full speed. When THERM-FAN-EN = 0, the status of the L-THERM and R-THERM bits do not affect the fan speed directly. Note that the THERM limit can be lower or higher than other temperature limits. For example, if the THERM limit is lower than the PSV temperature limit, then the CPU clock can be throttled while the cooling fan is off.

図 8-4. Temperature Out-of-Range Detection

#### 8.2.2.4 Remote Temperature Sensor Failure Detection

The remote temperature sensor failure detection determines whether the remote sensor diode has an open-circuit condition, a short-circuit to ground, or a short-circuit (IN+) to (IN-) condition. This fault detection is based on the analog input voltage and is not checked until the first monitoring cycle is completed after power-on.

Reading the fault sensor returns a value of  $-128^{\circ}$ C (0x80). Since the power-on default value of the temperature data registers is 0x80 ( $-128^{\circ}$ C), a reading of 0x80 from the temperature data register immediately after power-on does not indicate a diode fault condition. The remote temperature sensor failure is only checked after the first monitoring cycle has been completed after power-on or reset.

When a remote sensor failure occurs, the remote sensor failure bit (RTF in the Status Register) is set to '1', the  $\overline{\text{OVR}}$  pin is forced low, and if the interrupt is enabled (RTFIE = 1), the RTF interrupt is generated through the  $\overline{\text{SMBALERT}}$  pin. Once this interrupt is generated, the RTF bit remains '1' and the  $\overline{\text{OVR}}$  pin stays low until a power-on reset or software reset is issued, whether or not the failure condition persists.

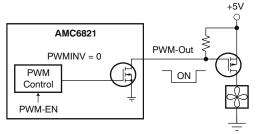

## 8.2.3 PWM Output

The PWM-Out pin is an open-drain output. When PWM-EN of Configuration Register 2 is cleared ('0'), the PWM-Out pin is disabled and goes into a high-impedance status. When PWM-EN is set ('1'), the PWM-Out pin is enabled to drive the fan. When enabled, the status of the PWM-Out pin is determined by the PWM duty cycle and phase bits (PWMINV of Configuration Register 1). When PWMINV = 0 (default), the PWM-Out pin goes low for 100% duty cycle (suitable for driving the fan using a PMOS FET). Setting PWMINV to '1' makes the PWM-Out pin go high (with an external pull-up resistor) for a 100% duty cycle. This setting is used to drive an NMOS-power FET.

PWMINV = 0 (default) for driving the PMOS.

PWMINV = 1 for driving the NMOS.

図 8-5. PWM Output

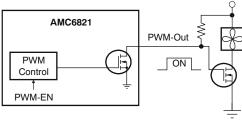

#### 8.2.4 PWM Waveform Setting

PWM frequency and duty cycle are programmable. The value of the DCY Register defines the duty cycle: it has 8-bit resolution, 1LSB corresponding to 1/255 (0.392%). Writing 0x00 sets the duty cycle to 0%; writing 0xFF sets the duty cycle to 100%.

PWM frequency has two ranges: the high range is from 1kHz to 40kHz, and the low range is from 10Hz to 94Hz. The PWM-MODE pin status determines which range is selected. When the PWM-MODE pin is tied to ground, the high range is selected. Otherwise, the low range is selected. Bits [PWM2:PWM0] in the Fan Characteristics Register define the frequency; see 表 8-2. The resolution of the PWM waveform period is 0.312µs, corresponding to a 3.2MHz clock. The default value after power-on is 30Hz when the low range is selected, or 25kHz when the high range is selected.

図 8-6. PWM Waveform (PWMinv = 1)

表 8-2. PWM Frequency

| PWM2 | PWM1       | PWM0       | PWM FREQUENCY                          |  |  |  |  |

|------|------------|------------|----------------------------------------|--|--|--|--|

| Whe  | en the PWN | I-MODE Pir | is Floating or Tied to V <sub>DD</sub> |  |  |  |  |

| 0    | 0          | 0          | 10Hz                                   |  |  |  |  |

| 0    | 0          | 1          | 15Hz                                   |  |  |  |  |

| 0    | 1          | 0          | 23Hz                                   |  |  |  |  |

| 0    | 1          | 1          | 30Hz (default)                         |  |  |  |  |

| 1    | 0          | 0          | 38Hz                                   |  |  |  |  |

| 1    | 0          | 1          | 47Hz                                   |  |  |  |  |

| 1    | 1          | 0          | 62Hz                                   |  |  |  |  |

| 1    | 1          | 1 1 94Hz   |                                        |  |  |  |  |

|      | When the   | PWM-MOD    | E Pin is Tied to GND                   |  |  |  |  |

| 0    | 0          | 0          | 1kHz                                   |  |  |  |  |

| 0    | 0          | 1          | 10kHz                                  |  |  |  |  |

| 0    | 1          | 0          | 20kHz                                  |  |  |  |  |

| 0    | 1          | 1          | 25kHz (default)                        |  |  |  |  |

| 1    | 0          | 0          | 30kHz                                  |  |  |  |  |

| 1    | 0          | 1          | 40kHz                                  |  |  |  |  |

| 1    | 1          | 0          | 40kHz                                  |  |  |  |  |

| 1    | 1          | 1          | 40kHz                                  |  |  |  |  |

## 8.2.5 Fan Speed Measurement

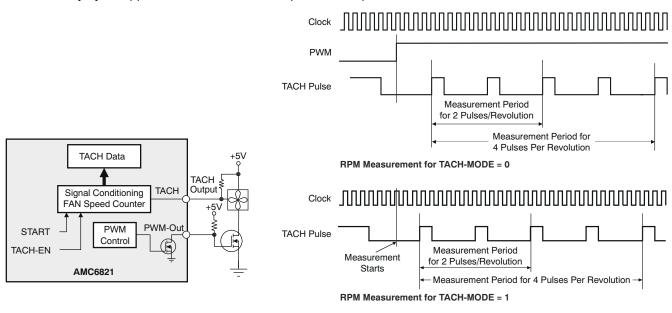

The AMC6821-Q1 monitors the fan speed (RPM) via the TACH pin, as illustrated in 🗵 8-7. The TACH-EN bit of Configuration Register 2 (bit 2, 0x01) enables the fan speed measurement. When TACH-EN is cleared ('0'), the measurement is disabled. The measurement is enabled when the TACH-EN bit is set to '1'. This section describes the device behavior when TACH-EN is set ('1').

The on-chip fan-speed counter does not count the fan tach output pulses directly because of the low RPM of the fan. Instead, the period of the fan revolution is measured by gating an on-chip clock (100kHz). The result is stored in the TACH-DATA Register that contains two bytes (16 bits total). RPM monitoring is disabled when the START bit of Configuration Register 1 or the TACH-EN bit of Configuration Register 2 is cleared ('0'), and is enabled when START = 1 and TACH-EN = 1.

If the TACH-MODE bit is cleared, RPM monitoring stops and the TACH-DATA register is not updated when the duty cycle is less than 7% for the software duty cycle mode and auto-temperature-fan control modes. In software-RPM mode, RPM monitoring is always performed and updated after each monitoring. If the TACH mode = '1' the RPM monitoring is always performed, and the TACH data are always updated after each monitoring.

## 8.2.5.1 Tach-Data Register

Two fan tach pulse periods (PSPR = 0) or four tach pulse periods (PSPR = 1) are measured and the result is stored in the TACH-DATA Register, as shown in  $\boxtimes$  8-7. Counting stops if the counter is over-range; the measurement cycle repeats until monitoring is disabled, and the fan speed (RPM) can be calculated as shown in  $\rightrightarrows$  2:

$$RPM = \frac{(100,000 \times 60)}{\text{(Value of TACH-DATA Register)}}$$

(2)

#### 8.2.5.1.1 Reading the Tach Data Register

To read the fan speed, both TACH-DATA-LByte and TACH-DATA-HByte must be read. TACH-DATA-LByte must be read first. This reading causes TACH-DATA-HByte to be frozen until both the high and low byte registers have been read from, preventing TACH reading errors.

#### 8.2.5.1.2 RPM Measurement Rate

The TACH-FAST bit of Configuration Register 4 determines the rate. When TACH-FAST = 1, the TACH-DATA Register is updated every 250ms (fast monitoring). When TACH-FAST = 0 (default), the reading is updated every second (standard monitoring period).

#### 8.2.5.1.3 Select Number of Pulses/Revolution

The speed sensor of most common fans provides two or four TACH pulses per revolution. The PSPR bit of Configuration Register 4 specifies how many pulses per revolution are generated. PSPR = 1 indicates four pulses/revolution and PSPR = 0 (default) indicates two pulses/revolution.

#### 8.2.5.1.4 Tach Mode Selection

The TACH-MODE bit of Configuration Register 2 specifies the TACH pulse output mode of the fan. Some fans (such as three- and two-wire) are powered directly by the PWM, and must be *PWM-On* to provide a TACH pulse output. When the PWM-Out pin switches these fans ON/OFF directly, the PWM-Out must be kept ON to power the fan during the measurement. In this case, the TACH-MODE bit of Configuration Register 2 must be cleared ('0'). When TACH-MODE = 0, the PWM-Out pin is kept ON during the critical tach edges of the measurement period. Clearing the TACH mode ('0') also enables the internal correction circuitry to correct the error caused by the extra duty cycle applied in the measurement period. The power-on default value of the PWM mode is '0'.

図 8-7. Fan Speed Measurement

a) Block Diagram of Fan Speed Monitoring

b) Measuring the Period of TACH Pulses to Determine the Fan Speed

Some fans (such as the JMC® four-wire fan) are powered directly by dc power, instead of being powered by the PWM. In this case, the TACH mode must be set to '1'. When TACH-MODE = 1, the PWM-Out pin is not forced ON; instead, the status is controlled completely by the DCY register, just as in normal operation. Setting TACH-MODE to '1' also disables the internal correction circuit because no extra duty cycle is applied. Setting the TACH mode to '1' allows TACH reading continuously, regardless of the status of the PWM-Out pin.

The selection of the TACH mode affects the RPM monitoring and control. When the TACH-MODE bit is equal to '1', the duty cycle of the PWM-Out pin is always determined by the calculated value; the TACH data are always updated at every RPM monitoring. However, when the TACH-MODE bit is equal to '0', in the Software-RPM Control mode the PWM-Out pin is forced to 30% if the calculated duty cycle is less than 30%; in other modes, the PWM-Out pin is forced to 0% and the TACH data are not updated if the calculated duty cycle is less than 7%.

#### 8.2.5.1.5 Fan RPM Out-of-Range Detection

The larger value of the TACH data corresponds to a slower speed. When the TACH data are larger than the TACH-Low-Limit, the fan runs at a speed below the predefined minimum RPM, and the FANS bit in Status Register 1 is set to '1'. Note that no FANS (fan-slow) detections are made during spin-up. The FANS bit is cleared ('0') only after reading this register and reasserted ('1') in the next monitoring if a fan-slow is detected. After spin-up, FANS is set ('1') even if the TACH data are less than the TACH-Low-Limit until the register is read.

When the TACH data are less than the TACH-High-Limit, the fan runs at a speed above the predefined maximum RPM, and the RPM-ALARM bit in Status Register 1 is set ('1'). Note that the RPM-ALARM bit is cleared when reading the register. Once cleared, this bit is not reasserted in the next monitoring cycle even if the condition persists. This bit may be reasserted only if the RPM drops below the allowed maximum speed.

When FANS = 1 or RPM-ALARM = 1, there is a fan-out-of-range interrupt and FAN-ORN is generated if the FANIE bit in Configuration Register 1 is set ('1'). This interrupt makes the SMBALERT pin go low.

図 8-8. RPM Out-of-Range Detection

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

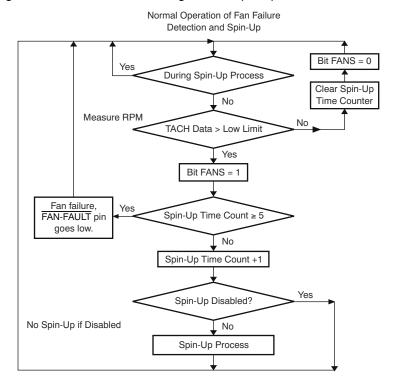

#### 8.2.6 Fan Failure Detection

When the TACH data are larger than the TACH low limit, the fan runs at a speed below the predefined minimum RPM. When this condition occurs, a spin-up process is applied to start the fan again when spin-up is enabled. Bits [STIME2:STIME0] of the Fan Characteristics Register define this time period.

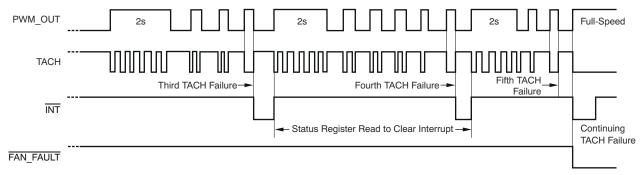

8-9 shows the function of the fan failure detection. Refer to the Fan Spin-Up section.

The fan speed is measured immediately after spin-up; the TACH-FAST bit of Configuration Register 4 determines the monitoring rate. If the fan does not return to a normal range after five consecutive spin-ups, a FAN-FAILURE occurs; the FAN-FAULT pin goes low when it is enabled (the FAN-FAULT-EN bit of Configuration Register 1 is set), and the spin-up process continues. If the fan returns to a normal speed range before the fifth spin-up, the FAN-FAULT pin does not go low even though the FANS bit is still set to '1'. No FANS (fan-slow) detections are performed during spin-up. After the FAN-FAULT pin goes low, spin-up is performed indefinitely until the RPM reading returns to within normal range or the spin-up is disabled.

Measure the RPM continuously once every 0.25s (TACH-FAST bit = 1) or 1s (TACH-FAST = 0), even after a fan failure. However, there are no FANS detections during spin-up.

The FAN-FAULT pin is negated if the fan returns to a normal RPM range.

図 8-9. Fan Failure Detection and Spin-Up

The SMBALERT pin continues to generate interrupts after the assertion of the FAN-FAULT pin because the tach measurement continues even after a fan failure. Should the fan recover from the failure condition, the FAN-FAULT pin signal is negated and the fan returns to normal operating speed. ☒ 8-10 shows the operation of a FANS interrupt.

INT is a Fan-Slow (FANS) Interrupt Through the SMBALERT Pin

図 8-10. Operation of the FAN-FAULT Pin With a Spin-Up Time = 2 Seconds

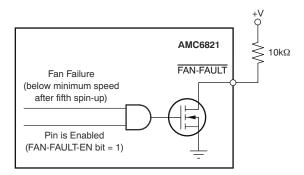

#### 8.2.7 FAN-FAULT Pin

The FAN-FAULT pin is an open-drain output pin (see 🗵 8-11). When the FAN-FAULT-EN bit of Configuration Register 1 is cleared ('0'), this pin is disabled and is always in a high-impedance status. When FAN-FAULT-EN = 1, the pin is enabled and the status indicates a fan-failure. The pin asserts low when a fan failure occurs. FAN-FAULT is negated when the fan returns to normal speed.

図 8-11. FAN-FAULT Pin

#### 8.2.8 Fan Control

## 8.2.8.1 THERM Pin and External Hardware Control

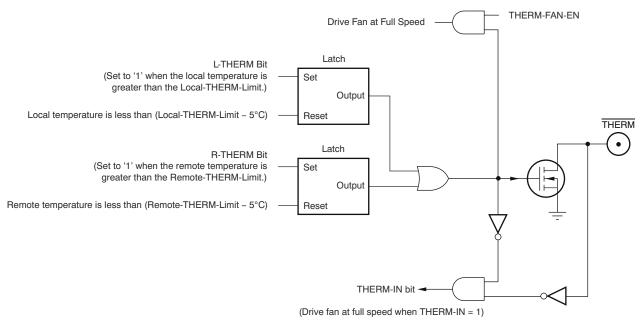

8-12 shows the THERM pin is a bidirectional I/O.

#### 8.2.8.1.1 THERM Pin as an Output

As an open-drain output, the THERM pin is the indicator of temperature over the THERM limit. When the remote temperature exceeds the Remote-THERM-Limit, or when the local temperature is greater than the Local-THERM-Limit, the THERM pin goes low and remains low until the measured temperature falls 5°C below the exceeded THERM limit.

図 8-12. Structure of the THERM Pin

When the THERM limit is exceeded, the corresponding status flag bit (R-THERM or L-THERM of Status Register 1 or Status Register 2) is set to '1', and the THERM interrupt through the SMBALERT pin is generated if it is enabled (THERMOVIE of bit Configuration Register 1 is set to '1'). This interrupt forces the SMBALERT pin low. Note that the THERM pin is always forced to low when R-THERM = 1 or L-THERM = 1, no matter what the status of THERMOVIE is. Reading the status registers clears the flag bit (R-THERM and L-THERM). Clearing the flag bit makes the SMBALERT pin go back to high, but does not negate the THERM pin. It remains low until the temperature falls 5 C below the exceeded THERM limit. After this bit is cleared, the active flag bit (R-THERM for remote temperature or L-THERM for local temperature) and the THERM interrupt are not re-armed until the temperature falls 5°C below the exceeded THERM limit.  $\boxtimes$  8-13 shows this procedure.

図 8-13. Operation of the Therm Interrupt and the THERM Pin

When working as an output, the status of the  $\overline{THERM}$  pin affects the RPM fan. If the THERM-FAN-EN bit is set ('1'), the fan goes to full-speed (that is, the duty cycle is 100%) when the  $\overline{THERM}$  pin goes low. However, when THERM-FAN-EN = 0, the status of the  $\overline{THERM}$  pin does not affect the fan speed.

#### 8.2.8.1.2 THERM Pin as an Input

When this pin works as input, it is the input of the external hardware control signal; the THERM-IN bit of Status Register 2 reflects the input. When the THERM pin is pulled low as an input, THERM-IN is set ('1') and the fan is driven at full speed (that is, the duty cycle is 100%), no matter what THERM-FAN-EN is. The THERM-FAN-EN bit has no effect when the THERM pin works as an input.

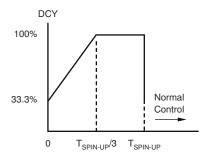

#### 8.2.8.2 Fan Spin-Up

The PWM duty cycle controls the cooling fan speed. To spin up a fan from a stopped state or under-speed status, the spin-up process is applied to overcome the fan inertia. During the first third of spin-up, the duty cycle of the PWM gradually increases from 33.3% to 100%, and then maintains at 100% through the rest of the process. At the end of the spin-up process, the duty cycle is adjusted to 33.3%. After starting, the fan speed is controlled normally. 図 8-14 shows the spin-up process. The bits [STIME2:STIME0] (bits 2:0 of 0x20) define the spin-up time, from 0.2 seconds to 8 seconds, as shown in 表 8-3. Fan speed is monitored immediately after the spin-up process.

Spin-up is disabled by setting the FSPD bit of the Fan Characteristics Register to '1'. If disabled, the spin-up process is not applied when the fan stops or an RPM is detected below the minimum speed. The TACH low limit register defines the minimum speed. After power-on or reset, the FSPD bit is cleared and the spin-up is always performed, regardless of the state of the FANS bit (bit 1 of 0x02).

Note that no FANS (fan-slow) detections are performed during spin-up. This bit is cleared ('0') only after reading it, and reasserts '1' in the next monitoring if a fan-slow condition is detected. After spin-up, FANS is set ('1') even if the TACH data are less than the TACH low limit until the flag is read.

図 8-14. Spin-Up Process

表 8-3. Spin-Up Time

| STIME2 | STIME1 | STIME0 | SPIN-UP TIME (SECONDS) |

|--------|--------|--------|------------------------|

| 0      | 0      | 0      | 0.2                    |

| 0      | 0      | 1      | 0.4                    |

| 0      | 1      | 0      | 0.6                    |

| 0      | 1      | 1      | 0.8                    |

| 1      | 0      | 0      | 1                      |

| 1      | 0      | 1      | 2 (default)            |

| 1      | 1      | 0      | 4                      |

| 1      | 1      | 1      | 8                      |

#### 8.2.8.3 Normal Fan Speed Control

The fan speed is controlled by four different modes:

- software DCY control;

- software RPM control,

- auto remote temperature fan control;

- maximum fast-speed calculated control.

The Auto Temperature-Fan Control mode consists of auto remote temperature-fan control and maximum fast-speed calculated control. It is an intelligent closed-loop control. In this mode, the fan speed is controlled either by the remote temperature (Auto-Remote Temperature-Fan Control) or by maximum speed calculated for internal and remote temperature. This control mode optimizes fan speed for a given temperature to intelligently manage the system thermals/acoustics. The user writes the proper registers to define the linear feedback control algorithm parameters. After programming, the AMC6821-Q1 runs stand-alone, even without the intervention of the micro-controller. It ensures that if the controller or system locks up, the fan can still be controlled based on temperature measurements, and the fan speed adjusted to correct any changes in system temperature. Software-RPM works as a fan speed regulator to maintain the speed at a programmable target value. It is a closed-loop mode and can run stand-alone as well. The Software-DCY mode is an open-loop mode; the PWM output duty cycle changes to the target value immediately after the user writes the desired duty cycle to the device registers.

Bits FDRC1 and FDRC0 in Configuration Register 1 determine the operation mode.

#### 8.2.8.3.1 Software DCY Control Mode

When the bits [FDRC1:FDRC0] = [00], the fan works in the software DCY control mode. The host writes the desired duty cycle value corresponding to the required RPM into the DCY register. The duty cycle changes to the new value immediately after the writing. In this mode, if the TACH measurement is enabled (bit 2 of 0x01 = 1) and the TACH-MODE bit (bit 1 of 0x01) is cleared ('0'), the duty cycle from the PWM-OUT pin is forced to 0% when the value in the DCY register is less than 7%. However, if the TACH measurement is disabled (bit 2 of 0x01 is cleared) or the TACH mode is set ('1'), the DCY register always keeps the programmed value written by the host and is not forced to '0' even when the programmed value is less than 7%.

#### 8.2.8.3.2 Software-RPM Control Mode (Fan Speed Regulator)

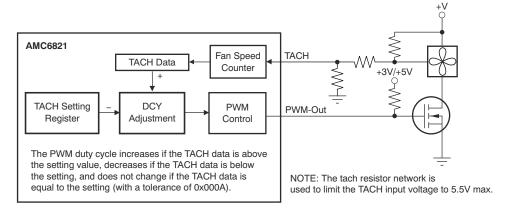

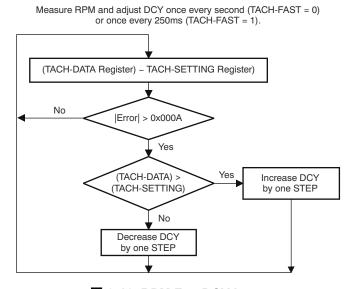

This mode works as a fan speed regulator that maintains the speed at a programmable target value. It works only when the TACH measurement is enabled (bit 2 of 0x02 = 1). When the bits [FDRC1:FDRC0] = [01], the fan works in the software RPM control mode, as shown in  $\boxtimes$  8-15. The host writes the proper value into the TACH Setting Register to set the target fan speed. The actual fan speed is monitored by an on-chip fan speed counter, and the result is stored in the TACH-DATA Register (refer to the Fan Speed Measurement section for more details). The actual speed is compared with the setting value. If there is a difference, the duty cycle is adjusted.

図 8-15. Software RPM Control

The monitoring and adjustment is made once every second, or once every 250ms, as determined by the TACH-FAST bit of Configuration Register 4 (bit 5, 0x04). Bits [STEP1:STEP0] of the DCY-RAMP Register define the allowed amount of each adjustment. When the difference between the values of the TACH-DATA and TACH Setting Registers are equal to or less than 0x000A, the adjustment finishes. 0x000A corresponds to about 1.8% tolerance for 10,000RPMs, or 0.9% for 5000RPMs. This measurement architecture is illustrated in  $\boxtimes$  8-16.

In practice, the selected target speed must be not too low to operate the fan. When the TACH-MODE bit (bit 1 of 0x02) is cleared ('0'), the duty cycle of PWM-Out is forced to 30% when the calculated desired value of duty cycle is less than 30%. Therefore, the TACH setting must be not greater than the value corresponding to the RPM for 30% duty cycle. When TACH mode = '1', the TACH setting must not be greater than the value corresponding to the allowed minimum RPM at which the fan runs properly.

図 8-16. RPM Fan DCY Loop

#### 8.2.8.3.3 Auto Temperature Fan Mode

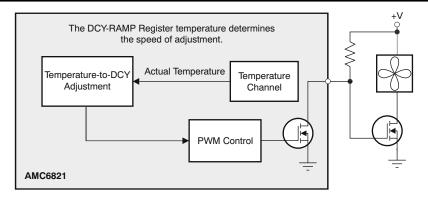

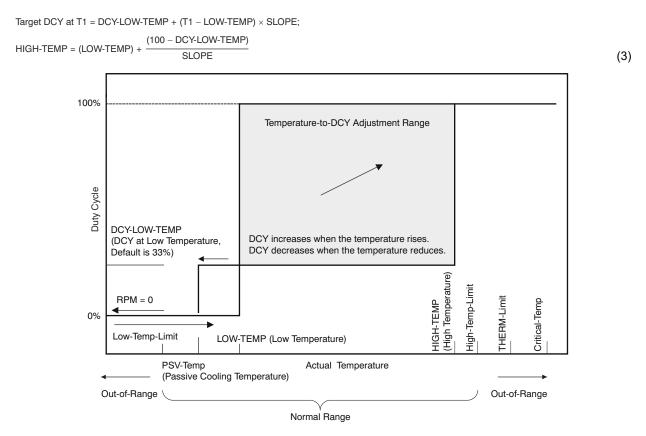

The Auto Temperature-Fan mode is a closed-loop control that optimizes fan speed for a given temperature to intelligently manage the system thermals/acoustics. It runs stand-alone even without the intervention of a controller. The AMC6821-Q1 has two auto temperature fan control modes. When the bits [FDRC1:FDRC0] = [10] (default), the fan is in the Auto Remote Temperature-Fan Speed control mode. The temperature reading from the remote temperature sensor is the active control temperature that controls the PWM duty cycle. When the bits [FDRC1:FDRC0] = [11], the fan is in the maximum fast-speed calculated control mode. The local temperature and the remote temperature have independently-programmed control loops with different parameters. In the maximum fast-speed calculated control mode, the required fan speed is calculated for the remote and local channels, respectively. Whichever control loop calculates the fastest speed based on the measured temperature drives the fan. After the monitor starts, the PWM duty cycle is determined by the actual control temperature. When the temperature is above the low temperature and below the high temperature, the internal control loop automatically adjusts the duty cycle to a proper value according to the measured temperature. When the temperature rises, the duty cycle increases to a higher value; when the temperature drops, the duty cycle reduces. This architecture makes the fan always run at an optimal speed. This adjustment is based on the control-loop parameters defined in the Local TEMP-FAN Control Register, Remote TEMP-FAN Control Register, and the DCY-RAMP Register. Changing the parameters changes the desired value of the duty cycle and the fan speed.

図 8-17. Auto Fan Temperature Loop

The bits [R-TEMP4:R-TEMP0] of the Remote TEMP-FAN Control Register and the bits [L-TEMP4:L-TEMP0] of the Local TEMP-FAN Control Register are the low temperature bits that define the low temperature of the control loops. Bits [SPL2:SPL0] of these registers are the slope bits that define the increment of the duty cycle when the temperature increases 1°C. The bits [RATE2:RATE0] of the DCY-RAMP Register (bits [4:1], 0x23) specify the updating rate of the duty cycle in the temp-fan control mode, and the bits [STEP1:STEP0] define how much the duty cycle is adjusted by each updating. The target duty cycle for temperature T1 and the HIGH-TEMP (high temperature) can be calculated by  $\vec{x}$  3:

図 8-18. Active Control Temperature—PWM Duty Cycle

When the active control temperature is equal to or below the corresponding low temperature, the duty cycle is equal to the value of the DCY-LOW-TEMP Register and the fan runs at a predefined minimum speed. When the control temperature is equal to or higher than the corresponding high temperature, the PWM duty cycle is set to 100% and the fan runs at full speed. When the active control temperature is equal to or below the corresponding

value of the PSV-Temp Register (the predefined passive cooling temperature), the fan stops and the PWM duty cycle is set to 0.

When the actual duty cycle is different from the desired value, the duty cycle is adjusted automatically. When the RAMPE bit of the DCY-RAMP Register is cleared ('0'), the duty cycle changes to the desired value immediately after being calculated. When the RAMPE bit is '1', the duty cycle changes to the new value gradually.

The DCY-RAMP Register specifies how quickly the duty cycle changes. The duty cycle can be checked every 0.0625 second to every eight seconds, depending on the bits [RATE2:RATE0] bits. It changes 1/255(0.392%) to 4/255 (1.57%) each time, depending on the bits [STEP1:STEP0] bits. When the difference between the actual value and the target value is equal to or less than the adjustment threshold (as defined by the bits [THRE1:THRE0] bits), the adjustment finishes. See the DCY-RAMP Register for details. When the TACH monitoring is enabled (TACH-EN bit, bit 2 of 0x02, is set to '1') and the TACH-MODE bit (bit 1 of 0x02) is cleared ('0'), the duty cycle is forced to 0% when the calculated value is less than 7%. If the TACH monitoring is disabled (TACH-EN = 0) or the TACH-MODE bit is set ('1'), the duty cycle is always set to the calculated value even if the value is less than 7%.

図 8-19. Temperature Monitoring Flow Chart

#### 8.2.9 Interrupt

The AMC6821-Q1 provides two interrupt output pins, OVR and SMBALERT.

#### 8.2.9.1 OVR Pin

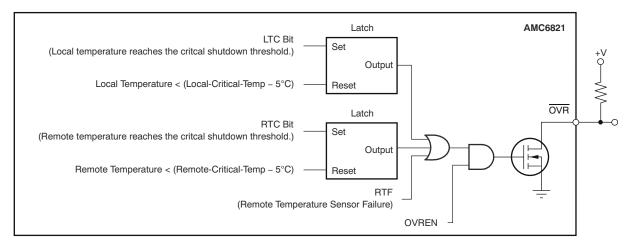

OVR is an open-drain output pin that works as an over-critical temperature limit (shutdown threshold) indicator and remote sensor failure indicator. ☒ 8-20 shows the architecture. Setting the OVREN bit of Configuration Register 4 to '1' enables this pin; clearing OVREN ('0') disables it. When disabled, the OVR pin is in a high-impedance status. When enabled, the status is controlled by the over-critical temperature flag and remote sensor failure flag bits of the Status Registers.

When the temperature is over the critical limit (shutdown threshold), the corresponding over-critical limit flag of the Status Register (RTC for the remote channel and LTC for the local channel) is set ('1'). This flag is cleared ('0') when reading the Status Registers. Once cleared, this bit is not reasserted until the temperature falls 5°C below the exceeded critical limit, even if the over-critical limit condition persists. When the temperature is equal to or above the critical temperature limit, the  $\overline{\text{OVR}}$  pin is asserted (active low) to indicate this critical condition. As the over-critical temperature limit indicator, the  $\overline{\text{OVR}}$  pin remains low once asserted until the measured temperature falls 5°C below the exceeded critical limit.

図 8-20. OVR Pin

When a remote temperature sensor failure condition is detected (either short-circuit or open-circuit), the remote temperature sensor failure bit (RTF) in Status Register 1 (bit 5, 0x02) is set ('1') and the  $\overline{\text{OVR}}$  pin is forced low no matter what the status of RTFIE is. This value indicates a remote sensor failure condition. Once this condition occurs, the RTF bit remains '1' and the  $\overline{\text{OVR}}$  pin stays low until a power-on reset or software reset is issued, regardless if the failure condition continues thereafter. RTF = 1 also generates an RTF interrupt through the  $\overline{\text{SMBALERT}}$  pin when RTFIE = 1.

## 8.2.9.2 SMBALERT Pin

The  $\overline{\text{SMBALERT}}$  pin is a standard interrupt output defined by SMBus specification revision 2.0. This pin is an open-drain output pin and is illustrated in  $\boxtimes$  8-23.

## 8.2.9.3 SMBALERT Interrupt Behavior

When an out-of-limit event occurs, the proper flag bits in the status registers are set ('1'), and the corresponding interrupts are generated, if enabled. When an interrupt is generated, the SMBALERT pin asserts low. The host can poll the device status registers to get the information, or give a response to the SMBALERT interrupt signal. It is important to note how the SMBALERT output and status bits behave when writing interrupt-handler software. SMBALERT output and status bits behave.

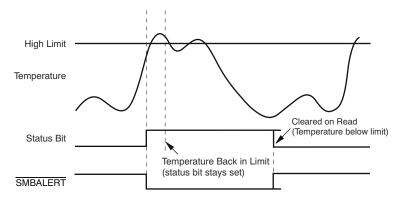

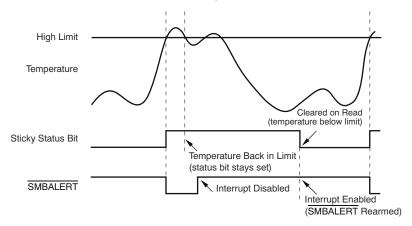

Once a limit is exceeded, the corresponding status bit is set to '1'. The status bit remains set until the error condition subsides and the status register gets read. The status bits are referred to as being *sticky* because they remain set until read by software. This design ensures that out-of-limit events cannot be missed if the software is polling the device periodically. The SMBALERT output remains low for the entire duration that the reading is out of limits and remains low until the status register has been read. This architecture has implications on how software handles the interrupt.

図 8-21. SMBALERT Pin and Status Bits Behavior

## 8.2.9.4 Handling SMBALERT Interrupts

To prevent the system from being tied up while servicing interrupts, it is recommend to handle the SMBALERT interrupt in this manner:

- 1. Detect the SMBALERT assertion.

- 2. Enter the interrupt handler.

- 3. Read the status registers to identify the interrupt source.

- 4. Disable the interrupt source by clearing the appropriate enable bit in the configuration registers.

- 5. Take the appropriate action for a given interrupt source.

- 6. Exit the interrupt handler.

- 7. Periodically poll the status registers. If the interrupt source bit has cleared, reset the corresponding interrupt enable bit to '1'. This reset makes the SMBALERT output and status bits behave as shown in ⋈ 8-22.

図 8-22. How Masking the Interrupt Source Affects SMBALERT

Individual interrupts can be masked by clearing the corresponding interrupt enable bit in the configuration registers to prevent SMBALERT interrupts. Note that masking an interrupt source only prevents the SMBALERT pin output from being asserted; the appropriate status bit gets set as normal.

図 8-23. SMBALERT

#### 8.3 Device Functional Modes

# 8.4 Programming

#### 8.4.1 SMBus Interface

The AMC6821-Q1 communicates through the serial system management bus (SMBus). The AMC6821-Q1 is connected to this bus as a slave device, under the control of a bus master. The AMC6821-Q1 has a 7-bit serial bus address that is programmable by properly connecting the address pins A0 and A1.  $\gtrsim$  8-4 shows the selection of the AMC6821-Q1 slave address. The address selection pins should be either tied directly to  $V_{DD}$  or GND. For the NC condition, they should be unconnected with minimum trace capacitance. Note that the address is checked only on a reset or power-up condition.

表 8-4. AMC6821-Q1 Address Select(1)

| A1       | ADDRESS              |

|----------|----------------------|

| GND      | 0011000              |

| GND      | 0011010              |

| GND      | 0011001              |

| NC       | 0101100              |

| NC       | 0101110              |

| NC       | 0101101              |

| $V_{DD}$ | 1001100              |

|          | GND GND GND NC NC NC |

## 表 8-4. AMC6821-Q1 Address Select<sup>(1)</sup> (continued)

| A0       | A1       | ADDRESS |

|----------|----------|---------|

| NC       | $V_{DD}$ | 1001110 |

| $V_{DD}$ | $V_{DD}$ | 1001101 |

NC = No connection.

#### 8.4.1.1 Communication Protocols

The AMC6821-Q1 employs four standard SMBus protocols: the send byte, receive byte, write byte, and read byte. All other operations result in undefined results. Repeated start is not allowed during the read bit.

## 表 8-5. Send Byte

| S | SLAVE ADDRESS                  | WR | ACK | COMMAND                | ACK | P |

|---|--------------------------------|----|-----|------------------------|-----|---|

|   | 7-bit AMC6821-Q1 slave address |    |     | 8-bit register address |     |   |

S = start condition; P = stop condition; shaded = slave to master; unshaded = master to slave; WR = write (bit value of 0).

## 表 8-6. Receive Byte

| S | SLAVE ADDRESS                  | RD | ACK | DATA                                             | NACK | P |

|---|--------------------------------|----|-----|--------------------------------------------------|------|---|

|   | 7-bit AMC6821-Q1 slave address |    |     | 8-bit data from the register selected previously |      |   |

S = start condition; P = stop condition; shaded = slave to master; unshaded = master to slave; RD = read (bit value of 1); NACK = not acknowledged.

# 表 8-7. Write Byte

| S | SLAVE ADDRESS                  | WR | ACK | COMMAND                | ACK | DATA                           | ACK | Р |

|---|--------------------------------|----|-----|------------------------|-----|--------------------------------|-----|---|

|   | 7-bit AMC6821-Q1 slave address |    |     | 8-bit register address |     | 8-bit data written to register |     |   |

S = start condition; P = stop condition; shaded = slave to master; unshaded = master to slave; WR = write (bit value of 0).

#### 表 8-8. Write Multiple Bytes

| S | SLAVE ADDRESS          | WR | ACK | COMMAND                      | ACK | DATA                     | ACK | DATA                      | ACK |  |

|---|------------------------|----|-----|------------------------------|-----|--------------------------|-----|---------------------------|-----|--|

|   | 7-bit AMC6821-Q1 slave |    |     | 8-bit register address of    |     | First 8-bit data written |     | Second 8-bit data written |     |  |

|   | address                |    |     | first register to be written |     | first register           |     | second register           |     |  |

| DATA                                    | ACK | <br>DATA        | ACK | Р |

|-----------------------------------------|-----|-----------------|-----|---|

| Third 8-bit data written third register |     | Last 8-bit data |     |   |

S = start condition; P = stop condition; shaded = slave to master; unshaded = master to slave; WR = write (bit value of 0).

The first register is the one to which the first data byte is written. The next register is the second register. If the bus master continues to transfer data into the AMC6821-Q1 after writing the last location, all data are ignored until the operation stops.

#### 表 8-9. Read Byte

| S | SLAVE ADDRESS                  | WR | ACK | COMMAND                | ACK | Sr | SLAVE ADDRESS                  | RD | ACK | DATA                        | NACK | Р |

|---|--------------------------------|----|-----|------------------------|-----|----|--------------------------------|----|-----|-----------------------------|------|---|

|   | 7-bit AMC6821-Q1 slave address |    |     | 8-bit register address |     |    | 7-bit AMC6821-Q1 slave address |    |     | 8-bit data from<br>register |      |   |

S = start condition; P = stop condition; shaded = slave to master; unshaded = master to slave; WR = write (bit value of 0); RD = read (bit value of 1); NACK = not acknowledged; Sr = repeated start condition.

# 表 8-10. Read Multiple Bytes

| S | SLAVE ADDRESS                  | WR | ACK | COMMAND                              | ACK | Sr | SLAVE ADDRESS                  | RD | ACK | DATA                           | ACK |

|---|--------------------------------|----|-----|--------------------------------------|-----|----|--------------------------------|----|-----|--------------------------------|-----|

|   | 7-bit AMC6821-Q1 slave address |    |     | Address of first register to be read |     |    | 7-bit AMC6821-Q1 slave address |    |     | 8-bit data from first register |     |

| DATA                            | ACK | <br>DATA        | NACK | Р |

|---------------------------------|-----|-----------------|------|---|

| 8-bit data from second register |     | Last 8-bit data |      |   |

S = start condition; P = stop condition; shaded = slave to master; unshaded = master to slave; WR = write (bit value of 0); RD = read (bit value of 1); NACK = not acknowledged; Sr = repeated start condition.

The first register is the one from which the first data byte is transmitted. The next register is the second register. If the bus master continues clocking data out after reading the last location (0x3F), the value 0x00 is sent out until the operation stops.

The AMC6821-Q1 is entirely controlled by the registers. All registers are 8-bit. The AMC6821-Q1 has an address pointer register; the value of the address pointer register determines the register to be written to or read from. To write data to the device register or read data from it, the address pointer register must be set properly. Data can then be written into or read from that register. The command issued by the bus master always contains the initial value of the address pointer register. The command is constructed as shown in 表 8-11.

表 8-11. Command Format<sup>(1)</sup>

| Bit 7 (MSB) | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 (LSB) |

|-------------|-------|-------|-------|-------|-------|-------|-------------|

| 0           | 0     | ADDR5 | ADDR4 | ADDR3 | ADDR2 | ADDR1 | ADDR0       |

(1) ADDR[5:0] is the address of the register that is accessed first. The register address is stored in the address pointer register.

In the send byte operation, the bus master writes the address of a specified device register into the address pointer register.

In the receive byte operation, the bus master reads the data back from the device register addressed by the address point register.

In the write byte operation, the bus master sets the address pointer register to the address of a specified device register, then writes 8-bit data into it. In the read byte operation, the SMBus master sets the address pointer register to the address of a specified device register first, then reads 8-bit data back from it.

In the write multiple bytes operation, the address pointer of the AMC6821-Q1 increments by '1' after the data are written, until it reaches the last register address (0x3F). If the host continues to transfer data into the AMC6821-Q1 after writing the last location, all data are ignored until the operation stops. When reading multiple bytes, the address pointer of the AMC6821-Q1 increments by '1' after transmitting the data until it reaches the last register address (0x3F). If the host continues clocking data out after reading the last location, the value 0x00 is sent out until the operation stops.

#### 8.4.2 SMBus Alert Response Address (ARA)

The alert response address is a feature of SMBus devices that allows an interrupting device to identify itself to the host when multiple devices issue simultaneous interrupts. The SMBALERT pin is an open-drain interrupt output pin. When the AMC6821-Q1 issues an interrupt request, the following procedure occurs:

- 1. SMBALERT is pulled low.

- 2. The bus master sends an alert response address or ARA (ARA = 0001100), and initiates a read operation (see 表 8-12).

- 3. The AMC6821-Q1 responds to the ARA by sending its slave address back. The 7-bit device slave address is placed in the seven most significant bits of the byte; the last bit is '0'.

- 4. The master receives the AMC6821-Q1 slave address and starts the interrupt service.

- 5. If more than one device pulls the SMBus low, the highest priority (lowest slave address) device wins the communication right via standard arbitration during the slave address transfer (refer to the SMBus specification version 2.0 for details).

- 6. To service the interrupt request of the AMC6821, the master must read the status register. Most interrupt source bits in the status registers are cleared after reading the status register, and are reasserted if the error

condition still exists on the next monitoring cycle. The SMBALERT only clears if the interrupt has been resolved.

#### 表 8-12. ARA Operation

| S | ALERT RESPONSE ADDRESS | RD | ACK | DATA                                           | NACK | Р |

|---|------------------------|----|-----|------------------------------------------------|------|---|

|   | 0001100                |    |     | 7-bit MSB: slave address of AMC6821-Q1 LSB = 0 |      |   |

S = start condition; P = stop condition; shaded = slave to master; unshaded = master to slave; RD = read (bit value of 1); NACK = not acknowledged.

#### 8.4.3 Power-On Reset and Start Operation

After power-on, all registers are set to the power-on default values. The device does not perform any monitoring functions until the START bit of Configuration Register 1 is set ('1'). No detections are executed until the first monitoring cycle is completed, and all measurement data registers (such as remote and local temp-data registers and the TACH data register) are updated with the new measured value. No interrupt signals are generated until the first cycle of monitoring and detection is completed. This process avoids any false alarms caused by the power-on default setting.

After power-on, the fan spin-up process is performed. At the end of spin-up, the duty cycle of the PWM driver is adjusted to 33%. (Refer to the Fan Spin-Up section for details). Device status after software reset is similar to power-on reset.

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

# 8.5 Register Map

All registers are 8-bit.  $\frac{1}{2}$  8-13 shows the memory map. Locations that are marked *Reserved* read back 0x0000 if they are read by the host. Writing to these locations has no effect.

表 8-13. Memory Map

|         | 表 8-13. Memory Map       |      |         |                                      |                                                   |                         |                     |                          |                  |                  |               |

|---------|--------------------------|------|---------|--------------------------------------|---------------------------------------------------|-------------------------|---------------------|--------------------------|------------------|------------------|---------------|

| ADDR    | NAME                     | R/W  | DEFAULT | BIT 7                                | BIT 6                                             | BIT 5                   | BIT 4               | BIT 3                    | BIT 2            | BIT 1            | BIT 0         |

| IDENTIF | CATION REGISTERS         |      |         |                                      |                                                   |                         |                     |                          |                  |                  |               |

| Ov3D    | Davisa ID Register       | R    | 0x21    | 0                                    | 0                                                 | 1                       | 0                   | 0                        | 0                | 0                | 1             |

| 0x3D    | Device ID Register       | K    | UX21    | Device identifica                    | Device identification number. Always read '0x21'. |                         |                     |                          |                  |                  |               |

|         |                          |      |         | 0                                    | 1                                                 | 0                       | 0                   | 1                        | 0                | 0                | 1             |

| 0x3E    | Company ID Register      | R    | 0x49    | Company identif                      | ication number                                    |                         |                     |                          |                  |                  |               |

| CONFIG  | URATION REGISTERS        |      |         |                                      |                                                   |                         |                     |                          |                  |                  |               |

| 000     | Confirmation Deviates 4  | DAM  | 004     | THERMOVIE                            | FDRC1                                             | FDRC0                   | FAN-Fault-<br>EN    | PWMINV                   | FANIE            | INT-EN           | START         |

| 0x00    | Configuration Register 1 | R/W  | 0xD4    | THERM INT<br>Enable                  | Fan Con                                           | trol Mode               | FAN-Fault<br>Pin EN | PWM Invert               | RPM Int EN       | Global Int EN    | Start Monitor |

|         |                          |      |         | RST                                  | PSVIE                                             | RTOIE                   | LTOIE               | RTFIE                    | TACH-EN          | TACH-MODE        | PWM-EN        |

| 0x01    | Configuration Register 2 | R/W  | 0x3D    | Reset                                | LPSV Int EN                                       | RT Int EN               | LT Int EN           | Remote<br>Failure Int EN | TACH EN          | TACH Mode        | PWM-Out EN    |

| 0x3F    | Configuration Register 3 | R/W  | 0x82    | THERM-FAN-<br>EN                     | 0                                                 | 0                       | 0                   | 0                        | 0                | 1                | 0             |