BQ34Z100-G1

JAJSLK7D – JANUARY 2015 – REVISED APRIL 2021

# BQ34Z100-G1 ワイド・レンジ残量計、Impedance Track™ テクノロジー採用

# 1 特長

- リチウムイオン、LiFePO<sub>4</sub>、NiMH、NiCd ケミストリをサポート

- 特許取得済みの Impedance Track<sup>™</sup> テクノロジーを 使った容量推定 (3V~65V のバッテリに対応)

- 経時変化補償

- 自己放電補償

- 標準構成で、最大 29Ah のバッテリ容量をサポート

- 標準構成で、最大 32A の充放電電流をサポート

- 外部 NTC サーミスタのサポート

- ホスト・システムとの2線式 I<sup>2</sup>C および HDQ1線式通信インターフェイスをサポート

- SHA-1/HMAC 認証機能

- 1 または 4 LED 直接表示制御

- ポート・エクスパンダによる 5 LED 以上の表示

- 低消費電力モード (一般的なバッテリ・パックの動作範囲の条件)

- NORMAL 動作:< 145µA (平均值)

- SLEEP:<84µA (平均值)

- FULL SLEEP: < 30µA (平均值)

- パッケージ:14 ピン TSSOP

# 2 アプリケーション

- 軽量の電気自動車

- 医療用計測機器

- 移動無線

- 電動工具

- 無停電電源 (UPS)

# 3 概要

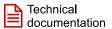

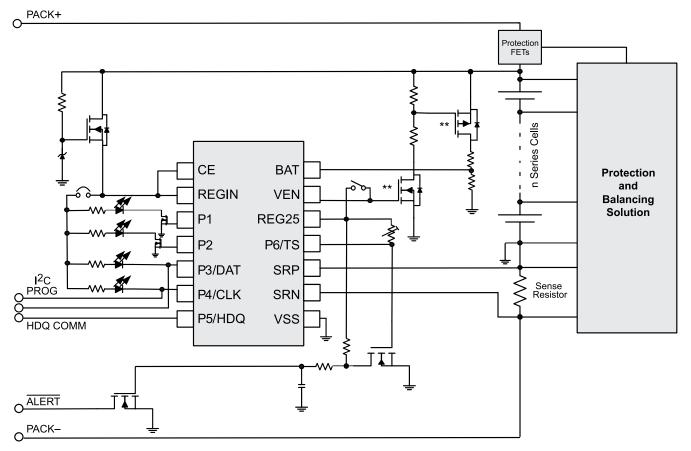

BQ34Z100-G1 デバイスは、リチウムイオン、PbA、 NiMH、NiCd バッテリ向けの Impedance Track<sup>™</sup> バッテリ 残量計であり、バッテリの直列セル構成と無関係に動作し ます。システムの消費電力を低減するように自動的に制御 される外部電圧変換回路を使って、3V~65V のバッテリ を簡単にサポートできます。

BQ34Z100-G1 デバイスは、I<sup>2</sup>C スレーブ、HDQ スレー ブ、1 つまたは 4 つの直接 LED、ALERT 出力ピンを含 む複数のインターフェイスの選択肢を備えています。ま た、BQ34Z100-G1 は、5 つ以上の LED のための外部ポ ート・エクスパンダもサポートしています。

| 製品情報                |            |                 |  |  |  |

|---------------------|------------|-----------------|--|--|--|

| 部品番号 <sup>(1)</sup> | パッケージ      | 本体サイズ (公称)      |  |  |  |

| BQ34Z100-G1         | TSSOP (14) | 5.00mm × 4.40mm |  |  |  |

(1) 利用可能なすべてのパッケージについては、このデータシートの 末尾にある注文情報を参照してください。

\*\* optional to reduce divider power consumption

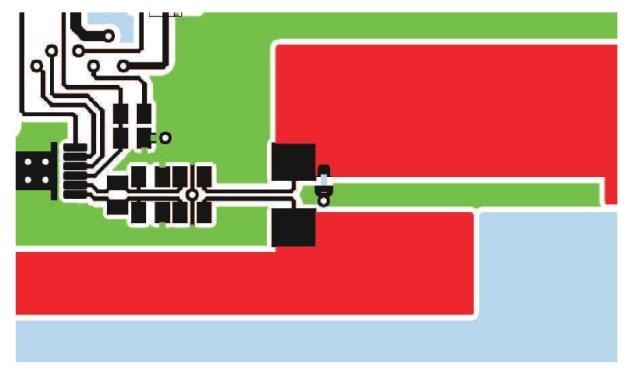

概略回路図

**A**

英語版の TI 製品についての情報を翻訳したこの資料は、製品の概要を確認する目的で便宜的に提供しているものです。該当する正式な英語版の最新情報は、 www.ti.com で閲覧でき、その内容が常に優先されます。TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、必ず 最新版の英語版をご参照くださいますようお願いいたします。

# **Table of Contents**

| 1 | 特長1                                                  |  |

|---|------------------------------------------------------|--|

|   | アプリケーション1                                            |  |

| 3 | 概要1                                                  |  |

| 4 | Revision History                                     |  |

| 5 | Pin Configuration and Functions                      |  |

| 6 | Specifications4                                      |  |

|   | 6.1 Absolute Maximum Ratings4                        |  |

|   | 6.2 ESD Ratings 4                                    |  |

|   | 6.3 Recommended Operating Conditions4                |  |

|   | 6.4 Thermal Information5                             |  |

|   | 6.5 Electrical Characteristics: Power-On Reset5      |  |

|   | 6.6 Electrical Characteristics: LDO Regulator5       |  |

|   | 6.7 Electrical Characteristics: Internal Temperature |  |

|   | Sensor Characteristics5                              |  |

|   | 6.8 Electrical Characteristics: Low-Frequency        |  |

|   | Oscillator6                                          |  |

|   | 6.9 Electrical Characteristics: High-Frequency       |  |

|   | Oscillator6                                          |  |

|   | 6.10 Electrical Characteristics: Integrating ADC     |  |

|   | (Coulomb Counter) Characteristics6                   |  |

|   | 6.11 Electrical Characteristics: ADC (Temperature    |  |

|   | and Cell Measurement) Characteristics6               |  |

|   | 6.12 Electrical Characteristics: Data Flash Memory   |  |

|   | Characteristics7                                     |  |

|   |                                                      |  |

| 6.13 Timing Requirements: HDQ Communication                     | 7    |

|-----------------------------------------------------------------|------|

| 6.14 Timing Requirements: I <sup>2</sup> C-Compatible Interface | 8    |

| 6.15 Typical Characteristics                                    | 9    |

| 7 Detailed Description                                          | .10  |

| 7.1 Overview                                                    | .10  |

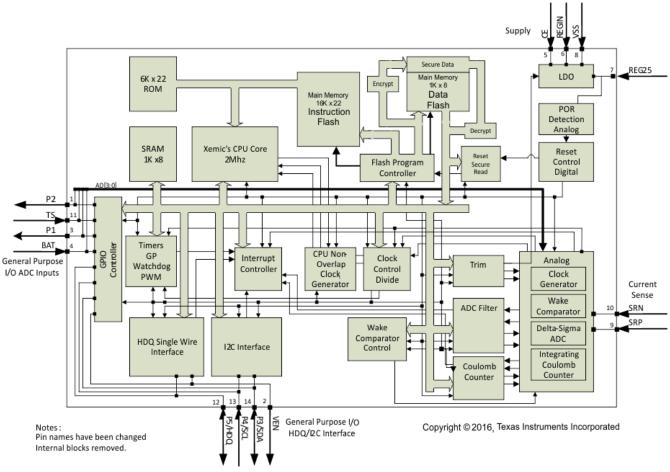

| 7.2 Functional Block Diagram                                    | . 11 |

| 7.3 Feature Description                                         |      |

| 7.4 Device Functional Modes                                     |      |

| 8 Application and Implementation                                | .45  |

| 8.1 Application Information                                     | . 45 |

| 8.2 Typical Applications                                        | . 45 |

| 9 Power Supply Recommendations                                  | 53   |

| 10 Layout                                                       | .54  |

| 10.1 Layout Guidelines                                          |      |

| 10.2 Layout Example                                             | . 54 |

| 11 Device and Documentation Support                             | .57  |

| 11.1 Documentation Support                                      | . 57 |

| 11.2 Receiving Notification of Documentation Updates.           | . 57 |

| 11.3 サポート・リソース                                                  | 57   |

| 11.4 Trademarks                                                 | . 57 |

| 11.5 Electrostatic Discharge Caution                            | . 57 |

| 11.6 Glossary                                                   |      |

| 12 Mechanical, Packaging, and Orderable                         |      |

| Information                                                     | . 57 |

|                                                                 |      |

# **4** Revision History

Updated the numbering format for tables, figures, and cross-references throughout the document.

| С | hanges from Revision C (February 2019) to Revision D (April 2021)            | Page |

|---|------------------------------------------------------------------------------|------|

| • | Changed Ground System                                                        | 54   |

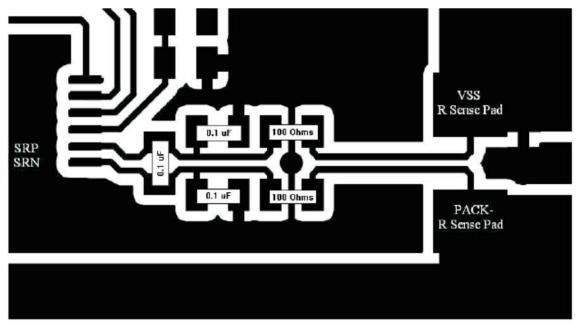

| • | Changed Differential Connection Between SRP and SRN Pins with Sense Resistor | 55   |

| Cł | hanges from Revision B (July 2016) to Revision C (February 2019) | Page |

|----|------------------------------------------------------------------|------|

| •  | Deleted EV2300 references                                        | 42   |

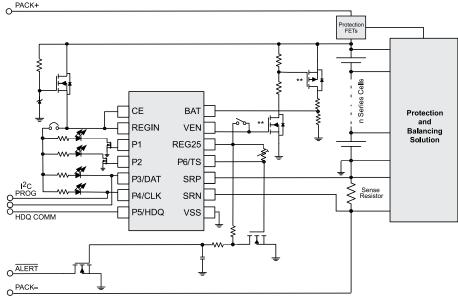

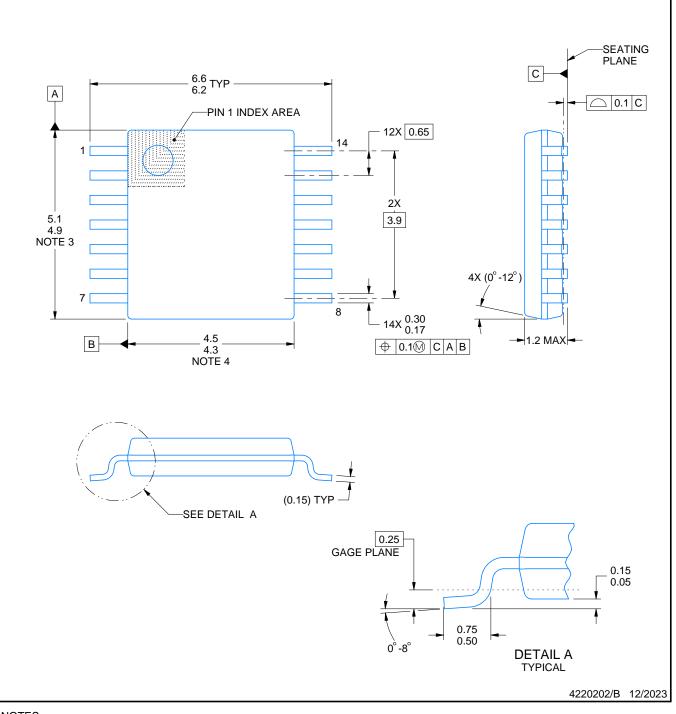

# **5** Pin Configuration and Functions

表 5-1. Pin Functions

| PIN    |        | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                |  |  |

|--------|--------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME   | NUMBER | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                |  |  |

| P2     | 1      | 0   | LED 2 or Not Used (connect to Vss)                                                                                                                                                                                                                         |  |  |

| VEN    | 2      | 0   | Active High Voltage Translation Enable. This signal is optionally used to switch the input voltage divider on/off to reduce the power consumption (typ 45 $\mu$ A) of the divider network. If not used, then this pin can be left floating or tied to Vss. |  |  |

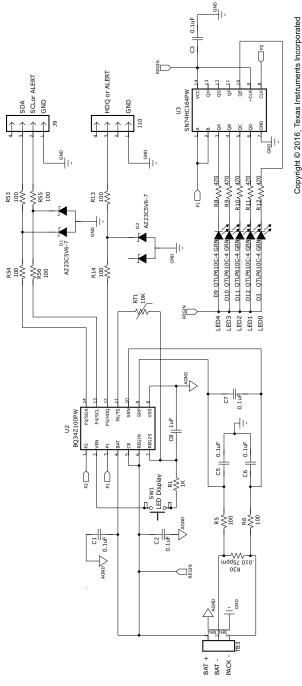

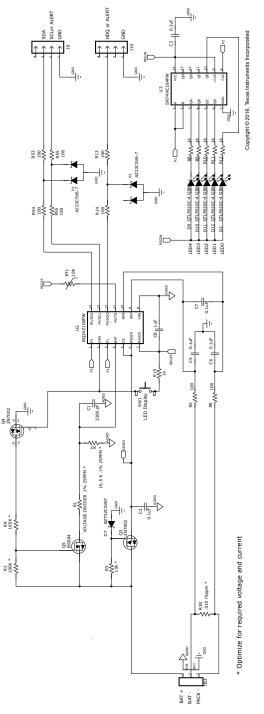

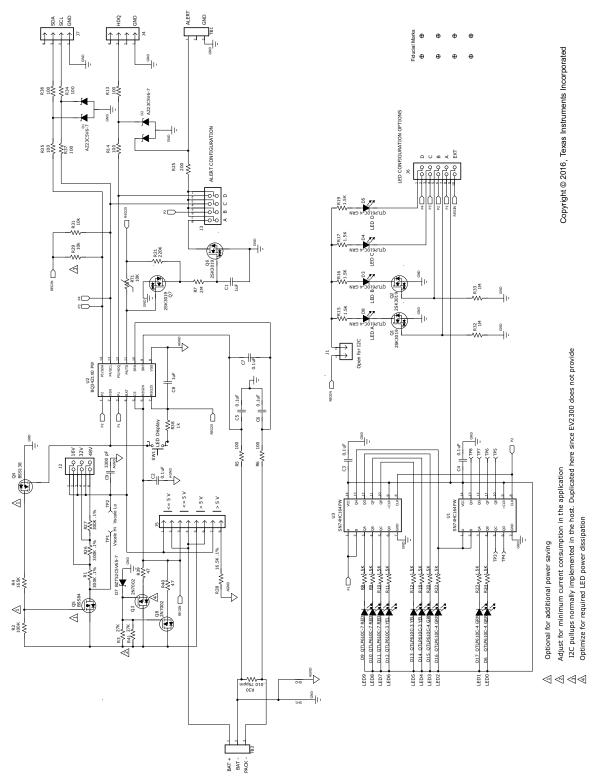

| P1     | 3      | 0   | LED 1 or Not Used (connect to Vss). This pin is also used to drive an LED for single-LED mode. Use a small signal N-FET (Q1) in series with the LED as shown on 🗵 8-4.                                                                                     |  |  |

| BAT    | 4      | I   | Translated Battery Voltage Input                                                                                                                                                                                                                           |  |  |

| CE     | 5      | I   | Chip Enable. Internal LDO is disconnected from REGIN when driven low.                                                                                                                                                                                      |  |  |

| REGIN  | 6      | Р   | Internal integrated LDO input. Decouple with a 0.1-µF ceramic capacitor to Vss.                                                                                                                                                                            |  |  |

| REG25  | 7      | Р   | 2.5-V Output voltage of the internal integrated LDO. Decouple with $1-\mu F$ ceramic capacitor to Vss.                                                                                                                                                     |  |  |

| VSS    | 8      | Р   | Device ground                                                                                                                                                                                                                                              |  |  |

| SRP    | 9      | I   | Analog input pin connected to the internal coulomb-counter peripheral for integrating a small voltage between SRP and SRN where SRP is nearest the BAT– connection.                                                                                        |  |  |

| SRN    | 10     | I   | Analog input pin connected to the internal coulomb-counter peripheral for integrating a small voltage between SRP and SRN where SRN is nearest the PACK– connection.                                                                                       |  |  |

| P6/TS  | 11     | I   | Pack thermistor voltage sense (use 103AT-type thermistor)                                                                                                                                                                                                  |  |  |

| P5/HDQ | 12     | I/O | Open drain HDQ Serial communication line (slave). If not used, then this pin can be left floating or tied to Vss.                                                                                                                                          |  |  |

| P4/SCL | 13     | I   | Slave I <sup>2</sup> C serial communication clock input. Use with a 10-K $\Omega$ pull-up resistor (typical). This pin is also used for LED 4 in the four-LED mode. If not used, then this pin can be left floating or tied to Vss.                        |  |  |

| P3/SDA | 14     | I/O | Open drain slave $l^2C$ serial communication data line. Use with a 10-k $\Omega$ pull-up resistor (typical). This pin is also used for LED 3 in the four-LED mode. If not used, then this pin can be left floating or tied to Vss.                         |  |  |

# **6** Specifications

# 6.1 Absolute Maximum Ratings

Over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                    |                                                          | MIN  | MAX       | UNIT |

|--------------------|----------------------------------------------------------|------|-----------|------|

| V <sub>REGIN</sub> | Regulator Input Range                                    | -0.3 | 5.5       | V    |

| V <sub>CC</sub>    | Supply Voltage Range                                     | -0.3 | 2.75      | V    |

| V <sub>IOD</sub>   | Open-drain I/O pins (SDA, SCL, HDQ, VEN)                 | -0.3 | 5.5       | V    |

| V <sub>BAT</sub>   | Bat Input pin                                            | -0.3 | 5.5       | V    |

| VI                 | Input Voltage range to all other pins (P1, P2, SRP, SRN) | -0.3 | VCC + 0.3 | V    |

| ESD                | Human-body model (HBM), BAT pin                          |      | 1.5       | kV   |

| ESD                | Human-body model (HBM), all other pins                   |      | 2         | kV   |

| T <sub>A</sub>     | Operating free-air temperature range                     | -40  | 85        | °C   |

| T <sub>F</sub>     | Functional temperature range                             | -40  | 100       | °C   |

| <b>-</b>           | Storage temperature range                                | -65  | 150       | °C   |

| T <sub>STG</sub>   | Lead temperature (soldering, 10 s)                       | -40  | 100       | °C   |

(1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 6.2 ESD Ratings

|    |                            |                                                                                | VALUE | UNIT |

|----|----------------------------|--------------------------------------------------------------------------------|-------|------|

|    | Electrostatic              | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±2000 | V    |

| )` | <sup>(ESD)</sup> discharge | Charged device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±500  | v    |

(1)

JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. (2)

# 6.3 Recommended Operating Conditions

T<sub>A</sub> =-40°C to 85°C; Typical Values at T<sub>A</sub> = 25°C C<sub>LDO25</sub> = 1.0 μF, and V<sub>REGIN</sub> = 3.6 V (unless otherwise noted)

|                     |                                                                       |                                                                           | MIN                   | NOM | MAX | UNIT |

|---------------------|-----------------------------------------------------------------------|---------------------------------------------------------------------------|-----------------------|-----|-----|------|

| V                   | Supply Voltage                                                        | No operating restrictions                                                 | 2.7                   |     | 4.5 | V    |

| V <sub>REGIN</sub>  | Supply Voltage                                                        | No FLASH writes                                                           | 2.45                  |     | 2.7 | V    |

| C <sub>REGIN</sub>  | External input capacitor for<br>internal LDO between REGIN<br>and VSS | Nominal capacitor values specified.                                       |                       | 0.1 |     | μF   |

| C <sub>LDO25</sub>  | External output capacitor for<br>internal LDO between VCC and<br>VSS  | Recommend a 10% ceramic X5R type — apacitor located close to the device.  | 0.47                  | 1   |     | μF   |

| I <sub>CC</sub>     | NORMAL operating-mode<br>current                                      | Gas Gauge in NORMAL mode,<br>I <sub>LOAD</sub> > <i>Sleep Current</i>     |                       | 145 |     | μA   |

| I <sub>SLP</sub>    | SLEEP operating-mode current                                          | Gas Gauge in SLEEP mode,<br>I <sub>LOAD</sub> < <b>Sleep Current</b>      |                       | 84  |     | μA   |

| I <sub>SLP+</sub>   | FULLSLEEP operating-mode<br>current                                   | Gas Gauge in FULL SLEEP mode,<br>I <sub>LOAD</sub> < <b>Sleep Current</b> |                       | 30  |     | μA   |

| V <sub>OL</sub>     | Output voltage, low (SCL, SDA, HDQ, VEN)                              | I <sub>OL</sub> = 3 mA                                                    |                       |     | 0.4 | V    |

| V <sub>OH(PP)</sub> | Output voltage, high                                                  | I <sub>OH</sub> = –1 mA                                                   | V <sub>CC</sub> - 0.5 |     |     | V    |

| V <sub>OH(OD)</sub> | Output voltage, high (SDA, SCL, HDQ, VEN)                             | External pull-up resistor connected to V <sub>CC</sub>                    | V <sub>CC</sub> – 0.5 |     |     | V    |

| V <sub>IL</sub>     | Input voltage, low                                                    |                                                                           | -0.3                  |     | 0.6 | V    |

# 6.3 Recommended Operating Conditions (continued)

| $T_{A} = -40^{\circ}C$ to 85°C:        | Typical Values at T <sub>A</sub> = 25°C | $C_{1DO25} = 1.0 \text{ µF}$ and $V_{PECINI}$ | = 3.6 V (unless otherwise noted) |

|----------------------------------------|-----------------------------------------|-----------------------------------------------|----------------------------------|

| $\mathbf{I}_{\mathbf{A}}$ is closed by | Typical values at 1 <sub>A</sub> _ Lo o |                                               |                                  |

| / .                 |                                        |  |             |     |       |      |

|---------------------|----------------------------------------|--|-------------|-----|-------|------|

|                     |                                        |  | MIN         | NOM | MAX   | UNIT |

| V <sub>IH(OD)</sub> | Input voltage, high (SDA, SCL,<br>HDQ) |  | 1.2         |     | 6     | V    |

| V <sub>A1</sub>     | Input voltage range (TS)               |  | VSS – 0.05  |     | 1     | V    |

| V <sub>A2</sub>     | Input voltage range (BAT)              |  | VSS – 0.125 |     | 5     | V    |

| V <sub>A3</sub>     | Input voltage range (SRP, SRN)         |  | VSS – 0.125 |     | 0.125 | V    |

| I <sub>LKG</sub>    | Input leakage current (I/O pins)       |  |             |     | 0.3   | μA   |

| t <sub>PUCD</sub>   | Power-up communication delay           |  |             | 250 |       | ms   |

# 6.4 Thermal Information

|                          |                                              | BQ34Z100-G1 |      |

|--------------------------|----------------------------------------------|-------------|------|

|                          | THERMAL METRIC <sup>(1)</sup>                | TSSOP (PW)  | UNIT |

|                          |                                              | 14 PINS     |      |

| R <sub>0JA, High K</sub> | Junction-to-ambient thermal resistance       | 103.8       |      |

| R <sub>0JC(top)</sub>    | Junction-to-case(top) thermal resistance     | 31.9        |      |

| R <sub>θJB</sub>         | Junction-to-board thermal resistance         | 46.6        | °c/w |

| Ψ <sub>JT</sub>          | Junction-to-top characterization parameter   | 2.0         | 0/11 |

| Ψ <sub>JB</sub>          | Junction-to-board characterization parameter | 45.9        |      |

| R <sub>0JC(bottom)</sub> | Junction-to-case(bottom) thermal resistance  | N/A         |      |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics Application Report, SPRA953.

# 6.5 Electrical Characteristics: Power-On Reset

$T_A = -40^{\circ}$ C to 85°C; Typical Values at TA = 25°C and  $V_{REGIN} = 3.6$  V (unless otherwise noted)

| PARAMET          | TER                                           | TEST CONDITIONS | MIN  | TYP  | MAX  | UNIT |

|------------------|-----------------------------------------------|-----------------|------|------|------|------|

| V <sub>IT+</sub> | Positive-going battery voltage input at REG25 |                 | 2.05 | 2.20 | 2.31 | V    |

| V <sub>HYS</sub> | Power-on reset hysteresis                     |                 | 45   | 115  | 185  | mV   |

# 6.6 Electrical Characteristics: LDO Regulator

$T_A = 25^{\circ}C$ ,  $C_{LDO25} = 1.0 \mu$ F,  $V_{REGIN} = 3.6 V$  (unless otherwise noted)<sup>(1)</sup>

| PARAMETER TEST CONDITIONS                         |                                                                                                             | MIN                                                                   | TYP                                   | MAX | UNIT |     |    |

|---------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|---------------------------------------|-----|------|-----|----|

| V <sub>REG25</sub><br>Regulator output<br>voltage | $2.7 \text{ V} \le \text{V}_{\text{REGIN}} \le 4.5 \text{ V},$<br>$\text{I}_{\text{OUT}} \le 16 \text{ mA}$ | $T_A = -40^{\circ}C$ to $85^{\circ}C$                                 | 2.3                                   | 2.5 | 2.7  | V   |    |

|                                                   | voltage                                                                                                     | $2.45 V \le V_{REGIN} \le 2.7 V$<br>(low battery), $I_{OUT} \le 3 mA$ | $T_A = -40^{\circ}C$ to $85^{\circ}C$ | 2.3 |      |     | v  |

| I <sub>SHORT</sub> <sup>(2)</sup>                 | Short Circuit<br>Current Limit                                                                              | V <sub>REG25</sub> = 0 V                                              | $T_A = -40^{\circ}C$ to $85^{\circ}C$ |     |      | 250 | mA |

(1) LDO output current,  $I_{OUT}$ , is the sum of internal and external load currents.

(2) Specified by design. Not production tested.

#### 6.7 Electrical Characteristics: Internal Temperature Sensor Characteristics

T<sub>A</sub> = -40°C to 85°C, 2.4 V < REG25 < 2.6 V; Typical Values at T<sub>A</sub> = 25°C and REG25 = 2.5 V (unless otherwise noted)

| PARAMETER         |                                 | TEST CONDITIONS | MIN | TYP | MAX | UNIT  |

|-------------------|---------------------------------|-----------------|-----|-----|-----|-------|

| G <sub>TEMP</sub> | Temperature sensor voltage gain |                 |     | -2  |     | mV/°C |

# 6.8 Electrical Characteristics: Low-Frequency Oscillator

$T_A = -40^{\circ}$ C to 85°C, 2.4 V < REG25 < 2.6 V; Typical Values at  $T_A = 25^{\circ}$ C and REG25 = 2.5 V (unless otherwise noted)

| PARAMETER           | R                                  | TEST CONDITIONS                             | MIN   | ТҮР    | MAX  | UNIT |

|---------------------|------------------------------------|---------------------------------------------|-------|--------|------|------|

| f <sub>(LOSC)</sub> | Operating frequency                |                                             |       | 32.768 |      | kHz  |

|                     |                                    | $TA = 0^{\circ}C$ to $60^{\circ}C$          | -1.5% | 0.25%  | 1.5% |      |

| f <sub>(LEIO)</sub> | Frequency error <sup>(1)</sup> (2) | $TA = -20^{\circ}C \text{ to } 70^{\circ}C$ | -2.5% | 0.25%  | 2.5% |      |

|                     |                                    | $TA = -40^{\circ}C \text{ to } 85^{\circ}C$ | -4%   | 0.25%  | 4%   |      |

| t <sub>(LSXO)</sub> | Start-up time <sup>(3)</sup>       |                                             |       | 500    |      | μs   |

(1) The frequency drift is included and measured from the trimmed frequency at VCC = 2.5 V,  $T_A = 25^{\circ}C$ .

(2) The frequency error is measured from 32.768 kHz.

(3) The startup time is defined as the time it takes for the oscillator output frequency to be  $\pm 3\%$ .

# 6.9 Electrical Characteristics: High-Frequency Oscillator

| $T_{1} = -40^{\circ}$ C to 85°C | 24V < REG25 < 2    | 3 V <sup>.</sup> Typical Values at T <sub>e</sub> | ▲ = 25°C and REG25 = 2.5 V | (unless otherwise noted) |

|---------------------------------|--------------------|---------------------------------------------------|----------------------------|--------------------------|

| $I_{A} = +0.0100000$            | , 2.4 V INCOLO IZ. |                                                   |                            |                          |

| PARAMET            | ER                                            | TEST CONDITION                        | S MIN | TYP   | MAX  | UNIT |

|--------------------|-----------------------------------------------|---------------------------------------|-------|-------|------|------|

| f <sub>(OSC)</sub> | Operating frequency                           |                                       |       | 8.389 |      | MHz  |

|                    | $T_A = 0^{\circ}C$ to $60^{\circ}C$           | -2%                                   | 0.38% | 2%    |      |      |

| f <sub>(EIO)</sub> | Frequency error <sup>(1)</sup> <sup>(2)</sup> | $T_A = -20^{\circ}C$ to $70^{\circ}C$ | -3%   | 0.38% | 3%   |      |

|                    |                                               | $T_A = -40^{\circ}C$ to $85^{\circ}C$ | -4.5% | 0.38% | 4.5% |      |

| t <sub>(SXO)</sub> | Start-up time <sup>(2)</sup>                  |                                       |       | 2.5   | 5    | ms   |

(1) The frequency error is measured from 2.097 MHz.

(2) The startup time is defined as the time it takes for the oscillator output frequency to be  $\pm 3\%$ .

# 6.10 Electrical Characteristics: Integrating ADC (Coulomb Counter) Characteristics

$T_A = -40^{\circ}$ C to 85°C, 2.4 V < REG25 < 2.6 V; Typical Values at  $T_A = 25^{\circ}$ C and REG25 = 2.5 V (unless otherwise noted)

|                      | , , , , , , , , , , , , , , , , , , , ,          | ~                                  | · ·    |         |         | ,                  |

|----------------------|--------------------------------------------------|------------------------------------|--------|---------|---------|--------------------|

| PARAMETER            | 1                                                | TEST CONDITIONS                    | MIN    | TYP     | MAX     | UNIT               |

| V <sub>(SR)</sub>    | Input voltage range, $V_{(SRN)}$ and $V_{(SRP)}$ | $V_{(SR)} = V_{(SRN)} - V_{(SRP)}$ | -0.125 |         | 0.125   | V                  |

| +                    | Conversion time                                  | Single conversion                  |        | 1       |         | s                  |

| t <sub>SR_CONV</sub> | Resolution                                       |                                    | 14     |         | 15      | bits               |

| V <sub>OS(SR)</sub>  | Input offset                                     |                                    |        | 10      |         | μV                 |

| I <sub>NL</sub>      | Integral nonlinearity error                      |                                    |        | ±0.007% | ±0.034% | FSR <sup>(2)</sup> |

| Z <sub>IN(SR)</sub>  | Effective input resistance <sup>(1)</sup>        |                                    | 2.5    |         |         | MΩ                 |

| I <sub>lkg(SR)</sub> | Input leakage current <sup>(1)</sup>             |                                    |        |         | 0.3     | μA                 |

(1) Specified by design. Not tested in production.

(2) Full-scale reference

# 6.11 Electrical Characteristics: ADC (Temperature and Cell Measurement) Characteristics

$T_{\Delta} = -40^{\circ}$ C to 85°C, 2.4 V < REG25 < 2.6 V; Typical Values at  $T_{\Delta} = 25^{\circ}$ C and REG25 = 2.5 V (unless otherwise noted)

| PARAMETER             |                                                 | TEST CONDITIONS                        | MIN  | TYP | MAX | UNIT |

|-----------------------|-------------------------------------------------|----------------------------------------|------|-----|-----|------|

| V <sub>IN(ADC)</sub>  | Input voltage range                             |                                        | 0.05 |     | 1   | V    |

| +                     | Conversion time                                 |                                        |      |     | 125 | ms   |

| t <sub>ADC_CONV</sub> | Resolution                                      |                                        | 14   |     | 15  | bits |

| V <sub>OS(ADC)</sub>  | Input offset                                    |                                        |      | 1   |     | mV   |

| Z <sub>ADC1</sub>     | Effective input resistance (TS) <sup>(1)</sup>  |                                        | 8    |     |     | MΩ   |

| Z <sub>ADC2</sub>     | Effective input registered (PAT)(1)             | BQ34Z100-G1 not measuring cell voltage | 8    |     |     | MΩ   |

|                       | Effective input resistance (BAT) <sup>(1)</sup> | BQ34Z100-G1 measuring cell voltage     |      | 100 |     | KΩ   |

# 6.11 Electrical Characteristics: ADC (Temperature and Cell Measurement) Characteristics (continued)

| PARAMETER                            | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|--------------------------------------|-----------------|-----|-----|-----|------|

| Input leakage current <sup>(1)</sup> |                 |     |     | 0.3 | μΑ   |

(1) Specified by design. Not tested in production.

# 6.12 Electrical Characteristics: Data Flash Memory Characteristics

T<sub>A</sub> = -40°C to 85°C, 2.4 V < REG25 < 2.6 V; Typical Values at T<sub>A</sub> = 25°C and REG25 = 2.5 V (unless otherwise noted)

| PARAMETER             |                                               | TEST CONDITIONS | MIN    | TYP | MAX | UNIT   |

|-----------------------|-----------------------------------------------|-----------------|--------|-----|-----|--------|

| +                     | Data retention <sup>(1)</sup>                 |                 | 10     |     |     | Years  |

| <sup>t</sup> DR       | Flash-programming write cycles <sup>(1)</sup> |                 | 20,000 |     |     | Cycles |

| t <sub>WORDPROG</sub> | Word programming time <sup>(1)</sup>          |                 |        |     | 2   | ms     |

| I <sub>CCPROG</sub>   | Flash-write supply current <sup>(1)</sup>     |                 |        | 5   | 10  | mA     |

(1) Specified by design. Not tested in production.

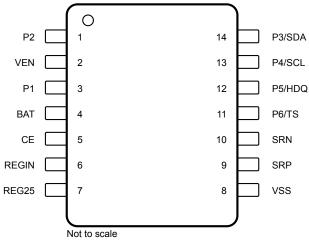

# 6.13 Timing Requirements: HDQ Communication

$T_A = -40^{\circ}$ C to 85°C, 2.45 V <  $V_{REGIN} = V_{BAT}$  < 5.5 V; typical values at  $T_A = 25^{\circ}$ C and  $V_{REGIN} = V_{BAT} = 3.6$  V (unless otherwise noted)

|                     | PARAMETER                               | TEST CONDITIONS | MIN | NOM | MAX | UNIT |

|---------------------|-----------------------------------------|-----------------|-----|-----|-----|------|

| t <sub>(CYCH)</sub> | Cycle time, host to BQ34Z100-G1         |                 | 190 |     |     | μs   |

| t <sub>(CYCD)</sub> | Cycle time, BQ34Z100-G1 to host         |                 | 190 | 205 | 250 | μs   |

| t <sub>(HW1)</sub>  | Host sends 1 to BQ34Z100-G1             |                 | 0.5 |     | 50  | μs   |

| t <sub>(DW1)</sub>  | BQ34Z100-G1 sends 1 to host             |                 | 32  |     | 50  | μs   |

| t <sub>(HW0)</sub>  | Host sends 0 to BQ34Z100-G1             |                 | 86  |     | 145 | μs   |

| t <sub>(DW0)</sub>  | BQ34Z100-G1 sends 0 to host             |                 | 80  |     | 145 | μs   |

| t <sub>(RSPS)</sub> | Response time, BQ34Z100-G1 to host      |                 | 190 |     | 950 | μs   |

| t <sub>(B)</sub>    | Break time                              |                 | 190 |     |     | μs   |

| t <sub>(BR)</sub>   | Break recovery time                     |                 | 40  |     |     | μs   |

| t <sub>(RISE)</sub> | HDQ line rising time to logic 1 (1.2 V) |                 |     |     | 950 | ns   |

| t <sub>(RST)</sub>  | HDQ Reset                               |                 | 1.8 |     | 2.2 | S    |

BQ34Z100-G1 JAJSLK7D – JANUARY 2015 – REVISED APRIL 2021

(e) Gauge to Host Response

# 図 6-1. Timing Diagrams

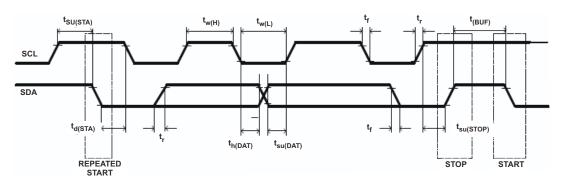

# 6.14 Timing Requirements: I<sup>2</sup>C-Compatible Interface

$T_A = -40^{\circ}C$  to 85°C, 2.45 V <  $V_{REGIN} = V_{BAT}$  < 5.5 V; typical values at  $T_A = 25^{\circ}C$  and  $V_{REGIN} = V_{BAT} = 3.6$  V (unless otherwise noted)

| ,                     | PARAMETER                            | TEST CONDITIONS | MIN | NOM | MAX | UNIT |

|-----------------------|--------------------------------------|-----------------|-----|-----|-----|------|

| t <sub>r</sub>        | SCL/SDA rise time                    |                 |     |     | 300 | ns   |

| t <sub>f</sub>        | SCL/SDA fall time                    |                 |     |     | 300 | ns   |

| t <sub>w(H)</sub>     | SCL pulse width (high)               |                 | 600 |     |     | ns   |

| t <sub>w(L)</sub>     | SCL pulse width (low)                |                 | 1.3 |     |     | μs   |

| t <sub>su(STA)</sub>  | Setup for repeated start             |                 | 600 |     |     | ns   |

| t <sub>d(STA)</sub>   | Start to first falling edge of SCL   |                 | 600 |     |     | ns   |

| t <sub>su(DAT)</sub>  | Data setup time                      |                 | 100 |     |     | ns   |

| t <sub>h(DAT)</sub>   | Data hold time                       |                 | 0   |     |     | ns   |

| t <sub>su(STOP)</sub> | Setup time for stop                  |                 | 600 |     |     | ns   |

| t <sub>BUF</sub>      | Bus free time between stop and start |                 | 66  |     |     | μs   |

| f <sub>SCL</sub>      | Clock frequency                      |                 |     |     | 400 | kHz  |

**2** 6-2. I<sup>2</sup>C-Compatible Interface Timing Diagrams

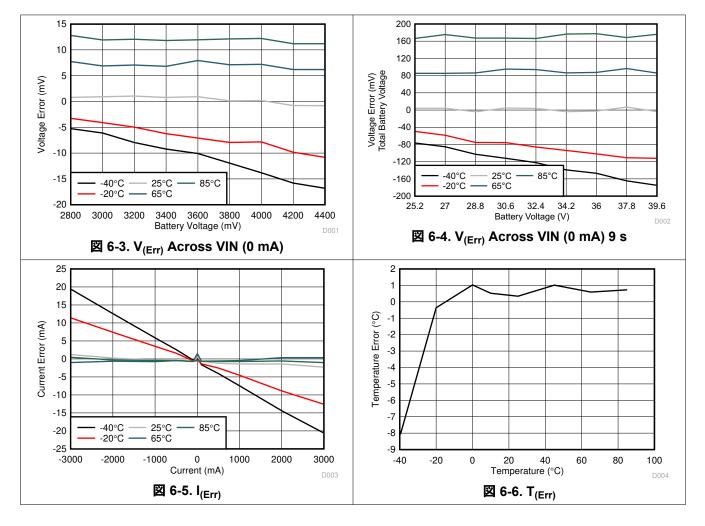

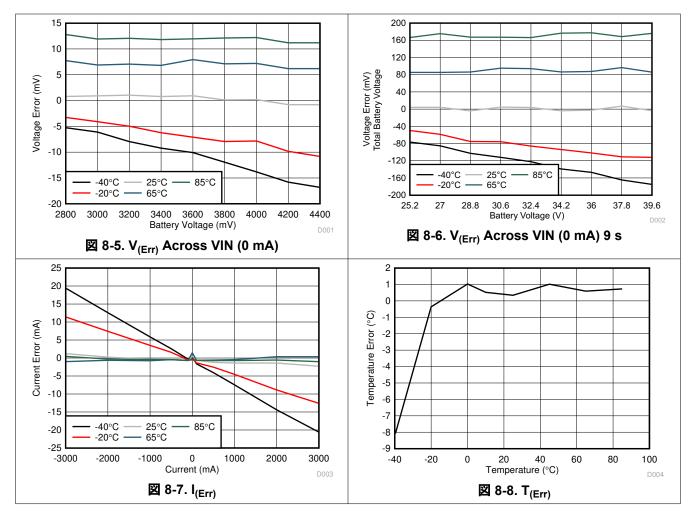

# 6.15 Typical Characteristics

# 7 Detailed Description

# 7.1 Overview

The BQ34Z100-G1 device accurately predicts the battery capacity and other operational characteristics of a single cell or multiple rechargeable cell blocks, which are voltage balanced when resting. The device supports various Li-ion , Lead Acid (PbA), Nickel Metal Hydride (NiMH), and Nickel Cadmium (NiCd) chemistries, and can be interrogated by a host processor to provide cell information, such as remaining capacity, full charge capacity, and average current.

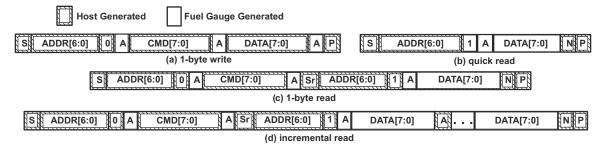

Information is accessed through a series of commands called Standard Data Commands (see  $\frac{1}{2} \frac{1}{2} \frac{1}{3} \frac{1}{3} \frac{1}{1}$ ). Further capabilities are provided by the additional Extended Data Commands set (see  $\frac{1}{2} \frac{1}{2} \frac{1}{3} \frac{1}{3} \frac{1}{3}$ ). Both sets of commands, indicated by the general format *Command()*, are used to read and write information contained within the BQ34Z100-G1 device's control and status registers, as well as its data flash locations. Commands are sent from host to gauge using the BQ34Z100-G1 serial communications engines, HDQ and I<sup>2</sup>C, and can be executed during application development, pack manufacture, or end-equipment operation.

Cell information is stored in the BQ34Z100-G1 in non-volatile flash memory. Many of these data flash locations are accessible during application development and pack manufacture. They cannot, generally, be accessed directly during end-equipment operation. Access to these locations is achieved by using the BQ34Z100-G1 device's companion evaluation software, through individual commands, or through a sequence of data-flash-access commands. To access a desired data flash location, the correct data flash subclass and offset must be known.

The BQ34Z100-G1 provides 32 bytes of user-programmable data flash memory. This data space is accessed through a data flash interface. For specifics on accessing the data flash, refer to  $\frac{\tau}{2}$  7.3.3.

The key to the BQ34Z100-G1 device's high-accuracy gas gauging prediction is Texas Instrument's proprietary Impedance Track algorithm. This algorithm uses voltage measurements, characteristics, and properties to create state-of-charge predictions that can achieve accuracy with as little as 1% error across a wide variety of operating conditions.

The BQ34Z100-G1 measures charge/discharge activity by monitoring the voltage across a small-value series sense resistor connected in the low side of the battery circuit. When an application's load is applied, cell impedance is measured by comparing its Open Circuit Voltage (OCV) with its measured voltage under loading conditions.

The BQ34Z100-G1 can use an NTC thermistor (default is Semitec 103AT or Mitsubishi BN35-3H103FB-50) for temperature measurement, or can also be configured to use its internal temperature sensor. The BQ34Z100-G1 uses temperature to monitor the battery-pack environment, which is used for fuel gauging and cell protection functionality.

To minimize power consumption, the BQ34Z100-G1 has three power modes: NORMAL, SLEEP, and FULL SLEEP. The BQ34Z100-G1 passes automatically between these modes, depending upon the occurrence of specific events.

Multiple modes are available for configuring from one to 16 LEDs as an indicator of remaining state of charge. More than four LEDs require the use of one or two inexpensive SN74HC164 shift register expanders.

A SHA-1/HMAC-based battery pack authentication feature is also implemented on the BQ34Z100-G1. When the IC is in UNSEALED mode, authentication keys can be (re)assigned. A scratch pad area is used to receive challenge information from a host and to export SHA-1/HMAC encrypted responses. See ゼクション 7.3.15.1 for further details.

#### Note

Formatting conventions in this document:

Commands: italics with parentheses and no breaking spaces; for example, RemainingCapacity().

Data Flash: *italics*, **bold**, and breaking spaces; for example, *Design Capacity*.

Register Bits and Flags: brackets only; for example, [TDA] Data

Flash Bits: *italic* and **bold**; for example, [LED1]

Modes and states: ALL CAPITALS; for example, UNSEALED mode.

# 7.2 Functional Block Diagram

# 7.3 Feature Description

# 7.3.1 Data Commands

# 7.3.1.1 Standard Data Commands

The BQ34Z100-G1 uses a series of 2-byte standard commands to enable host reading and writing of battery information. Each standard command has an associated command-code pair, as indicated in  $\frac{1}{2}$  7-1. Because each command consists of two bytes of data, two consecutive HDQ/I<sup>2</sup>C transmissions must be executed to initiate the command function and to read or write the corresponding two bytes of data. Standard commands are accessible in NORMAL operation. Also, two block commands are available to read Manufacturer Name and Device Chemistry. Read/Write permissions depend on the active access mode.

Copyright © 2021 Texas Instruments Incorporated

## 表 7-1. Commands

| NAME                 |        | COMMAND CODE | UNIT  | SEALED ACCESS | UNSEALED<br>ACCESS |

|----------------------|--------|--------------|-------|---------------|--------------------|

| Control()            | CNTL   | 0x00/0x01    | N/A   | R/W           | R/W                |

| StateOfCharge()      | SOC    | 0x02         | %     | R             | R                  |

| MaxError()           | ME     | 0x03         | %     | R             | R                  |

| RemainingCapacity()  | RM     | 0x04/0x05    | mAh   | R             | R                  |

| FullChargeCapacity() | FCC    | 0x06/0x07    | mAh   | R             | R                  |

| Voltage()            | VOLT   | 0x08/0x09    | mV    | R             | R                  |

| AverageCurrent()     | AI     | 0x0A/0x0B    | mA    | R             | R                  |

| Temperature()        | TEMP   | 0x0C/0x0D    | 0.1 K | R             | R                  |

| Flags()              | FLAGS  | 0x0E/0x0F    | N/A   | R             | R                  |

| Current()            | I      | 0x10/0x11    | mA    | R             | R                  |

| FlagsB()             | FLAGSB | 0x12/0x13    | N/A   | R             | R                  |

#### 7.3.1.2 Control(): 0x00/0x01

Issuing a *Control()* command requires a subsequent two-byte subcommand. These additional bytes specify the particular control function desired. The *Control()* command allows the host to control specific features of the BQ34Z100-G1 during normal operation, and additional features when the BQ34Z100-G1 is in different access modes, as described in 表 7-2.

| CNTL FUNCTION      | CNTL DATA | SEALED ACCESS | DESCRIPTION                                                          |

|--------------------|-----------|---------------|----------------------------------------------------------------------|

| CONTROL_STATUS     | 0x0000    | Yes           | Reports the status of key features.                                  |

| DEVICE_TYPE        | 0x0001    | Yes           | Reports the device type of 0x100 (indicating BQ34Z100-G1)            |

| FW_VERSION         | 0x0002    | Yes           | Reports the firmware version on the device type                      |

| HW_VERSION         | 0x0003    | Yes           | Reports the hardware version of the device type                      |

| RESET_DATA         | 0x0005    | Yes           | Returns reset data                                                   |

| PREV_MACWRITE      | 0x0007    | Yes           | Returns previous Control() command code                              |

| CHEM_ID            | 0x0008    | Yes           | Reports the chemical identifier of the Impedance Track configuration |

| BOARD_OFFSET       | 0x0009    | Yes           | Forces the device to measure and store the board offset              |

| CC_OFFSET          | 0x000A    | Yes           | Forces the device to measure the internal CC offset                  |

| CC_OFFSET_SAVE     | 0x000B    | Yes           | Forces the device to store the internal CC offset                    |

| DF_VERSION         | 0x000C    | Yes           | Reports the data flash version on the device                         |

| SET_FULLSLEEP      | 0x0010    | Yes           | Set the [FULLSLEEP] bit in the control register to 1                 |

| STATIC_CHEM_CHKSUM | 0x0017    | Yes           | Calculates chemistry checksum                                        |

| SEALED             | 0x0020    | No            | Places the device in SEALED access mode                              |

| IT_ENABLE          | 0x0021    | No            | Enables the Impedance Track algorithm                                |

| CAL_ENABLE         | 0x002D    | No            | Toggle CALIBRATION mode enable                                       |

| RESET              | 0x0041    | No            | Forces a full reset of the BQ34Z100-G1                               |

| EXIT_CAL           | 0x0080    | No            | Exit CALIBRATION mode                                                |

| ENTER_CAL          | 0x0081    | No            | Enter CALIBRATION mode                                               |

| OFFSET_CAL         | 0x0082    | No            | Reports internal CC offset in CALIBRATION mode                       |

#### 表 7-2. Control() Subcommands

#### 7.3.1.2.1 CONTROL\_STATUS: 0x0000

Instructs the fuel gauge to return status information to Control addresses 0x00/0x01. The status word includes the following information.

|           | Bit 7 | Bit 6 | Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 |       |      |         |     |      |

|-----------|-------|-------|-------------------------------------|-------|------|---------|-----|------|

| High Byte | RSVD  | FAS   | SS                                  | CALEN | CCA  | BCA     | CSV | RSVD |

| Low Byte  | RSVD  | RSVD  | FULLSLEEP                           | SLEEP | LDMD | RUP_DIS | VOK | QEN  |

#### 表 7-3. CONTROL\_STATUS Flags

# Legend: **RSVD** = Reserved

- FAS: Status bit that indicates the BQ34Z100-G1 is in FULL ACCESS SEALED state. Active when set.

- SS: Status bit that indicates the BQ34Z100-G1 is in the SEALED state. Active when set.

- CALEN: Status bit that indicates the BQ34Z100-G1 calibration function is active. True when set. Default is 0.

- CCA: Status bit that indicates the BQ34Z100-G1 Coulomb Counter Calibration routine is active. Active when set.

- BCA: Status bit that indicates the BQ34Z100-G1 Board Calibration routine is active. Active when set.

- **CSV:** Status bit that indicates a valid data flash checksum has been generated. Active when set.

- **FULLSLEEP:** Status bit that indicates the BQ34Z100-G1 is in FULL SLEEP mode. True when set. The state can only be detected by monitoring the power used by the BQ34Z100-G1 because any communication will automatically clear it.

- **SLEEP:** Status bit that indicates the BQ34Z100-G1 is in SLEEP mode. True when set.

- **LDMD:** Status bit that indicates the BQ34Z100-G1 Impedance Track algorithm using constant-power mode. True when set. Default is 0 (CONSTANT CURRENT mode).

- RUP\_DIS: Status bit that indicates the BQ34Z100-G1 Ra table updates are disabled. True when set.

- VOK: Status bit that indicates cell voltages are OK for Qmax updates. True when set.

- **QEN:** Status bit that indicates the BQ34Z100-G1 Qmax updates are enabled. True when set.

#### 7.3.1.2.2 DEVICE TYPE: 0x0001

Instructs the fuel gauge to return the device type to addresses 0x00/0x01.

#### 7.3.1.2.3 FW\_VERSION: 0x0002

Instructs the fuel gauge to return the firmware version to addresses 0x00/0x01.

#### 7.3.1.2.4 HW\_VERSION: 0x0003

Instructs the fuel gauge to return the hardware version to addresses 0x00/0x01.

#### 7.3.1.2.5 RESET\_DATA: 0x0005

Instructs the fuel gauge to return the number of resets performed to addresses 0x00/0x01.

#### 7.3.1.2.6 PREV\_MACWRITE: 0x0007

Instructs the fuel gauge to return the previous command written to addresses 0x00/0x01. The value returned is limited to less than 0x0020.

#### 7.3.1.2.7 CHEM ID: 0x0008

Instructs the fuel gauge to return the chemical identifier for the Impedance Track configuration to addresses 0x00/0x01.

#### 7.3.1.2.8 BOARD\_OFFSET: 0x0009

Instructs the fuel gauge to calibrate board offset. During board offset calibration the [BCA] bit is set.

#### 7.3.1.2.9 CC\_OFFSET: 0x000A

Instructs the fuel gauge to calibrate the coulomb counter offset. During calibration the [CCA] bit is set.

#### 7.3.1.2.10 CC\_OFFSET\_SAVE: 0x000B

Instructs the fuel gauge to save the coulomb counter offset after calibration.

#### 7.3.1.2.11 DF\_VERSION: 0x000C

Instructs the fuel gauge to return the data flash version to addresses 0x00/0x01.

#### 7.3.1.2.12 SET\_FULLSLEEP: 0x0010

Instructs the fuel gauge to set the FULLSLEEP bit in the Control Status register to 1. This allows the gauge to enter the FULL SLEEP power mode after the transition to SLEEP power state is detected. In FULL SLEEP mode, less power is consumed by disabling an oscillator circuit used by the communication engines. For HDQ communication, one host message will be dropped. For I<sup>2</sup>C communications, the first I<sup>2</sup>C message will incur a 6-ms–8-ms clock stretch while the oscillator is started and stabilized. A communication to the device in FULL SLEEP will force the part back to the SLEEP mode.

#### 7.3.1.2.13 STATIC\_CHEM\_DF\_CHKSUM: 0x0017

Instructs the fuel gauge to calculate chemistry checksum as a 16-bit unsigned integer sum of all static chemistry data. The most significant bit (MSB) of the checksum is masked yielding a 15-bit checksum. This checksum is compared with the value stored in the data flash Static Chem DF Checksum. If the value matches, the MSB will be cleared to indicate a pass. If it does not match, the MSB will be set to indicate a failure.

#### 7.3.1.2.14 SEALED: 0x0020

Instructs the fuel gauge to transition from UNSEALED state to SEALED state. The fuel gauge should always be set to SEALED state for use in customer's end equipment.

#### 7.3.1.2.15 IT ENABLE: 0x0021

Forces the fuel gauge to begin the Impedance Track algorithm, sets Bit 2 of **UpdateStatus** and causes the [VOK] and [QEN] flags to be set in the CONTROL STATUS register. [VOK] is cleared if the voltages are not suitable for a Qmax update. Once set, [QEN] cannot be cleared. This command is only available when the fuel gauge is UNSEALED and is typically enabled at the last step of production after the system test is completed.

#### 7.3.1.2.16 CAL\_ENABLE: 0x002D

Instructs the fuel gauge to enable entry and exit to CALIBRATION mode.

#### 7.3.1.2.17 RESET: 0x0041

Instructs the fuel gauge to perform a full reset. This command is only available when the fuel gauge is UNSEALED.

#### 7.3.1.2.18 EXIT\_CAL: 0x0080

Instructs the fuel gauge to exit CALIBRATION mode.

#### 7.3.1.2.19 ENTER\_CAL: 0x0081

Instructs the fuel gauge to enter CALIBRATION mode.

#### 7.3.1.2.20 OFFSET\_CAL: 0x0082

Instructs the fuel gauge to perform offset calibration.

#### 7.3.1.3 StateOfCharge(): 0x02

This read-only command returns an unsigned integer value of the predicted remaining battery capacity expressed as a percentage of *FullChargeCapacity()* with a range of 0 to 100%.

#### 7.3.1.4 MaxError(): 0x03

This read-only command returns an unsigned integer value of the expected margin of error, in %, in the state-ofcharge calculation, with a range of 1% to 100%. *MaxError()* is incremented internally by 0.05% for every increment of *CycleCount* after the last *QMAX* update. *MaxError()* is incremented in the display by 1% for each increment of *CycleCount*.

#### 表 7-4. MaxError() Updates

| EVENT                    | MaxError() SETTING |  |

|--------------------------|--------------------|--|

| Full reset Set to 100%   |                    |  |

| QMAX and Ra table update | Set to 1%          |  |

| QMAX update              | Set to 3%          |  |

| Ra table update          | Set to 5%          |  |

If MaxError() exceeds the value programmed in Max Error Limit, then [CF] in ControlStatus() is set. Only when MaxError() returns below this value will [CF] be cleared.

#### 7.3.1.5 RemainingCapacity(): 0x04/0x05

This read-only command pair returns the compensated battery capacity remaining. Unit is 1 mAh per bit.

#### 7.3.1.6 FullChargeCapacity(): 0x06/07

This read-only command pair returns the compensated capacity of the battery when fully charged with units of 1 mAh per bit. However, if **PackConfiguration [SCALED]** is set then the units have been scaled through the calibration process. The actual scale is not set in the device and SCALED is just an indicator flag. FullChargeCapacity() is updated at regular intervals under the control of the Impedance Track algorithm.

#### 7.3.1.7 Voltage(): 0x08/0x09

This read-word command pair returns an unsigned integer value of the measured battery voltage in mV with a range of 0 V to 65535 mV.

#### 7.3.1.8 AverageCurrent(): 0x0A/0x0B

This read-only command pair returns a signed integer value that is the average current flowing through the sense resistor. It is updated every 1 second with units of 1 mA per bit. However, if PackConfiguration [SCALED] is set then the units have been scaled through the calibration process. The actual scale is not set in the device and SCALED is just an indicator flag.

#### 7.3.1.9 Temperature(): 0x0C/0x0D

This read-only command pair returns an unsigned integer value of the temperature, in units of 0.1 K, measured by the gas gauge and has a range of 0 to 6553.5 K. The source of the measured temperature is configured by the [TEMPS] bit in the Pack Configuration register .

| 表 7-5. Temperature Sensor Selection |                             |  |  |  |  |  |

|-------------------------------------|-----------------------------|--|--|--|--|--|

| TEMPS                               | TEMPERATURE() SOURCE        |  |  |  |  |  |

| 0                                   | Internal Temperature Sensor |  |  |  |  |  |

| 1                                   | TS Input (default)          |  |  |  |  |  |

# Concer Colection

#### 7.3.1.10 Flags(): 0x0E/0x0F

This read-only command pair returns the contents of the Gas Gauge Status register, depicting current operation status.

|           | AX 7-0. Flags bit Demittions |       |       |        |         |       |       |       |  |

|-----------|------------------------------|-------|-------|--------|---------|-------|-------|-------|--|

|           | Bit 7                        | Bit 6 | Bit 5 | Bit 4  | Bit 3   | Bit 2 | Bit 1 | Bit 0 |  |

| High Byte | OTC                          | OTD   | BATHI | BATLOW | CHG_INH | XCHG  | FC    | CHG   |  |

| Low Byte  | OCVTAKEN                     | RSVD  | RSVD  | CF     | RSVD    | SOC1  | SOCF  | DSG   |  |

#### 表 7-6 Flags Bit Definitions

#### Legend: **RSVD** = Reserved

OTC: Overtemperature in Charge condition is detected. True when set

OTD: Overtemperature in Discharge condition is detected. True when set

- **BATHI:** Battery High bit that indicates a high battery voltage condition. Refer to the data flash *Cell BH* parameters for threshold settings. True when set

- **BATLOW:** Battery Low bit that indicates a low battery voltage condition. Refer to the data flash *Cell BL* parameters for threshold settings. True when set

- CHG\_INH: Charge Inhibit: unable to begin charging. Refer to the data flash [Charge Inhibit Temp Low, Charge Inhibit Temp High] parameters for threshold settings. True when set

- XCHG: Charging not allowed

- FC: Full charge is detected. FC is set when charge termination is reached and FC Set% = -1 (see セクション 7.3.11 for details) or StateOfCharge() is larger than FC Set% and FC Set% is not -1. True when set

- CHG: (Fast) charging allowed. True when set

OCVTAKEN: Cleared on entry to RELAX mode and set to 1 when OCV measurement is performed in RELAX mode.

- CF: Condition Flag indicates that the gauge needs to run through an update cycle to optimize accuracy.

- SOC1: State-of-Charge Threshold 1 reached. True when set

- SOCF: State-of-Charge Threshold Final reached. True when set

- DSG: Discharging detected. True when set

#### 7.3.1.11 FlagsB(): 0x12/0x13

This read-word function returns the contents of the gas-gauge status register, depicting current operation status.

|           | Bit 7 | Bit 6 | Bit 5    | Bit 4 | Bit 3 | Bit 2  | Bit 1 | Bit 0 |  |

|-----------|-------|-------|----------|-------|-------|--------|-------|-------|--|

| High Byte | SOH   | LIFE  | FIRSTDOD | RSVD  | RSVD  | DODEOC | DTRC  | RSVD  |  |

| Low Byte  | RSVD  | RSVD  | RSVD     | RSVD  | RSVD  | RSVD   | RSVD  | RSVD  |  |

#### 表 7-7. Flags B Bit Definitions

#### Legend: **RSVD** = Reserved

**SOH:** *StateOfHealth()* calculation is active.

LIFE: Indicates that LiFePO<sub>4</sub> RELAX is enabled.

- FIRSTDOD: Set when RELAX mode is entered and then cleared upon valid DOD measurement for QMAX update or RELAX exit.

- **DODEOC:** DOD at End-of-Charge is updated.

- DTRC: Indicates RemainingCapacity() has been changed due to change in temperature.

#### 7.3.1.12 Current(): 0x10/0x11

This read-only command pair returns a signed integer value that is the current flow through the sense resistor. It is updated every 1 s with units of 1 mA; however, if *PackConfiguration [SCALED]* is set, then the units have been scaled through the calibration process. The actual scale is not set in the device and *SCALED* is just an indicator flag.

#### 7.3.2 Extended Data Commands

Extended commands offer additional functionality beyond the standard set of commands. They are used in the same manner; however, unlike standard commands, extended commands are not limited to 2-byte words. The number of command bytes for a given extended command ranges in size from single to multiple bytes, as specified in  $\frac{1}{2}$  7-8. For details on the SEALED and UNSEALED states, refer to  $\frac{1}{2}$  7.3.3.3.

| NAME                 |       | COMMAND CODE | UNIT    | SEALED<br>ACCESS <sup>(1)</sup> <sup>(2)</sup> | UNSEALED<br>ACCESS <sup>(1)</sup> (2) |

|----------------------|-------|--------------|---------|------------------------------------------------|---------------------------------------|

| AverageTimeToEmpty() | ATTE  | 0x18/0x19    | Minutes | R                                              | R                                     |

| AverageTimeToFull()  | ATTF  | 0x1A/0x1B    | Minutes | R                                              | R                                     |

| PassedCharge()       | PCHG  | 0x1C/0x1D    | mAh     | R                                              | R                                     |

| DoD0Time()           | DoD0T | 0x1E/0x1F    | Minutes | R                                              | R                                     |

| AvailableEnergy()    | AE    | 0x24/0x25    | 10 mW/h | R                                              | R                                     |

#### 表 7-8. Extended Commands

| 表 7-8. Extended Commands (continued) |          |              |        |                                                |                                       |  |  |

|--------------------------------------|----------|--------------|--------|------------------------------------------------|---------------------------------------|--|--|

| NAME                                 |          | COMMAND CODE | UNIT   | SEALED<br>ACCESS <sup>(1)</sup> <sup>(2)</sup> | UNSEALED<br>ACCESS <sup>(1)</sup> (2) |  |  |

| AveragePower()                       | AP       | 0x26/0x27    | 10 mW  | R                                              | R                                     |  |  |

| Serial Number                        | SERNUM   | 0x28/0x29    | N/A    | R                                              | R                                     |  |  |

| Internal_Temperature()               | INTTEMP  | 0x2A/0x2B    | 0.1 K  | R                                              | R                                     |  |  |

| CycleCount()                         | CC       | 0x2C/0x2D    | Counts | R                                              | R                                     |  |  |

| StateOfHealth()                      | SOH      | 0x2E/0x2F    | %      | R                                              | R                                     |  |  |

| ChargeVoltage()                      | CHGV     | 0x30/0x31    | mV     | R                                              | R                                     |  |  |

| ChargeCurrent()                      | CHGI     | 0x32/0x33    | mA     | R                                              | R                                     |  |  |

| PackConfiguration()                  | PKCFG    | 0x3A/0x3B    | N/A    | R                                              | R                                     |  |  |

| DesignCapacity()                     | DCAP     | 0x3C/0x3D    | mAh    | R                                              | R                                     |  |  |

| DataFlashClass() (2)                 | DFCLS    | 0x3E         | N/A    | N/A                                            | R/W                                   |  |  |

| DataFlashBlock() (2)                 | DFBLK    | 0x3F         | N/A    | R/W                                            | R/W                                   |  |  |

| Authenticate()/BlockData()           | A/DF     | 0x400x53     | N/A    | R/W                                            | R/W                                   |  |  |

| AuthenticateCheckSum()/BlockData()   | ACKS/DFD | 0x54         | N/A    | R/W                                            | R/W                                   |  |  |

| BlockData()                          | DFD      | 0x550x5F     | N/A    | R                                              | R/W                                   |  |  |

| BlockDataCheckSum()                  | DFDCKS   | 0x60         | N/A    | R/W                                            | R/W                                   |  |  |

| BlockDataControl()                   | DFDCNTL  | 0x61         | N/A    | N/A                                            | R/W                                   |  |  |

| GridNumber()                         | GN       | 0x62         | N/A    | R                                              | R                                     |  |  |

| LearnedStatus()                      | LS       | 0x63         | N/A    | R                                              | R                                     |  |  |

| DoD@EoC()                            | DEOC     | 0x64/0x65    | N/A    | R                                              | R                                     |  |  |

| QStart()                             | QS       | 0x66/0x67    | mAh    | R                                              | R                                     |  |  |

| TrueRC()                             | TRC      | 0x68/0x69    | mAh    | R                                              | R                                     |  |  |

| TrueFCC()                            | TFCC     | 0x6A/0x6B    | mAh    | R                                              | R                                     |  |  |

| StateTime()                          | ST       | 0x6C/0x6D    | S      | R                                              | R                                     |  |  |

| QMaxPassedQ                          | QPC      | 0x6E/0x6F    | mAh    | R                                              | R                                     |  |  |

| DOD0()                               | DOD0     | 0x70/0x71    | HEX#   | R                                              | R                                     |  |  |

| QmaxDOD0()                           | QD0      | 0x72/0x73    | N/A    | R                                              | R                                     |  |  |

| QmaxTime()                           | QT       | 0x74/0x75    | h/16   | R                                              | R                                     |  |  |

| Reserved                             | RSVD     | 0x760x7F     | N/A    | R                                              | R                                     |  |  |

#### 表 7-8. Extended Commands (continued)

(1) SEALED and UNSEALED states are entered via commands to CNTL 0x00/0x01.

(2) In SEALED mode, data flash *cannot* be accessed through commands 0x3E and 0x3F.

# 7.3.2.1 AverageTimeToEmpty(): 0x18/0x19

This read-only command pair returns an unsigned integer value of the predicted remaining battery life at the present rate of discharge (using *AverageCurrent()*), in minutes. A value of 65535 indicates that the battery is not being discharged.

# 7.3.2.2 AverageTimeToFull(): 0x1A/0x1B

This read-only command pair returns an unsigned integer value of predicted remaining time until the battery reaches full charge, in minutes, based upon *AverageCurrent()*. The computation should account for the taper current time extension from the linear TTF computation based on a fixed *AverageCurrent()* rate of charge accumulation. A value of 65535 indicates the battery is not being charged.

# 7.3.2.3 PassedCharge(): 0x1C/0x1D

This read-only command pair returns a signed integer, indicating the amount of charge passed through the sense resistor since the last IT simulation in mAh.

# 7.3.2.4 DOD0Time(): 0x1E/0x1F

This read-only command pair returns the time since the last DOD0 update.

## 7.3.2.5 AvailableEnergy(): 0x24/0x25

This read-only command pair returns an unsigned integer value of the predicted charge or energy remaining in the battery. The value is reported in units of mWh.

#### 7.3.2.6 AveragePower(): 0x26/0x27

This read-word command pair returns an unsigned integer value of the average power of the current discharge. A value of 0 indicates that the battery is not being discharged. The value is reported in units of mW.

#### 7.3.2.7 SerialNumber(): 0x28/0x29

This read-only command pair returns the assigned pack serial number programmed in Serial Number.

#### 7.3.2.8 InternalTemperature(): 0x2A/0x2B

This read-only command pair returns an unsigned integer value of the measured internal temperature of the device, in units of 0.1 K, measured by the fuel gauge.

#### 7.3.2.9 CycleCount(): 0x2C/0x2D

This read-only command pair returns an unsigned integer value of the number of cycles the battery has experienced with a range of 0 to 65535. One cycle occurs when accumulated discharge  $\geq$  *CC Threshold*.

#### 7.3.2.10 StateOfHealth(): 0x2E/0x2F

This read-only command pair returns an unsigned integer value, expressed as a percentage of the ratio of predicted FCC (25°C, SOH current rate) over the *DesignCapacity()*. The FCC (25°C, SOH current rate) is the calculated full charge capacity at 25°C and the SOH current rate that is specified in the data flash (State of Health Load). The range of the returned SOH percentage is 0x00 to 0x64, indicating 0% to 100%, correspondingly.

#### 7.3.2.11 ChargeVoltage(): 0x30/0x31

This read-only command pair returns the recommended charging voltage output from the JEITA charging profile. It is updated automatically based on the present temperature range.

#### 7.3.2.12 ChargeCurrent(): 0x32/0x33

This read-only command pair returns the recommended charging current output from the JEITA charging profile. It is updated automatically based on the present temperature range.

#### 7.3.2.13 PackConfiguration(): 0x3A/0x3B

This read-only command pair allows the host to read the configuration of selected features of the device pertaining to various features.

#### 7.3.2.14 DesignCapacity(): 0x3C/0x3D

This read-only command pair returns theoretical or nominal capacity of a new pack. The value is stored in **Design Capacity** and is expressed in mAh.

#### 7.3.2.15 DataFlashClass(): 0x3E

UNSEALED Access: This command sets the data flash class to be accessed. The class to be accessed should be entered in hexadecimal.

SEALED Access: This command is not available in SEALED mode.

# 7.3.2.16 DataFlashBlock(): 0x3F

UNSEALED Access: If **BlockDataControl** has been set to 0x00, this command directs which data flash block will be accessed by the *BlockData()* command. Writing a 0x00 to *DataFlashBlock()* specifies the *BlockData()*

command will transfer authentication data. Issuing a 0x01 instructs the *BlockData()* command to transfer *Manufacturer Data*.

SEALED Access: This command directs which data flash block will be accessed by the *BlockData()* command. Writing a 0x00 to *DataFlashBlock()* specifies that the *BlockData()* command will transfer authentication data. Issuing a 0x01 instructs the *BlockData()* command to transfer *Manufacturer Data*.

#### 7.3.2.17 AuthenticateData/BlockData(): 0x40...0x53

UNSEALED Access: This data block has a dual function: It is used for the authentication challenge and response and is part of the 32-byte data block when accessing data flash.

SEALED Access: This data block has a dual function: It is used for authentication challenge and response, and is part of the 32-byte data block when accessing the *Manufacturer Data*.

#### 7.3.2.18 AuthenticateChecksum/BlockData(): 0x54

UNSEALED Access: This byte holds the authentication checksum when writing the authentication challenge to the device, and is part of the 32-byte data block when accessing data flash.

SEALED Access: This byte holds the authentication checksum when writing the authentication challenge to the device, and is part of the 32-byte data block when accessing *Manufacturer Data*.

#### 7.3.2.19 BlockData(): 0x55...0x5F

UNSEALED Access: This data block is the remainder of the 32-byte data block when accessing data flash.

SEALED Access: This data block is the remainder of the 32-byte data block when accessing *Manufacturer Data*.

#### 7.3.2.20 BlockDataChecksum(): 0x60

UNSEALED Access: This byte contains the checksum on the 32 bytes of block data read or written to data flash.

SEALED Access: This byte contains the checksum for the 32 bytes of block data written to *Manufacturer Data*.

#### 7.3.2.21 BlockDataControl(): 0x61

UNSEALED Access: This command is used to control data flash ACCESS mode. Writing 0x00 to this command enables *BlockData()* to access general data flash. Writing a 0x01 to this command enables the SEALED mode operation of *DataFlashBlock()*.

#### 7.3.2.22 GridNumber(): 0x62

This read-only command returns the active grid point. This data is only valid during DISCHARGE mode when  $[R_DIS] = 0$ . If  $[R_DIS] = 1$  or not discharging, this value is not updated.

#### 7.3.2.23 LearnedStatus(): 0x63

This read-only command returns the learned status of the resistance table.

#### 表 7-9. LearnedStatus(): 0x63

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| RSVD  | RSVD  | RSVD  | RSVD  | Qmax  | ITEN  | CF1   | CF0   |

#### Legend: **RSVD** = Reserved

QMax (Bit 3): QMax updates in the field.

- 0 = QMax has not been updated in the field.

- 1 = QMax updated in the field.

- ITEN (Bit 2): IT enable

CF1, CF0 (Bits 1-0): QMax Status

- 0 = IT is disabled.

- 1 = IT is enabled.

0,0 = Battery is OK.

0,1 = QMax is first updated in the learning cycle.

#### 7.3.2.24 Dod@Eoc(): 0x64/0x65

This read-only command pair returns the depth of discharge (DOD) at the end of charge.

## 7.3.2.25 QStart(): 0x66/0x67

This read-only command pair returns the initial capacity calculated from IT simulation.

## 7.3.2.26 TrueRC(): 0x68/0x69

This read-only command pair returns the True remaining capacity from IT simulation without the effects of the smoothing function.

#### 7.3.2.27 TrueFCC(): 0x6A/0x6B

This read-only command pair returns the True full charge capacity from IT simulation without the effects of the smoothing function.

#### 7.3.2.28 StateTime(): 0x6C/0x6D

This read-only command pair returns the time past since last state change (DISCHARGE, CHARGE, REST).

#### 7.3.2.29 QmaxPassedQ(): 0x6E/0x6F

This read-only command pair returns the passed capacity since the last Qmax DOD update.

#### 7.3.2.30 DOD0(): 0x70/0x71

This unsigned integer indicates the depth of discharge during the most recent OCV reading.

#### 7.3.2.31 QmaxDod0(): 0x72/0x73

This read-only command pair returns the DOD0 saved to be used for next QMax update of Cell 1. The value is only valid when [VOK] = 1.

# 7.3.2.32 QmaxTime(): 0x74/0x75

This read-only command pair returns the time since the last Qmax DOD update.

#### 7.3.3 Data Flash Interface

#### 7.3.3.1 Accessing Data Flash

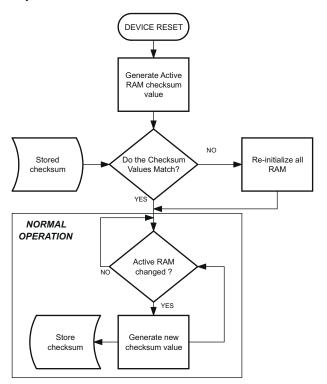

The BQ34Z100-G1 data flash is a non-volatile memory that contains BQ34Z100-G1 initialization, default, cell status, calibration, configuration, and user information. The data flash can be accessed in several different ways, depending on in what mode the BQ34Z100-G1 is operating and what data is being accessed.

Commonly accessed data flash memory locations, frequently read by a host, are conveniently accessed through specific instructions described in  $\frac{1}{2} \frac{1}{2} \frac{1}{3} \frac{1}{3}$ . These commands are available when the BQ34Z100-G1 is either in UNSEALED or SEALED modes.

Most data flash locations, however, can only be accessible in UNSEALED mode by use of the BQ34Z100-G1 evaluation software or by data flash block transfers. These locations should be optimized and/or fixed during the development and manufacture processes. They become part of a Golden Image File and can then be written to multiple battery packs. Once established, the values generally remain unchanged during end-equipment operation.

To access data flash locations individually, the block containing the desired data flash location(s) must be transferred to the command register locations where they can be read to the host or changed directly. This is accomplished by sending the set-up command *BlockDataControl()* (code 0x61) with data 0x00. Up to 32 bytes of data can be read directly from the *BlockData()* command locations 0x40...0x5F, externally altered, then rewritten to the *BlockData()* command space. Alternatively, specific locations can be read, altered, and re-written if their corresponding offsets are used to index into the *BlockData()* command space. Finally, the data residing in

the command space is transferred to data flash, once the correct checksum for the whole block is written to *BlockDataChecksum()* (command number 0x60).

Occasionally, a data flash class will be larger than the 32-byte block size. In this case, the *DataFlashBlock()* command is used to designate which 32-byte block in which the desired locations reside. The correct command address is then given by 0x40 + offset modulo 32. For example, to access *Terminate Voltage* in the Gas Gauging class, *DataFlashClass()* is issued 80 (0x50) to set the class. Because the offset is 48, it must reside in the second 32-byte block. Hence, *DataFlashBlock()* is issued 0x01 to set the block offset, and the offset used to index into the *BlockData()* memory area is  $0x40 + 48 \mod 0 32 = 0x40 + 16 = 0x40 + 0x10 = 0x50$ ; for example, to modify *[VOLTSEL]* in *Pack Configuration* from 0 to 1 to enable the external voltage measurement option.

#### Note

The subclass ID and Offset values are in decimal format in the documentation and in bqStudio. The example below shows these values converted to hexadecimal. For example, the *Pack Configuration* subclass is d64 = 0x40.

- 1. Unseal the device using the *Control()* (0x00/0x01) command if the device is sealed.

- a. Write the first 2 bytes of the UNSEAL key using the *Control*(0x0414) command.

- (wr 0x00 0x14 0x04)

- b. Write the second 2 bytes of the UNSEAL key using the *Control*(0x3672) command.

(wr 0x00 0x72 0x36)

2. Write 0x00 using *BlockDataControl()* command (0x61) to enable block data flash control.

(wr 0x61 0x00)

3. Write 0x40 (*Pack Configuration* Subclass) using the *DataFlashClass()* command (0x3E) to access the Registers subclass.

(wr 0x3E 0x40)

4. Write the block offset location using *DataFlashBlock()* command (0x3F). To access data located at offset 0 to 31, use offset = 0x00. To access data located at offset 32 to 63, use offset = 0x01, and so on, as necessary.

For example, *Pack Configuration* (offset = 0) is in the first block so use (*wr 0x3F 0x00*).

5. To read the data of a specific offset, use address 0x40 + mod(offset, 32). For example, *Pack Configuration* (offset = 0) is located at 0x40 and 0x41; however, **[VOLTSEL]** is in the MSB so only 0x40 needs to be read. Read 1 byte starting at the 0x40 address.

(rd 0x40 old\_Pack\_Configuration\_MSB)

In this example, assume **[VOLTSEL]** = 0 (default).

6. To read the 1-byte checksum, use the *BlockDataChecksum()* command (0x60).

(*rd* 0x60 OLD\_checksum)

- 7. In this example, set **[VOLTSEL]** by setting Bit 3 of *old\_Pack\_Configuration\_MSB* to create *new\_Pack\_Configuration\_MSB*.

- 8. The new value for *new\_Pack\_Configuration\_MSB* can be written by writing to the specific offset location.

For example, to write 1-byte *new\_Pack\_Configuration\_MSB* to *Pack Configuration* (offset=0) located at 0x40, use command (*wr 0x4B new\_Pack\_Configuration\_MSB*).

9. The data is actually transferred to the data flash when the correct checksum for the whole block (0x40 to 0x5F) is written to *BlockDataChecksum()* (0x60).

(wr 0x60 NEW\_checksum)

The checksum is (255-x) where x is the 8-bit summation of the *BlockData()* (0x40 to 0x5F) on a byte-by-byte basis.

A quick way to calculate the new checksum is to make use of the old checksum:

- a. temp = mod (255 *OLD\_checksum old\_Pack\_Configuration\_MSB*), 256)

- b. NEW\_checksum = 255 mod (temp + new\_Pack\_Configuration\_MSB, 256)

10. Reset the gauge to ensure the new data flash parameter goes into effect by using Control(0x0041).

(wr 0x00 0x41 0x00)

If previously sealed, the gauge will automatically become sealed again after RESET.

11. If not previously sealed, then seal the gauge by using *Control*(0x0020).

(*wr* 0x00 0x20 0x00)

Reading and writing subclass data are block operations 32 bytes in length. Data can be written in shorter block sizes, however. Blocks can be shorter than 32 bytes in length. Writing these blocks back to data flash will not overwrite data that extend beyond the actual block length.

#### Note

None of the data written to memory is bounded by the BQ34Z100-G1: The values are not rejected by the gas gauge. Writing an incorrect value may result in hardware failure due to firmware program interpretation of the invalid data. The data written is persistent, so a power-on reset resolves the fault.

#### 7.3.3.2 Manufacturer Information Block