DLP2010LC

JAJSJ81C - MAY 2020 - REVISED JULY 2023

# DLP2010LC .2 WVGA デジタル・マイクロミラー・デバイス

# 1 特長

- 対角 0.2 インチ (5.29mm) のマイクロミラー・アレイ

- 直交レイアウトで 854 × 480 ピクセル・アレイを表示

- マイクロミラー・ピッチ:5.4 ミクロン

- マイクロミラー傾斜角:±17°(水平面に対して)

- 側面照明による最適な効率と光学エンジン・サイズ

- 偏波無依存のアルミニウム製マイクロミラー表面

- 4 ビットの SubLVDS 入力データ・バス

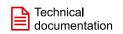

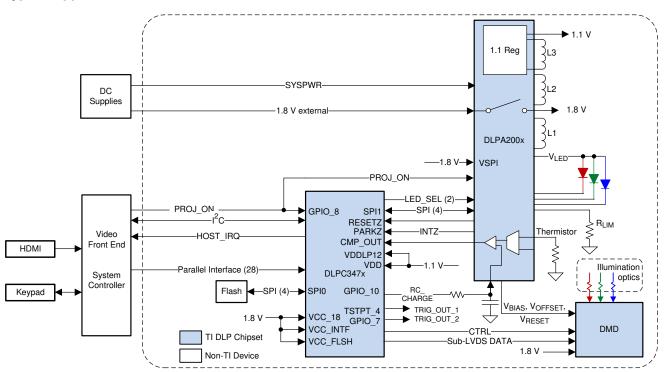

- 専用の DLPC3470 ディスプレイおよび光コントローラと、DLPA200x/DLPA3000 PMIC および LED ドライバによる信頼性の高い動作

# 2 アプリケーション

- 統合型ディスプレイおよび 3D 深度キャプチャ

- スマートフォン / タブレット / ノートブック PC / カメラ

- バッテリ駆動のモバイル・アクセサリ

- 3D 深度キャプチャ:3D カメラ、3D 再構築、AR/VR、 デンタル・スキャナ

- 3D マシン・ビジョン:ロボティクス、計測、インライン検査 (AOI)

- 3D バイオメトリクス:顔面および指紋認識

- 露光:3D プリンタ、空間的および時間的な露光をプログラム可能

# 3 概要

DLP2010LC デジタル・マイクロミラー・デバイス (DMD) は、デジタル制御の MOEMS (micro-opto-electromechanical system) 空間光変調器 (SLM) です。適切な光学システムと組み合わせることで、この DMD は画像、映像、パターンを表示できます。このデバイスは、DLP2010LCDMD、DLPC3470 コントローラ、DLPA200x/DLPA3000 PMIC/LEDドライバで構成されるチップセットの一部です。この DMD は物理的なサイズが小さいため、小さな外形と低消費電力が重要な携帯機器に使用できます。小型パッケージと小型 LED が、スペースが制約される光エンジンに理想的です。

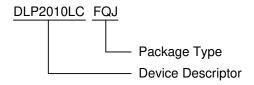

## 製品情報

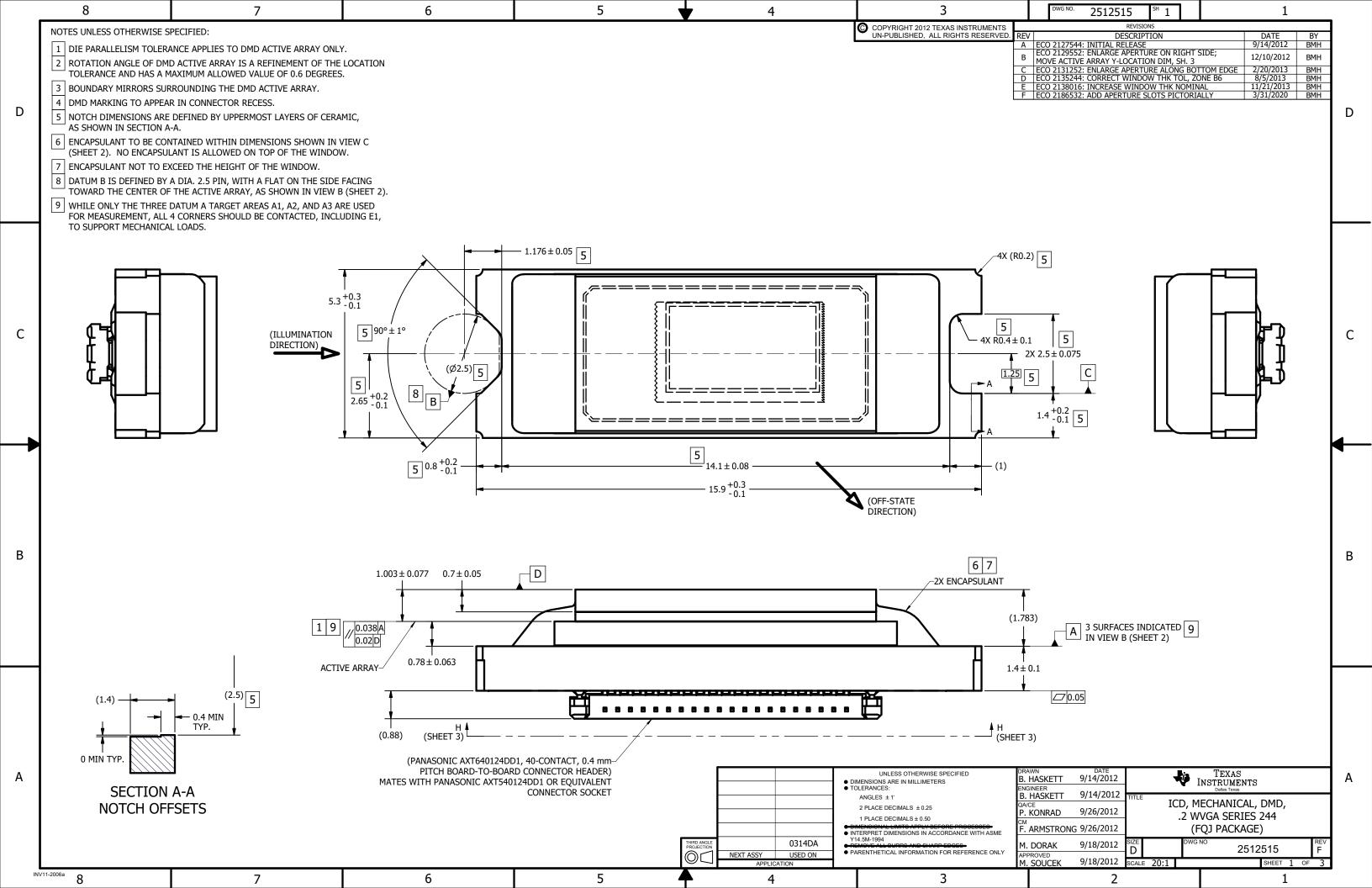

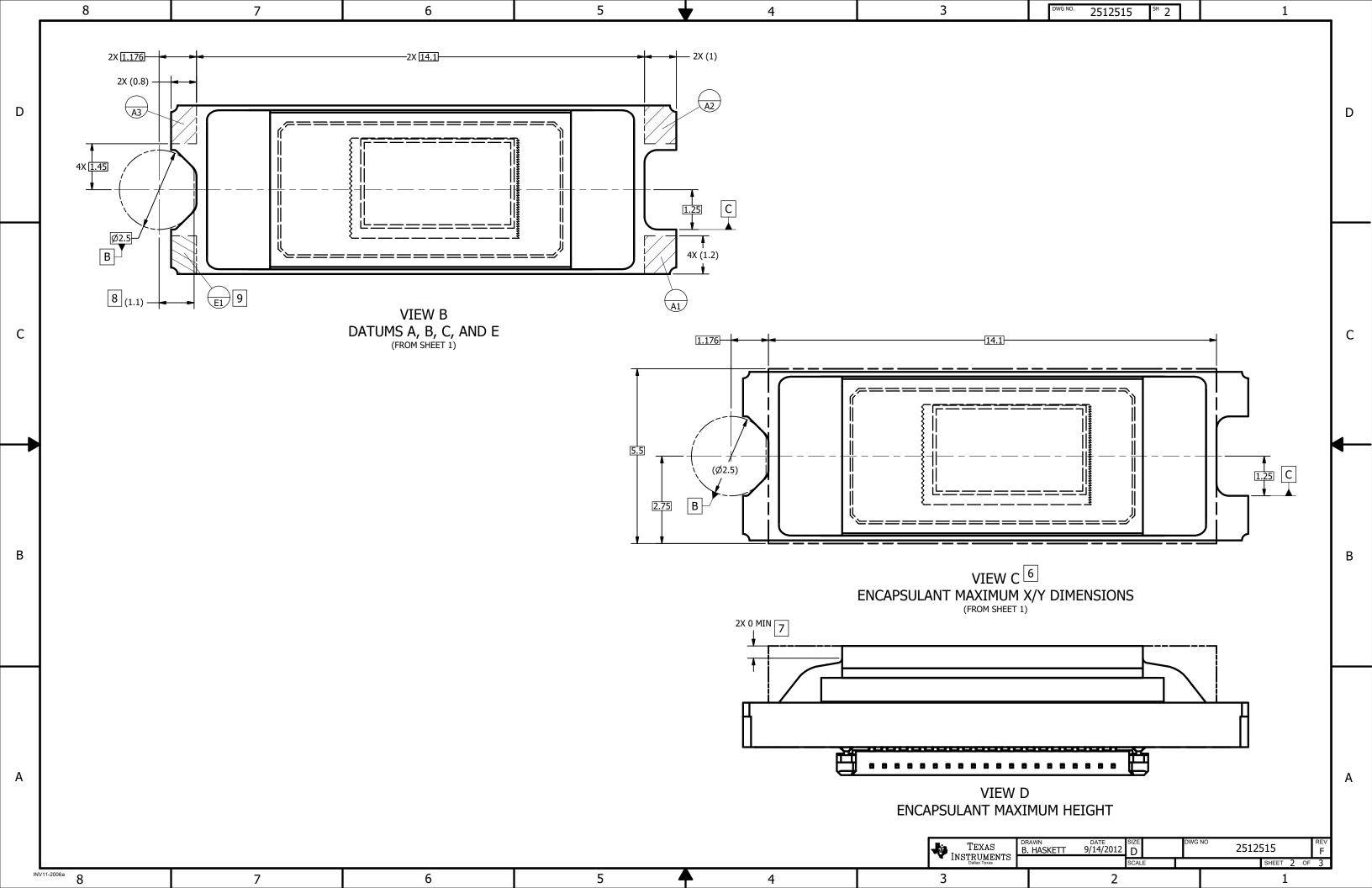

| 部品番号      | パッケージ <sup>(1)</sup> | 本体サイズ (公称)     |

|-----------|----------------------|----------------|

| DLP2010LC | FQJ (40)             | 15.9mm × 5.3mm |

(1) 利用可能なすべてのパッケージについては、このデータシートの 末尾にある注文情報を参照してください。

0.2 WVGA チップセット

# **Table of Contents**

| <b>1</b> 特長 1                                            | 7.5 Optical Interface and System Image Quality  |                  |

|----------------------------------------------------------|-------------------------------------------------|------------------|

| 2 アプリケーション1                                              | Considerations                                  | 25               |

| 3 概要1                                                    | 7.6 Micromirror Array Temperature Calculation   | 26               |

| 4 Revision History2                                      | 7.7 Micromirror Power Density Calculation       | 27               |

| 5 Pin Configuration and Functions3                       | 7.8 Micromirror Landed-On/Landed-Off Duty Cycle |                  |

| Specifications6                                          | 8 Application and Implementation                |                  |

| 6.1 Absolute Maximum Ratings6                            | 8.1 Application Information                     |                  |

| 6.2 Storage Conditions6                                  | 8.2 Typical Application                         |                  |

| 6.3 ESD Ratings8                                         | 9 Power Supply Recommendations                  | 35               |

| 6.4 Recommended Operating Conditions8                    | 9.1 DMD Power Supply Power-Up Procedure         |                  |

| 6.5 Thermal Information10                                | 9.2 DMD Power Supply Power-Down Procedure       |                  |

| 6.6 Electrical Characteristics10                         | 9.3 Power Supply Sequencing Requirements        | 36               |

| 6.7 Timing Requirements12                                | 10 Layout                                       | 38               |

| 6.8 Switching Characteristics18                          | 10.1 Layout Guidelines                          |                  |

| 6.9 System Mounting Interface Loads                      | 10.2 Layout Example                             |                  |

| 6.10 Physical Characteristics of the Micromirror Array20 | 11 Device and Documentation Support             | 40               |

| 6.11 Micromirror Array Optical Characteristics           | 11.1 Device Support                             | 40               |

| 6.12 Window Characteristics23                            | 11.2 Related Links                              |                  |

| 6.13 Chipset Component Usage Specification23             | 11.3ドキュメントの更新通知を受け取る方法                          | 40               |

| 6.14 Software Requirements23                             | <b>11.4</b> サポート・リソース                           | <mark>4</mark> 1 |

| 7 Detailed Description24                                 | 11.5 Trademarks                                 | <b>4</b> 1       |

| 7.1 Overview24                                           | 11.6 静電気放電に関する注意事項                              | 41               |

| 7.2 Functional Block Diagram24                           | 11.7 用語集                                        |                  |

| 7.3 Feature Description25                                | 12 Mechanical, Packaging, and Orderable         |                  |

| 7.4 Device Functional Modes25                            | Information                                     | 42               |

|                                                          |                                                 |                  |

# **4 Revision History**

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Changes from Revision B (May 2022) to Revision C (July 2023)          | Page |

|-----------------------------------------------------------------------|------|

| Added "ILLUMINATION" to Recommended Operating Conditions              | 8    |

| Updated Micromirror Array Optical Characteristics    6-18             | 21   |

| Updated Micromirror Array Temperature Calculation                     | 26   |

| Added Micromirror Power Density Calculation                           | 27   |

| Changes from Revision A (October 2021) to Revision B (May 2022)       | Page |

| Updated Absolute Maximum Ratings disclosure to the latest TI standard | 6    |

| Updated Micromirror Array Optical Characteristics                     | 21   |

| Added Third-Party Products Disclaimer                                 | 40   |

|                                                                       |      |

Product Folder Links: DLP2010LC

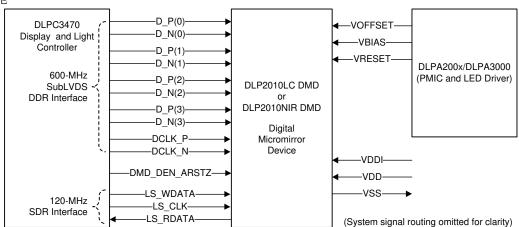

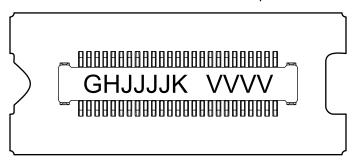

# **5 Pin Configuration and Functions**

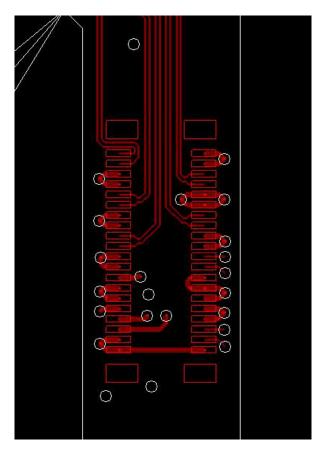

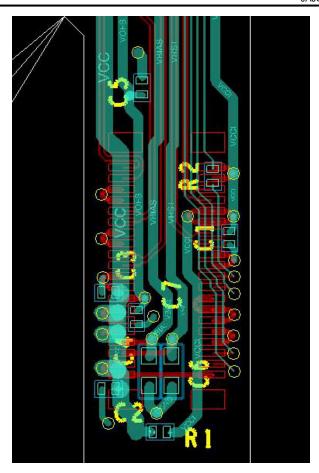

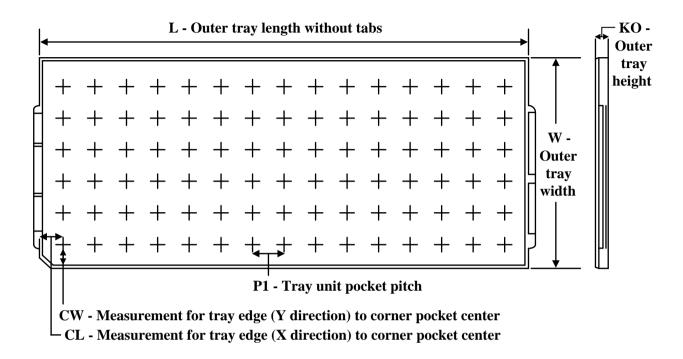

図 5-1. FQJ Package 40-Pin Connector Bottom View

表 5-1. Pin Functions - Connector Pins

| PIN <sup>(1)</sup> |     | TYPE | TYPE SIGNAL DATA RATE | DESCRIPTION | PACKAGE NET     |                           |  |  |

|--------------------|-----|------|-----------------------|-------------|-----------------|---------------------------|--|--|

| NAME               | NO. | ITPE | SIGNAL                | DAIA RAIE   | DESCRIPTION     | LENGTH <sup>(2)</sup> (mm |  |  |

| DATA INPUTS        |     |      |                       | 1           |                 | 1                         |  |  |

| D_N(0)             | G4  | I    | SubLVDS               | Double      | Data, Negative  | 7.03                      |  |  |

| D_P(0)             | G3  | I    | SubLVDS               | Double      | Data, Positive  | 7.03                      |  |  |

| D_N(1)             | G8  | I    | SubLVDS               | Double      | Data, Negative  | 7.03                      |  |  |

| D_P(1)             | G7  | I    | SubLVDS               | Double      | Data, Positive  | 7.03                      |  |  |

| D_N(2)             | H5  | I    | SubLVDS               | Double      | Data, Negative  | 7.02                      |  |  |

| D_P(2)             | H6  | I    | SubLVDS               | Double      | Data, Positive  | 7.02                      |  |  |

| D_N(3)             | H1  | I    | SubLVDS               | Double      | Data, Negative  | 7.00                      |  |  |

| D_P(3)             | H2  | I    | SubLVDS               | Double      | Data, Positive  | 7.00                      |  |  |

| DCLK_N             | H9  | I    | SubLVDS               | Double      | Clock, Negative | 7.03                      |  |  |

| DCLK_P             | H10 | 1    | SubLVDS               | Double      | Clock, Positive | 7.03                      |  |  |

| CONTROL INPUTS     |     |      | •                     | 1           | ,               | ,                         |  |  |

## 表 5-1. Pin Functions – Connector Pins (continued)

| PIN <sup>(1)</sup>     |     |        |                      |           |                                                                                                                                                                                         | PACKAGE NET                |

|------------------------|-----|--------|----------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| NAME                   | NO. | TYPE   | SIGNAL               | DATA RATE | DESCRIPTION                                                                                                                                                                             | LENGTH <sup>(2)</sup> (mm) |

| DMD_DEN_ARSTZ          | G12 | I      | LPSDR <sup>(1)</sup> |           | Asynchronous reset DMD signal. A low signal places the DMD in reset. A high signal releases the DMD from reset and places it in active mode.                                            | 5.72                       |

| LS_CLK                 | G19 | I      | LPSDR                | Single    | Clock for low-speed interface                                                                                                                                                           | 3.54                       |

| LS_WDATA               | G18 | I      | LPSDR                | Single    | Write data for low-speed interface                                                                                                                                                      | 3.54                       |

| LS_RDATA               | G11 | 0      | LPSDR                | Single    | Read data for low-speed interface                                                                                                                                                       | 8.11                       |

| POWER                  |     |        |                      |           |                                                                                                                                                                                         |                            |

| VBIAS <sup>(3)</sup>   | H17 | Power  |                      |           | Supply voltage for positive bias level at micromirrors                                                                                                                                  |                            |

| VOFFSET <sup>(3)</sup> | H13 | Power  |                      |           | Supply voltage for HVCMOS core logic.<br>Includes: supply voltage for stepped high<br>level at micromirror address electrodes and<br>supply voltage for offset level at<br>micromirrors |                            |

| VRESET <sup>(3)</sup>  | H18 | Power  |                      |           | Supply voltage for negative reset level at micromirrors                                                                                                                                 |                            |

| VDD <sup>(3)</sup>     | G20 | Power  |                      |           |                                                                                                                                                                                         |                            |

| VDD                    | H14 | Power  |                      |           | Supply voltage for micromirror low voltage                                                                                                                                              |                            |

| VDD                    | H15 | Power  |                      |           | CMOS core logic includes supply voltage for LPSDR inputs and supply voltage for                                                                                                         |                            |

| VDD                    | H16 | Power  |                      |           | normal high level at micromirror address                                                                                                                                                |                            |

| VDD                    | H19 | Power  |                      |           | electrodes.                                                                                                                                                                             |                            |

| VDD                    | H20 | Power  |                      |           |                                                                                                                                                                                         |                            |

| VDDI <sup>(3)</sup>    | G1  | Power  |                      |           |                                                                                                                                                                                         |                            |

| VDDI                   | G2  | Power  |                      |           | Supply voltage for Subl VDS receivers                                                                                                                                                   |                            |

| VDDI                   | G5  | Power  |                      |           | Supply voltage for SubLVDS receivers                                                                                                                                                    |                            |

| VDDI                   | G6  | Power  |                      |           |                                                                                                                                                                                         |                            |

| VSS <sup>(3)</sup>     | G9  | Ground |                      |           |                                                                                                                                                                                         |                            |

| VSS                    | G10 | Ground |                      |           |                                                                                                                                                                                         |                            |

| VSS                    | G13 | Ground |                      |           |                                                                                                                                                                                         |                            |

| VSS                    | G14 | Ground |                      |           |                                                                                                                                                                                         |                            |

| VSS                    | G15 | Ground |                      |           |                                                                                                                                                                                         |                            |

| VSS                    | G16 | Ground |                      |           | ]                                                                                                                                                                                       |                            |

| VSS                    | G17 | Ground |                      |           | Ground. Common return for all power.                                                                                                                                                    |                            |

| VSS                    | НЗ  | Ground |                      |           | ]                                                                                                                                                                                       |                            |

| VSS                    | H4  | Ground |                      |           | ]                                                                                                                                                                                       |                            |

| VSS                    | H7  | Ground |                      |           | 1                                                                                                                                                                                       |                            |

| VSS                    | H8  | Ground |                      |           | 1                                                                                                                                                                                       |                            |

| VSS                    | H11 | Ground |                      |           | 1                                                                                                                                                                                       |                            |

| VSS                    | H12 | Ground |                      |           |                                                                                                                                                                                         |                            |

<sup>(1)</sup> Low speed interface is LPSDR and adheres to the Electrical Characteristics and AC/DC Operating Conditions table in JEDEC Standard No. 209B, Low Power Double Data Rate (LPDDR) JESD209B.

(2) Net trace lengths inside the package:

Relative dielectric constant for the FQJ ceramic package is 9.8.

Propagation speed = 11.8 / sqrt(9.8) = 3.769 inches/ns.

Propagation delay = 0.265 ns/inch = 265 ps/inch = 10.43 ps/mm.

(3) The following power supplies are all required to operate the DMD: VSS, VDD, VDDI, VOFFSET, VBIAS, VRESET.

# 表 5-2. Pin Functions – Test Pads

|        | EX U-Z. I III I UIIC |        | 311 843        |

|--------|----------------------|--------|----------------|

| NUMBER | SYSTEM BOARD         | NUMBER | SYSTEM BOARD   |

| A2     | Do not connect       | D2     | Do not connect |

| A3     | Do not connect       | D3     | Do not connect |

| A4     | Do not connect       | D17    | Do not connect |

| A5     | Do not connect       | D18    | Do not connect |

| A6     | Do not connect       |        |                |

| A7     | Do not connect       | E2     | Do not connect |

| A8     | Do not connect       | E3     | Do not connect |

| A9     | Do not connect       | E17    | Do not connect |

| A10    | Do not connect       | E18    | Do not connect |

| A11    | Do not connect       |        |                |

| A12    | Do not connect       | F1     | Do not connect |

| A13    | Do not connect       | F2     | Do not connect |

| A14    | Do not connect       | F3     | Do not connect |

| A15    | Do not connect       | F4     | Do not connect |

| A16    | Do not connect       | F5     | Do not connect |

| A17    | Do not connect       | F6     | Do not connect |

| A18    | Do not connect       | F7     | Do not connect |

| A19    | Do not connect       | F8     | Do not connect |

|        |                      | F9     | Do not connect |

| B2     | Do not connect       | F10    | Do not connect |

| В3     | Do not connect       | F11    | Do not connect |

| B17    | Do not connect       | F12    | Do not connect |

| B18    | Do not connect       | F13    | Do not connect |

|        | 1                    | F14    | Do not connect |

| C2     | Do not connect       | F15    | Do not connect |

| C3     | Do not connect       | F16    | Do not connect |

| C17    | Do not connect       | F17    | Do not connect |

| C18    | Do not connect       | F18    | Do not connect |

|        |                      | F19    | Do not connect |

|        |                      |        |                |

# **6 Specifications**

# 6.1 Absolute Maximum Ratings

See (1)

|                 |                                                                                   |                                                                                                               | MIN  | MAX        | UBIT  |

|-----------------|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|------|------------|-------|

|                 | VDD                                                                               | for LVCMOS core logic <sup>(2)</sup> Supply voltage for LPSDR low speed interface                             | -0.5 | 2.3        |       |

|                 | VDDI                                                                              | for SubLVDS receivers <sup>(2)</sup>                                                                          | -0.5 | 2.3        |       |

| Supply voltage  | VOFFSET                                                                           | for HVCMOS and micromirror electrode <sup>(2) (3)</sup>                                                       | -0.5 | 10.6       |       |

|                 | VBIAS                                                                             | for micromirror electrode <sup>(2)</sup>                                                                      | -0.5 | 19         | V     |

|                 | VRESET                                                                            | for micromirror electrode <sup>(2)</sup>                                                                      | -15  | 0.5        |       |

|                 | VDDI–VDD                                                                          | delta (absolute value) <sup>(4)</sup>                                                                         |      | 0.3        |       |

|                 | VBIAS-VOFFSET                                                                     | delta (absolute value) <sup>(5)</sup>                                                                         |      | 11         |       |

|                 | VBIAS-VRESET                                                                      | delta (absolute value) <sup>(6)</sup>                                                                         |      | 34         |       |

| Innut voltage   | for other inputs LPSDR <sup>(2)</sup> for other inputs SubLVDS <sup>(2) (7)</sup> |                                                                                                               |      | VDD + 0.5  | V     |

| Input voltage   |                                                                                   |                                                                                                               |      | VDDI + 0.5 | v     |

| Innut nine      | VID                                                                               | SubLVDS input differential voltage (absolute value) <sup>(7)</sup>                                            |      | 810        | mV    |

| Input pins      | IID                                                                               | SubLVDS input differential current                                                                            |      | 8.1        | mA    |

| Clock frequency | $f_{clock}$                                                                       | Clock frequency for low speed interface LS_CLK                                                                |      | 130        | MHz   |

| Clock frequency | $f_{clock}$                                                                       | Clock frequency for high speed interface DCLK                                                                 |      | 620        | IVITZ |

|                 | T and T                                                                           | Temperature – operational <sup>(8)</sup>                                                                      | -20  | 90         |       |

|                 | T <sub>ARRAY</sub> and T <sub>WINDOW</sub>                                        | Temperature – non-operational <sup>(8)</sup>                                                                  | -40  | 90         |       |

| Environmental   | T <sub>DP</sub>                                                                   | Dew Point Temperature - operating and non-operating (non-condensing)                                          |      | 81         |       |

|                 | T <sub>DELTA</sub>                                                                | Absolute Temperature delta between any point on the window edge and the ceramic test point TP1 <sup>(9)</sup> |      | 30         |       |

- (1) Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

- (2) All voltage values are with respect to the ground terminals (VSS). The following power supplies are all required to operate the DMD: VSS, VDD, VDDI, VOFFSET, VBIAS, and VRESET.

- (3) VOFFSET supply transients must fall within specified voltages.

- (4) Exceeding the recommended allowable absolute voltage difference between VDDI and VDD may result in excessive current draw.

- (5) Exceeding the recommended allowable absolute voltage difference between VBIAS and VOFFSET may result in excessive current draw.

- (6) Exceeding the recommended allowable absolute voltage difference between VBIAS and VRESET may result in excessive current draw.

- (7) This maximum input voltage rating applies when each input of a differential pair is at the same voltage potential. Sub-LVDS differential inputs must not exceed the specified limit or damage may result to the internal termination resistors.

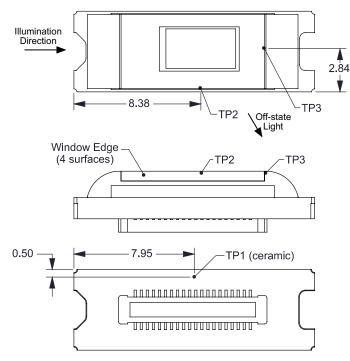

- (8) The highest temperature of the active array (as calculated by the セクション 7.6), or of any point along the Window Edge as defined in 図 7-1. The locations of thermal test points TP2 and TP3 in 図 7-1 are intended to measure the highest window edge temperature. If a particular application causes another point on the window edge to be at a higher temperature, that point should be used.

- (9) Temperature delta is the highest difference between the ceramic test point 1 (TP1) and anywhere on the window edge as shown in ☑ 7-1. The window test points TP2 and TP3 shown in ☑ 7-1 are intended to result in the worst case delta. If a particular application causes another point on the window edge to result in a larger delta temperature, that point should be used.

## **6.2 Storage Conditions**

applicable for the DMD as a component or non-operational in a system

|                     |                                                                       | MIN | MAX | UNIT |

|---------------------|-----------------------------------------------------------------------|-----|-----|------|

| $T_{DMD}$           | DMD storage temperature                                               | -40 | 85  | °C   |

| T <sub>DP-AVG</sub> | Average dew point temperature, (non-condensing) <sup>(1)</sup>        |     | 24  | °C   |

| T <sub>DP-ELR</sub> | Elevated dew point temperature range, (non-condensing) <sup>(2)</sup> | 28  | 36  | °C   |

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

English Data Sheet: DLPS180

# **6.2 Storage Conditions (continued)**

applicable for the DMD as a component or non-operational in a system

|                   |                                                         | MIN | MAX | UNIT   |

|-------------------|---------------------------------------------------------|-----|-----|--------|

| CT <sub>ELR</sub> | Cumulative time in elevated dew point temperature range |     | 6   | Months |

- (1) The average over time (including storage and operating) that the device is not in the elevated dew point temperature range.

- (2) Exposure to dew point temperatures in the elevated range during storage and operation should be limited to less than a total cumulative time of CT<sub>ELR</sub>.

# **6.3 ESD Ratings**

|                    |                         |                                                                   | VALUE | UNIT |

|--------------------|-------------------------|-------------------------------------------------------------------|-------|------|

| V <sub>(ESD)</sub> | Electrostatic discharge | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup> | ±2000 | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

# **6.4 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)(1) (2) (3)

|                      |                                                                                      | MIN   | NOM | MAX   | UNIT |

|----------------------|--------------------------------------------------------------------------------------|-------|-----|-------|------|

| SUPPLY VOLTAGE RA    | NGE <sup>(4)</sup>                                                                   |       |     |       |      |

| VDD                  | Supply voltage for LVCMOS core logic<br>Supply voltage for LPSDR low-speed interface | 1.65  | 1.8 | 1.95  | V    |

| VDDI                 | Supply voltage for SubLVDS receivers                                                 | 1.65  | 1.8 | 1.95  | V    |

| VOFFSET              | Supply voltage for HVCMOS and micromirror electrode <sup>(5)</sup>                   | 9.5   | 10  | 10.5  | V    |

| VBIAS                | Supply voltage for mirror electrode                                                  | 17.5  | 18  | 18.5  | V    |

| VRESET               | Supply voltage for micromirror electrode                                             | -14.5 | -14 | -13.5 | V    |

| VDDI-VDD             | Supply voltage delta (absolute value) <sup>(6)</sup>                                 |       |     | 0.3   | V    |

| VBIAS-VOFFSET        | Supply voltage delta (absolute value) <sup>(7)</sup>                                 |       |     | 10.5  | V    |

| VBIAS-VRESET         | Supply voltage delta (absolute value) <sup>(8)</sup>                                 |       |     | 33    | V    |

| CLOCK FREQUENCY      |                                                                                      |       |     | -     |      |

| $f_{clock}$          | Clock frequency for low speed interface LS_CLK <sup>(9)</sup>                        | 108   |     | 120   | MHz  |

| $f_{clock}$          | Clock frequency for high speed interface DCLK <sup>(10)</sup>                        | 300   |     | 600   | MHz  |

|                      | Duty cycle distortion DCLK                                                           | 44%   |     | 56%   |      |

| SUBLVDS INTERFACE    | <b>-</b> (10)                                                                        |       |     |       |      |

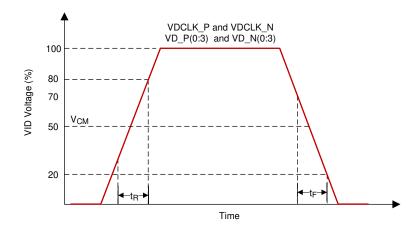

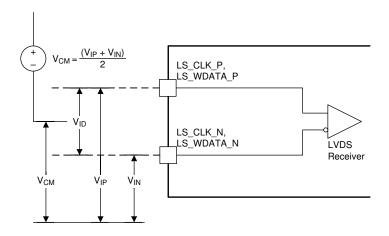

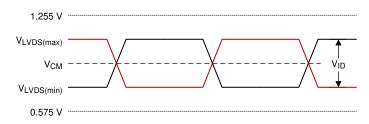

| V <sub>ID</sub>      | SubLVDS input differential voltage (absolute value),<br>☑ 6-9, ☑ 6-10                | 150   | 250 | 350   | mV   |

| V <sub>CM</sub>      | Common mode voltage,<br>☑ 6-9, ☑ 6-10                                                | 700   | 900 | 1100  | mV   |

| V <sub>SUBLVDS</sub> | SubLVDS voltage,<br>☑ 6-9, ☑ 6-10                                                    | 575   |     | 1225  | mV   |

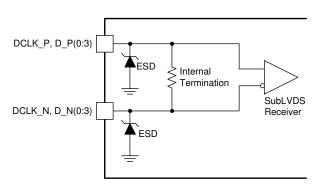

| Z <sub>LINE</sub>    | Line differential impedance (PWB/trace)                                              | 90    | 100 | 110   | Ω    |

| Z <sub>IN</sub>      | Internal differential termination resistance 図 6-11                                  | 80    | 100 | 120   | Ω    |

|                      | 100-Ω differential PCB trace                                                         | 6.35  |     | 152.4 | mm   |

Product Folder Links: DLP2010LC

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

# 6.4 Recommended Operating Conditions (continued)

over operating free-air temperature range (unless otherwise noted)(1) (2) (3)

|                     |                                                                                                          | MIN | NOM | MAX                      | UNIT               |

|---------------------|----------------------------------------------------------------------------------------------------------|-----|-----|--------------------------|--------------------|

| ENVIRONMENTAL       |                                                                                                          |     |     |                          |                    |

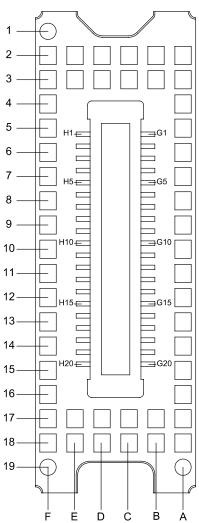

| <del>-</del>        | Array Temperature – long-term operational <sup>(11)</sup> (12) (13) (14)                                 | 0   |     | 40 to 70 <sup>(13)</sup> |                    |

| T <sub>ARRAY</sub>  | Array Temperature - short-term operational, 25 hr max <sup>(12)</sup> (15)                               | -20 |     | -10                      | °C                 |

|                     | Array Temperature - short-term operational, 500 hr max <sup>(12)</sup> (15)                              | -10 |     | 0                        |                    |

|                     | Array Temperature – short-term operational, 500 hr max <sup>(12)</sup> (15)                              | 70  |     | 75                       |                    |

| T <sub>DELTA</sub>  | Absolute Temperature difference between any point on the window edge and the ceramic test point TP1 (16) |     |     | 15                       | °C                 |

| T <sub>WINDOW</sub> | Window temperature – operational <sup>(11)</sup> (17)                                                    |     |     | 90                       | °C                 |

| T <sub>DP-AVG</sub> | Average dew point temperature (non-condensing) <sup>(18)</sup>                                           |     |     | 24                       | °C                 |

| T <sub>DP-ELR</sub> | Elevated dew point temperature range (non-condensing) <sup>(19)</sup>                                    | 28  |     | 36                       | °C                 |

| CT <sub>ELR</sub>   | Cumulative time in elevated dew point temperature range                                                  |     |     | 6                        | Months             |

| ILLUMINATION        |                                                                                                          | -   |     |                          |                    |

| ILL <sub>UV</sub>   | Illumination power at wavelengths < 410 nm <sup>(11)</sup>                                               |     |     | 10                       | mW/cm <sup>2</sup> |

| ILL <sub>VIS</sub>  | Illumination power at wavelengths ≥ 410 nm and ≤ 800 nm <sup>(21)</sup>                                  |     |     | 26.1                     | W/cm <sup>2</sup>  |

| ILL <sub>IR</sub>   | Illumination power at wavelengths > 800 nm                                                               | ,   |     | 10                       | mW/cm <sup>2</sup> |

| ILL <sub>BLU</sub>  | Illumination power at wavelengths ≥ 410 nm and ≤ 475 nm <sup>(21)</sup>                                  |     |     | 8.3                      | W/cm <sup>2</sup>  |

| ILL <sub>BLU1</sub> | Illumination power at wavelengths ≥ 410 nm and ≤ 445 nm <sup>(21)</sup>                                  |     |     | 1.5                      | W/cm2              |

| ILL <sub>θ</sub>    | Illumination marginal ray angle <sup>(20)</sup>                                                          |     |     | 55                       | deg                |

- (1) セクション 6.4 are applicable after the DMD is installed in the final product.

- (2) The functional performance of the device specified in this datasheet is achieved when operating the device within the limits defined by the セクション 6.4. No level of performance is implied when operating the device above or below the セクション 6.4 limits.

- (3) The following power supplies are all required to operate the DMD: VSS, VDD, VDDI, VOFFSET, VBIAS, and VRESET.

- (4) All voltage values are with respect to the ground pins (VSS).

- (5) VOFFSET supply transients must fall within specified maximum voltages.

- (6) To prevent excess current, the supply voltage delta |VDDI VDD| must be less than specified limit.

- (7) To prevent excess current, the supply voltage delta |VBIAS VOFFSET| must be less than specified limit.

- (8) To prevent excess current, the supply voltage delta |VBIAS VRESET| must be less than specified limit.

- (9) LS\_CLK must run as specified to ensure internal DMD timing for reset waveform commands.

- (10) Refer to the SubLVDS timing requirements in *Timing Requirements*.

- (11) Simultaneous exposure of the DMD to the maximum セクション 6.4 for temperature and UV illumination will reduce device lifetime.

- (12) The array temperature cannot be measured directly and must be computed analytically from the temperature measured at test point 1 (TP1) shown in 図 7-1 and the Package Thermal Resistance using セクション 7.6.

- (13) Per 🗵 6-1, the maximum operational array temperature should be derated based on the micromirror landed duty cycle that the DMD experiences in the end application. Refer to セクション 7.8 for a definition of micromirror landed duty cycle.

- (14) Long-term is defined as the usable life of the device

- (15) Short-term is the total cumulative time over the useful life of the device.

- (16) Temperature delta is the highest difference between the ceramic test point 1 (TP1) and anywhere on the window edge shown in ⊠ 7-1. The window test points TP2 and TP3 shown in ⊠ 7-1 are intended to result in the worst case delta temperature. If a particular application causes another point on the window edge to result in a larger delta temperature, that point should be used.

- (17) Window temperature is the highest temperature on the window edge shown in  $\boxtimes$  7-1. The locations of thermal test points TP2 and TP3 in  $\boxtimes$  7-1 are intended to measure the highest window edge temperature. If a particular application causes another point on the window edge to result in a larger delta temperature, that point should be used.

- (18) The average over time (including storage and operating) that the device is not in the elevated dew point temperature range.

- (19) Exposure to dew point temperatures in the elevated range during storage and operation should be limited to less than a total cumulative time of CT<sub>FI R</sub>.

- (20) The maximum marginal ray angle of the incoming illumination light at any point in the micromirror array, including Pond of Micromirrors (POM), should not exceed 55 degrees from the normal to the device array plane. The device window aperture has not necessarily been designed to allow incoming light at higher maximum angles to pass to the micromirrors, and the device performance has not been tested nor qualified at angles exceeding this. Illumination light exceeding this angle outside the micromirror array (including POM) will contribute to thermal limitations described in this document, and may negatively affect lifetime.

- (21) The maximum allowable optical power incident on the DMD is limited by the maximum optical power density for each wavelength range specified and the micromirror array temperature (T<sub>ARRAY</sub>).

☑ 6-1. Maximum Recommended Array Temperature – Derating Curve

#### 6.5 Thermal Information

|                                                                     | DLP2010LC   |      |

|---------------------------------------------------------------------|-------------|------|

| THERMAL METRIC <sup>(1)</sup>                                       | FQJ Package | UNIT |

|                                                                     | 40 PINS     |      |

| Thermal resistance Active area to test point 1 (TP1) <sup>(1)</sup> | 7.9         | °C/W |

(1) The DMD is designed to conduct absorbed and dissipated heat to the back of the package. The cooling system must be capable of maintaining the package within the temperature range specified in the \*\*\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textstyle=\textst

#### **6.6 Electrical Characteristics**

Over operating free-air temperature range (unless otherwise noted)(1)

|                     | PARAMETER                                            | TEST CONDITIONS(2) | MIN | TYP  | MAX  | UNIT    |  |

|---------------------|------------------------------------------------------|--------------------|-----|------|------|---------|--|

| CURREN              | Т                                                    |                    |     |      |      |         |  |

|                     | Supply current: VDD <sup>(3)</sup> (4)               | VDD = 1.95 V       |     |      | 34.7 | mA      |  |

| I <sub>DD</sub>     | Supply current. VDD-7-7-7                            | VDD = 1.8 V        |     | 27.5 |      | ША      |  |

| ı                   | Supply current: VDDI <sup>(3)</sup> (4)              | VDDI = 1.95 V      |     |      | 9.4  | mA      |  |

| I <sub>DDI</sub>    | Supply current. VDDI (777)                           | VDD = 1.8 V        |     | 6.6  |      | ША      |  |

| 1                   | Supply current: VOFFSET <sup>(5)</sup> (6)           | VOFFSET = 10.5 V   |     |      | 1.7  | - mA    |  |

| IOFFSET             | Supply culterit. VOFFSET(47)                         | VOFFSET = 10 V     |     | 0.9  |      |         |  |

| 1                   | Supply current: VBIAS <sup>(5)</sup> (6)             | VBIAS = 18.5 V     |     |      | 0.4  | mA      |  |

| I <sub>BIAS</sub>   | Supply current. VBIAS (7 (7)                         | VBIAS = 18 V       |     | 0.2  |      |         |  |

|                     | Supply current: VRESET <sup>(6)</sup>                | VRESET = -14.5 V   |     |      | 2    |         |  |

| I <sub>RESET</sub>  | Supply current. VRESET                               | VRESET = -14 V     |     | 1.2  |      | mA      |  |

| POWER <sup>(7</sup> |                                                      |                    |     |      |      |         |  |

| P <sub>DD</sub>     | Supply power dissipation: VDD <sup>(3)</sup> (4)     | VDD = 1.95 V       |     |      | 67.7 | mW      |  |

| F DD                | Supply power dissipation. VDD                        | VDD = 1.8 V        |     | 49.5 |      | - IIIVV |  |

| В                   | Supply power dissipation: VDDI <sup>(3)</sup> (4)    | VDDI = 1.95 V      |     |      | 18.3 | mW      |  |

| P <sub>DDI</sub>    | Supply power dissipation. VDDIV/V/                   | VDD = 1.8 V        |     | 11.9 |      |         |  |

| D                   | Supply power dissipation: VOFFSET <sup>(5)</sup> (6) | VOFFSET = 10.5 V   |     |      | 17.9 | mW      |  |

| P <sub>OFFSET</sub> | Supply power dissipation. VOFFSET(8) (8)             | VOFFSET = 10 V     |     | 9    |      | IIIVV   |  |

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

### **6.6 Electrical Characteristics (continued)**

Over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                     | PARAMETER                                          | TEST CONDITIONS(2)                                    | MIN       | TYP  | MAX       | UNIT  |  |

|---------------------|----------------------------------------------------|-------------------------------------------------------|-----------|------|-----------|-------|--|

| D                   | Supply power dissipation: VBIAS <sup>(5)</sup> (6) | VBIAS = 18.5 V                                        |           |      | 7.4       | mW    |  |

| P <sub>BIAS</sub>   | Supply power dissipation. VBIAS(9)(9)              | VBIAS = 18 V                                          |           | 3.6  |           | IIIVV |  |

| D                   | Supply payor dissination: VDCSCT(6)                | VRESET = -14.5 V                                      |           |      | 29        | m2\A/ |  |

| P <sub>RESET</sub>  | Supply power dissipation: VRESET <sup>(6)</sup>    | VRESET = -14 V                                        |           | 16.8 |           | mW    |  |

| P <sub>TOTAL</sub>  | Supply power dissipation: Total                    |                                                       |           | 90.8 | 140.3     | mW    |  |

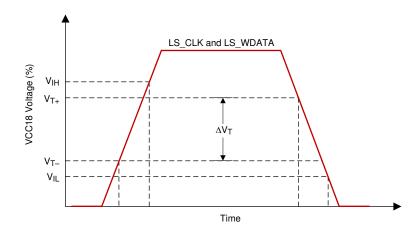

| LPSDR IN            | NPUT <sup>(8)</sup>                                |                                                       |           |      |           |       |  |

| V <sub>IH(DC)</sub> | DC input high voltage <sup>(9)</sup>               |                                                       | 0.7 × VDD |      | VDD + 0.3 | V     |  |

| V <sub>IL(DC)</sub> | DC input low voltage <sup>(9)</sup>                |                                                       | -0.3      |      | 0.3 × VDD | V     |  |

| V <sub>IH(AC)</sub> | AC input high voltage <sup>(9)</sup>               |                                                       | 0.8 × VDD |      | VDD + 0.3 | V     |  |

| V <sub>IL(AC)</sub> | AC input low voltage <sup>(9)</sup>                |                                                       | -0.3      |      | 0.2 × VDD | V     |  |

| $\Delta V_T$        | Hysteresis ( V <sub>T+</sub> – V <sub>T-</sub> )   | ☑ 6-12                                                | 0.1 × VDD |      | 0.4 × VDD | V     |  |

| I <sub>IL</sub>     | Low-level input current                            | VDD = 1.95 V; V <sub>I</sub> = 0 V                    | -100      |      |           | nA    |  |

| I <sub>IH</sub>     | High-level input current                           | VDD = 1.95 V; V <sub>I</sub> = 1.95 V                 |           |      | 100       | nA    |  |

| LPSDR O             | OUTPUT <sup>(10)</sup>                             |                                                       |           |      |           |       |  |

| V <sub>OH</sub>     | DC output high voltage                             | I <sub>OH</sub> = –2 mA                               | 0.8 × VDD |      |           | V     |  |

| V <sub>OL</sub>     | DC output low voltage                              | I <sub>OL</sub> = 2 mA                                |           |      | 0.2 × VDD | V     |  |

| CAPACIT             | ANCE                                               |                                                       |           |      |           |       |  |

| 0                   | Input capacitance LPSDR                            | f = 1 MHz                                             |           |      | 10        |       |  |

| C <sub>IN</sub>     | Input capacitance SubLVDS                          | f = 1 MHz                                             |           |      | 20        | pF    |  |

| C <sub>OUT</sub>    | Output capacitance                                 | f = 1 MHz                                             |           |      | 10        | pF    |  |

| C <sub>RESET</sub>  | Reset group capacitance                            | $f = 1 \text{ MHz}; (480 \times 108)$<br>micromirrors | 95        |      | 113       | pF    |  |

- (1) Device electrical characteristics are over *Recommended Operating Conditions* unless otherwise noted.

- (2) All voltage values are with respect to the ground pins (VSS).

- (3) To prevent excess current, the supply voltage delta |VDDI VDD| must be less than specified limit.

- (4) Supply power dissipation based on non-compressed commands and data.

- (5) To prevent excess current, the supply voltage delta |VBIAS VOFFSET| must be less than specified limit.

- (6) Supply power dissipation based on 3 global resets in 200 μs.

- (7) The following power supplies are all required to operate the DMD: VSS, VDD, VDDI, VOFFSET, VBIAS, VRESET.

- 8) LPSDR specifications are for pins LS CLK and LS WDATA.

- (9) Low-speed interface is LPSDR and adheres to the Electrical Characteristics and AC/DC Operating Conditions table in JEDEC Standard No. 209B, Low-Power Double Data Rate (LPDDR) JESD209B.

- (10) LPSDR specification is for pin LS\_RDATA.

# 6.7 Timing Requirements

Device electrical characteristics are over Recommended Operating Conditions unless otherwise noted.

|                                      |                                         | , ,                                                           | MIN  | NOM  | MAX  | UNIT |

|--------------------------------------|-----------------------------------------|---------------------------------------------------------------|------|------|------|------|

| LPSDR                                |                                         |                                                               |      |      |      |      |

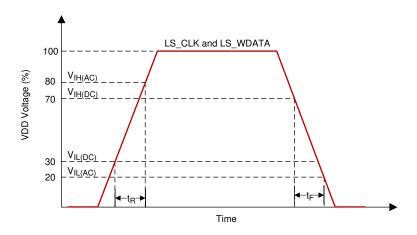

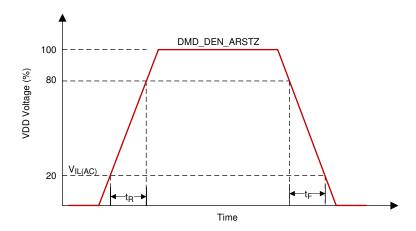

| t <sub>R</sub>                       | Rise slew rate <sup>(1)</sup>           | (30% to 80%) × VDD, ⊠ 6-3                                     | 1    |      | 3    | V/ns |

| t <sub>F</sub>                       | Fall slew rate <sup>(1)</sup>           | (70% to 20%) × VDD, ⊠ 6-3                                     | 1    |      | 3    | V/ns |

| t <sub>R</sub>                       | Rise slew rate <sup>(2)</sup>           | (20% to 80%) × VDD, ⊠ 6-3                                     | 0.25 |      |      | V/ns |

| t <sub>F</sub>                       | Fall slew rate <sup>(2)</sup>           | (80% to 20%) × VDD, ⊠ 6-3                                     | 0.25 |      |      | V/ns |

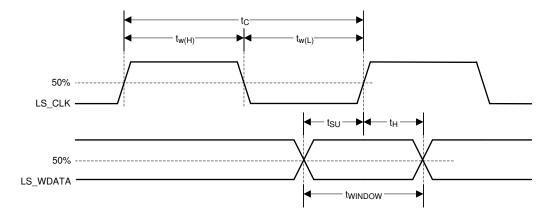

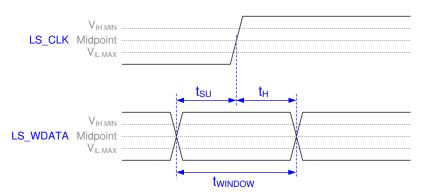

| t <sub>C</sub>                       | Cycle time LS_CLK,                      | ⊠ 6-2                                                         | 7.7  | 8.3  |      | ns   |

| t <sub>W(H)</sub>                    | Pulse duration LS_CLK high              | 50% to 50% reference points, ⊠ 6-2                            | 3.1  |      |      | ns   |

| t <sub>W(L)</sub>                    | Pulse duration LS_CLK low               | 50% to 50% reference points, ⊠ 6-2                            | 3.1  |      |      | ns   |

| t <sub>SU</sub>                      | Setup time                              | LS_WDATA valid before LS_CLK ↑, 図 6-2                         | 1.5  |      |      | ns   |

| t <sub>H</sub>                       | Hold time                               | LS_WDATA valid after LS_CLK ↑, 図 6-2                          | 1.5  |      |      | ns   |

| t <sub>WINDOW</sub>                  | Window time <sup>(1) (3)</sup>          | Setup time + Hold time, ⊠ 6-2                                 | 3.0  |      |      | ns   |

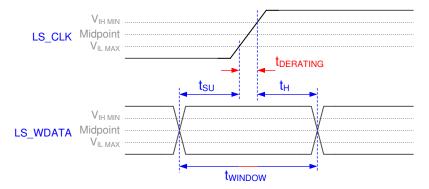

| t <sub>DERATING</sub>                | Window time derating <sup>(1) (3)</sup> | For each 0.25 V/ns reduction in slew rate below 1 V/ns, ⊠ 6-6 |      | 0.35 |      | ns   |

| SubLVDS                              |                                         |                                                               |      |      |      |      |

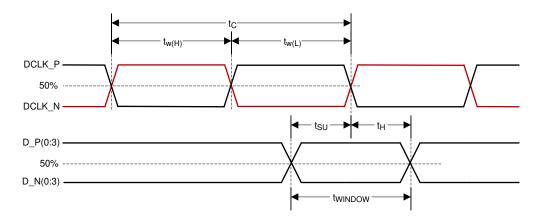

| t <sub>R</sub>                       | Rise slew rate                          | 20% to 80% reference points, ⊠ 6-5                            | 0.7  | 1    |      | V/ns |

| t <sub>F</sub>                       | Fall slew rate                          | 80% to 20% reference points, ⊠ 6-5                            | 0.7  | 1    |      | V/ns |

| t <sub>C</sub>                       | Cycle time LS_CLK,                      | ☑ 6-7                                                         | 1.61 | 1.67 |      | ns   |

| t <sub>W(H)</sub>                    | Pulse duration DCLK high                | 50% to 50% reference points, ⊠ 6-7                            | 0.71 |      |      | ns   |

| t <sub>W(L)</sub>                    | Pulse duration DCLK low                 | 50% to 50% reference points, ⊠ 6-7                            | 0.71 |      |      | ns   |

| t <sub>SU</sub>                      | Setup time                              | D(0:3) valid before<br>DCLK ↑ or DCLK ↓ , ⊠ 6-7               |      |      |      |      |

| t <sub>H</sub>                       | Hold time                               | D(0:3) valid after<br>DCLK ↑ or DCLK ↓ , ⊠ 6-7                |      |      |      |      |

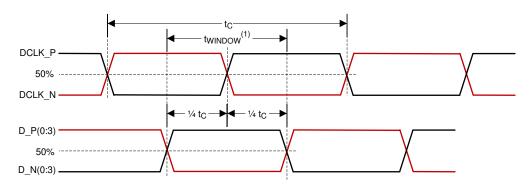

| t <sub>WINDOW</sub>                  | Window time                             | Setup time + Hold time, ⊠ 6-7, ⊠ 6-8                          | 3.0  |      |      | ns   |

| t <sub>LVDS</sub> -<br>ENABLE+REFGEN | Power-up receiver <sup>(4)</sup>        |                                                               |      |      | 2000 | ns   |

- (1) Specification is for LS CLK and LS WDATA pins. Refer to LPSDR input rise slew rate and fall slew rate in 🗵 6-3.

- (2) Specification is for DMD\_DEN\_ARSTZ pin. Refer to LPSDR input rise and fall slew rate in 🗵 6-3.

- (3) Window time derating example: 0.5-V/ns slew rate increases the window time by 0.7 ns, from 3 to 3.7 ns.

- (4) Specification is for SubLVDS receiver time only and does not take into account commanding and latency after commanding.

English Data Sheet: DLPS180

A. Low-speed interface is LPSDR and adheres to the *Electrical Characteristics* and AC/DC Operating Conditions table in JEDEC Standard No. 209B, *Low Power Double Data Rate (LPDDR)* JESD209B.

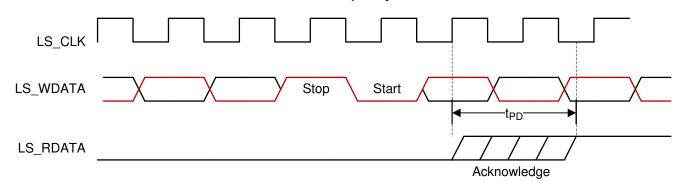

図 6-2. LPSDR Switching Parameters

図 6-3. LPSDR Input Slew Rate

図 6-4. LPSDR Input Slew Rate

図 6-5. SubLVDS Input Rise and Fall Slew Rate

図 6-6. Window Time Derating Concept

図 6-7. SubLVDS Switching Parameters

(1) High-speed training scan window

Note: Refer to High-Speed Interface for details.

図 6-8. High-Speed Training Scan Window

図 6-9. SubLVDS Voltage Parameters

- A.  $V_{SubLVDS(max)} = V_{CM(max)} + | \frac{1}{2} \times V_{ID(max)} |$

- B.  $V_{SubLVDS(min)} = V_{CM(min)} | \frac{1}{2} \times V_{ID(max)} |$

#### 図 6-10. SubLVDS Waveform Parameters

図 6-11. SubLVDS Equivalent Input Circuit

図 6-12. LPSDR Input Hysteresis

図 6-13. LPSDR Read Out

# **Data Sheet Timing Reference Point**

A. See *Timing* for more information.

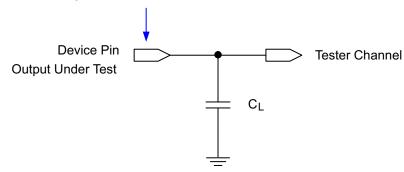

図 6-14. Test Load Circuit for Output Propagation Measurement

# **6.8 Switching Characteristics**

Over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                 | PARAMETER                                                                              | TEST CONDITIONS        | MIN | TYP MA | X UNIT |

|-----------------|----------------------------------------------------------------------------------------|------------------------|-----|--------|--------|

| t <sub>PD</sub> | Output propagation, Clock to Q, rising edge of LS_CLK input to LS_RDATA output. ☑ 6-13 | C <sub>L</sub> = 45 pF |     | 1      | 5 ns   |

|                 | Slew rate, LS_RDATA                                                                    |                        | 0.5 |        | V/ns   |

|                 | Output duty cycle distortion, LS_RDATA                                                 |                        | 40% | 609    | 6      |

Product Folder Links: DLP2010LC

<sup>(1)</sup> Device electrical characteristics are over セクション 6.4 unless otherwise noted.

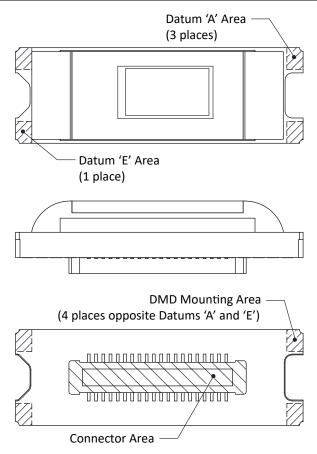

# 6.9 System Mounting Interface Loads

| PARAMETER                            |                                                                   | MIN | NOM | MAX | UNIT |

|--------------------------------------|-------------------------------------------------------------------|-----|-----|-----|------|

| Maximum system mounting              | Connector area (see 🗵 6-15)                                       |     |     | 45  | N    |

| interface load to be applied to the: | DMD mounting area uniformly distributed over 4 areas (see ☑ 6-15) |     |     | 100 | N    |

図 6-15. System Interface Loads

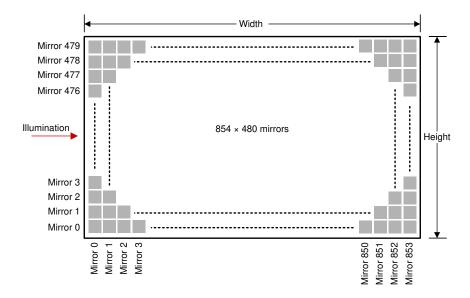

# **6.10 Physical Characteristics of the Micromirror Array**

|                                 | PARAMETER                                                | VALUE  | UNIT              |

|---------------------------------|----------------------------------------------------------|--------|-------------------|

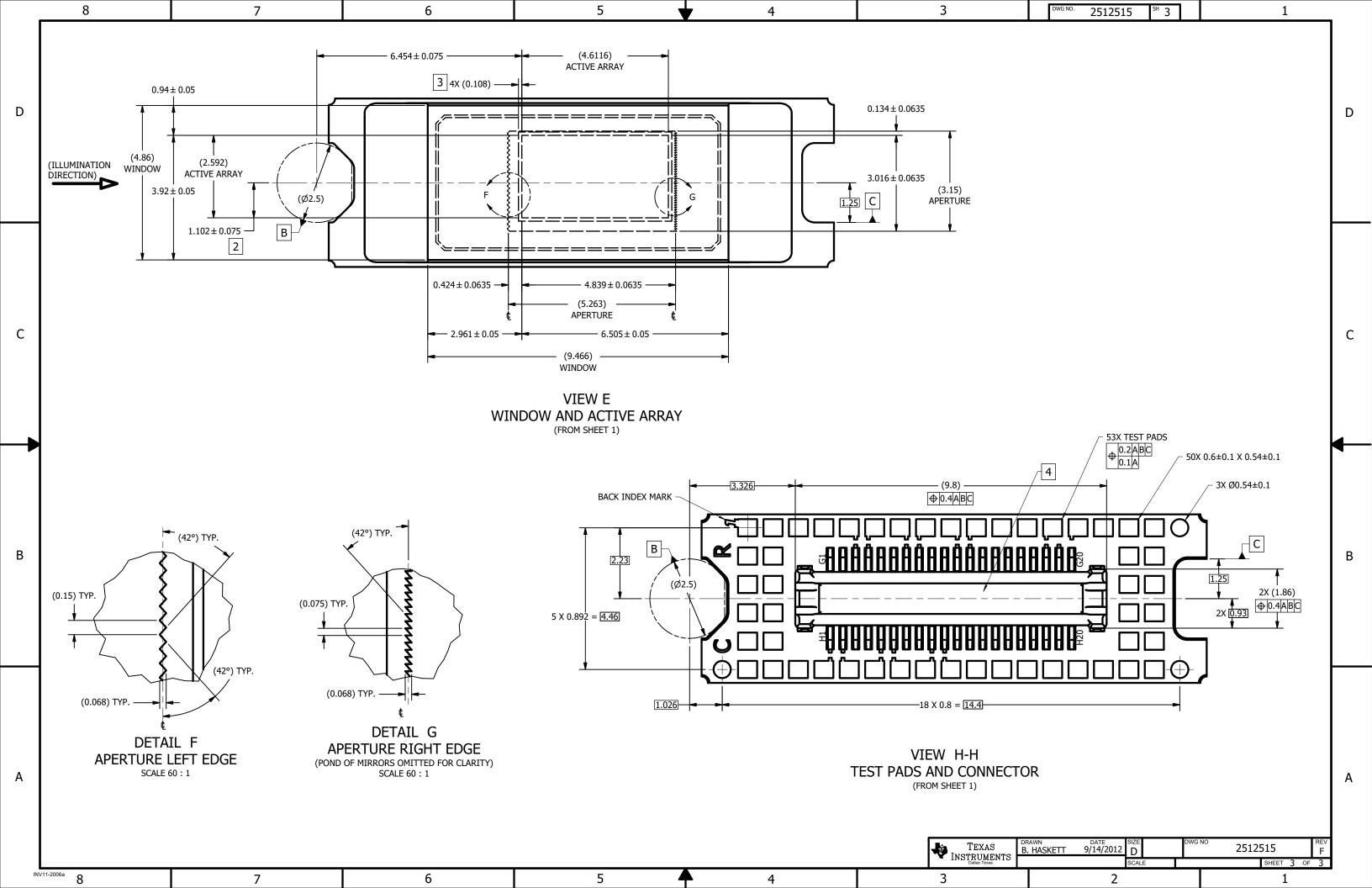

| Number of active columns        | See ☑ 6-16                                               | 854    | micromirrors      |

| Number of active rows           | See ☑ 6-16                                               | 480    | micromirrors      |

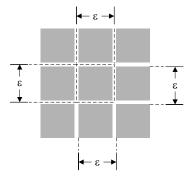

| Micromirror (pixel) pitch       | See ⊠ 6-17                                               | 5.4    | μm                |

| Micromirror active array width  | Micromirror pitch × number of active columns; see ☑ 6-16 | 4.6116 | mm                |

| Micromirror active array height | Micromirror pitch × number of active rows; see ☒ 6-16    | 2.592  | mm                |

| Micromirror active border       | Pond of micromirror (POM) <sup>(1)</sup>                 | 20     | micromirrors/side |

(1) The structure and qualities of the border around the active array includes a band of partially functional micromirrors called the POM. These micromirrors are structurally and/or electrically prevented from tilting toward the bright or ON state, but still require an electrical bias to tilt toward OFF.

図 6-16. Micromirror Array Physical Characteristics

図 6-17. Mirror (Pixel) Pitch

### **6.11 Micromirror Array Optical Characteristics**

| PARA                                      | METER                                 | TEST CONDITIONS                 | MIN  | NOM | MAX | UNIT         |  |

|-------------------------------------------|---------------------------------------|---------------------------------|------|-----|-----|--------------|--|

| Micromirror tilt angle                    |                                       | DMD landed state <sup>(1)</sup> |      | 17  |     | degrees      |  |

| Micromirror tilt angle to                 | lerance <sup>(2) (3) (4) (5)</sup>    |                                 | -1.4 |     | 1.4 | degrees      |  |

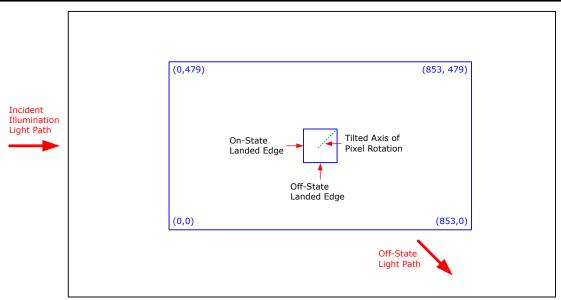

| Micromirror tilt direction                | .(6) (7)                              | Landed ON state                 |      | 180 |     | 4            |  |

| Micromirror tilt direction                | (0)                                   | Landed OFF state                |      | 270 |     | degrees      |  |

| Micromirror crossover t                   | ime <sup>(8)</sup>                    | Typical Performance             |      | 1   | 3   |              |  |

| Micromirror switching time <sup>(9)</sup> |                                       | Typical Performance             | 10   |     |     | μs           |  |

|                                           | Bright pixel(s) in active area (11)   | Gray 10 Screen (12)             |      |     | 0   |              |  |

|                                           | Bright pixel(s) in the POM (13)       | Gray 10 Screen (12)             |      |     | 1   |              |  |

| Image performance <sup>(10)</sup>         | Dark pixel(s) in the active area (14) | White Screen                    |      |     | 4   | micromirrors |  |

|                                           | Adjacent pixel(s) (15)                | Any Screen                      |      |     | 0   |              |  |

|                                           | Unstable pixel(s) in active area (16) | Any Screen                      |      |     | 0   |              |  |

- (1) Measured relative to the plane formed by the overall micromirror array.

- (2) Additional variation exists between the micromirror array and the package datums.

- (3) Represents the landed tilt angle variation relative to the nominal landed tilt angle.

- (4) Represents the variation that can occur between any two individual micromirrors, located on the same device or located on different devices.

- (5) For some applications, it is critical to account for the micromirror tilt angle variation in the overall system optical design. With some system optical designs, the micromirror tilt angle variation within a device may result in perceivable non-uniformities in the light field reflected from the micromirror array. With some system optical designs, the micromirror tilt angle variation between devices may result in colorimetry variations, system efficiency variations or system contrast variations.

- (6) When the micromirror array is landed (not parked), the tilt direction of each individual micromirror is dictated by the binary contents of the CMOS memory cell associated with each individual micromirror. A binary value of 1 results in a micromirror landing in the ON state direction. A binary value of 0 results in a micromirror landing in the OFF state direction. See 🗵 6-18

- (7) Micromirror tilt direction is measured as in a typical polar coordinate system: Measuring counter-clockwise from a 0° reference which is aligned with the +X Cartesian axis.

- (8) The time required for a micromirror to nominally transition from one landed state to the opposite landed state.

- (9) The minimum time between successive transitions of a micromirror.

- (10) Conditions of Acceptance: All DMD image quality returns will be evaluated using the following projected image test conditions:

Test set degamma shall be linear

Test set brightness and contrast shall be set to nominal

The diagonal size of the projected image shall be a minimum of 20 inches

The projections screen shall be 1X gain

The projected image shall be inspected from a 38 inch minimum viewing distance

The image shall be in focus during all image quality tests

- (11) Bright pixel definition: A single pixel or mirror that is stuck in the ON position and is visibly brighter than the surrounding pixels

- (12) Gray 10 screen definition: All areas of the screen are colored with the following settings:

Red = 10/255

Green = 10/255

Blue = 10/255

- (13) POM definition: Rectangular border of off-state mirrors surrounding the active area

- (14) Dark pixel definition: A single pixel or mirror that is stuck in the OFF position and is visibly darker than the surrounding pixels

- (15) Adjacent pixel definition: Two or more stuck pixels sharing a common border or common point, also referred to as a cluster

- (16) Unstable pixel definition: A single pixel or mirror that does not operate in sequence with parameters loaded into memory. The unstable pixel appears to be flickering asynchronously with the image

English Data Sheet: DLPS180

図 6-18. Landed Pixel Orientation and Tilt

#### 6.12 Window Characteristics

| PARAMETER <sup>(1)</sup>                                          |                                                                                         |     | NOM              | MAX     | UNIT |

|-------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-----|------------------|---------|------|

| Window material designation                                       |                                                                                         |     | Corning Eagle XG |         |      |

| Window refractive index                                           | at wavelength 546.1 nm                                                                  |     | 1.5119           |         |      |

| Window aperture <sup>(2)</sup>                                    |                                                                                         |     |                  | See (2) |      |

| Illumination overfill <sup>(3)</sup>                              |                                                                                         |     |                  | See (3) |      |

| Window transmittance, single-pass through both surfaces and glass | Minimum within the wavelength range 420 to 680 nm. Applies to all angles 0° to 30° AOI. | 97% |                  |         |      |

| Window Transmittance, single-pass through both surfaces and glass | Average over the wavelength range 420 to 680 nm. Applies to all angles 30° to 45° AOI.  | 97% |                  |         |      |

- (1) See Optical Interface and System Image Quality Considerations for more information.

- (2) See the package mechanical characteristics for details regarding the size and location of the window aperture.

- The active area of the DLP2010LC device is surrounded by an aperture on the inside of the DMD window surface that masks structures of the DMD device assembly from normal view. The aperture is sized to anticipate several optical conditions. Overfill light illuminating the area outside the active array can scatter and create adverse effects to the performance of an end application using the DMD. The illumination optical system should be designed to limit light flux incident outside the active array to less than 10% of the average flux level in the active area. Depending on the particular system's optical architecture and assembly tolerances, the amount of overfill light on the outside of the active array may cause system performance degradation.

#### 6.13 Chipset Component Usage Specification

The DLP2010LC is a component of one or more TI DLP® chipsets. Reliable function and operation of the DLP2010LC requires that it be used in conjunction with the other components of the applicable DLP chipset, including those components that contain or implement TI DMD control technology. TI DMD control technology is the TI technology and devices for operating or controlling a DLP DMD.

注

TI assumes no responsibility for image quality artifacts or DMD failures caused by optical system operating conditions exceeding limits described previously.

#### 6.14 Software Requirements

注意

The DLP2010LC DMD has mandatory software requirements. Refer to *Software Requirements for TI DLP®Pico™ TRP Digital Micromirror Devices* application report for additional information. Failure to use the specified software will result in failure at power up.

Product Folder Links: DLP2010LC

# 7 Detailed Description

## 7.1 Overview

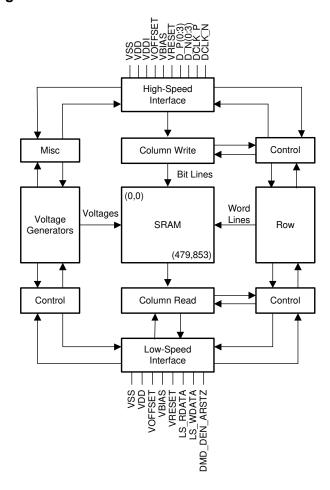

The DLP2010LC is a 0.2 inch diagonal spatial light modulator of aluminum micromirrors. Pixel array size is 854 columns by 480 rows in a square grid pixel arrangement. The electrical interface is sub low voltage differential signaling (SubLVDS) data.

This DMD is part of the chipset that is composed of the DMD, DLPC3470 display and light controller and the DLPA200x/DLPA3000 PMIC and LED driver. To ensure reliable operation, the DMD must always be used with the DLPC3470 display and light controller and the DLPA200x/DLPA3000 PMIC and LED driver.

## 7.2 Functional Block Diagram

Product Folder Links: DLP2010LC

Details omitted for clarity.

#### 7.3 Feature Description

## 7.3.1 Power Interface

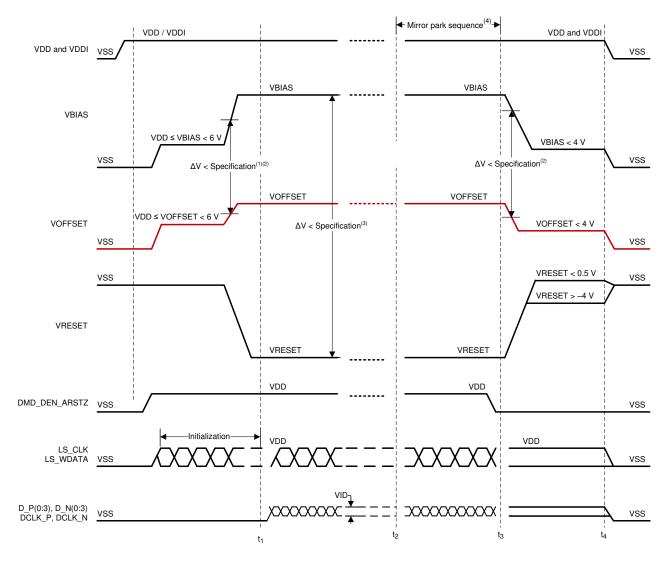

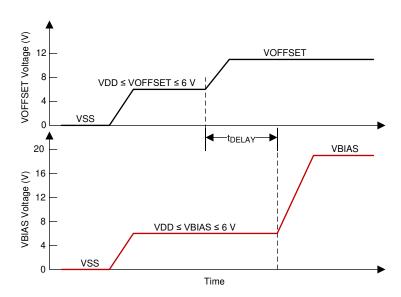

The power management component DLPA200x/DLPA3000, contains three 3 regulated DC supplies for the DMD reset circuitry: VBIAS, VRESET and VOFFSET, as well as the two regulated DC supplies for the DLPC3470 controller.

#### 7.3.2 Low-Speed Interface

The low speed interface handles instructions that configure the DMD and control reset operation. LS\_CLK is the low–speed clock, and LS\_WDATA is the low speed data input.

#### 7.3.3 High-Speed Interface

The purpose of the high-speed interface is to transfer pixel data rapidly and efficiently, making use of high speed DDR transfer and compression techniques to save power and time. The high-speed interface uses differential SubLVDS receivers for inputs, with a dedicated clock.

#### **7.3.4 Timing**

The data sheet provides timing test results at the device pin. For output timing analysis, the tester pin electronics and its transmission line effects must be considered. Test Load Circuit for Output Propagation Measurement shows an equivalent test load circuit for the output under test. Timing reference loads are not intended as a precise representation of any particular system environment or depiction of the actual load presented by a production test. TI recommends that system designers use IBIS or other simulation tools to correlate the timing reference load to a system environment. The load capacitance value stated is intended for characterization and measurement of AC timing signals only. This load capacitance value does not indicate the maximum load the device is capable of driving.

#### 7.4 Device Functional Modes

DMD functional modes are controlled by the DLPC3470 controller. See the DLPC3470 controller data sheet or contact a TI applications engineer.

## 7.5 Optical Interface and System Image Quality Considerations

注

TI assumes no responsibility for image quality artifacts or DMD failures caused by optical system operating conditions exceeding limits described previously.

#### 7.5.1 Optical Interface and System Image Quality

TI assumes no responsibility for end-equipment optical performance. Achieving the desired end-equipment optical performance involves making trade-offs between numerous component and system design parameters. Optimizing system optical performance and image quality strongly relate to optical system design parameter trades. Although it is not possible to anticipate every conceivable application, projector image quality and optical performance is contingent on compliance to the optical system operating conditions described in the following sections.

# 7.5.1.1 Numerical Aperture and Stray Light Control

The angle defined by the numerical aperture of the illumination and projection optics at the DMD optical area is typically the same. Ensure this angle does not exceed the nominal device micromirror tilt angle unless appropriate apertures are added in the illumination or projection pupils to block out flat-state and stray light from the projection lens. The micromirror tilt angle defines DMD capability to separate the "ON" optical path from any other light path, including undesirable flat-state specular reflections from the DMD window, DMD border structures, or other system surfaces near the DMD such as prism or lens surfaces. If the numerical aperture exceeds the micromirror tilt angle, or if the projection numerical aperture angle is more than two degrees larger than the illumination numerical aperture angle (and vice versa), contrast degradation and objectionable artifacts in the display border and/or active area may occur.

## 7.5.1.2 Pupil Match

The optical and image quality specifications assume that the exit pupil of the illumination optics is nominally centered within 2° of the entrance pupil of the projection optics. Misalignment of pupils can create objectionable artifacts in the display border and/or active area. These artifacts may require additional system apertures to control, especially if the numerical aperture of the system exceeds the pixel tilt angle.

#### 7.5.1.3 Illumination Overfill

The active area of the device is surrounded by an aperture on the inside DMD window surface that masks structures of the DMD chip assembly from normal view, and is sized to anticipate several optical operating conditions. Overfill light illuminating the window aperture can create artifacts from the edge of the window aperture opening and other surface anomalies that may be visible on the screen. Be sure to design an illumination optical system that limits light flux incident anywhere on the window aperture from exceeding approximately 10% of the average flux level in the active area. Depending on the particular optical architecture, overfill light may require further reduction below the suggested 10% level in order to be acceptable.

# 7.6 Micromirror Array Temperature Calculation

図 7-1. DMD Thermal Test Points

Micromirror array temperature cannot be measured directly, therefore it must be computed analytically from measurement points on the outside of the package, the package thermal resistance, the electrical power, and the illumination heat load. The relationship between array temperature and the reference ceramic temperature (thermal test TP1 in  $\boxtimes$  7-1) is provided by the following equations:

$$T_{ARRAY} = T_{CERAMIC} + (Q_{ARRAY} \times R_{ARRAY-TO-CERAMIC})$$

$$Q_{ARRAY} = Q_{ELECTRICAL} + Q_{ILLUMINATION}$$

#### where

- T<sub>ARRAY</sub> = Computed array temperature (°C)

- T<sub>CERAMIC</sub> = Measured ceramic temperature (°C) (TP1 location)

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

- R<sub>ARRAY-TO-CERAMIC</sub> = Thermal resistance of package specified in セクション 6.5 from array to ceramic TP1 (°C/Watt)

- Q<sub>ARRAY</sub> = Total DMD power on the array (W) (electrical + absorbed)

- Q<sub>ELECTRICAL</sub> = Nominal electrical power (W)

- Q<sub>INCIDENT</sub> = Incident illumination optical power (W)

- Q<sub>ILLUMINATION</sub> = (DMD average thermal absorptivity × Q<sub>INCIDENT</sub>) (W)

- DMD average thermal absorptivity = 0.4

The electrical power dissipation of the DMD is variable and depends on the voltages, data rates and operating frequencies. A nominal electrical power dissipation to use when calculating array temperature is 0.07 Watts. The absorbed power from the illumination source is variable and depends on the operating state of the micromirrors and the intensity of the light source. The equations shown above are valid for a single chip or multichip DMD system. It assumes an illumination distribution of 83.7% on the active array, and 16.3% on the array border.

The sample calculation for a typical projection application is as follows:

```

\begin{aligned} &Q_{\text{INCIDENT}} = 2.0 \text{ W (measured)} \\ &T_{\text{CERAMIC}} = 55.0^{\circ}\text{C (measured)} \\ &Q_{\text{ELECTRICAL}} = 0.07 \text{ W} \\ &Q_{\text{ARRAY}} = 0.07 \text{ W} + (0.40 \times 2.0 \text{ W}) = 0.87 \text{ W} \\ &T_{\text{ARRAY}} = 55.0^{\circ}\text{C} + (0.87 \text{ W} \times 7.9^{\circ}\text{C/W}) = 61.9^{\circ}\text{C} \end{aligned}

```

# 7.7 Micromirror Power Density Calculation

The calculation of the optical power density of the illumination on the DMD in the different wavelength bands uses the total measured optical power on the DMD, percent illumination overfill, area of the active array, and ratio of the spectrum in the wavelength band of interest to the total spectral optical power.

Product Folder Links: DLP2010LC

- ILL<sub>UV</sub> =  $[OP_{UV-RATIO} \times Q_{INCIDENT}] \times 1000 \div A_{ILL} (mW/cm^2)$

- ILL<sub>VIS</sub> = [OP<sub>VIS-RATIO</sub> × Q<sub>INCIDENT</sub>] ÷ A<sub>ILL</sub> (W/cm<sup>2</sup>)

- ILL<sub>IR</sub> = [OP<sub>IR-RATIO</sub> × Q<sub>INCIDENT</sub>] × 1000 ÷ A<sub>ILL</sub> (mW/cm<sup>2</sup>)