Technical documentation

DLP4500NIR

JAJSGU1B – JANUARY 2019 – REVISED MAY 2022

## DLP4500NIR 0.45 WXGA 近赤外線 DMD

### 1 特長

**TEXAS**

INSTRUMENTS

- 0.45 インチ対角マイクロミラー・アレイ

- 912×1140 解像度のアレイ (100 万個超のマイ クロミラー)

- ダイヤモンド型のアレイ方向により側面照明を サポートし、光学設計を簡素化かつ効率化

- WXGA 解像度の表示が可能

- 7.6μm のマイクロミラー・ピッチ

- ±12°の傾斜角

- 5µs のマイクロミラー・クロスオーバー時間 (公称値)

- NIR 光の高効率なステアリング

- ウィンドウ伝送効率 96% (公称値) (700 ~

2000nm、2 つのウィンドウ表面経由のシング ル・パス)

- ウィンドウ伝送効率 90% (公称値) (2000 ~

2500nm、2 つのウィンドウ表面経由のシング ル・パス)

- 偏光に依存しないアルミニウム製のマイクロミ ラー

- アレイの充填率 92% (公称値)

- 専用の DLPC350 コントローラによる信頼性の高 い動作

- 最大 4kHz のバイナリ・パターン・レート

- パターン・シーケンス・モードによりアレイ内 の各マイクロミラーを制御

- マイクロミラー・ドライバ回路を内蔵

- 9.1mm × 20.7mm で携帯機器に好適

- 拡張サーマル・インターフェイス付き FQD パッケージ

### 2 アプリケーション

- 分光計 (化学分析)

- プロセス・アナライザ

- 実験機器

- 専用アナライザ

- 圧縮センシング (シングル・ピクセル NIR カメラ)

- ・ 3D バイオメトリクス

- ・ マシン・ビジョン

- 赤外線シーン投影

- レーザー・マーキング

- 光学チョッパー

- ◇ 顕微鏡 ◇ 光学ネットワーク機器

- 元子ネットワー

#### 3 概要

DLP4500NIR デジタル・マイクロミラー・デバイス (DMD) は空間光変調器 (SLM) として動作し、近赤外 光 (NIR) をステアリングして高速度、高精度、高効率 でパターンを生成します。DLP4500NIR DMD は小さ な外形で高解像度を実現し、多くの場合、単一要素検 出器と組み合わせることで、高価な InGaAs アレイを 基礎とする検出器の設計の代替品となり、高性能でコ スト効率の優れた携帯型ソリューションを実現できま す。

| 部品番号       | パッケージ <sup>(1)</sup> | サーマル・インター<br>フェイス領域 |

|------------|----------------------|---------------------|

| DLP4500NIR | LCCC (98)            | 7.00mm × 7.00mm     |

(1) 利用可能なパッケージについては、このデータシートの末尾 にある注文情報を参照してください。

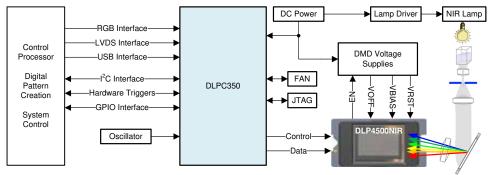

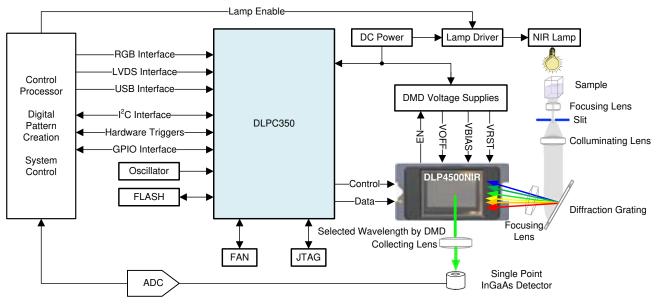

アプリケーション概略

★ 英語版の TI 製品についての情報を翻訳したこの資料は、製品の概要を確認する目的で便宜的に提供しているものです。該当する正式な英語版の最新情報 は、www.ti.com で閲覧でき、その内容が常に優先されます。TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計など の前には、必ず最新版の英語版をご参照くださいますようお願いいたします。

### **Table of Contents**

| 1 | 特長                                             | 1   |

|---|------------------------------------------------|-----|

| 2 | アプリケーション                                       | 1   |

| 3 | 概要                                             | 1   |

|   | Revision History                               |     |

|   | Chipset Component Usage Specification          |     |

|   | Pin Configuration and Functions                |     |

| 7 | Specifications                                 | 8   |

|   | 7.1 Absolute Maximum Ratings                   | 8   |

|   | 7.2 Storage Conditions                         | 8   |

|   | 7.3 ESD Ratings                                | 9   |

|   | 7.4 Recommended Operating Conditions           | 9   |

|   | 7.5 Thermal Information                        |     |

|   | 7.6 Electrical Characteristics                 |     |

|   | 7.7 Timing Requirements                        |     |

|   | 7.8 System Mounting Interface Loads            |     |

|   | 7.9 Micromirror Array Physical Characteristics |     |

|   | 7.10 Micromirror Array Optical Characteristics |     |

|   | 7.11 Typical Characteristics                   |     |

| 8 | Detailed Description                           |     |

|   | 8.1 Overview                                   |     |

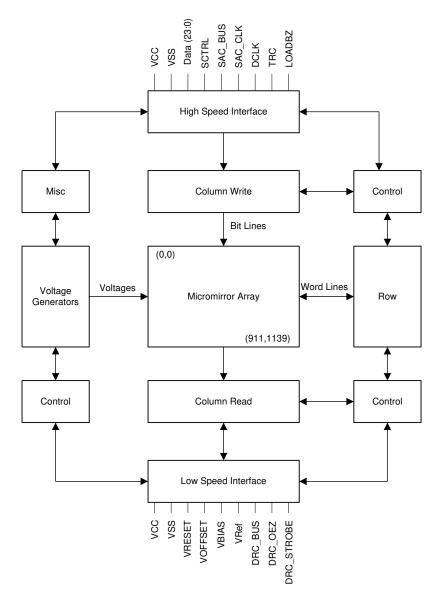

|   | 8.2 Functional Block Diagram                   |     |

|   | 8.3 Feature Description                        |     |

|   | 8.4 Device Functional Modes                    | .21 |

| 8.5 Micromirror Array Temperature Calculation       | 21                |

|-----------------------------------------------------|-------------------|

| 8.6 Micromirror Landed-on/Landed-Off Duty Cycle     | 23                |

| 9 Applications and Implementation                   | 26                |

| 9.1 Application Information                         | 26                |

| 9.2 Typical Application                             | 26                |

| 10 Power Supply Recommendations                     |                   |

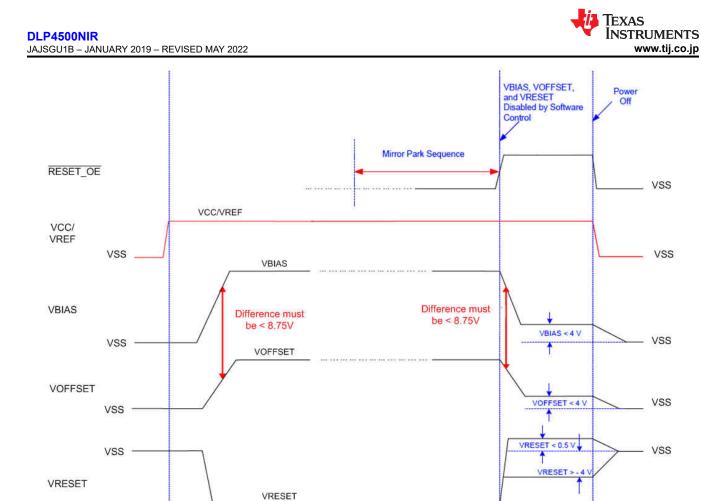

| 10.1 Power Supply Sequencing Requirements           | 31                |

| 10.2 DMD Power Supply Power-Up Procedure            | 31                |

| 10.3 DMD Power Supply Power-Down Procedure          | 31                |

| 11 Layout                                           |                   |

| 11.1 Layout Guidelines                              |                   |

| 11.2 Layout Example                                 | 38                |

| 12 Device and Documentation Support                 |                   |

| 12.1 Device Support                                 | 42                |

| 12.2 Documentation Support                          |                   |

| 12.3 Receiving Notification of Documentation Update | s <mark>43</mark> |

| 12.4 サポート・リソース                                      | 43                |

| 12.5 Trademarks                                     | 43                |

| 12.6 Electrostatic Discharge Caution                | 43                |

| 12.7 Glossary                                       | 43                |

| 13 Mechanical, Packaging, and Orderable             |                   |

| Information                                         | 43                |

|                                                     |                   |

**4 Revision History** 資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| С | hanges from Revision A (December 2021) to Revision B (May 2022)       | Page |

|---|-----------------------------------------------------------------------|------|

| • | Updated Absolute Maximum Ratings disclosure to the latest TI standard |      |

| • | Updated Micromirror Array Optical Characteristics                     |      |

|   | Added Third-Party Products Disclaimer                                 |      |

|   | ·                                                                     |      |

| C | hanges from Revision * (January 2019) to Revision A (December 2021) | Page |

|---|---------------------------------------------------------------------|------|

| • | 文書全体にわたって表、図、相互参照の採番方法を更新                                           | 1    |

| • | Updated  T <sub>DELTA</sub>   MAX from 30°C to 15°C                 | 9    |

### **5** Chipset Component Usage Specification

Note

TI assumes no responsibility for image quality artifacts or DMD failures caused by optical system operating conditions exceeding limits described previously.

The DLP4500NIR is a component of one or more DLP<sup>®</sup> chipsets. Reliable function and operation of the DLP4500NIR requires that it be used in conjunction with the other components of the applicable DLP chipset, including those components that contain or implement TI DMD control technology. TI DMD control technology is the TI technology and devices for operating or controlling a DLP DMD.

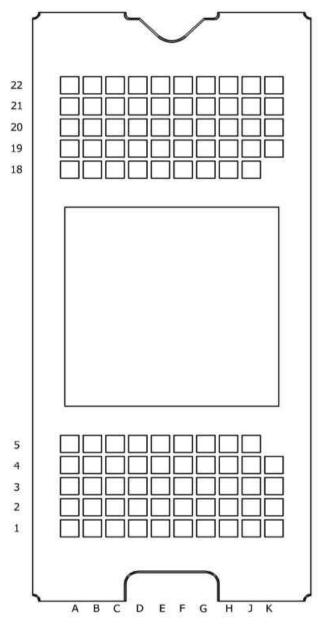

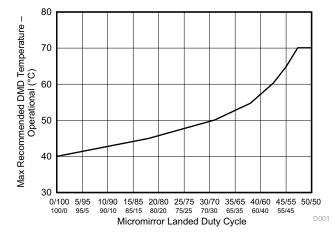

### **6** Pin Configuration and Functions

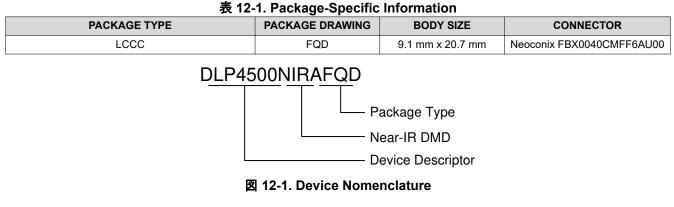

|                 |        |        |        | 表 6-1. Connec            | tor Pins for F | QD                                                                            |                            |

|-----------------|--------|--------|--------|--------------------------|----------------|-------------------------------------------------------------------------------|----------------------------|

| PIN             |        | TYPE   | SIGNAL | DATA RATE <sup>(1)</sup> | INTERNAL       | DESCRIPTION                                                                   | PACKAGE NET                |

| NAME            | NO.    | 1111   | SIGNAL |                          | TERMINATION    | DESCRIPTION                                                                   | LENGTH (mm) <sup>(2)</sup> |

| DATA INPUTS     |        |        |        |                          |                | ·                                                                             |                            |

| DATA(0)         | A1     | Input  | LVCMOS | DDR                      | none           | Input data bus, bit 0, LSB                                                    | 3.77                       |

| DATA(1)         | A2     | Input  | LVCMOS | DDR                      | none           | Input data bus, bit 1                                                         | 3.77                       |

| DATA(2)         | A3     | Input  | LVCMOS | DDR                      | none           | Input data bus, bit 2                                                         | 3.73                       |

| DATA(3)         | A4     | Input  | LVCMOS | DDR                      | none           | Input data bus, bit 3                                                         | 3.74                       |

| DATA(4)         | B1     | Input  | LVCMOS | DDR                      | none           | Input data bus, bit 4                                                         | 3.79                       |

| DATA(5)         | B3     | Input  | LVCMOS | DDR                      | none           | Input data bus, bit 5                                                         | 3.75                       |

| DATA(6)         | C1     | Input  | LVCMOS | DDR                      | none           | Input data bus, bit 6                                                         | 3.72                       |

| DATA(7)         | C3     | Input  | LVCMOS | DDR                      | none           | Input data bus, bit 7                                                         | 3.75                       |

| DATA(8)         | C4     | Input  | LVCMOS | DDR                      | none           | Input data bus, bit 8                                                         | 3.78                       |

| DATA(9)         | D1     | Input  | LVCMOS | DDR                      | none           | Input data bus, bit 9                                                         | 3.75                       |

| DATA(10)        | D4     | Input  | LVCMOS | DDR                      | none           | Input data bus, bit 10                                                        | 3.77                       |

| DATA(11)        | E1     | Input  | LVCMOS | DDR                      | none           | Input data bus, bit 11                                                        | 3.75                       |

| DATA(12)        | E4     | Input  | LVCMOS | DDR                      | none           | Input data bus, bit 12                                                        | 3.71                       |

| DATA(13)        | F1     | Input  | LVCMOS | DDR                      | none           | Input data bus, bit 13                                                        | 3.76                       |

| DATA(14)        | F3     | Input  | LVCMOS | DDR                      | none           | Input data bus, bit 14                                                        | 3.73                       |

| DATA(15)        | G1     | Input  | LVCMOS | DDR                      | none           | Input data bus, bit 15                                                        | 3.72                       |

| DATA(16)        | G2     | Input  | LVCMOS | DDR                      | none           | Input data bus, bit 16                                                        | 3.77                       |

| DATA(17)        | G4     | Input  | LVCMOS | DDR                      | none           | Input data bus, bit 17                                                        | 3.73                       |

| DATA(18)        | H1     | Input  | LVCMOS | DDR                      | none           | Input data bus, bit 18                                                        | 3.74                       |

| DATA(19)        | H2     | Input  | LVCMOS | DDR                      | none           | Input data bus, bit 19                                                        | 3.76                       |

| DATA(20)        | H4     | Input  | LVCMOS | DDR                      | none           | Input data bus, bit 20                                                        | 3.70                       |

| DATA(21)        | J1     | Input  | LVCMOS | DDR                      | none           | Input data bus, bit 21                                                        | 3.77                       |

| DATA(22)        | J3     | Input  | LVCMOS | DDR                      | none           | Input data bus, bit 22                                                        | 3.76                       |

| DATA(23)        | J4     | Input  | LVCMOS | DDR                      | none           | Input data bus, bit 23, MSB                                                   | 3.77                       |

| DCLK            | K1     | Input  | LVCMOS | DDR                      | none           | Input data bus clock                                                          | 3.74                       |

| DATA CONTROL IN | IPUTS  |        |        |                          |                |                                                                               |                            |

| LOADB           | K2     | Input  | LVCMOS | DDR                      | none           | Parallel-data load enable                                                     | 3.74                       |

| TRC             | K4     | Input  | LVCMOS | DDR                      | none           | Input-data toggle rate control                                                | 4.70                       |

| SCTRL           | K3     | Input  | LVCMOS | DDR                      | none           | Serial-control bus                                                            | 3.75                       |

| SAC_BUS         | C20    | Input  | LVCMOS | _                        | none           | Stepped address-control serial-<br>bus data                                   | 3.77                       |

| SAC_CLK         | C22    | Input  | LVCMOS | _                        | none           | Stepped address-control serial-<br>bus clock                                  | 1.49                       |

| MIRROR RESET CO | ONTROL | INPUTS | 8      |                          |                |                                                                               |                            |

| DRC_BUS         | B21    | Input  | LVCMOS | _                        | none           | DMD reset-control serial bus                                                  | 3.73                       |

| DRC_OE          | A20    | Input  | LVCMOS | _                        | none           | Active-low output enable signal<br>for internal DMD reset driver<br>circuitry | 3.74                       |

| DRC_STROBE      | A22    | Input  | LVCMOS | _                        | none           | Strobe signal for DMD reset-<br>control inputs                                | 3.73                       |

#### DLP4500NIR JAJSGU1B – JANUARY 2019 – REVISED MAY 2022

|                 |     |       | 衣 6-1. | Connector Pil | ns for FQD (co | ontinued)                           |                            |

|-----------------|-----|-------|--------|---------------|----------------|-------------------------------------|----------------------------|

| PIN             |     | TYPE  | SIGNAL | DATA RATE (1) | INTERNAL       | DESCRIPTION                         | PACKAGE NET                |

| NAME            | NO. | 1176  | SIGNAL |               | TERMINATION    | DESCRIPTION                         | LENGTH (mm) <sup>(2)</sup> |

| POWER INPUTS (3 | 3)  |       |        |               | •              | ·                                   |                            |

| VBIAS           | C19 | Power |        |               |                | Mirror-reset bias voltage           |                            |

| VBIAS           | D19 | Power |        |               |                | Will of reset blas voltage          |                            |

| VOFFSET         | A19 | Power |        |               |                | Mirror rooot offect veltage         |                            |

| VOFFSET         | K19 | Power |        |               |                | Mirror-reset offset voltage         |                            |

| VRESET          | E19 | Power |        |               |                | Mirror report voltage               |                            |

| VRESET          | F19 | Power |        |               |                | Mirror-reset voltage                |                            |

| VREF            | B19 | Power |        |               |                | Power supply for LVCMOS             |                            |

| VREF            | J19 | Power |        |               |                | double-data-rate (DDR)<br>interface |                            |

| VCC             | B22 | Power |        |               |                |                                     |                            |

| VCC             | C2  | Power |        |               |                |                                     |                            |

| VCC             | D21 | Power |        |               |                |                                     |                            |

| VCC             | E2  | Power |        |               |                |                                     |                            |

| VCC             | E20 | Power |        |               |                |                                     |                            |

| VCC             | E22 | Power |        |               |                |                                     |                            |

| VCC             | F21 | Power |        |               |                |                                     |                            |

| VCC             | G3  | Power |        |               |                | Dower ourply for LVCMOS logic       |                            |

| VCC             | G19 | Power |        |               |                | Power supply for LVCMOS logic       |                            |

| VCC             | G20 | Power |        |               |                |                                     |                            |

| VCC             | G22 | Power |        |               |                |                                     |                            |

| VCC             | H19 | Power |        |               |                |                                     |                            |

| VCC             | H21 | Power |        |               |                |                                     |                            |

| VCC             | J20 | Power |        |               |                |                                     |                            |

| VCC             | J22 | Power |        |               |                |                                     |                            |

| VCC             | K21 | Power |        |               |                |                                     |                            |

|                 |     |       |        |               |                |                                     |                            |

#### 表 6-1. Connector Pins for FQD (continued)

| PIN  |     | TYPE  |        | DATA RATE <sup>(1)</sup> | INTERNAL    | PACKAGE                        |                            |  |

|------|-----|-------|--------|--------------------------|-------------|--------------------------------|----------------------------|--|

| NAME | NO. | TYPE  | SIGNAL | DAIA RAIE (1)            | TERMINATION | DESCRIPTION                    | LENGTH (mm) <sup>(2)</sup> |  |

| VSS  | A21 | Power |        |                          |             |                                |                            |  |

| VSS  | B2  | Power |        |                          |             |                                |                            |  |

| VSS  | B4  | Power |        |                          |             |                                |                            |  |

| VSS  | B20 | Power |        |                          |             |                                |                            |  |

| VSS  | C21 | Power |        |                          |             |                                |                            |  |

| VSS  | D2  | Power |        |                          |             |                                |                            |  |

| VSS  | D3  | Power |        |                          |             |                                |                            |  |

| VSS  | D20 | Power |        |                          |             |                                |                            |  |

| VSS  | D22 | Power |        |                          |             |                                |                            |  |

| VSS  | E3  | Power |        |                          |             |                                |                            |  |

| VSS  | E21 | Power |        |                          |             | Ground – Common return for all |                            |  |

| VSS  | F2  | Power |        |                          |             | power inputs                   |                            |  |

| VSS  | F4  | Power |        |                          |             |                                |                            |  |

| VSS  | F20 | Power |        |                          |             |                                |                            |  |

| VSS  | F22 | Power |        |                          |             |                                |                            |  |

| VSS  | G21 | Power |        |                          |             |                                |                            |  |

| VSS  | H3  | Power |        |                          |             |                                |                            |  |

| VSS  | H20 | Power |        |                          |             |                                |                            |  |

| VSS  | H22 | Power |        |                          |             |                                |                            |  |

| VSS  | J2  | Power |        |                          |             |                                |                            |  |

| VSS  | J21 | Power |        |                          |             |                                |                            |  |

| VSS  | K20 | Power |        |                          |             |                                |                            |  |

#### 表 6-1. Connector Pins for FQD (continued)

- (1) DDR = Double data rate

- SDR = Single data rate

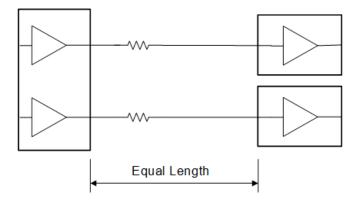

- Refer to  $\pm 2 2 = 27.7$  for specifications and relationships.

- (2) Net trace lengths inside the package:

- Relative dielectric constant for the FQD ceramic package is 9.8.

- Propagation speed = 11.8 / sqrt(9.8) = 3.769 inches/ns.

- Propagation delay = 0.265 ns/inch = 265 ps/inch = 10.43 ps/mm.

- (3) The following power supplies are all required to operate the DMD: VSS, VCC, VOFFSET, VBIAS, VRESET.

#### 表 6-2. Test Pads for FQD Package

| NAME   | PIN                                                                                        | SIGNAL    | DESCRIPTION    |

|--------|--------------------------------------------------------------------------------------------|-----------|----------------|

| UNUSED | A5, A18, B5, B18, C5, C18, D5, D18, E5,<br>E18, F5, F18, G5, G18, H5, H18, J5, J18,<br>K22 | Test pads | Do not connect |

# 7 Specifications

### 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

|                      |                                                   |                         | MIN  | MAX        | UNIT |

|----------------------|---------------------------------------------------|-------------------------|------|------------|------|

| SUPPLY VOLTAGES (2)  |                                                   |                         |      |            |      |

| VCC                  | Supply voltage for LVCMOS core logic              |                         | -0.5 | 4          | V    |

| VREF                 | Supply voltage for LVCMOS DDR interface           |                         | -0.5 | 4          | V    |

| VOFFSET              | Supply voltage for high voltage CMOS and mid      | cromirror electrode     | -0.5 | 8.75       | V    |

| VBIAS <sup>(3)</sup> | Supply voltage for micromirror electrode          |                         | -0.5 | 17         | V    |

| VRESET               | Supply voltage for micromirror electrode          |                         | -11  | 0.5        | V    |

| VBIAS - VOFFSET  (3) | Supply voltage delta (absolute value)             |                         |      | 8.75       | V    |

| INPUT VOLTAGES (2)   |                                                   |                         |      |            |      |

|                      | Input voltage to all other input pins             |                         | -0.5 | VREF + 0.5 | V    |

| INPUT CURRENTS       |                                                   |                         | -1   |            |      |

|                      | Current required from a high-level output         | V <sub>OH</sub> = 1.4 V |      | -9         | mA   |

|                      | Current required from a low-level output          | V <sub>OL</sub> = 0.4 V |      | 18         | mA   |

| CLOCKS               |                                                   |                         |      |            |      |

| f <sub>CLK</sub>     | DCLK clock frequency                              |                         | 80   | 120        | MHz  |

| ENVIRONMENTAL        |                                                   |                         |      |            |      |

| т                    | Case temperature - operational <sup>(4)</sup>     |                         | -20  | 90         | °C   |

| T <sub>CASE</sub>    | Case temperature - non-operational <sup>(4)</sup> |                         | -40  | 90         | °C   |

| T <sub>DP</sub>      | Dew Point (operation and non-operational)         |                         |      | 81         | °C   |

|                      | Operating Relative Humidity (non-condensing)      | i                       | 0    | 95         | %RH  |

(1) Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

- (2) All voltage values are referenced to common ground VSS. Supply voltages VCC, VREF, VOFFSET, VBIAS, and VRESET are all required for proper DMD operation. VSS must also be connected.

- (3) To prevent excess current, the supply voltage delta |VBIAS VOFFSET| must be less than the specified limit.

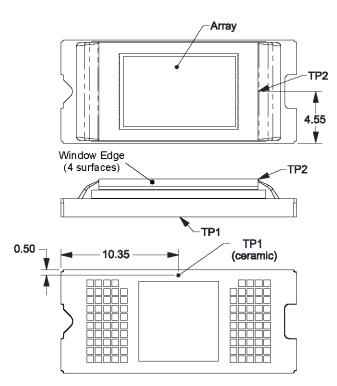

- (4) DMD Temperature is the worst-case of any test point shown in or 🛛 8-3, or the active array as calculated by the Micromirror Array Temperature Calculation, or any point along the Window Edge as defined in or 🖾 8-3. The locations of thermal test point TP2 is intended to measure the highest window edge temperature. If a particular application causes another point on the window edge to be at a higher temperature, a test point should be added to that location.

### 7.2 Storage Conditions

applicable before the DMD is installed in the final product

|   |     |                                                            | MIN | MAX | UNIT |

|---|-----|------------------------------------------------------------|-----|-----|------|

|   |     | Storage temperature <sup>(1)</sup>                         | -40 | 85  | °C   |

| - | r   | Storage humidity, non-condensing <sup>(1)</sup>            | 0   | 95% | RH   |

|   | stg | Long-term storage dew point <sup>(1)</sup> <sup>(2)</sup>  |     | 24  | °C   |

|   |     | Short-term storage dew point <sup>(1)</sup> <sup>(3)</sup> |     |     | °C   |

(1) As a best practice, TI recommends storing the DMD in a temperature and humidity controlled environment.

- (2) Long-term is defined as the average over the usable life.

- (3) Short-term is defined as <60 cumulative days over the usable life of the device.

### 7.3 ESD Ratings

|                                               |                                                                                                 | VALUE | UNIT |

|-----------------------------------------------|-------------------------------------------------------------------------------------------------|-------|------|

| V <sub>(ESD)</sub> Electrostatic<br>discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup> <sup>(2)</sup> <sup>(3)</sup> | ±2000 | V    |

ESD Ratings are applicable before the DMD is installed in final product. (1)

(2)

All CMOS devices require proper Electrostatic Discharge (ESD) handling procedures. JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. (3)

### 7.4 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                                        |                                                                  | MIN        | NOM | MAX                  | UNIT               |

|----------------------------------------|------------------------------------------------------------------|------------|-----|----------------------|--------------------|

| SUPPLY VOLT                            | AGES                                                             |            |     |                      |                    |

| VCC                                    | Supply voltage for LVCMOS core logic                             | 2.375      | 2.5 | 2.625                | V                  |

| VREF                                   | Supply voltage for LVCMOS DDR interface                          | 1.6        | 1.9 | 2                    | V                  |

| VOFFSET                                | Supply voltage for HVCMOS and micromirror electrode              | 8.25       | 8.5 | 8.75                 | V                  |

| VBIAS                                  | Supply voltage for micromirror electrode                         | 15.5       | 16  | 16.5                 | V                  |

| VRESET                                 | Supply voltage for micromirror electrode                         | -9.5       | -10 | -10.5                | V                  |

| VBIAS –<br>VOFFSET                     | Supply voltage delta (absolute value)                            |            |     | 8.75                 | V                  |

| VOLTAGE RAN                            | IGE                                                              |            |     | 1                    |                    |

| V <sub>T+</sub>                        | Positive-going threshold voltage                                 | 0.4 × VREF |     | 0.7 × VREF           | V                  |

| V <sub>T-</sub>                        | Negative-going threshold voltage                                 | 0.3 × VREF |     | 0.6 × VREF           | V                  |

| V <sub>hys</sub>                       | Hysteresis voltage (V <sub>T+</sub> – V <sub>T–</sub> )          | 0.1 × VREF |     | 0.4 × VREF           | V                  |

| CLOCK FREQ                             | UENCY                                                            |            |     | 1                    |                    |

| f <sub>(CLK)</sub>                     | DCLK clock frequency                                             | 80         |     | 120                  | MHz                |

| ENVIRONMEN                             | TAL                                                              |            |     | I                    |                    |

| <b>+</b>                               | DMD temperature - operational, long-term                         | 10         |     | 40 to 70             | °C                 |

| T <sub>DMD</sub>                       | DMD temperature - operational, short-term                        | -20        |     | 70                   | °C                 |

| T <sub>Window</sub>                    | DMD window temperature - operational                             | 0          |     | 90                   | °C                 |

| T <sub>CERAMIC</sub> -<br>WINDOW-DELTA | DMD  ceramic - window  temperature delta - operational           | 0          |     | 15                   | °C                 |

|                                        | DMD long-term dewpoint (operational, non-operational)            |            |     | 24                   | °C                 |

|                                        | DMD short-term dewpoint (operational, non-operational)           |            |     | 28                   | °C                 |

| ILLUMINATION                           | 4                                                                |            |     | I                    |                    |

| ILL <sub>UV-VIS</sub>                  | Illumination power - spectral region <700 nm                     |            |     | 0.68                 | mW/cm <sup>2</sup> |

| ILL <sub>NIR</sub>                     | Illumination power - spectral region 700 to 2500 nm, FQD package |            |     | Thermally<br>Limited | mW/cm <sup>2</sup> |

| ILL <sub>MWIR</sub>                    | Illumination power - spectral region >2500 nm                    |            |     | 10                   | mW/cm <sup>2</sup> |

### 7.5 Thermal Information

|                                                                 | DLP4500NIR |      |

|-----------------------------------------------------------------|------------|------|

| THERMAL METRIC                                                  | FQD (LCCC) | UNIT |

|                                                                 | 98 PINS    |      |

| Thermal resistance - Active area to case ceramic <sup>(1)</sup> | 2          | °C/W |

(1) The DMD is designed to conduct absorbed and dissipated heat to the back of the package. The cooling system must be capable of maintaining the package within the temperature range specified in the Recommended Operating Conditions. The total heat load on the DMD is largely driven by the incident light absorbed by the active area; although other contributions include light energy absorbed by the window aperture and electrical power dissipation of the array. Optical systems should be designed to minimize the light energy falling outside the window clear aperture since any additional thermal load in this area can significantly degrade the reliability of the device.

### 7.6 Electrical Characteristics

|                     | PARAMETER                                            | TEST CONDITIONS                                                        | MIN | NOM    | MAX    | UNIT |

|---------------------|------------------------------------------------------|------------------------------------------------------------------------|-----|--------|--------|------|

| IIL                 | Low-level input current (1)                          | VREF = 2.00 V, V <sub>1</sub> = 0 V                                    | -50 |        |        | nA   |

| I <sub>IH</sub>     | High-level input current (1)                         | VREF = 2.00 V, V <sub>I</sub> = VREF                                   |     |        | 50     | nA   |

| CURRENT             |                                                      |                                                                        |     |        |        |      |

| I <sub>REF</sub>    | Current into VREF pin                                | VREF = 2.00 V, f <sub>DCLK</sub> = 120 MHz                             |     | 2.15   | 2.75   | mA   |

| I <sub>CC</sub>     | Current into VCC pin                                 | VCC = 2.75 V, f <sub>DCLK</sub> = 120 MHz                              |     | 125    | 160    | mA   |

| I <sub>OFFSET</sub> | Current into VOFFSET pin <sup>(2)</sup>              | VOFFSET = 8.75 V, Three global resets within time period = 200 $\mu$ s |     | 3      | 3.3    | mA   |

| I <sub>BIAS</sub>   | Current into VBIAS pin <sup>(2)</sup> <sup>(3)</sup> | VBIAS = 16.5 V, Three global resets within time period = 200 µs        |     | 2.55   | 6.5    | mA   |

| I <sub>RESET</sub>  | Current into VRESET pin                              | VRESET = -10.5 V                                                       |     | 2.45   | 3.1    | mA   |

| I <sub>TOTAL</sub>  |                                                      |                                                                        |     | 135.15 | 175.65 | mA   |

| POWER               |                                                      |                                                                        |     |        |        |      |

| P <sub>REF</sub>    | Power into VREF pin <sup>(4)</sup>                   | VREF = 2.00 V, f <sub>DCLK</sub> = 120 MHz                             |     | 4.15   | 5.5    | mW   |

| P <sub>CC</sub>     | Power into VCC pin <sup>(4)</sup>                    | VCC = 2.75 V, f <sub>DCLK</sub> = 120 MHz                              |     | 343.75 | 440    | mW   |

| P <sub>OFFSET</sub> | Power into VOFFSET pin <sup>(4)</sup>                | VOFFSET = 8.75 V, Three global resets<br>within time period = 200 μs   |     | 26.25  | 28.9   | mW   |

| P <sub>BIAS</sub>   | Power into VBIAS pin <sup>(4)</sup>                  | VBIAS = 16.5 V, Three global resets within time period = 200 $\mu$ s   |     | 42.1   | 58.6   | mW   |

| P <sub>RESET</sub>  | Power into VRESET pin <sup>(4)</sup>                 | VRESET = -10.5 V                                                       |     | 25.71  | 32.6   | mW   |

| P <sub>TOTAL</sub>  |                                                      |                                                                        |     | 442    | 566    | mW   |

| CAPACITA            | NCE                                                  |                                                                        |     |        | 1      |      |

| CI                  | Input capacitance                                    | f = 1 MHz                                                              |     |        | 10     | pF   |

| Co                  | Output capacitance                                   | <i>f</i> = 1 MHz                                                       |     |        | 10     | pF   |

(1) Applies to LVCMOS pins only. LVCMOS pins do not have pullup or pulldown configurations.

(2) Exceeding the maximum allowable absolute voltage difference between VBIAS and VOFFSET may result in excess current draw. See the セクション 7.1 for further details.

(3) When  $\overline{DRC_{OE}}$  = HIGH, the internal reset drivers are tri-stated and I<sub>BIAS</sub> standby current is 6.5 mA.

(4) In some applications, the total DMD heat load can be dominated by the amount of incident light energy absorbed. See the  $\pm 222$  8.5 for further details.

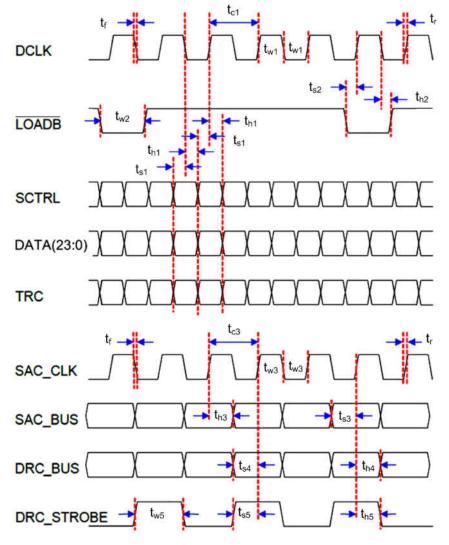

### 7.7 Timing Requirements

Over operating free-air temperature range (unless otherwise noted). This data sheet provides timing at the device pin.

|                    |                                                                          | MIN  | NOM   | MAX  | UNIT |

|--------------------|--------------------------------------------------------------------------|------|-------|------|------|

|                    | Setup time: DATA before rising or falling edge of DCLK <sup>(1)</sup>    | 0.7  |       |      |      |

| t <sub>su(1)</sub> | Setup time: TRC before rising or falling edge of DCLK (1)                | 0.7  |       |      | ns   |

|                    | Setup time: SCTRL before rising or falling edge of DCLK <sup>(1)</sup>   | 0.7  |       |      |      |

| t <sub>su(2)</sub> | Setup time: LOADB low before rising edge of DCLK <sup>(1)</sup>          | 0.7  |       |      | ns   |

| t <sub>su(3)</sub> | Setup time: SAC_BUS low before rising edge of SAC_CLK <sup>(1)</sup>     | 1    |       |      | ns   |

| t <sub>su(4)</sub> | Setup time: DRC_BUS high before rising edge of SAC_CLK (1)               | 1    |       |      | ns   |

| t <sub>su(5)</sub> | Setup time: DRC_STROBE high before rising edge of SAC_CLK <sup>(1)</sup> | 2    |       |      | ns   |

|                    | Hold time: DATA after rising or falling edge of DCLK <sup>(1)</sup>      | 0.7  |       |      |      |

| t <sub>h(1)</sub>  | Hold time: TRC after rising or falling edge of DCLK <sup>(1)</sup>       | 0.7  |       |      | ns   |

|                    | Hold time: SCTRL after rising or falling edge of DCLK <sup>(1)</sup>     | 0.7  |       |      |      |

| t <sub>h(2)</sub>  | Hold time: LOADB low after falling edge of DCLK <sup>(1)</sup>           | 0.7  |       |      | ns   |

| t <sub>h(3)</sub>  | Hold time: SAC_BUS low after rising edge of SAC_CLK <sup>(1)</sup>       | 1    |       |      | ns   |

| t <sub>h(4)</sub>  | Hold time: DRC_BUS after rising edge of SAC_CLK <sup>(1)</sup>           | 1    |       |      | ns   |

| t <sub>h(5)</sub>  | Hold time: DRC_STROBE after rising edge of SAC_CLK <sup>(1)</sup>        | 2    |       |      | ns   |

| 4                  | Rise time (20% to 80%): DCLK / SAC_CLK, VREF = 1.8 V                     |      |       | 1.08 | 20   |

| t <sub>r</sub>     | Rise time (20% to 80%): DATA / TRC / SCTRL / TOADB, VREF = 1.8 V         |      |       | 1.08 | ns   |

| +                  | Fall time (20% to 80%): DCLK / SAC_CLK, VREF = 1.8 V                     |      |       | 1.08 | 20   |

| t <sub>f</sub>     | Fall time (20% to 80%): DATA / TRC / SCTRL / LOADB                       |      |       | 1.08 | ns   |

| t <sub>c1</sub>    | Clock cycle: DCLK                                                        | 8.33 | 10    | 12.5 | ns   |

| t <sub>c3</sub>    | Clock cycle: SAC_CLK                                                     | 12.5 | 13.33 | 14.3 | ns   |

| t <sub>w1</sub>    | Pulse width high or low: DCLK                                            | 3.33 |       |      | ns   |

| t <sub>w2</sub>    | Pulse width low: LOADB                                                   | 4.73 |       |      | ns   |

| t <sub>w3</sub>    | Pulse width high or low: SAC_CLK                                         | 5    |       |      | ns   |

| t <sub>w5</sub>    | Pulse width high: DRC_STROBE                                             | 7    |       |      | ns   |

(1) Setup and hold times shown are for fast input slew rates >1 V/ns. For slow slew rates >0.5 V/ns and <1 V/ns, the setup and hold times are longer. For every 0.1 V/ns decrease in slew rate from 1 V/ns, add 150 ps on setup and hold.

🗷 7-2. Timing Diagram

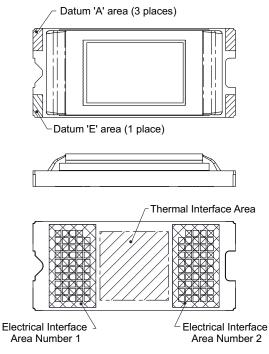

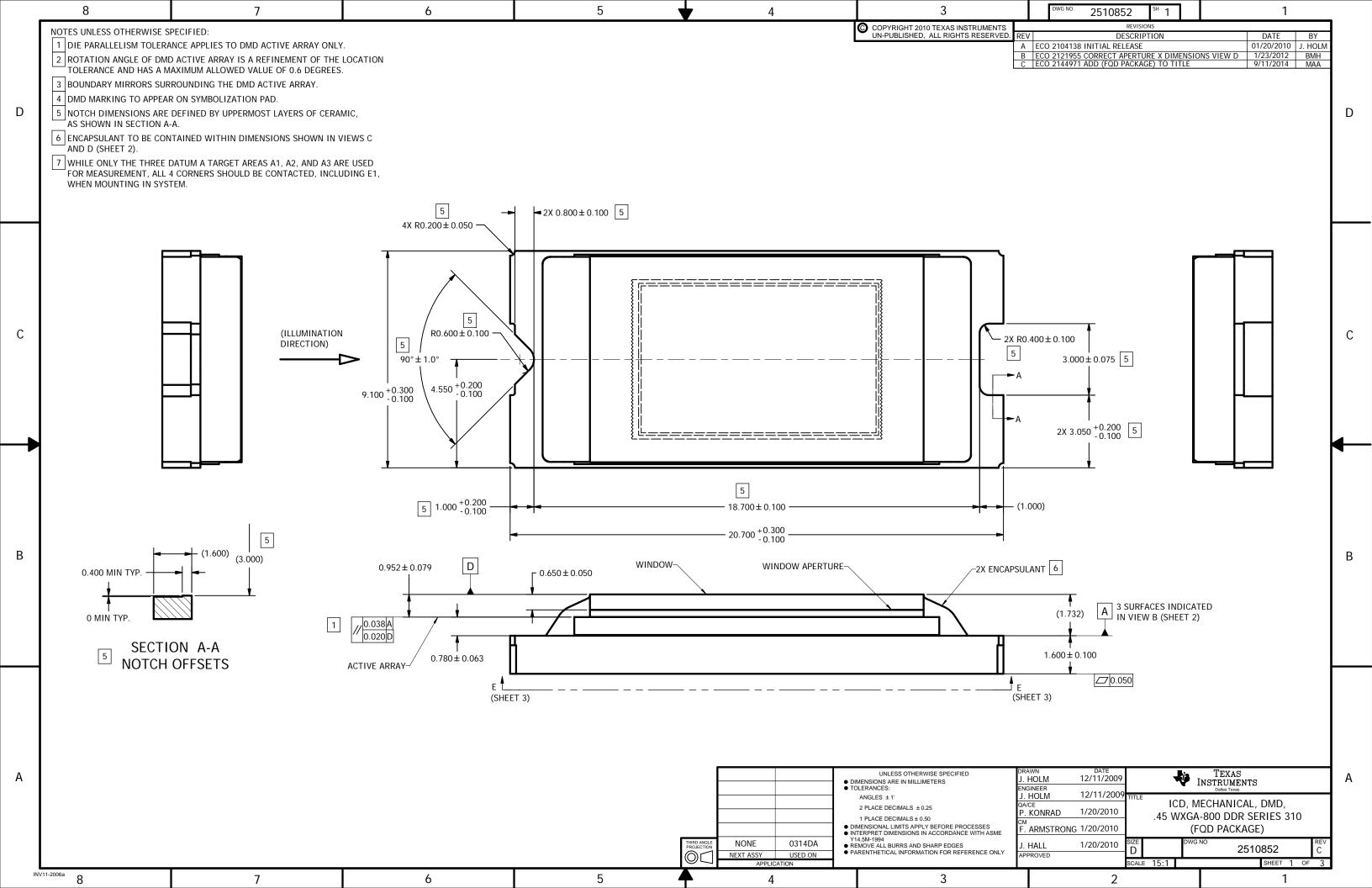

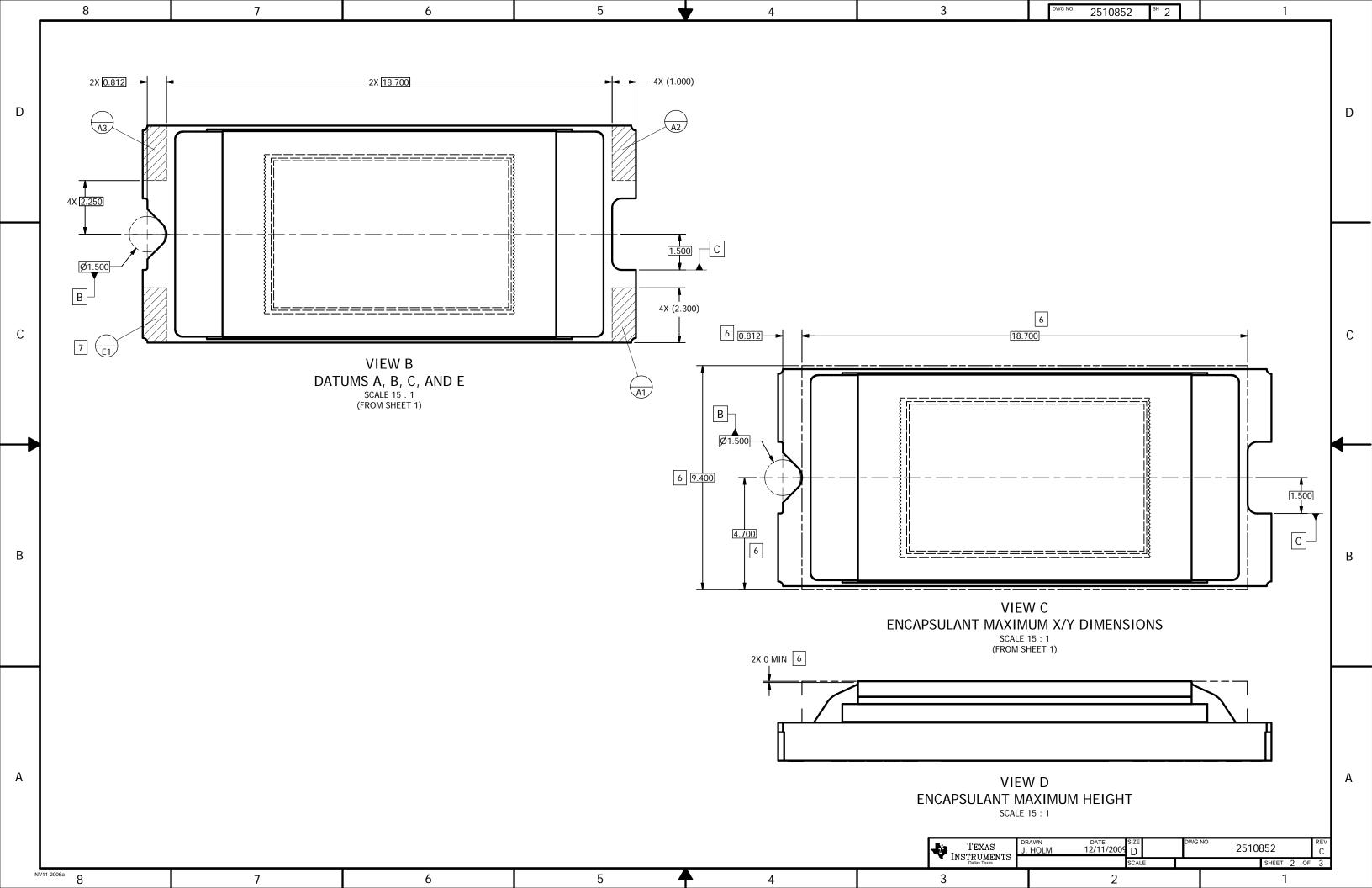

### 7.8 System Mounting Interface Loads

|                                                           |                |                                                      | MIN | NOM | MAX | UNIT |

|-----------------------------------------------------------|----------------|------------------------------------------------------|-----|-----|-----|------|

| Load applied to the thermal interface area <sup>(1)</sup> | FQD<br>package | Uniformly distributed over<br>Thermal Interface area |     |     | 62  | Ν    |

| Load applied to the electrical interface areas (1)        | (2)            | Uniformly distributed over each of the two areas     |     |     | 55  | Ν    |

(1) See and  $\boxtimes$  7-3 for diagrams.

(2) See Mounting Concepts DLP4500FQD.

図 7-3. System Interface Loads for FQD

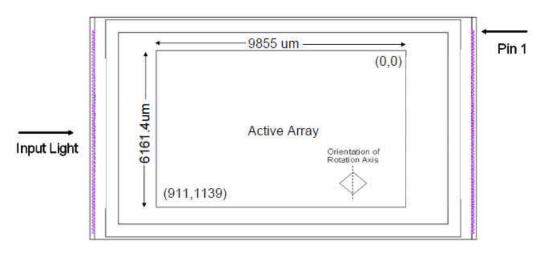

### 7.9 Micromirror Array Physical Characteristics

|                                                           | VALUE  | UNIT         |

|-----------------------------------------------------------|--------|--------------|

| Number of active micromirror rows <sup>(2)</sup>          | 1140   | micromirrors |

| Number of active micromirror columns <sup>(2)</sup>       | 912    | micromirrors |

| Micromirror pitch, diagonal <sup>(2)</sup>                | 7.6    | μm           |

| Micromirror pitch, vertical and horizontal <sup>(2)</sup> | 10.8   | μm           |

| Micromirror active array height <sup>(3)</sup>            | 1140   | micromirrors |

|                                                           | 6161.4 | μm           |

| Micromitron active array width (3)                        | 912    | micromirrors |

| Micromirror active array width <sup>(3)</sup>             | 9855   | μm           |

| Micromirror array border <sup>(1)</sup>                   | 10     | mirrors/side |

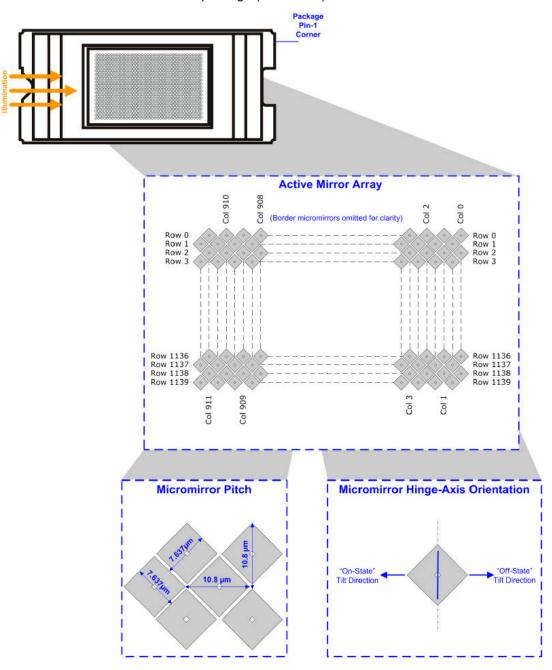

(1) The mirrors that form the array border are hard-wired to tilt in the -12° ("Off") direction once power is applied to the DMD (see Micromirror Array, Pitch, and Hinge-Axis Orientation and Micromirror Landed Positions and Light Paths).

(2) See Micromirror Array, Pitch, and Hinge-Axis Orientation.

(3) See Micromirror Active Area in 🗷 7-4.

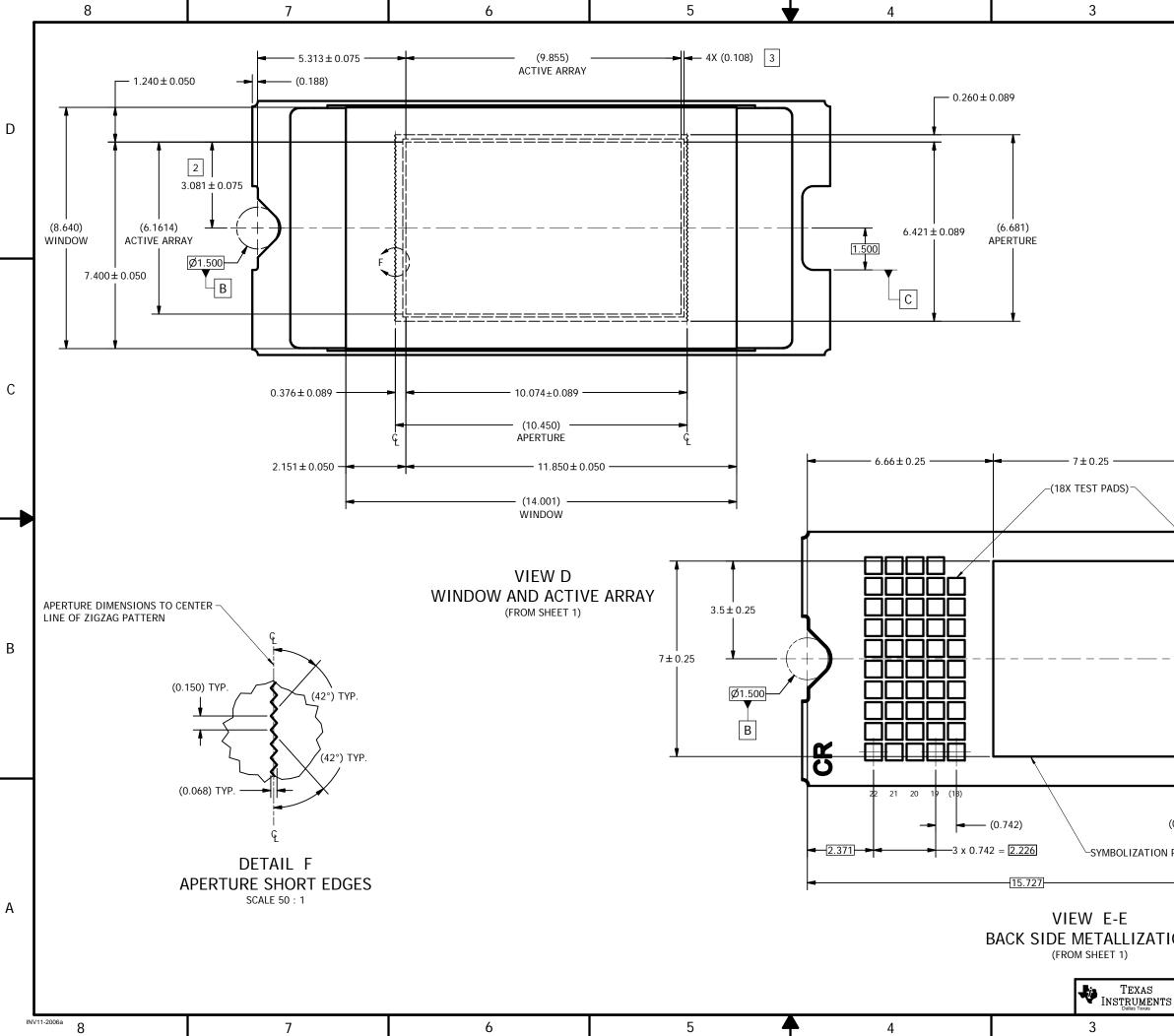

### 図 7-4. DLP4500NIR Micromirror Active Area

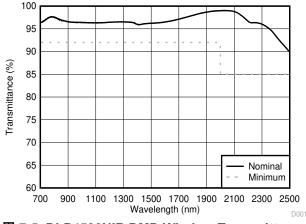

### 7.10 Micromirror Array Optical Characteristics

TI assumes no responsibility for end-equipment optical performance. Achieving the desired end-equipment optical performance involves making trade-offs between numerous component and system design parameters. See the related application reports in  $\frac{1}{2}\sqrt{2}\frac{3}{2}\sqrt{12.2.1}$  for guidelines.

|                            | PARAMETER                                                                                            | TEST CONDITIONS                                                            | MIN    | NOM                 | MAX | UNIT        |

|----------------------------|------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|--------|---------------------|-----|-------------|

|                            |                                                                                                      | DMD <i>parked</i> state <sup>(1) (3) (4)</sup> , see <sup>(10)</sup>       |        | 0                   |     |             |

| α                          | Micromirror tilt angle                                                                               | DMD <i>landed</i> state <sup>(1) (5) (6)</sup> , see <sup>(10)</sup>       | 11     | 12                  | 13  | degrees     |

| β                          | Micromirror tilt angle variation <sup>(1)</sup><br>(5) (7) (8) (9)                                   | See <sup>(10)</sup>                                                        | -1     |                     | 1   | degrees     |

|                            | Micromirror crossover time <sup>(2)</sup> (11)                                                       |                                                                            |        | 5                   |     | μs          |

|                            | Micromirror switching time (11)                                                                      |                                                                            |        | 16                  |     | μs          |

|                            | Orientation of the micromirror axis-of-rotation <sup>(12)</sup>                                      |                                                                            | 89     | 90                  | 91  | degrees     |

|                            | Micromirror array fill factor <sup>(13)</sup> <sup>(14)</sup> <sup>(17)</sup>                        | f/3 illumination at 24 degree angle,<br>mirrors tilted toward illumination |        | 92%                 |     |             |

|                            | Mirror metal specular reflectivity (13) (14)                                                         | 700 nm to 2500 nm                                                          |        | 89%                 |     |             |

|                            | Window material                                                                                      |                                                                            | Cornir | ng Eagle X          | G   |             |

|                            | Window aperture                                                                                      |                                                                            |        | See <sup>(15)</sup> |     |             |

|                            | Illumination overfill (16)                                                                           |                                                                            |        | See (16)            |     |             |

|                            | Window transmittance (single<br>pass through two window<br>surfaces) <sup>(13)</sup> <sup>(14)</sup> | 2000 nm to 2500 nm, See 🛛 7-5                                              |        | 90%                 |     |             |

|                            | Bright pixel(s) in active area <sup>(19)</sup>                                                       | Gray 10 Screen <sup>(20)</sup>                                             |        |                     | 0   |             |

|                            | Bright pixel(s) in the POM <sup>(21)</sup>                                                           | Gray 10 Screen <sup>(20)</sup>                                             |        |                     | 1   |             |

| mage                       | Dark pixel(s) in the active area <sup>(22)</sup>                                                     | White Screen                                                               |        |                     | 4   | micromirror |

| erformance <sup>(18)</sup> | Adjacent pixel(s) <sup>(23)</sup>                                                                    | Any Screen                                                                 |        |                     | 0   |             |

|                            | Unstable pixel(s) in active area                                                                     | Any Screen                                                                 |        |                     | 0   |             |

(1) Measured relative to the plane formed by the overall micromirror array.

(2) Micromirror crossover time is primarily a function of the natural response time of the micromirrors.

(3) *Parking* the micromirror array returns all of the micromirrors to a relatively flat (0°) state (as measured relative to the plane formed by the overall micromirror array).

- (4) When the micromirror array is parked, the tilt angle of each individual micromirror is uncontrolled.

- (5) Additional variation exists between the micromirror array and the package datums.

- (6) When the micromirror array is *landed*, the tilt angle of each individual micromirror is dictated by the binary contents of the CMOS memory cell associated with each individual micromirror. A binary value of 1 results in a micromirror *landing* in an nominal angular position of +12°. A binary value of 0 results in a micromirror *landing* in an nominal angular position of -12°.

- (7) Represents the landed tilt angle variation relative to the nominal landed tilt angle

- (8) Represents the variation that can occur between any two individual micromirrors, located on the same device or located on different devices.

- (9) For some applications, it is critical to account for the micromirror tilt angle variation in the overall system optical design. With some system optical designs, the micromirror tilt angle variation within a device may result in perceivable non-uniformities in the light field reflected from the micromirror array. With some system optical designs, the micromirror tilt angle variations or system contrast variations.

(10) See 🛛 8-2.

- (11) Performance as measured at the start of life.

- (12) Measured relative to the package datums B and C, shown in the Package Mechanical Data section in t 2 2 3 2 3.

- (13) The nominal DMD total optical efficiency results from the following four components:

- Micromirror array fill factor

- Micromirror array diffraction efficiency

- Micromirror surface reflectivity (very similar to the reflectivity of bulk Aluminum)

- · Window Transmission (single pass through two surfaces for incoming light, and single pass through two surfaces for reflected light)

- (14) The DMD diffraction efficiency and total optical efficiency observed in a specific application depends on numerous application-specific design variables, such as:

- Illumination wavelength, bandwidth or line-width, degree of coherence

- Illumination angle, plus angle tolerence

- Illumination and projection aperture size, and location in the system optical path

- · Illumination overfill of the DMD micromirror array

- Aberrations present in the illumination source or path, or both

- Aberrations present in the projection path

Does not account for the effect of micromirror switching duty cycle, which is application dependent. Micromirror switching duty cycle represents the percentage of time that the micromirror is actually reflecting light from the optical illumination path to the optical projection path. This duty cycle depends on the illumination aperture size, the projection aperture size, and the micromirror array update rate.

- (15) See the Package Mechanical Characteristics in  $\pm \sigma \hat{\gamma} \Rightarrow 13$  for details regarding the size and location of the window aperture.

- (16) The active area of the DLP4500NIR device is surrounded by an aperture on the inside of the DMD window surface that masks structures of the DMD device assembly from normal view. The aperture is sized to anticipate several optical conditions. Overfill light illuminating the area outside the active array can scatter and create adverse effects to the performance of an end application using the DMD. Design the illumination optical system as to limit light flux incident outside the active array to less than 10% of the light flux level in the active area. Depending on the particular system's optical architecture and assembly tolerances, the amount of overfill light on the outside of the active array may cause system performance degradation.

- (17) The Micromirror array fill factor depends on numerous application-specific design variables, such as:

- Illumination angle, plus angle tolerance

- · Illumination and projection aperture size, and location in the system optical path

- (18) Conditions of Acceptance: All DMD image quality returns will be evaluated using the following projected image test conditions: Test set degamma shall be linear

- Test set brightness and contrast shall be set to nominal

- The diagonal size of the projected image shall be a minimum of 20 inches

- The projections screen shall be 1X gain

- The projected image shall be inspected from a 38 inch minimum viewing distance

- The image shall be in focus during all image quality tests

- (19) Bright pixel definition: A single pixel or mirror that is stuck in the ON position and is visibly brighter than the surrounding pixels

- (20) Gray 10 screen definition: All areas of the screen are colored with the following settings:

- Red = 10/255

- Green = 10/255

- Blue = 10/255

- (21) POM definition: Rectangular border of off-state mirrors surrounding the active area

- (22) Dark pixel definition: A single pixel or mirror that is stuck in the OFF position and is visibly darker than the surrounding pixels

- (23) Adjacent pixel definition: Two or more stuck pixels sharing a common border or common point, also referred to as a cluster

- (24) Unstable pixel definition: A single pixel or mirror that does not operate in sequence with parameters loaded into memory. The unstable pixel appears to be flickering asynchronously with the image

### 7.11 Typical Characteristics

Angle of incidence = 0°

Single pass through two window surfaces

### 8 Detailed Description

### 8.1 Overview

Electrically, the DLP4500NIR device consists of a two-dimensional array of 1-bit CMOS memory cells, organized in a grid of 912 memory cell columns by 1140 memory cell rows. The CMOS memory array is addressed on a column-by-column basis, over a 24-bit DDR bus. Addressing is handled through a serial control bus. The specific CMOS memory access protocol is handled by the DLPC350 digital controller.

Optically, the DLP4500NIR device consists of 1039680 highly reflective, digitally switchable, micrometer-sized mirrors (micromirrors) organized in a two-dimensional array. The micromirror array consists of 912 micromirror columns by 1140 micromirror rows in diamond pixel configuration ( $\boxtimes$  8-1). Due to the diamond pixel configuration, the columns of each odd row are offset by half a pixel from the columns of the even row.

### 8.2 Functional Block Diagram

### 8.3 Feature Description

Each aluminum micromirror is approximately 7.6 microns in size and arranged in row and columns as shown in  $\boxtimes$  8-1. Due to the diamond pixel array of the DMD, the pixel data does not appear on the DMD exactly as it would in an orthogonal pixel arrangement. Pixel arrangement and numbering for the DLP4500NIR is shown in  $\boxtimes$  8-1.

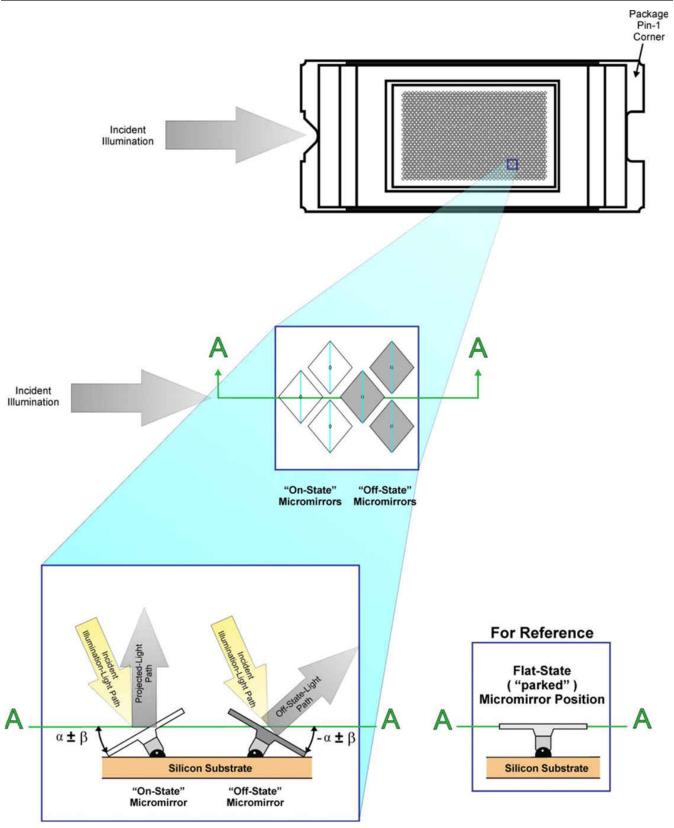

Each micromirror is switchable between two discrete angular positions:  $-12^{\circ}$  and  $12^{\circ}$ . The angular positions  $\alpha$  and  $\beta$  are measured relative to a 0° *flat reference when the mirrors are parked in their inactive state*, parallel to the array plane (see 🛛 8-2). The parked position is not a latched position. Individual micromirror angular positions are relatively flat, but do vary. The tilt direction is perpendicular to the hinge-axis. The on-state landed position is directed toward the left side of the package (see 🖾 8-2).

図 8-1. Micromirror Array, Pitch, and Hinge-Axis Orientation

図 8-2. Micromirror Landed Positions and Light Paths

Each individual micromirror is positioned over a corresponding CMOS memory cell. The angular position of a specific micromirror is determined by the binary state (logic 0 or 1) of the corresponding CMOS memory cell contents, after the mirror *clocking pulse* is applied. The angular position  $(-12^{\circ} \text{ or } 12^{\circ})$  of the individual micromirrors changes synchronously with a micromirror clocking pulse, rather than being coincident with the CMOS memory cell data update. Therefore, writing a logic 1 into a memory cell followed by a mirror clocking pulse results in the corresponding micromirror switching to a  $12^{\circ}$  position. Writing a logic 0 into a memory cell followed by a mirror clocking pulse results in the corresponding micromirror switching to a  $12^{\circ}$  position.

Updating the angular position of the micromirror array consists of two steps.

- 1. Update the contents of the CMOS memory.

- 2. Applying a mirror clocking pulse to the entire micromirror array.

Mirror reset pulses are generated internally by the DLP4500NIR DMD, with initiation of the pulses being coordinated by the DLPC350 controller. For timing specifications, see t2227.7.

Around the perimeter of the 912 × 1140 array of micromirrors is a uniform band of *border* micromirrors. The border micromirrors are not user-addressable. The border micromirrors land in the  $-12^{\circ}$  position after power has been applied to the device. There are 10 border micromirrors on each side of the 912 × 1140 active array.

#### 8.4 Device Functional Modes

DLP4500NIR is part of the chipset comprising of the DLP4500NIR DMD and DLPC350 display controller. To ensure reliable operation, the DLP4500NIR DMD must always be used with the DLPC350 display controller. DMD functional modes are controlled by the DLPC350 digital display controller. See the DLPC350 data sheet listed in  $\pm 2 \ge 12.2.1$ .

#### 8.4.1 Operating Modes

The DLPC350 is capable of sending patterns to the DLP4500NIR DMD in two different streaming modes. The first mode is continuous streaming mode, where the DLPC350 uses the parallel RGB interface to stream the 24-bit patterns to the DMD. The second mode is burst mode, where the DLPC350 loads up to 48 binary patterns from flash storage into internal memory, and then streams those patterns to the DMD.  $\frac{1}{5}$  8-1 shows the maximum pattern and data rates for both modes of operation.

| OPERATING MODE                      | PATTERN RATE (Hz) | DATA RATE (Gbps) | MAXIMUM BINARY PATTERNS |  |  |

|-------------------------------------|-------------------|------------------|-------------------------|--|--|

| Continuous Streaming <sup>(1)</sup> | 2880              | 2.99             | Unlimited               |  |  |

| Burst <sup>(2)</sup>                | 4220              | 4.39             | 48                      |  |  |

#### 表 8-1. Pattern and Data Rates

(1) Continuous streaming mode uses patterns from RGB interface.

(2) Burst mode uses patterns from internal memory.

#### 8.5 Micromirror Array Temperature Calculation

Achieving optimal DMD performance requires proper management of the maximum DMD case temperature, the maximum temperature of any individual micromirror in the active array, the maximum temperature of the window aperture, and the temperature gradient between any two points on or within the package.

See the  $\pm 29 \neq 7.1$  and  $\pm 29 \neq 7.4$  for applicable temperature limits.

#### 8.5.1 Package Thermal Resistance

The DMD is designed to conduct the absorbed and dissipated heat back to the package where it can be removed by an appropriate thermal management system. The thermal management system must be capable of maintaining the package within the specified operational temperatures at the Thermal test point location, see 8-3. The total heat load on the DMD is typically driven by the incident light absorbed by the active area; although other contributions can include light energy absorbed by the window aperture, electrical power dissipation of the array, and/or parasitic heating.

#### 8.5.2 Case Temperature

The temperature of the DMD case can be measured directly. For consistency, a thermal test point location TP1 representing the case temperature is defined as shown in and  $\boxtimes$  8-3.

図 8-3. Thermal Test Point Location - FQD Package

#### 8.5.2.1 Temperature Calculation

Micromirror array temperature cannot be measured directly, therefore it must be computed analytically using one or more of these conditions:

- Thermal test point location (see or 28-3)

- Package thermal resistance

- Electrical power dissipation

- Illumination heat load

The relationship between the micromirror array and the case temperature is provided by the following equations:

| $T_{Array} = T_{Ceramic} + (Q_{Array} \times R_{Array-To-Ceramic})$ | (1)    |

|---------------------------------------------------------------------|--------|

| $Q_{Array} = Q_{Elec} + Q_{IIIum}$                                  | (2)    |

| $Q_{IIIum} = P_D \times A \times DMD$ Absorption Constant           | nt (3) |

#### where

- T<sub>Array</sub> = Computed micromirror array temperature (°C)

- T<sub>Ceramic</sub> = Ceramic case temperature (°C), located at TP1

- Q<sub>Array</sub> = Total (electrical + absorbed) DMD array power (W)

- R<sub>Array-to-Ceramic</sub> = Thermal resistance of DMD package from array to TP1 (°C/W)

- Q<sub>Elec</sub> = Nominal electrical power (W)

- Q<sub>Illum</sub> = Absorbed illumination heat (W)

- $P_D$  = Illumination power density

• A = Illumination area on DMD

An example calculation is provided in  $\pm$  4 and  $\pm$  5. DMD electrical power dissipation varies and depends on the voltage, data rates, and operating frequencies. The nominal electrical power dissipation is used in this calculation with a power density of 2 W/cm<sup>2</sup>, an illumination area of 0.725 cm<sup>2</sup>, and a ceramic case temperature at TP1 of 55°C. The DMD absorption constant of 0.42 assumes nominal operation with an illumination distribution of 83.7% on the active array, 11.9% on the array border, and 4.4% on the window aperture. A system aperture may be required to limit power incident on the package aperture since this area absorbs much more efficiently than the array . Using these values in the previous equations, the following values are computed:

$$Q_{Arrav} = Q_{Elec} + Q_{IIlum} = 0.442 W + (2 W/cm^2 \times 0.725 cm^2 \times 0.42) = 1.05 W$$

(4)

$T_{Array} = T_{Ceramic} + (Q_{Array} \times R_{Array-To-Ceramic}) = 55^{\circ}C + (1.05 \text{ W} \times 2^{\circ}C/W) = 57.1^{\circ}C$ (5)

#### 8.6 Micromirror Landed-on/Landed-Off Duty Cycle

#### 8.6.1 Definition of Micromirror Landed-On/Landed-Off Duty Cycle

The micromirror landed-on/landed-off duty cycle (landed duty cycle) denotes the amount of time (as a percentage) that an individual micromirror is landed in the On–state versus the amount of time the same micromirror is landed in the Off–state.

As an example, a landed duty cycle of 75/25 indicates that the referenced micromirror is in the On–state 75% of the time (and in the Off–state 25% of the time); whereas 25/75 would indicate that the micromirror is in the On–state 25% of the time. Likewise, 50/50 indicates that the micromirror is On 50% of the time and Off 50% of the time.

Note that when assessing landed duty cycle, the time spent switching from one state (ON or OFF) to the other state (OFF or ON) is considered negligible and is thus ignored.

Since a micromirror can only be landed in one state or the other (ON or OFF), the two numbers (percentages) always add to 100.

#### 8.6.2 Landed Duty Cycle and Useful Life of the DMD

Knowing the long-term average landed duty cycle (of the end product or application) is important because subjecting all (or a portion) of the DMD's micromirror array (also called the active array) to an asymmetric landed duty cycle for a prolonged period of time can reduce the DMD's usable life.

The symmetry of the landed duty cycle is determined by how close the On-state and Off-state percentages are to being equal. For example, a landed duty cycle of 50/50 is perfectly symmetrical whereas a landed duty cycle of 100/0 or 0/100 is perfectly asymmetrical.

For extended useful lifetime of the DMD, it is strongly recommended not to put any individual pixel in a 100/0 or 0/100 duty cycle for prolonged periods of time. It's recommended as much as possible to put the DMD in a 50/50 duty cycle across the entire DMD mirror array, where all the mirrors are continuously flipped between the on and off states. A few examples when the DMD could be in a 50/50 duty cycle mode include: when the system is idle, the illumination is disabled, between sequential pattern exposures, or when the exposure pattern sequence is stopped for any reason.

#### 8.6.3 Landed Duty Cycle and Operational DMD Temperature

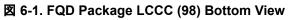

Operational DMD temperature and landed duty cycle interact to affect the DMD's usable life, and this interaction can be exploited to reduce the impact that an asymmetrical landed duty cycle has on the DMD's usable life. This is quantified in the de-rating curve shown in  $\mathbb{Z}$  7-1. The importance of this curve is that:

- All points along this curve represent the same usable life.

- All points above this curve represent lower usable life (and the further away from the curve, the lower the usable life).

• All points below this curve represent higher usable life (and the further away from the curve, the higher the usable life).

In practice, this curve specifies the maximum operating DMD temperature for a given long-term average landed duty cycle.

#### 8.6.4 Estimating the Long-Term Average Landed Duty Cycle of a Product or Application

During a given period of time, the landed duty cycle of a given micromirror follows from the image content being displayed by that micromirror.

For example, in the simplest case, when displaying pure-white on a given micromirror for a given time period, that micromirror experiences a 100/0 landed duty cycle during that time period. Likewise, when displaying pure-black, the micromirror experiences a 0/100 landed duty cycle.

Between the two extremes (ignoring for the moment color and any image processing that may be applied to an incoming image), the landed duty cycle tracks one-to-one with the linear gray scale value, as shown in  $\frac{1}{5}$  8-2.

| GRAYSCALE VALUE | NOMINAL LANDED DUTY<br>CYCLE |

|-----------------|------------------------------|

| 0%              | 0/100                        |

| 10%             | 10/90                        |

| 20%             | 20/80                        |

| 30%             | 30/70                        |

| 40%             | 40/60                        |

| 50%             | 50/50                        |

| 60%             | 60/40                        |

| 70%             | 70/30                        |

| 80%             | 80/20                        |

| 90%             | 90/10                        |

| 100%            | 100/0                        |

表 8-2. Grayscale Value and Landed Duty Cycle

Accounting for color rendition (but still ignoring image processing) requires knowing both the color intensity (from 0% to 100%) for each constituent primary color (red, green, and/or blue) for the given micromirror as well as the color cycle time for each primary color, where "color cycle time" is the total percentage of the frame time that a given primary must be displayed in order to achieve the desired white point.

During a given period of time, the landed duty cycle of a given micromirror can be calculated as follows:

```

Landed Duty Cycle = (Red_Cycle_% × Red_Scale_Value) + (Green_Cycle_% × Green_Scale_Value) + (Blue_Cycle_% (6)

× Blue_Scale_Value)

```

#### where

• Red\_Cycle\_%, Green\_Cycle\_%, and Blue\_Cycle\_%, represent the percentage of the frame time that Red, Green, and Blue are displayed (respectively) to achieve the desired white point.

For example, assume that the red, green and blue color cycle times are 50%, 20%, and 30% respectively (in order to achieve the desired white point), then the landed duty cycle for various combinations of red, green, blue color intensities would be as shown in  $\frac{1}{5}$  8-3.

When used with a single near-IR LED, the landed duty cycle of the DLP4500NIR device depends on the single LED cycle time and the scale value.

For example, assume the LED cycle time is 100% and the scale value is 80%, then the landed duty cycle is 80/20.

| RED CYCLE PERCENTAGE<br>50% | GREEN CYCLE PERCENTAGE 20% | BLUE CYCLE PERCENTAGE<br>30% | NOMINAL LANDED DUTY<br>CYCLE |

|-----------------------------|----------------------------|------------------------------|------------------------------|

| RED SCALE VALUE             | GREEN SCALE VALUE          | BLUE SCALE VALUE             | CTOLE                        |

| 0%                          | 0%                         | 0%                           | 0/100                        |

| 100%                        | 0%                         | 0%                           | 50/50                        |

| 0%                          | 100%                       | 0%                           | 20/80                        |

| 0%                          | 0%                         | 100%                         | 30/70                        |

| 12%                         | 0%                         | 0%                           | 6/94                         |

| 0%                          | 35%                        | 0%                           | 7/93                         |

| 0%                          | 0%                         | 60%                          | 18/82                        |

| 100%                        | 100%                       | 0%                           | 70/30                        |

| 0%                          | 100%                       | 100%                         | 50/50                        |

| 100%                        | 0%                         | 100%                         | 80/20                        |

| 12%                         | 35%                        | 0%                           | 13/87                        |

| 0%                          | 35%                        | 60%                          | 25/75                        |

| 12%                         | 0%                         | 60%                          | 24/76                        |

| 100%                        | 100%                       | 100%                         | 100/0                        |

#### 表 8-3. Example Landed Duty Cycle for Full-Color

### 9 Applications and Implementation

Note

以下のアプリケーション情報は、TIの製品仕様に含まれるものではなく、TIではその正確性または 完全性を保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断して いただくことになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確 認する必要があります。

### 9.1 Application Information

For reliable operation, the DLP4500NIR DMD must be coupled with the DLPC350 controller. The DMD is a spatial light modulator which reflects incoming light from an illumination source to one of two directions, with the primary direction being into a projection or collection optic. Each application is derived primarily from the optical architecture of the system and the format of the data coming into the DLPC350. Applications of interest include 3D measurement systems, spectrometers, medical systems, and compressive sensing.

### 9.2 Typical Application

☑ 9-1 shows a typical embedded system application using the DLPC350 controller and DLP4500NIR DMD. In this configuration, the DLPC350 controller supports a 24-bit parallel RGB input from an external source or processor. In this system, the external processor controls the near-IR lamp and sends structured light patterns to the DLPC350. The near-IR radiation is projected through a liquid sample where the non-absorbed spectra is transmitted through an entrance slit and onto a diffraction grating. Diffracted light of varying wavelengths is then focused onto the DMD. The DLPC350 uses patterns to scan across the DMD thereby selecting specific wavelengths of light which are then focused onto a single point InGaAs detector. The external processor samples the outputs of the InGaAs detector to create an absorbance curve of the sample.

図 9-1. Typical Application Schematic

#### 9.2.1 Design Requirements

All applications using the DLP4500NIR chipset require both the controller and DMD components for operation. The system also requires an external parallel flash memory device loaded with the DLPC350 configuration and support firmware. The chipset has several system interfaces and requires some support circuitry. The following interfaces and support circuitry are required:

- DLPC350 system interfaces:

- Control interface

- Trigger interface

- Input data interface

- Illumination interface

- DLPC350 support circuitry and interfaces:

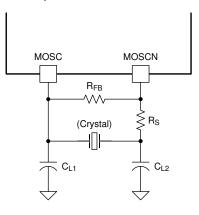

- Reference clock

- PLL

- Program memory flash interface

- DMD interfaces:

- DLPC350 to DMD digital data

- DLPC350 to DMD control interface

- DLPC350 to DMD micromirror reset control interface

#### 9.2.2 Detailed Design Procedure

#### 9.2.2.1 DLPC350 System Interfaces

The DLP4500NIR chipset supports a 30-bit parallel RGB interface for image data transfers from another device and a 30-bit interface for video data transfers. The system input requires proper generation of the PWRGOOD and POSENSE inputs to ensure reliable operation. The two primary output interfaces are the illumination driver control interface and sync outputs.

#### 9.2.2.1.1 Control Interface

The DLP4500NIR chipset accepts control interface commands via the I<sup>2</sup>C or USB input buses. The control interface allows another master processor to send commands to the DLP4500NIR chipset to query system status or perform realtime operations such as programming LED driver current settings.