**DRV8161, DRV8162** JAJSUL1A - MAY 2024 - REVISED JULY 2024

# DRV816x 保護機能および電流センス アンプ搭載、100V ハーフブリッジ スマ ート ゲート ドライバ

## 1 特長

- ハーフブリッジ構成の 2 つの N チャネル MOSFET を

- ハイサイド MOSFET ソース / ドレイン最大 102V (絶対最大定格)

- 8V (5V DRV8162L)~20V のゲートドライブ電源

- ブートストラップ ダイオードを内蔵

- 16 レベルのゲートドライブ ピーク電流

- 16mA~1000mA ソース電流

- 32mA~2000mA シンク電流

- ソース シンク電流比 1:1、1:2、1:3

- 可変 PWM デッド タイム挿入 20ns~400ns

- モーター位相 (SH) スイッチング向けの堅牢な設計

- スルーレート 20V/µs

- 負の過渡電圧 -20V

- 2A の強力なゲート プルダウン

- 冗長シャットダウン用にゲート駆動電源入力を分割 (DRV8162, DRV8162L)

- 低オフセットの電流センス アンプ (DRV8161)

- 可変ゲイン (5、10、20、40V/V)

- 柔軟な PWM 制御インターフェイス、2 ピン PWM、独 立 PWM モード

- 13 レベル VDS 過電流スレッショルド

- 独立したシャットダウンピン (nDRVOFF)

- ゲートドライバ ソフト シャットダウン シーケンス

- 保護機能内蔵

- GVDD 低電圧 (GVDDUV)

- ブートストラップ低電圧 (BST UV)

- MOSFET 過電流保護 (VDS)

- 貫通電流保護

- サーマル シャットダウン (OTSD)

- フォルト状態インジケータ (nFAULT)

- 3.3V および 5V のロジック入力をサポート

# 2 アプリケーション

- 産業用ロボット/協力ロボット(コボット)

- 移動ロボット (AGV/AMR)

- リニア モーター輸送用システム

- サーボドライブ

- ドローン

- 電動アシスト自転車、電動スクーター、E-モビリティ

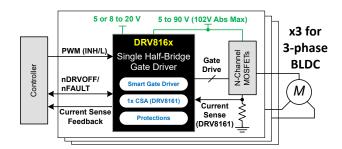

### 3 概要

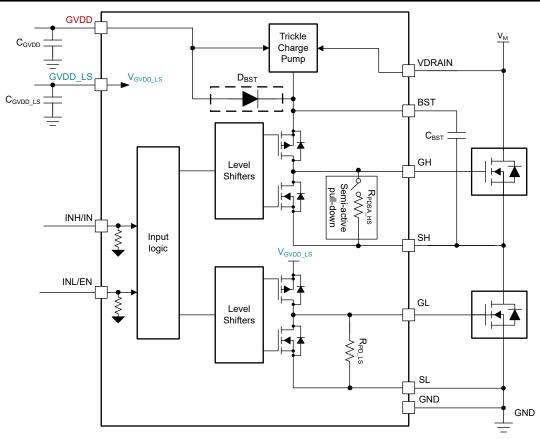

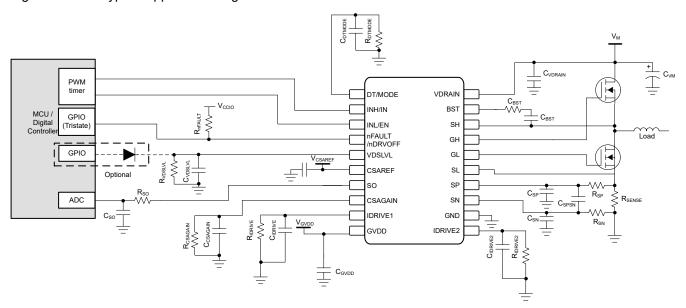

DRV816x は、ハイサイドおよびローサイドの N チャネル パワー MOSFET を駆動できる、ハーフ ブリッジ ゲートド ライバです。ゲート駆動電圧は GVDD 電源ピンから生成 され、内蔵ブートストラップ回路はハイサイド FET を最大 102V ドレインまで駆動するために使用されます。 スマート ゲート ドライブ アーキテクチャは、最大でソース 1A、シン ク 2A の 16 レベル (48 通りの組み合わせ) のゲート駆動 ピーク電流をサポートし、ゲート駆動電流の内蔵タイミング 制御機能も搭載しています。これらのデバイスを使用し て、ブラシレス / ブラシ付き DC モータ、PMSM、ステッピ ング モータ、SRM、ソレノイドなど、各種の負荷を駆動でき ます。

電源低電圧、FET 過電流、ダイ過熱に対する保護機能が 内蔵されています。 nFAULT ピンは、保護機能によって検 出されたフォルト イベントを通知します。 nDRVOFF ピン は、PWM 制御から独立して電力段のシャットダウンを開 始します。DRV8162 および DRV8162L デバイスは、セ ーフトルクオフ (STO) 機能を補助するために、分割電源 アーキテクチャを採用しています。

ゲート駆動電流、デッドタイム、PWM 制御インターフェイ ス、過電流検出など、デバイスの多くのパラメータは、いく つかの受動部品をデバイスのピンに接続して構成できま す。 内蔵のローサイド電流センス アンプ (DRV8161) は、 電流測定情報をコントローラに返します。

#### 製品情報

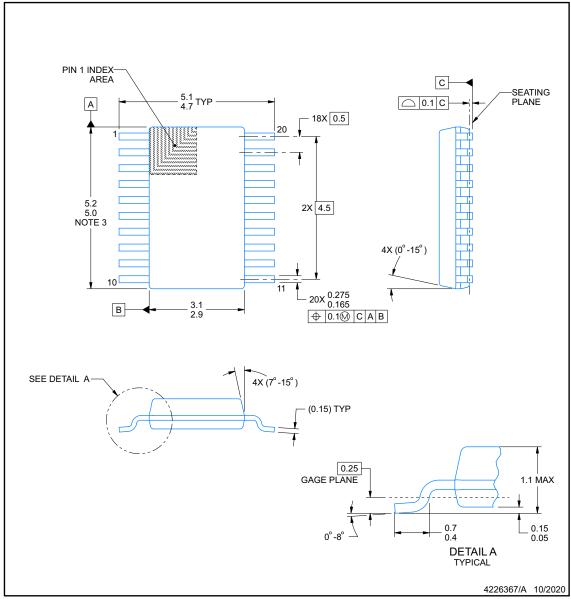

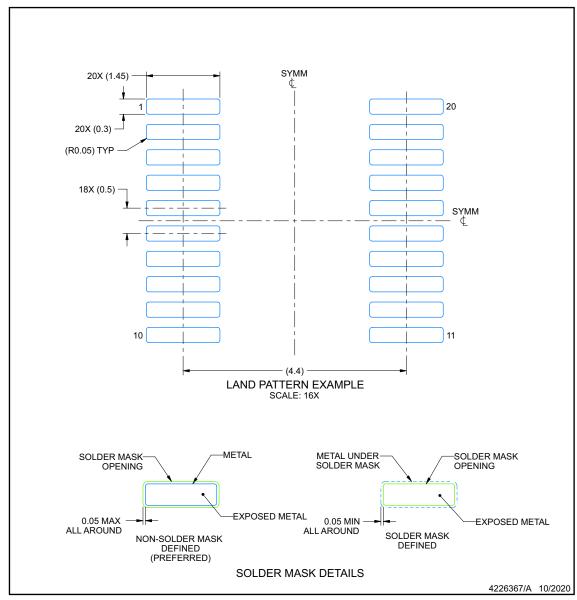

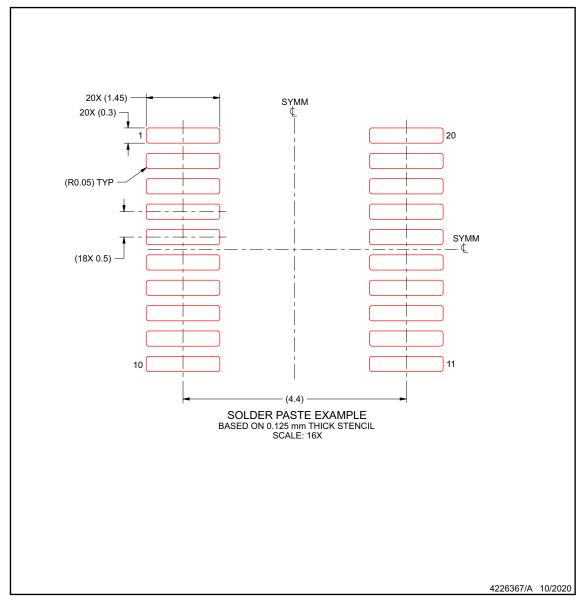

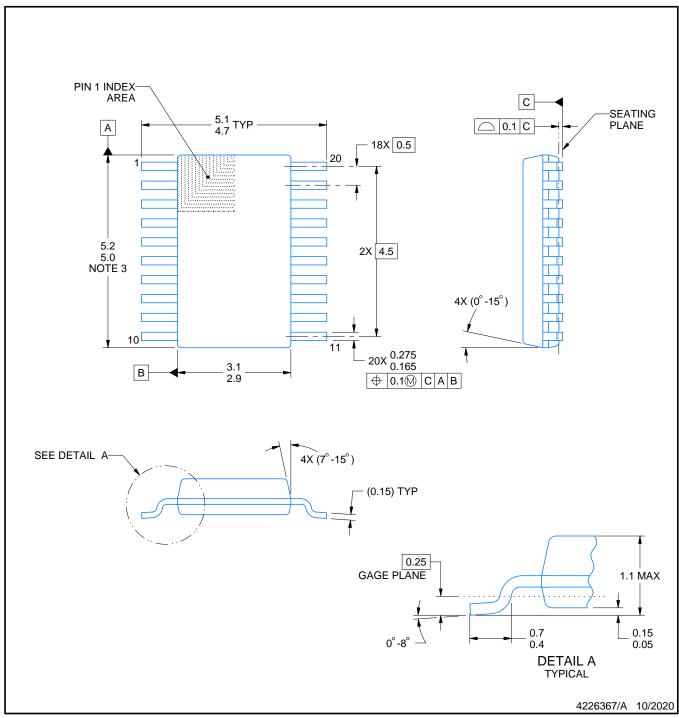

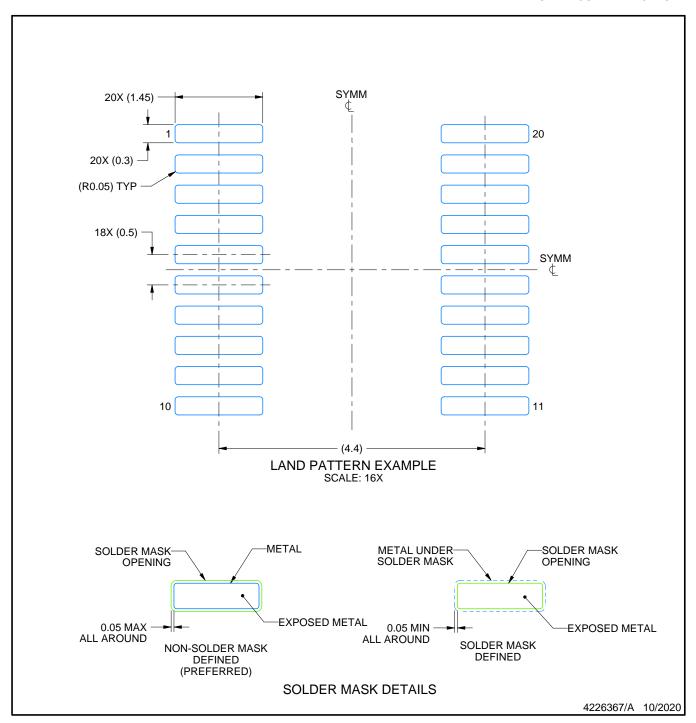

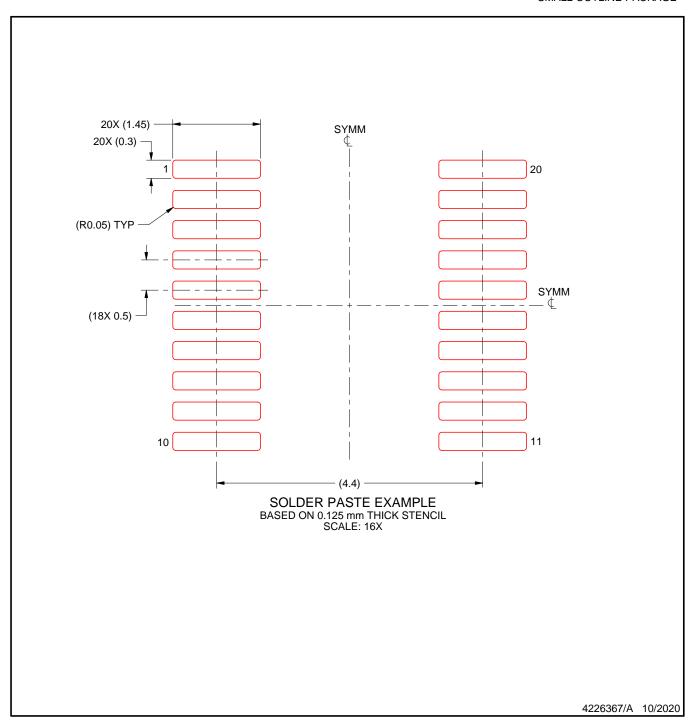

| 部品番号                   | パッケージ <sup>(1)</sup> | 本体サイズ (公称)    |

|------------------------|----------------------|---------------|

| DRV8161                | VSSOP (20)           | 5.1mm × 3.0mm |

| DRV8162 <sup>(2)</sup> | VSSOP (20)           | 5.1mm × 3.0mm |

- 詳細については、セクション 12 を参照してください。 (1)

- DRV8162 (製品プレビュー) および DRV8162L (事前情報) のデ バイス バリアントが含まれます。「 Device Comparison Table 」を 参照してください。

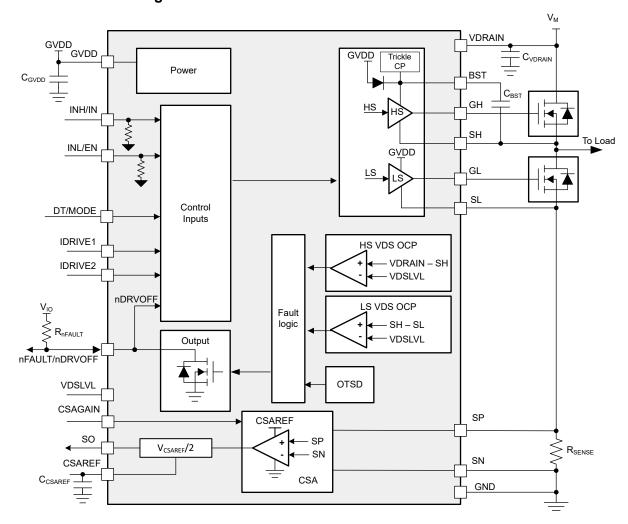

DRV816x の概略回路図

# **Table of Contents**

| 1 | 特長                                   | <mark>1</mark> |

|---|--------------------------------------|----------------|

| 2 | アプリケーション                             | 1              |

|   | 概要                                   |                |

|   | Device Comparison Table              |                |

|   | Pin Configuration and Functions      |                |

|   | Specification                        |                |

| Ī | 6.1 Absolute Maximum Ratings         |                |

|   | 6.2 ESD Ratings                      |                |

|   | 6.3 Recommended Operating Conditions |                |

|   | 6.4 Thermal Information 1pkg         |                |

|   | 6.5 Electrical Characteristics       |                |

|   | 6.6 Timing Diagrams                  |                |

| 7 | Detailed Description                 |                |

|   | 7.1 Overview                         |                |

|   | 7.2 Functional Block Diagram         |                |

|   | 7.3 Feature Description              |                |

|   |                                      |                |

| 8 Application and Implementation                     | 33 |

|------------------------------------------------------|----|

| 8.1 Application Information                          | 33 |

| 8.2 Typical Application                              | 33 |

| 9 Layout                                             | 36 |

| 9.1 Layout Guidelines                                | 36 |

| 10 Device and Documentation Support                  | 37 |

| 10.1 Device Support                                  | 37 |

| 10.2 Documentation Support                           | 37 |

| 10.3 Receiving Notification of Documentation Updates | 37 |

| 10.4 Community Resources                             | 37 |

| 10.5 Trademarks                                      | 37 |

| 11 Revision History                                  | 37 |

| 12 Mechanical, Packaging, and Orderable              |    |

| Information                                          | 37 |

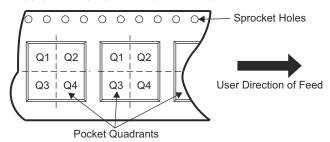

| 12.1 Tape and Reel Information                       | 41 |

# **4 Device Comparison Table**

| DEVICE  | DEVICE<br>VARIANT       | PACKAGE<br>PIN COUNT | CURRENT SENSE<br>AMPLIFIER | GATE DRIVE POWER SUPPLY | MIN GVDD<br>OPERATION | Control Mode           |

|---------|-------------------------|----------------------|----------------------------|-------------------------|-----------------------|------------------------|

| DRV8161 | DRV8161 <sup>(1)</sup>  |                      | YES                        | GVDD                    | 8-V                   |                        |

| DRV8162 | DRV8162 <sup>(2)</sup>  | 20                   | No                         | GVDD and GVDD_LS        | 8-V                   | 2-pin, Independent FET |

|         | DRV8162L <sup>(1)</sup> |                      |                            |                         | 5-V                   |                        |

- (1) Advance Information. The products are in sampling and preproduction phase.

- (2) Product Preview. The product is in the formative or design phase. Contact TI for more information.

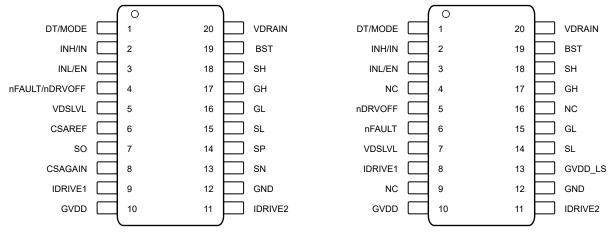

## 5 Pin Configuration and Functions

図 5-1. DRV8161 (Advance Information) DGS Package 20-pin VSSOP Top View

図 5-2. DRV8162 (Product Preview) and DRV8162L (Advance Information) DGS Package 20-pin VSSOP Top View

#### 表 5-1. Pin Functions—DRV816x Devices

|                    | PIN                                              |       |      |                                                                                                                                                                                                                                                                                          |  |  |

|--------------------|--------------------------------------------------|-------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                    | N                                                | О.    | TYPE |                                                                                                                                                                                                                                                                                          |  |  |

| NAME               | DRV8161<br>20-pin DRV8162,<br>DRV8162L<br>20-pin |       | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                              |  |  |

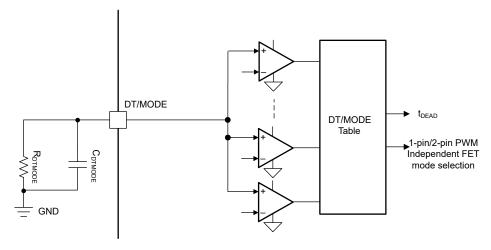

| DT/MODE            | 1                                                | 1     | I    | Selects input pin interface logic and gate drive dead time setting. Connect a resistor between DT and GND to adjust dead time between 20 ns to 1000 ns, and select a PWM mode.                                                                                                           |  |  |

| INLH/IN            | 2                                                | 2     | I    | Gate driver control input. Gate driver control depends on DT/MODE pin setting.                                                                                                                                                                                                           |  |  |

| INL/EN             | 3                                                | 3     | I    | Gate driver control input. Gate driver control depends on DT/MODE pin setting.  No Connect. Leave open.                                                                                                                                                                                  |  |  |

| NC                 | _                                                | 4     | N/A  | No Connect. Leave open.                                                                                                                                                                                                                                                                  |  |  |

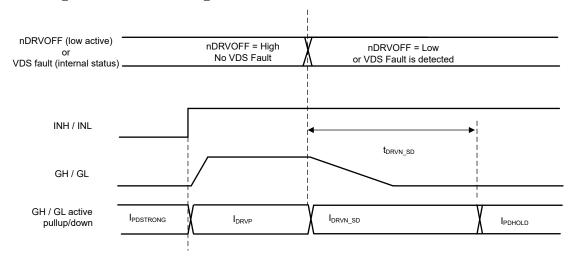

| nDRVOFF            | _                                                | 5     | ı    | Gate driver shutdown control. Pulling nDRVOFF low turns off high-side and low-side external MOSFETs by putting the gate drivers into the pull-down state.                                                                                                                                |  |  |

| nFAULT/<br>nDRVOFF | 4                                                | _     | I/OD | Shared fault indicator pin and gate driver shutdown pin. Connect this pin to an external pull-up resistor to the controller supply or a controller output pin. This pin is pulled logic low during a fault condition. To active gate drive shutdown, pull the pin low by external logic. |  |  |

| nFAULT             | _                                                | 6     | OD   | Fault indicator output. This pin is pulled logic low during a fault condition and requires an external pull-up resistor to controller I/O supply, 3.3V to 5.0V.                                                                                                                          |  |  |

| VDSLVL             | 5                                                | 7     | 1    | VDS monitor threshold setting. This pin is a multilevel input pin set by an external resistor.                                                                                                                                                                                           |  |  |

| CSAREF             | 6                                                | _     | PWR  | Current sense amplifier reference. Connect a capacitor between the CSAREF and GND pins.                                                                                                                                                                                                  |  |  |

| so                 | 7                                                | _     | 0    | Current sense amplifier output.                                                                                                                                                                                                                                                          |  |  |

| CSAGAIN            | 8                                                | _     | 1    | Gain settings for current sense amplifier. This pin is a multilevel input pin set by an external resistor.                                                                                                                                                                               |  |  |

| IDRIVE1            | 9                                                | 8     | ı    | Gate drive source and sink current setting. This pin is a multilevel input pin set by an external resistor.                                                                                                                                                                              |  |  |

| NC                 |                                                  | 9, 16 |      | No Connect. Leave open.                                                                                                                                                                                                                                                                  |  |  |

| GVDD               | 10                                               | 10    | PWR  | Gate driver power supply input. Connect a capacitor between the GVDD and GND pins.                                                                                                                                                                                                       |  |  |

資料に関するフィードバック(ご意見やお問い合わせ) を送信

Copyright © 2024 Texas Instruments Incorporated

1

## 表 5-1. Pin Functions—DRV816x Devices (続き)

|             | PIN                              |    |      |                                                                                                                                                                 |  |

|-------------|----------------------------------|----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|             | N                                | 0. |      |                                                                                                                                                                 |  |

| NAME        | DRV8161 DRV8162, DRV8162L 20-pin |    | TYPE | DESCRIPTION                                                                                                                                                     |  |

| IDRIVE2     | 11                               | 11 | I    | Gate drive source and sink current setting. This pin is a multilevel input pin set by an external resistor.                                                     |  |

| GND         | 12                               | 12 | PWR  | Device ground.                                                                                                                                                  |  |

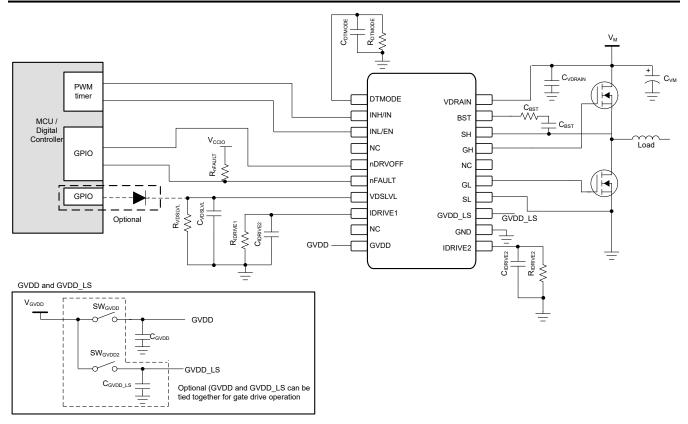

| GVDD_LS     | _                                | 13 | PWR  | Low-side gate driver power supply input (DRV8162 and DRV8162L only). Connect a capacitor between the GVDD_LS and GND pins.                                      |  |

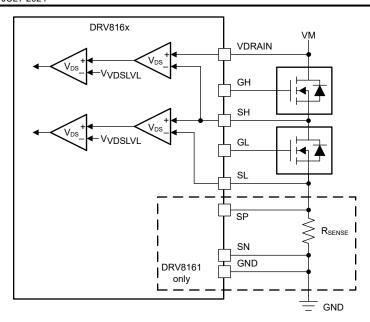

| SN          | 13                               | _  | I    | Current sense amplifier input. Connect to the low-side of the current shunt resistor.                                                                           |  |

| SP          | 14                               | _  | I    | Current shunt amplifier input. Connect to the low-side power MOSFET source and high-side of the current shunt resistor.                                         |  |

| SL          | 15                               | 14 | I    | Low-side source pin. Connect to the low-side power MOSFET source. This pin is an input for the VDS monitor and the output for the low-side gate driver sink.    |  |

| GL          | 16                               | 15 | 0    | Low-side gate driver output. Connect to the gate of the low-side power MOSFET.                                                                                  |  |

| GH          | 17                               | 17 | 0    | High-side gate driver output. Connect to the gate of the high-side power MOSFET.                                                                                |  |

| SH          | 18                               | 18 | I    | High-side source pin. Connect to the high-side power MOSFET source. This pin is an input for the VDS monitor and the output for the high-side gate driver sink. |  |

| BST         | 19                               | 19 | 0    | Bootstrap output pin. Connect a capacitor between BST and SH.                                                                                                   |  |

| VDRAIN      | 20                               | 20 | PWR  | High-side MOSFET drain sense input for VDS monitor and charge pump reference. Connect to the high-side MOSFET drain.                                            |  |

| THERMAL PAI | D                                |    | PWR  | Leave open, or tied to GND                                                                                                                                      |  |

PWR = power, I = input, O = output, NC = no connection, OD = open-drain output

### 6 Specification

### **6.1 Absolute Maximum Ratings**

Over recommended operating conditions (unless otherwise noted)(1)

|                                                                                                                                  |                                          | MIN  | MAX                       | UNIT |

|----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|------|---------------------------|------|

| Gate driver regulator pin voltage                                                                                                | GVDD, GVDD_LS                            | -0.3 | 20                        | V    |

| High-side drain pin voltage                                                                                                      | VDRAIN, T <sub>J</sub> = 25°C            | -0.3 | 102                       | V    |

| Bootstrap pin voltage                                                                                                            | BST, T <sub>J</sub> = 25°C               | -0.3 | 115                       | V    |

| Bootstrap pin voltage                                                                                                            | BST with respect to SH                   | -0.3 | 20                        | V    |

|                                                                                                                                  | nFAULT                                   | -0.3 | 20                        |      |

| Logic pin voltage                                                                                                                | INH(IN), INL(EN), nDRVOFF, VDSLVL        | -0.3 | 20                        | V    |

| n-side gate drive pin voltage n-side source pin voltage nsient high-side source pin negative voltage n-side source pin slew rate | DT/MODE, IDRIVE1, IDRIVE2,<br>CSAGAIN    | -0.3 | 6                         | V    |

| High-side gate drive pin voltage                                                                                                 | GH, T <sub>J</sub> = 25°C<br>GVDD >= 11V | -5   | 115                       | V    |

| High-side gate drive pin voltage                                                                                                 | GH with respect to SH                    | -0.3 | 20                        | V    |

| High-side source pin voltage                                                                                                     | SH, DC                                   | -5   | 105                       | V    |

| Transient high-side source pin negative voltage                                                                                  | SH, 1 µs                                 | -20  |                           | V    |

| High-side source pin slew rate                                                                                                   | SH , V <sub>BST-SH</sub> >3.5V           |      | 20                        | V/ns |

| Low-side gate drive pin voltage                                                                                                  | GL with respect to SL                    | -0.3 | 20                        | V    |

| Low-side source sense pin voltage                                                                                                | SL                                       | -5   | V <sub>GVDD</sub> +0.3    | V    |

| Transient low-side source sense pin negative voltage                                                                             | SL, 1 µs                                 | -16  |                           | V    |

| Current sense amplifier reference input pin voltage                                                                              | CSAREF                                   | -0.3 | 5.5                       | V    |

| Shunt amplifier input pin voltage                                                                                                | SN, SP                                   | -1   | 1                         | V    |

| Transient 500-ns shunt amplifier input pin voltage                                                                               | SN, SP, 500ns                            | -16  | 20                        | V    |

| Shunt amplifier output pin voltage                                                                                               | so                                       | -0.3 | V <sub>CSAREF</sub> + 0.3 | V    |

| Junction temperature, T <sub>J</sub>                                                                                             |                                          | -40  | 150                       | °C   |

| Storage temperature, T <sub>stg</sub>                                                                                            |                                          | -65  | 150                       | °C   |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime

### 6.2 ESD Ratings

|                    |               |                                                                       | VALUE | UNIT |

|--------------------|---------------|-----------------------------------------------------------------------|-------|------|

| V                  | Electrostatic | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>     | ±1000 | \/   |

| V <sub>(ESD)</sub> | discharge     | Charged device model (CDM), per ANSI/ESDA/JEDEC JS-002 <sup>(2)</sup> | ±250  | V    |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

資料に関するフィードバック(ご意見やお問い合わせ)を送信

# **6.3 Recommended Operating Conditions**

over operating temperature range (unless otherwise noted)

|                     |                                                         |                                                                                                                                                                                             | MIN | NOM | MAX | UNIT |

|---------------------|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

|                     | Power supply voltage                                    | GVDD, GVDD_LS                                                                                                                                                                               | 8   |     |     | V    |

| $V_{GVDD}$          | Power supply voltage (DRV8162L only)                    | GVDD, GVDD_LS, DRV8162L device variant                                                                                                                                                      | 5   |     | 20  | V    |

| $V_{GVDD-SL}$       | Power supply voltage with respect to SL                 | GVDD(DRV8161), GVDD_LS<br>(DRV8162x) for low-side Pre-Driver<br>PWM operation                                                                                                               | 3.5 |     |     | V    |

| V <sub>VDRAIN</sub> | High-side drain pin voltage                             | VDRAIN, low-side gate drive, and high-<br>side gate drive switching with bootstrap                                                                                                          | 0   |     | 90  | V    |

|                     | Bootstrap pin voltage with respect to SH                | BST (V <sub>BST</sub> - V <sub>SH</sub> ), high-side gate drive switching and no BST_UV detection, V <sub>BST-SH</sub> min > V <sub>BST_UV</sub> max (rising),                              | 6.1 |     |     | V    |

| V <sub>BST-SH</sub> | Bootstrap pin voltage with respect to SH (DRV8162Lonly) | BST (V <sub>BST</sub> - V <sub>SH</sub> ), DRV8162L device variant only, high-side gate drive switching and no BST_UV detection, V <sub>BST-SH</sub> min > V <sub>BST_UV</sub> max (rising) | 4.6 |     | 20  | V    |

| V <sub>BST</sub>    | Bootstrap pin voltage                                   | BST                                                                                                                                                                                         | 0   |     | 105 | V    |

| V <sub>SH</sub>     | High-side source pin voltage                            | SH                                                                                                                                                                                          | -2  |     | 95  | V    |

| VI                  | Digital / Pin detection input voltage                   | INH, INL, IDRIVE1, IDRIVE2, GAIN, VDSLVL                                                                                                                                                    | 0   |     | 5.5 | V    |

| V <sub>OD</sub>     | Open drain pullup voltage                               | nFAULT                                                                                                                                                                                      |     |     | 5.5 | V    |

| I <sub>OD</sub>     | Open drain output current                               | nFAULT                                                                                                                                                                                      |     |     | -5  | mA   |

| V <sub>CSAREF</sub> | Current sense amplifier reference voltage               | CSAREF                                                                                                                                                                                      | 3.0 |     | 5.5 | V    |

| T <sub>A</sub>      | Operating ambient temperature                           |                                                                                                                                                                                             | -40 |     | 125 | °C   |

| T <sub>J</sub>      | Operating junction temperature                          |                                                                                                                                                                                             | -40 |     | 150 | °C   |

## 6.4 Thermal Information 1pkg

|                       |                                              | DRV8161/DRV8162 |      |

|-----------------------|----------------------------------------------|-----------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | DGS(VSSOP)      | UNIT |

|                       |                                              | 20 PINS         |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | TBD             | °C/W |

| R <sub>θJC(top)</sub> | Junction-to-case (top) thermal resistance    | TBD             | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | TBD             | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | TBD             | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | TBD             | °C/W |

| $R_{\theta JC(bot)}$  | Junction-to-case (bottom) thermal resistance | TBD             | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

### 6.5 Electrical Characteristics

$V_{GVDD}$  = 12 V,  $V_{VDRAIN}$  = 48 V, CSAREF = 5V,  $T_J$  = 25°C (unless otherwise noted)

|                               | PARAMETER                                                           | TEST CONDITIONS                                                                                                                                                  | MIN | TYP | MAX | UNIT |

|-------------------------------|---------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| POWER SUF                     | PPLIES (GVDD, BST)                                                  |                                                                                                                                                                  |     |     | '   |      |

| I <sub>VDRAIN_UNP</sub><br>WR | VDRAIN leakage current under GVDD unpowered                         | GVDD = 0V, VDRAIN = 48V, V <sub>BST-SH</sub> = 0V                                                                                                                |     | 3.5 | 5   | μΑ   |

| $I_{GVDD}$                    | GVDD active mode current                                            | INH = INL = Switching @ 20kHz; $V_{BST}$ = $V_{GVDD}$ ; No FETs connected, DT/MODE Pin open. VDS_LVL = 2V                                                        |     | 2   |     | mA   |

| t <sub>WAKE</sub>             | Turnon time                                                         | GVDD = 0V to 12V V <sub>GVDD</sub> = V <sub>GVDD_UV</sub> to active mode (outputs ready : nFAULT = High)                                                         |     | 0.4 |     | ms   |

| IL <sub>BS_TCPON</sub>        | Bootstrap pin leakage current during high-side pull-up              | INH = high; TCP_ON                                                                                                                                               |     | 30  |     | μΑ   |

| LOGIC-LEVE                    | EL INPUTS (INH, INL, nDRVOFF)                                       |                                                                                                                                                                  |     |     |     |      |

| V <sub>IL</sub>               | Input logic low voltage                                             | INL, INH, nDRVOFF                                                                                                                                                |     |     | 0.8 | V    |

| V <sub>IH</sub>               | Input logic high voltage                                            | INL, INH, nDRVOFF                                                                                                                                                | 2.2 |     |     | V    |

| R <sub>PU</sub>               | Input pullup resistance                                             | nDRVOFF to internal regulator, no external connection                                                                                                            |     | 250 |     | kΩ   |

| R <sub>PD</sub>               | Input pulldown resistance                                           | INH, INL to GND                                                                                                                                                  |     | 250 |     | kΩ   |

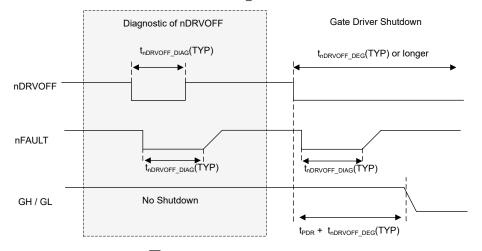

| t <sub>nDRVOFF_DE</sub><br>G  | nDRVOFF input deglitch time                                         | nDRVOFF falling and rising                                                                                                                                       |     | 2.1 |     | μs   |

| t <sub>nDRVOFF_DIA</sub><br>G | nDRVOFF diagnostic pulse valid input time                           | DRV8162 and DRV8162L only                                                                                                                                        |     | 0.5 |     | μs   |

| OPEN-DRAI                     | N OUTPUT (nFAULT)                                                   |                                                                                                                                                                  |     |     |     |      |

| V <sub>OL</sub>               | Output logic low voltage                                            | I <sub>OD</sub> = 5 mA, GVDD > 4V                                                                                                                                |     |     | 0.4 | V    |

| BOOTSTRA                      | P DIODE (BST)                                                       |                                                                                                                                                                  |     |     |     |      |

| V                             | Bootstrap diode forward voltage                                     | I <sub>BOOT</sub> = 10 mA                                                                                                                                        |     | 0.8 |     | V    |

| $V_{BOOTD}$                   | Bootstrap diode forward voltage                                     | I <sub>BOOT</sub> = 100 mA                                                                                                                                       |     | 1.3 |     | V    |

| R <sub>BOOTD</sub>            | Bootstrap dynamic resistance ( $\Delta V_{BOOTD}/\Delta I_{BOOT}$ ) | I <sub>BOOT</sub> = 100 mA and 50 mA                                                                                                                             |     | 4.8 |     | Ω    |

| CHARGE PU                     | JMP (BST)                                                           |                                                                                                                                                                  |     |     |     |      |

| V                             | Trickle charge nump output voltage                                  | $V_{\rm BST-SH}$ , INH = High, $V_{\rm SH}$ = $V_{\rm VDRAIN}$ = 20V, $V_{\rm BST}$ > $V_{\rm GVDD}$ , External load $I_{\rm TRICKLE}$ = 2uA, $T_{\rm J}$ = 25°C |     | 8.5 |     | V    |

| V <sub>TCP</sub>              | Trickle charge pump output voltage                                  | $V_{BST-SH}$ , INH = High, $V_{SH} = V_{VDRAIN} = 20V$ , $V_{BST} > V_{GVDD}$ , External load $I_{TRICKLE} = 2uA$ , $T_J = 150^{\circ}C$                         |     | 4.9 |     | V    |

| GATE DRIVE                    | ERS (GH, GL, SH, SL)                                                |                                                                                                                                                                  |     |     |     |      |

資料に関するフィードバック (ご意見やお問い合わせ) を送信

$V_{GVDD}$  = 12 V,  $V_{VDRAIN}$  = 48 V, CSAREF = 5V,  $T_J$  = 25°C (unless otherwise noted)

|                       | PARAMETER                                 | TEST CONDITIONS                                                                                         | MIN TYP | MAX | UNIT |

|-----------------------|-------------------------------------------|---------------------------------------------------------------------------------------------------------|---------|-----|------|

| I <sub>DRIVEP0</sub>  |                                           | V <sub>BST</sub> -V <sub>SH</sub> = V <sub>GVDD</sub> = 12V                                             | 16      |     |      |

| I <sub>DRIVEP1</sub>  |                                           | V <sub>BST</sub> -V <sub>SH</sub> = V <sub>GVDD</sub> = 12V                                             | 32      |     |      |

| DRIVEP2               |                                           | V <sub>BST</sub> -V <sub>SH</sub> = V <sub>GVDD</sub> = 12V                                             | 64      |     |      |

| DRIVEP3               |                                           | V <sub>BST</sub> -V <sub>SH</sub> = V <sub>GVDD</sub> = 12V                                             | 96      |     |      |

| DRIVEP4               |                                           | V <sub>BST</sub> -V <sub>SH</sub> = V <sub>GVDD</sub> = 12V                                             | 128     |     |      |

| DRIVEP5               |                                           | V <sub>BST</sub> -V <sub>SH</sub> = V <sub>GVDD</sub> = 12V                                             | 160     |     |      |

| DRIVEP6               |                                           | V <sub>BST</sub> -V <sub>SH</sub> = V <sub>GVDD</sub> = 12V                                             | 192     |     |      |

| DRIVEP7               | Dark assumes mate assument                | V <sub>BST</sub> -V <sub>SH</sub> = V <sub>GVDD</sub> = 12V                                             | 224     |     | ^    |

| DRIVEP8               | Peak source gate current                  | V <sub>BST</sub> -V <sub>SH</sub> = V <sub>GVDD</sub> = 12V                                             | 256     |     | mA   |

| DRIVEP9               |                                           | $V_{BST}-V_{SH} = V_{GVDD} = 12V$                                                                       | 288     |     |      |

| DRIVEP10              |                                           | V <sub>BST</sub> -V <sub>SH</sub> = V <sub>GVDD</sub> = 12V                                             | 320     |     |      |

| DRIVEP11              |                                           | V <sub>BST</sub> -V <sub>SH</sub> = V <sub>GVDD</sub> = 12V                                             | 384     |     |      |

| I <sub>DRIVEP12</sub> |                                           | $V_{BST}$ - $V_{SH} = V_{GVDD} = 12V$                                                                   | 448     |     |      |

| DRIVEP13              | V                                         | $V_{BST}$ - $V_{SH}$ = $V_{GVDD}$ = 12 $V$                                                              | 512     |     |      |

| DRIVEP14              |                                           | $V_{BST}$ - $V_{SH} = V_{GVDD} = 12V$                                                                   | 768     |     |      |

| DRIVEP15              |                                           | $V_{BST}$ - $V_{SH}$ = $V_{GVDD}$ = 12 $V$                                                              | 1024    |     |      |

| DRIVEN0               |                                           | V <sub>BST</sub> -V <sub>SH</sub> = V <sub>GVDD</sub> = 12V                                             | 32      |     |      |

| DRIVEN1               |                                           | V <sub>BST</sub> -V <sub>SH</sub> = V <sub>GVDD</sub> = 12V                                             | 64      |     |      |

| DRIVEN2               | Peak sink gate current                    | $V_{BST}$ - $V_{SH} = V_{GVDD} = 12V$                                                                   | 128     |     |      |

| DRIVEN3               |                                           | $V_{BST}$ - $V_{SH} = V_{GVDD} = 12V$                                                                   | 192     |     |      |

| DRIVEN4               |                                           | $V_{BST}$ - $V_{SH} = V_{GVDD} = 12V$                                                                   | 256     |     |      |

| DRIVEN5               |                                           | $V_{BST}$ - $V_{SH} = V_{GVDD} = 12V$                                                                   | 320     |     |      |

| DRIVEN6               |                                           | $V_{BST}$ - $V_{SH} = V_{GVDD} = 12V$                                                                   | 384     |     |      |

| DRIVEN7               |                                           | $V_{BST}$ - $V_{SH} = V_{GVDD} = 12V$                                                                   | 448     |     | mΔ   |

| DRIVEN8               |                                           | $V_{BST}$ - $V_{SH} = V_{GVDD} = 12V$                                                                   | 512     |     | mA   |

| DRIVEN9               |                                           | $V_{BST}$ - $V_{SH} = V_{GVDD} = 12V$                                                                   | 576     |     |      |

| DRIVEN10              |                                           | $V_{BST}$ - $V_{SH} = V_{GVDD} = 12V$                                                                   | 640     |     |      |

| DRIVEN11              |                                           | $V_{BST}$ - $V_{SH} = V_{GVDD} = 12V$                                                                   | 768     |     |      |

| DRIVEN12              |                                           | $V_{BST}$ - $V_{SH} = V_{GVDD} = 12V$                                                                   | 896     |     |      |

| DRIVEN13              |                                           | $V_{BST}$ - $V_{SH} = V_{GVDD} = 12V$                                                                   | 1024    |     |      |

| DRIVEN14              |                                           | $V_{BST}$ - $V_{SH} = V_{GVDD} = 12V$                                                                   | 1536    |     |      |

| DRIVEN15              |                                           | V <sub>BST</sub> -V <sub>SH</sub> = V <sub>GVDD</sub> = 12V                                             | 2048    |     |      |

| R <sub>PD_LS</sub>    | Low-side passive pull down                | GL to SL, $V_{GL} - V_{SL} = 2V$                                                                        | 85      |     | kΩ   |

| R <sub>PDSA_HS</sub>  | High-side semi active pull down           | $V_{GVDD} < V_{GVDD\_UV}$<br>GH to SH, $V_{GH} - V_{SH} = 2V$                                           | 4       |     | kΩ   |

| PUHOLD_HS             | High-side pull-up hold current            |                                                                                                         | 512     |     | mA   |

| PDHOLD_HS             | High-side pull-down hold current          |                                                                                                         | 2048    |     | mA   |

| PDSTRONG_L            | Low-side pull-down strong current         |                                                                                                         | 2048    |     | mA   |

| PDSTRONG_H            | High-side pull-down strong current        |                                                                                                         | 2048    |     | mA   |

| DRVIVENSD_L           | Low-side peak sink gate shutdown current  | I <sub>DRIVENx</sub> is set to I <sub>DRIVEN13</sub> (1024mA<br>Typ) or smaller settings                | 32      |     | mA   |

| DRVIVENSD_L           | Low-side peak sink gate shutdown current  | I <sub>DRIVENx</sub> is set to I <sub>DRIVEN14</sub> (1536mA Typ) or I <sub>DRIVEN15</sub> (2048mA Typ) | 64      |     | mA   |

| DRIVENSD_H            | High-side peak sink gate shutdown current | I <sub>DRIVENx</sub> is set to I <sub>DRIVEN13</sub> (1024mA<br>Typ) or smaller settings                | 32      |     | mA   |

**ADVANCE INFORMATION**

V<sub>GVDD</sub> = 12 V, V<sub>VDRAIN</sub> = 48 V, CSAREF = 5V, T<sub>.I</sub> = 25°C (unless otherwise noted)

|                               | PARAMETER                                                             | TEST CONDITIONS                                                                                                        | MIN TY | P MAX                         | UNIT  |

|-------------------------------|-----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|--------|-------------------------------|-------|

| I <sub>DRIVENSD_H</sub><br>s  | High-side peak sink gate shutdown current                             | I <sub>DRIVENx</sub> is set to I <sub>DRIVEN14</sub> (1536mA Typ) or I <sub>DRIVEN15</sub> (2048mA Typ)                | 6      | 4                             | mA    |

| GATE DRIVE                    | ERS TIMINGS                                                           |                                                                                                                        |        |                               |       |

| t <sub>PDR_LS</sub>           | Low-side rising propagation delay                                     | INL to GL rising, no load on GL                                                                                        | 5      | 0                             | ns    |

| t <sub>PDF_LS</sub>           | Low-side falling propagation delay                                    | INL to GL falling, no load on GL                                                                                       | 5      | 0                             | ns    |

| t <sub>PDR_HS</sub>           | High-side rising propagation delay                                    | INH to GH rising, no load on GH                                                                                        | 5      | 0                             | ns    |

| t <sub>PDF_HS</sub>           | High-side falling propagation delay                                   | INH to GH falling, no load on GH                                                                                       | 5      | 0                             | ns    |

| t <sub>PD_MATCH</sub>         | Matching propagation delay of low-side gate driver                    | GL turning ON to GL turning OFF, From $V_{GL-SL}$ = 1V to $V_{GL-SL}$ = $V_{GVDD}$ - 1V;, no load on GL                | ±      | 4                             | ns    |

| t <sub>PD_MATCH</sub>         | Matching propagation delay of high-side gate driver                   | GH turning ON to GH turning OFF, From $V_{GH-SH}$ = 1V to $V_{GH-SH}$ = $V_{BST-SH}$ - 1V; no load on GH               | ±      | 4                             | ns    |

| t <sub>PD_MATCH_P</sub>       | Matching propagation delay per phase from GL off to GH on             | Deadtime disabled. GL turning OFF to GH turning ON, From $V_{GL-SL} = V_{GVDD} - 1V$ to $V_{GH-SH} = 1V$               | ±      | 4                             | ns    |

| t <sub>PD_MATCH_P</sub><br>H  | Matching propagation delay per phase from GH off to GL on             | Deadtime disabled. GH turning OFF to GL turning ON, From $V_{GH-SH} = V_{BST-SH} - 1V$ to $V_{GL-SL} = 1V$             | ±      | 4                             | ns    |

|                               |                                                                       | $R_{DT}$ = 470 $\Omega$ 2-pin PWM mode;<br>$I_{DRIVEN15}$                                                              | 2      | 0                             |       |

| t <sub>DEAD</sub>             | Gate drive dead time                                                  | $R_{DT}$ = 1.3 K $\Omega$ 2-pin PWM mode;<br>$I_{DRIVEN15}$                                                            | 10     | 0                             | ns    |

|                               |                                                                       | $R_{DT}$ = 3.3 K $\Omega$ 2-pin PWM mode; $I_{DRIVEN15}$                                                               | 370    |                               |       |

| t <sub>MINDEAD_</sub> VG<br>S | Minimum gate drive dead time (shortest available) of VGS monitor mode | VGS monitor dead time insertion;<br>t <sub>DEAD_CFG</sub> < 130ns; HS falling to LS<br>rising, LS falling to HS rising | 28     | 0                             | ns    |

| CURRENT S                     | HUNT AMPLIFIERS (SN, SO, SP, CSARI                                    | EF)                                                                                                                    |        |                               |       |

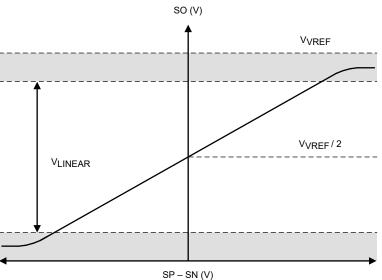

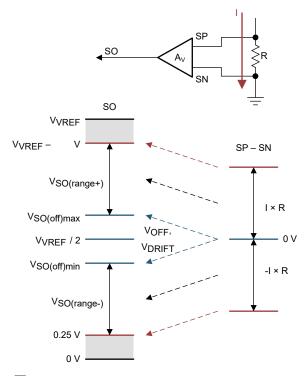

|                               |                                                                       | CSAGAIN = Tied to GND (LEVEL0)                                                                                         |        | 5                             | V/V   |

| ٨                             | Sanas amplifiar gain                                                  | CSAGAIN = 10kΩ typ tied to GND (LEVEL1)                                                                                | 10 20  |                               | V/V   |

| A <sub>CSA</sub>              | Sense amplifier gain                                                  | CSAGAIN = 30kΩ typ tied to GND (LEVEL2)                                                                                |        |                               | V/V   |

|                               |                                                                       | CSAGAIN = open; (LEVEL3)                                                                                               | 4      | 0                             | V/V   |

|                               | Softling time to 140/                                                 | V <sub>STEP</sub> = 1.6 V, A <sub>CSA</sub> = 5 V/V, C <sub>SO</sub> = 500pF                                           | 0.     | 6                             | μs    |

| t <sub>SET</sub>              | Settling time to ±1%                                                  | V <sub>STEP</sub> = 1.6 V, A <sub>CSA</sub> = 40 V/V, C <sub>SO</sub> = 500pF                                          | 0.8    |                               | μs    |

| BW                            | Bandwidth                                                             | A <sub>CSA</sub> = 5 V/V, C <sub>LOAD</sub> = 60-pF, small signal -3 dB                                                |        | 5                             | MHz   |

| V <sub>SWING</sub>            | Output voltage range                                                  | V <sub>CSAREF</sub> = 3 to 5.5 V                                                                                       | 0.25   | V <sub>CSAREF</sub><br>- 0.25 | V     |

| V <sub>COM</sub>              | Common-mode input range                                               |                                                                                                                        | -0.225 | 0.225                         | V     |

| V <sub>OFF</sub>              | Input offset voltage                                                  | $V_{SP} = V_{SN} = GND; T_J = 25^{\circ}C, Gain A_{CSA}$<br>= 10, 20, 40 V/V                                           | -1.3   | 1.3                           | mV    |

| V <sub>OFF</sub>              | Input offset voltage                                                  | $V_{SP} = V_{SN} = GND; T_J = 25^{\circ}C, Gain A_{CSA}$<br>= 5 V/V                                                    | -2.6   | 2.6                           | mV    |

| V <sub>OFF_DRIFT</sub>        | Input drift offset voltage                                            | V <sub>SP</sub> = V <sub>SN</sub> = GND, ; –40°C ≤ T <sub>J</sub> ≤ 150°C                                              |        | 8                             | μV/°C |

| I <sub>BIAS</sub>             | Input bias current                                                    | V <sub>SP</sub> = V <sub>SN</sub> = GND, V <sub>CSAREF</sub> = 3V to 5.5V                                              |        | 100                           | μA    |

| I <sub>BIAS_OFF</sub>         | Input bias current offset                                             | I <sub>SP</sub> – I <sub>SN</sub>                                                                                      | -1     | 1                             | μA    |

V<sub>GVDD</sub> = 12 V, V<sub>VDRAIN</sub> = 48 V, CSAREF = 5V, T<sub>J</sub> = 25°C (unless otherwise noted)

|                        | PARAMETER                                                                      | TEST CONDITIONS                                                                    | MIN TYP | MAX | UNIT |

|------------------------|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------|---------|-----|------|

| CMRR                   | Common-mode rejection ratio                                                    | DC                                                                                 | 80      |     | dB   |

| CIVIRR                 | Common-mode rejection ratio                                                    | 20 kHz                                                                             | 60      |     | dB   |

| I <sub>CSA_SUP</sub>   | Supply current for CSA                                                         | CSAREF, V <sub>CSAREF</sub> = 3.V to 5.5V                                          | 1.5     |     | mA   |

| T <sub>CMREC</sub>     | Common mode recovery time                                                      |                                                                                    | 2       |     | us   |

| PROTECTION             | ON CIRCUITS                                                                    |                                                                                    |         |     |      |

| \/                     | GVDD undervoltage threshold                                                    | V <sub>GVDD</sub> rising                                                           | 7.4     |     | V    |

| $V_{GVDD\_UV}$         | GVDD dildervoltage tillesiloid                                                 | V <sub>GVDD</sub> falling                                                          | 6.7     |     | V    |

| V                      | GVDD undervoltage threshold                                                    | V <sub>GVDD</sub> rising, DRV8162L                                                 | 4.8     |     | V    |

| $V_{GVDD\_UV}$         | GVDD undervoltage threshold                                                    | V <sub>GVDD</sub> falling, DRV8162L                                                | 4.7     |     |      |

|                        |                                                                                | $V_{BST}$ - $V_{SH}$ ; $V_{BST}$ rising, GVDD = 12V                                | 7.43    |     |      |

|                        |                                                                                | $V_{BST}$ - $V_{SH}$ ; $V_{BST}$ falling, GVDD = 12V                               | 7.25    |     |      |

| V <sub>BST_UV</sub>    | Bootstrap undervoltage threshold                                               | $V_{BST}$ - $V_{SH}$ ; $V_{BST}$ rising, GVDD = 5V, DRV8162L                       | 4.08    |     | V    |

|                        |                                                                                | V <sub>BST</sub> - V <sub>SH</sub> ; V <sub>BST</sub> falling, GVDD = 5V, DRV8162L | 3.94    |     |      |

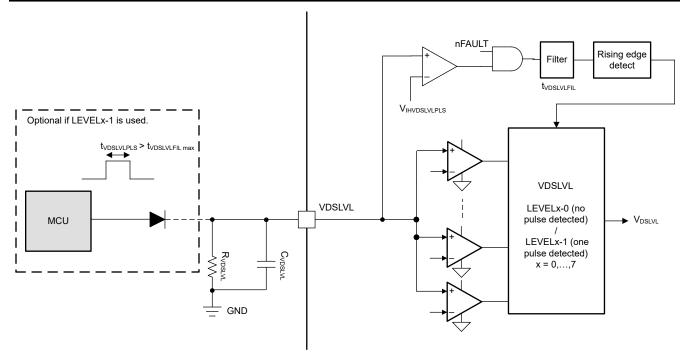

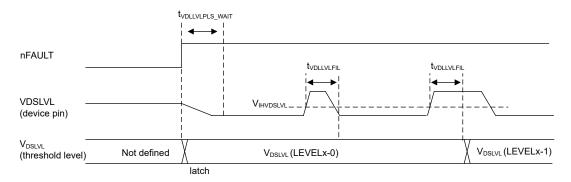

| V <sub>DS_LVL0-0</sub> |                                                                                | R <sub>VDSLVL</sub> = 0.1 KΩ max (LEVEL0)                                          | 0.1     |     |      |

| V <sub>DS_LVL1-1</sub> |                                                                                | $R_{VDSLVL}$ = 2 K $\Omega$ typ (LEVEL1); one pulse detected on VDSLVL pin         | 0.15    |     |      |

| V <sub>DS_LVL1-0</sub> |                                                                                | R <sub>VDSLVL</sub> = 2 KΩ typ (LEVEL1); DC                                        | 0.2     |     |      |

| V <sub>DS_LVL2-1</sub> |                                                                                | $R_{VDSLVL}$ = 5.6 K $\Omega$ typ (LEVEL2); one pulse detected on VDSLVL pin       | 0.3     |     |      |

| V <sub>DS_LVL2-0</sub> |                                                                                | $R_{VDSLVL}$ = 5.6 KΩ typ (LEVEL2)                                                 | 0.4     |     |      |

| V <sub>DS_LVL3-1</sub> |                                                                                | R <sub>VDSLVL</sub> = 12 KΩ typ (LEVEL3); one pulse detected on VDSLVL pin         | 0.5     |     |      |

| V <sub>DS_LVL3-0</sub> | V <sub>DS</sub> overcurrent protection threshold level (DC)                    | R <sub>VDSLVL</sub> = 12 KΩ typ (LEVEL3)                                           | 0.6     |     | V    |

| V <sub>DS_LVL4-1</sub> |                                                                                | $R_{VDSLVL}$ = 26 K $\Omega$ typ (LEVEL4); one pulse detected on VDSLVL pin        | 0.7     |     | _    |

| V <sub>DS_LVL4-0</sub> |                                                                                | R <sub>VDSLVL</sub> = 26 KΩ typ (LEVEL4)                                           | 0.8     |     |      |

| V <sub>DS_LVL5-1</sub> |                                                                                | $R_{VDSLVL}$ = 62 K $\Omega$ typ (LEVEL5); one pulse detected on VDSLVL pin        | 0.9     |     |      |

| V <sub>DS_LVL5-0</sub> |                                                                                | R <sub>VDSLVL</sub> = 62 KΩ typ (LEVEL5)                                           | 1.0     |     |      |

| V <sub>DS_LVL6-1</sub> |                                                                                | $R_{VDSLVL}$ = 130 KΩ typ (LEVEL6); one pulse detected on VDSLVL pin VDSLVL        | 1.5     |     |      |

| V <sub>DS_LVL6-0</sub> |                                                                                | $R_{VDSLVL}$ = 130 KΩ typ (LEVEL6);                                                | 2.0     |     |      |

| t <sub>DS_DG</sub>     | V <sub>DS</sub> protection deglitch time                                       |                                                                                    | 3       |     | μs   |

| t <sub>DS_BLK</sub>    | V <sub>DS</sub> overcurrent protection blanking time                           |                                                                                    | 1       |     | μs   |

| t <sub>VDSLVLFIL</sub> | VDSLVL pin digital input - one pulse filter time for LEVELx-1                  |                                                                                    | 4       |     | μs   |

| V <sub>IHVDSLVL</sub>  | VDSLVL pin digital input - one pulse high-level detection voltage for LEVELx-1 |                                                                                    | 1       |     | V    |

| T <sub>OTSD</sub>      | Thermal shutdown temperature                                                   |                                                                                    | 170     |     | °C   |

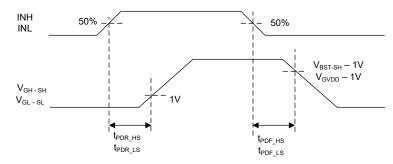

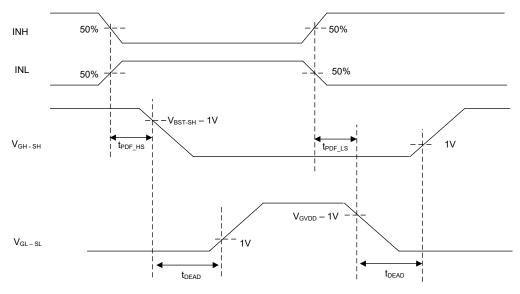

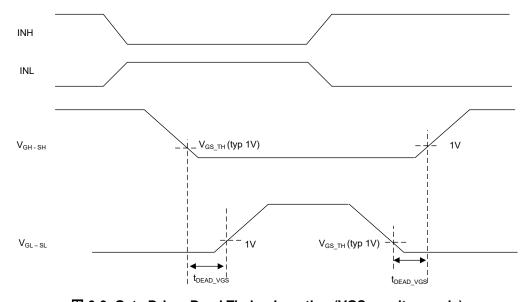

### **6.6 Timing Diagrams**

図 6-1. Gate Driver Propagation Delay Timing Diagram

図 6-2. Gate Driver Dead Timing Insertion (INH and INL monitor mode)

図 6-3. Gate Driver Dead Timing Insertion (VGS monitor mode)

## 7 Detailed Description

#### 7.1 Overview

The DRV816x devices are integrated 100-V gate drivers for various electromechanical loads including brushless DC (BLDC) motors, brushed DC motors, stepper motors, switched reluctance motors, and solenoids. These devices reduce system component count, cost, and complexity by integrating half-bridge gate drivers with a trickle charge pump, bootstrap diode, and FET VDS monitoring. The FET VDS monitors protect the external FETs against shorts to the supply, to ground, or across motor terminals. The DRV8161 integrates a bidirectional low-side current sense amplifier for current feedback to the controller ADC. The half-bridge architecture allows for the gate driver to be placed near the power stage FETs to simplify signal routing, reduce radiated EMI, and reduce overall PCB area.

The gate drivers support external N-channel high-side and low-side power MOSFETs and can drive up to 1-A source, 2-A sink peak currents. The integrated bootstrap diode, external bootstrap capacitor, and integrated trickle charge pump generate the high-side gate drive supply voltage from the GVDD pin. The GVDD pin directly supplies the low-side gate drive supply voltage. The DRV8162 and DRV8162L device variants offer separate GVDD and GVDD LS pins to help the system design of safe torque off (STO).

A smart gate-drive architecture provides the ability to adjust the output gate-drive current strength allowing for the gate driver to control the power MOSFET VDS switching speed. This allows for the removal of external gate drive resistors and diodes reducing BOM component count, cost, and PCB area. The architecture also uses an internal state machine to protect against gate-drive short-circuit events, control the half-bridge dead time, and protect against dV/dt parasitic turn on of the external power MOSFET.

In addition to the high level of device integration, the DRV816x devices provide a wide range of integrated protection features. These features include power-supply under voltage lockout (UVLO), VDS over current monitoring (OCP), and over temperature shutdown (OTSD). The nFAULT pin indicates fault events detected by the protection features.

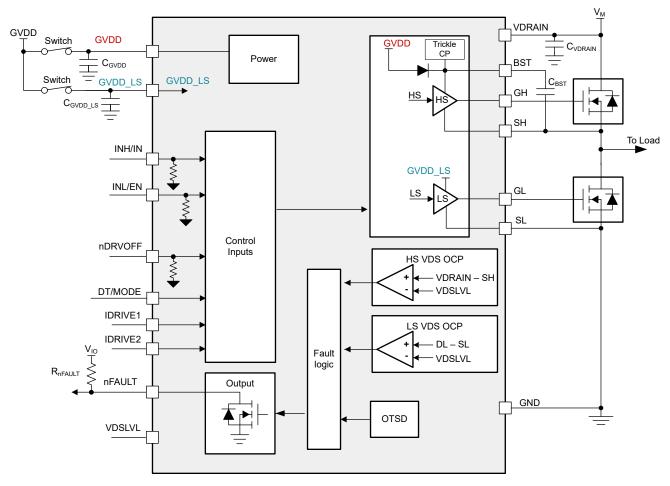

### 7.2 Functional Block Diagram

図 7-1. Block Diagram for DRV8161

図 7-2. Block Diagram for DRV8162 and DRV8162L

### 7.3 Feature Description

#### 7.3.1 Gate Drivers

The DRV816x family of devices integrates high-side and low-side FET gate drivers capable of driving N-channel power MOSFETs in half-bridge configuration. A bootstrap gate drive architecture generates the high-side gate driver voltage during PWM switching. The GVDD pin supplies both high-side and low-side gate drivers and sets the  $V_{GS}$  voltage for the FETs.

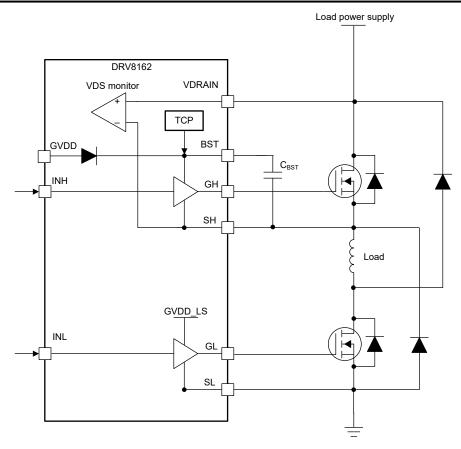

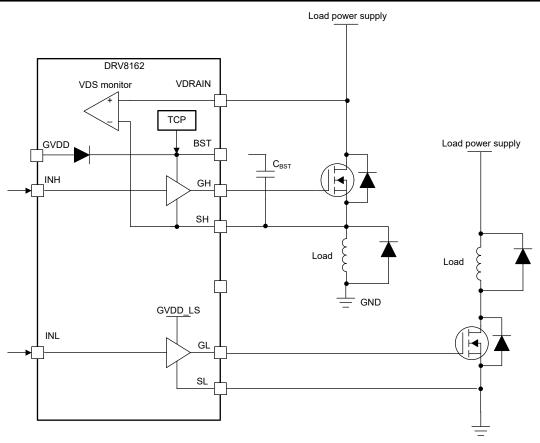

The DRV816x devices support half-bridge power stage architecture. In addition to the regular 2-pin PWM control interface, the device offers an independent PWM mode by disabling shoot through protection and allowing the high-side and low-side FETs to be controlled independently. Independent FET control is useful for driving solenoids and switched reluctance motors. The DRV8162 and DRV8162L have separate supply pins (GVDD and GVDD\_LS) for high-side and low-side FET gate drive. This allows the system to support safe torque off (STO) function by adding external power switches to the gate drive supply pins.

#### 7.3.1.1 PWM Control Modes

The DRV816x family of devices provides three different PWM control modes to support various commutation and control methods. The PWM control modes are 1-pin PWM, 2-pin PWM and independent PWM mode. The modes are configured by DT/MODE pin.

DT/MODE pin is latched at power up, so in order to change the PWM control mode the device needs to be reset through power supply. Refer to  $\frac{1}{5}$  7-6 for the configuration of PWM control mode using the DT/MODE pin.

#### 7.3.1.1.1 2-pin PWM Mode

In 2-pin PWM mode, half-bridge driver supports three output states: low, high, or high-impedance (Hi-Z). The corresponding INH and INL signals control the output state as listed in 表 7-1.

表 7-1. 2-pin PWM Mode Truth Table

| INL | INH | GL | GH | SH   |

|-----|-----|----|----|------|

| 0   | 0   | L  | L  | Hi-Z |

| 0   | 1   | L  | Н  | Н    |

| 1   | 0   | Н  | L  | L    |

| 1   | 1   | L  | L  | Hi-Z |

資料に関するフィードバック(ご意見やお問い合わせ)を送信

#### 7.3.1.1.2 1-pin PWM Mode (preview only)

#### 警告

The DRV8161 prototype samples do not support 1-pin PWM Mode. This function is preview only. Please contact TI for more detailed information.

In 1-pin PWM mode, the IN pin controls half-bridge and supports two output states: low or high. The EN pin is used to put the half bridge in the Hi-Z state. If the Hi-Z state is not required, tie INL/EN pin to logic high. The corresponding INH/IN and INL/EN signals control the output state as listed in 表 7-2.

表 7-2. 1-pin PWM Mode Truth Table (preview only)

| INL/EN | INH/IN | GL | GH | SH   |

|--------|--------|----|----|------|

| 0      | Х      | L  | L  | Hi-Z |

| 1      | 0      | Н  | L  | L    |

| 1      | 1      | L  | Н  | Н    |

#### 7.3.1.1.3 Independent PWM Mode

DRV816x supports independent PWM mode, the INH and INL pins control the outputs, GH and GL, respectively. This control mode lets the device drive separate high-side and low-side load. The independent PWM drive mode can be used for various type of loads including solenoids, Switched Reluctance Motor (SRM), unidirectional brushed DC motors, and low-side and high-side switches. In this mode, turning on both the high-side and low-side MOSFETs at the same time in a given half bridge gate driver is possible to use the device as a high-side or low-side driver. The shoot-through protection and dead time are bypassed in the mode.

表 7-3. Independent PWM Mode Truth Table

| INL | INH | GL | GH |

|-----|-----|----|----|

| 0   | 0   | L  | L  |

| 0   | 1   | L  | Н  |

| 1   | 0   | Н  | L  |

| 1   | 1   | Н  | Н  |

☑ 7-3 shows how the device can be used to connect an inductive load where both the high-side and low-side MOSFETs can be turned on at the same time to drive the load without causing shoot-through. The external diodes for current recirculation are recommended. This configuration helps the design of solenoids or applications. The trickle charge pump is enabled all the time regardless of low-side PWM activity.

注

The low-side VDS monitor of DRV816x is not available if independent PWM mode is configured. For DRV8161, the CSA output can be monitored by MCU to detect the over current condition.

図 7-3. Independent PWM mode for single load between high-side and low-side

☑ 7-4shows how the device can be used to connect a high-side load and a low-side load at the same time with one half-bridge and drive the loads independently.

図 7-4. Independent PWM mode for high-side and low-side independent loads

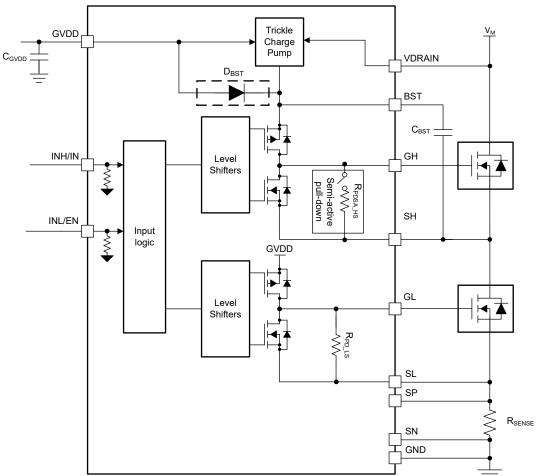

#### 7.3.1.2 Gate Drive Architecture

The gate driver device use a complimentary, push-pull topology for both the high-side and low-side drivers. This topology allows for both a strong pullup and pulldown of the external MOSFET gates. The low side gate driver is supplied directly from the GVDD regulator supply. For the high-side gate driver a bootstrap diode and capacitor are used to generate the floating high-side gate voltage supply. The bootstrap diode is integrated and an external bootstrap capacitor is used on the BST pin.

The high-side gate driver has semi-active pull down and low side gate has passive pull down to help prevent the external MOSFET from turning ON when power supply is disconnected.

図 7-5. DRV8161 Gate Driver Block Diagram

**ADVANCE INFORMATION**

図 7-6. DRV8162 and DRV8162L Gate Driver Block Diagram

#### 7.3.1.2.1 Tickle Charge Pump (TCP)

An internal trickle charge pump (TCP) is connected to BST node to reduce voltage drop due to the leakage currents of the driver and external components. The charge pump generates  $V_{TCP}$  voltage with respect to VDRAIN pin. For the independent PWM mode, the charge pump is active all the time. For the 2-pin PWM and 1-pin PWM mode, if the INL stays low for 250us (typ), the charge pump is activated.

#### 警告

Depending on the system use case or the device condition, the output capability of TCP charge pump is not always sufficient to maintain the voltage on  $C_{\rm BST}$  during 100% duty cycle. In particular at high temperature, the charge pump output voltage  $V_{\rm TCP}$  can be lower than the bootstrap undervoltage threshold  $V_{\rm BST\_UV}$ , and hence the high-side gate driver output becomes shutdown. To avoid the shutdown, the length of 100% duty cycle time must be limited, or  $C_{\rm BST}$  must be charged by system periodically to maintain the voltage.

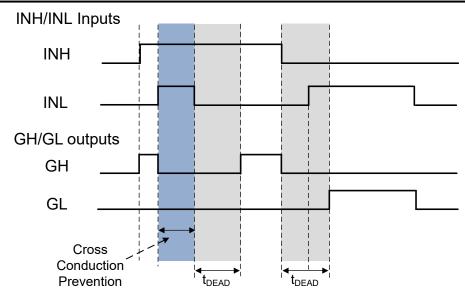

#### 7.3.1.2.2 Deadtime and Cross-Conduction Prevention (Shoot through protection)

In the DRV816x, if the device is configured to 2-pin PWM mode, high- and low-side inputs operate independently, with an exception to prevent cross conduction when the high and low side of the same half-bridge are turned ON at same time. The device turns OFF high- and low- side output to prevent shoot through when high- and low-side inputs are logic high at same time.

The DRV816x also provide dead time insertion to prevent both external MOSFETs of each half-bridge from switching on at the same time. The deadtime can be enabled and adjusted between 20 ns and 400 ns by connecting resistor between DT/MODE and ground. Refer to セクション 7.3.2.6.

🗵 7-7. Cross Conduction Prevention and Dead time Insertion (2-pin PWM, dead time insertion enabled)

#### 7.3.2 Pin Diagrams

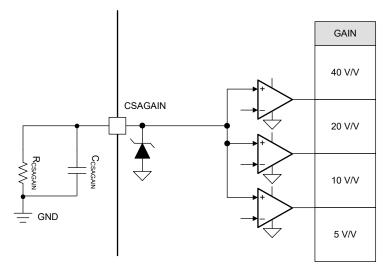

#### 7.3.2.1 Four Level Input Pin (CSAGAIN)

$\boxtimes$  7-8 shows the structure of the four level input pin, CSAGAIN, for hardware interface configuration. The input can be set with an external resistor. The C<sub>CSAGAIN</sub> is optional to help reduce the impact of GND noise. The CSA GAIN information is not latched at the device power up and may be updated during the device operation.

図 7-8. Four Level Input Pin Structure

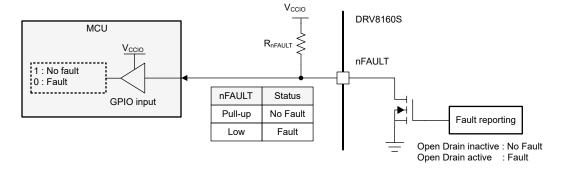

#### 7.3.2.2 Digital output nFAULT (DRV8162, DRV8162L)

図 7-9 shows the structure of the open-drain output pins, nFAULT. The open-drain output requires an external pullup resistor to function correctly. Refer to 表 7-7 for the device actions including nFAULT.

図 7-9. nFAULT Open Drain Output buffer

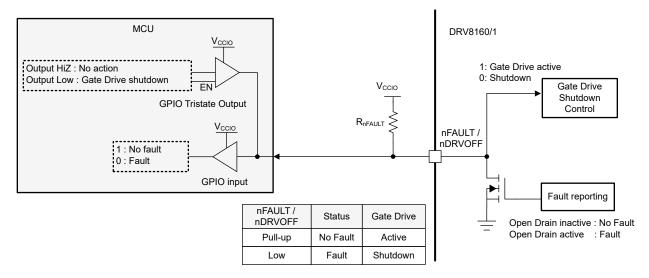

### 7.3.2.3 Digital InOut nFAULT/nDRVOFF (DRV8161)

図 7-10 shows the structure of the open-drain output and input pin. In the DRV8161 device variant, two functions nFAULT and nDRVOFF are achieved by sharing one device pin, nFAULT/nDRVOFF. The open-drain output requires an external pullup resistor to function correctly. If a fault condition is detected, the device activates Open Drain buffer, and nFAULT/nDRVOFF pin is driven low. The nFAULT/nDRVOFF pins is internally connected to Gate Drive Shutdown logic, and the gate drive outputs are shutdown (pull-down) if the nFAULT/nDRVOFF pin low. Refer to 表 7-7 for the device actions including nFAULT.

図 7-10. nFAULT/nDRVOFF Open Drain Output and Input buffer

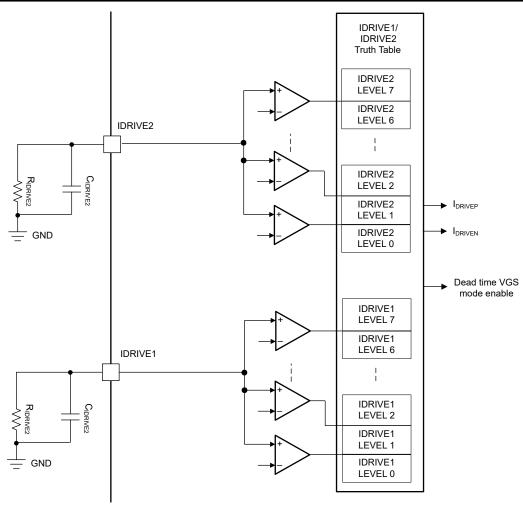

#### 7.3.2.4 Multi-level inputs (IDRIVE1 and IDRIVE2)

The DRV816x have IDRIVE1 and IDRIVE2 device pins for gate drive current configuration. Each pin can set 8 levels, LEVEL0 to LEVEL7, with an external resistor connected between the device pin and GND. The gate drive current I<sub>DRIVEN</sub> and I<sub>DRIVEP</sub> can be determined by 表 7-4. The (G) in the table indicates that VGS monitor dead time insertion is enabled. The IDRIVE1 and IDRIVE2 information are latched at the device power up.

図 7-11. Multi-level digital inputs of IDRIVE1 and IDRIVE2

### 表 7-4. IDRIVE1/IDRIVE2 Truth Table for Gate Drive Current configuration

|         |            |                                         | IDRIVE2                                 |                                         |                                         |                                         |                                         |                                         |                                         |                                         |                                         |                                         |                                         |                                         |                                         |                                         |                                         |

|---------|------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|

|         |            | LEV                                     | EL0                                     | LEV                                     | EL1                                     | LEV                                     | EL2                                     | LEV                                     | EL3                                     | LEV                                     | EL4                                     | LEV                                     | EL5                                     | LEV                                     | EL6                                     | LEV                                     | EL7                                     |

|         |            | Source<br>1                             | :Sink =<br>:2                           | Source<br>1                             | :Sink =<br>:2                           |                                         | :Sink =<br>1.5                          | Source<br>1:                            | :Sink =<br>1.5                          | Source<br>1                             |                                         |                                         | :Sink =<br>:3                           | time in                                 | dead<br>sertion<br>bled                 | IDRIVE                                  | 2 open                                  |

|         |            | I <sub>DRIVE</sub><br><sub>P</sub> [mA] | I <sub>DRIVE</sub><br><sub>N</sub> [mA] |

| IDRIVE1 | LEVE<br>L7 | 256                                     | 512                                     | 16                                      | 32                                      | 256                                     | 384                                     | 16                                      | 32                                      | 128                                     | 128                                     | 64                                      | 192                                     | 32 (G)                                  | 64 (G)                                  | 16 (G)                                  | 32 (G)                                  |

| □       | LEVE<br>L6 | 288                                     | 576                                     | 32                                      | 64                                      | 288                                     | 448                                     | 32                                      | 32                                      | 192                                     | 192                                     | 128                                     | 384                                     | 96 (G)                                  | 192<br>(G)                              | 64 (G)                                  | 128<br>(G)                              |

|         | LEVE<br>L5 | 320                                     | 640                                     | 64                                      | 128                                     | 320                                     | 448                                     | 64                                      | 64                                      | 256                                     | 256                                     | 192                                     | 576                                     | 128<br>(G)                              | 256<br>(G)                              | 128                                     | 256                                     |