🕳 Order

Now

## DRV8305-Q1

Reference

Design

JAJSHP7D-MAY 2015-REVISED JULY 2019

# DRV8305-Q1 オートモーティブ 3 相スマート・ゲート・ドライバ、3 つ の電流シャント・アンプ、電圧レギュレータ付き

# 1 特長

- 車載アプリケーション用に AEC-Q100 認定済み

- 動作時周囲温度範囲

- 温度グレード 0 (E):-40℃~+150℃

- 温度グレード 1 (Q):-40℃~+125℃

- 4.4V~45Vの動作電圧

- 1.25A/1A のピーク・ゲート駆動電流

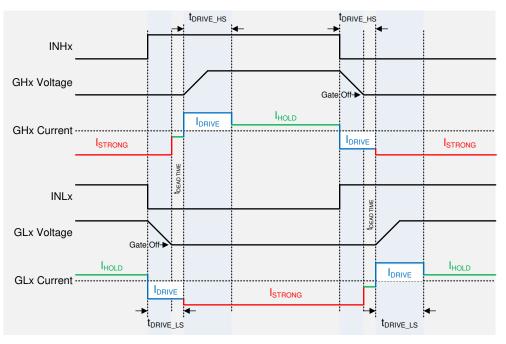

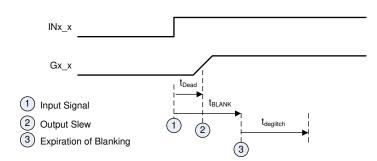

- スマート・ゲート駆動アーキテクチャ (IDRIVE お よび TDRIVE)

- ハイサイドおよびローサイドのスルーレート制御 をプログラム可能

- 100% デューティ・サイクルに対応するチャージ・ポンプ・ゲート・ドライバ

- 3つの電流シャント・アンプを内蔵

- 50mA LDO (3.3V および 5V オプション)を内蔵

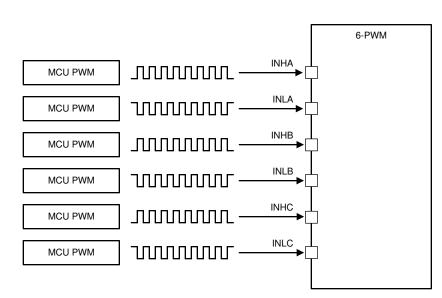

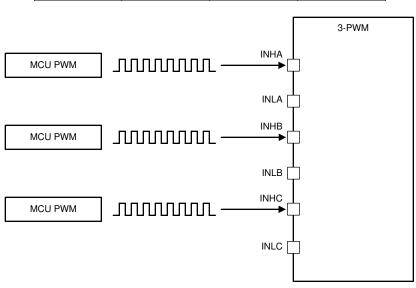

- 最高 200kHz の 3-PWM または 6-PWM 入力制御

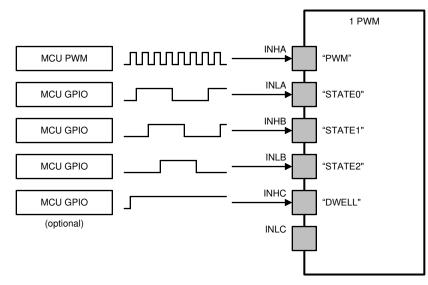

- 単一 PWM モード整流機能

- シリアル・ペリフェラル・インターフェイス (SPI)によるデバイス設定とフォルト通知

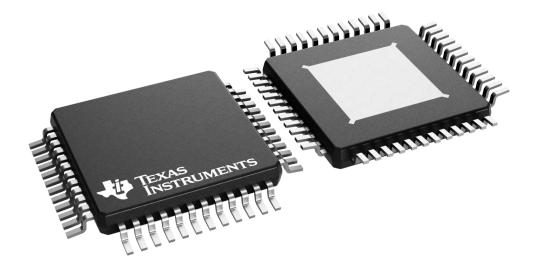

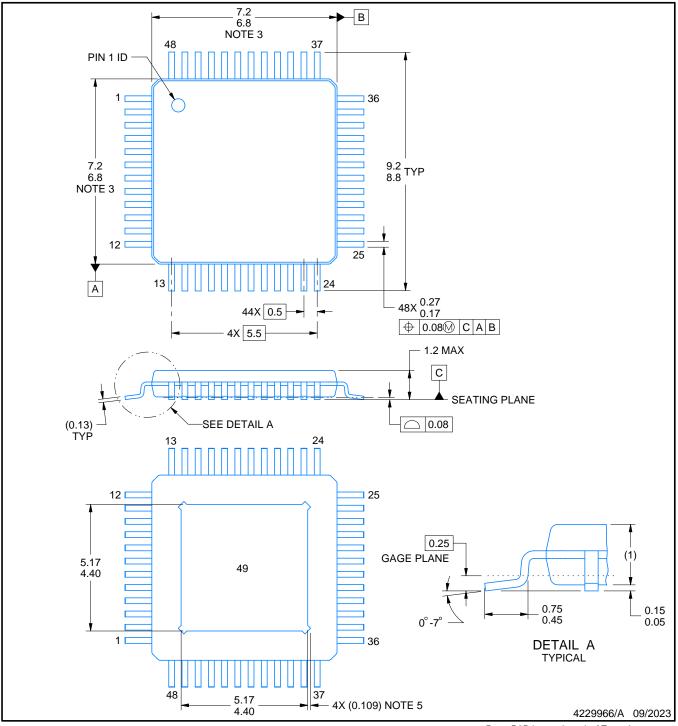

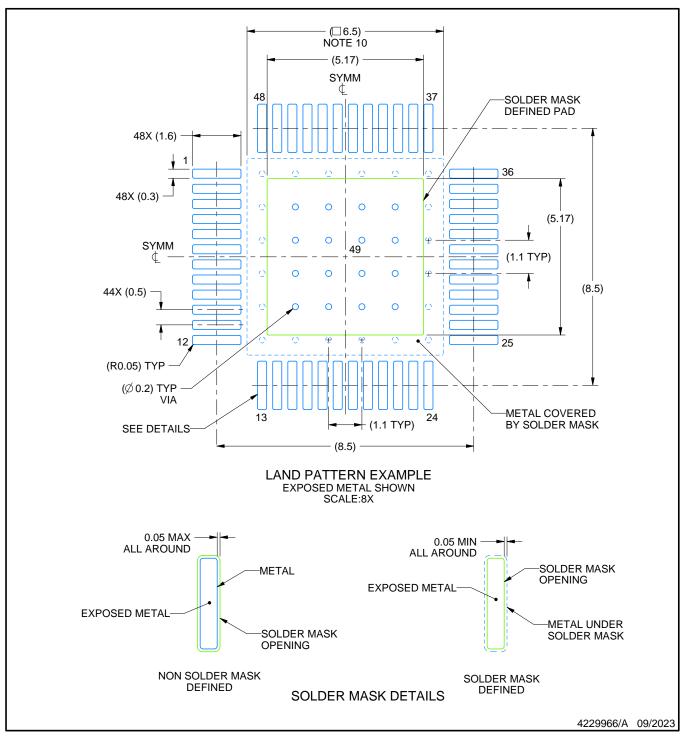

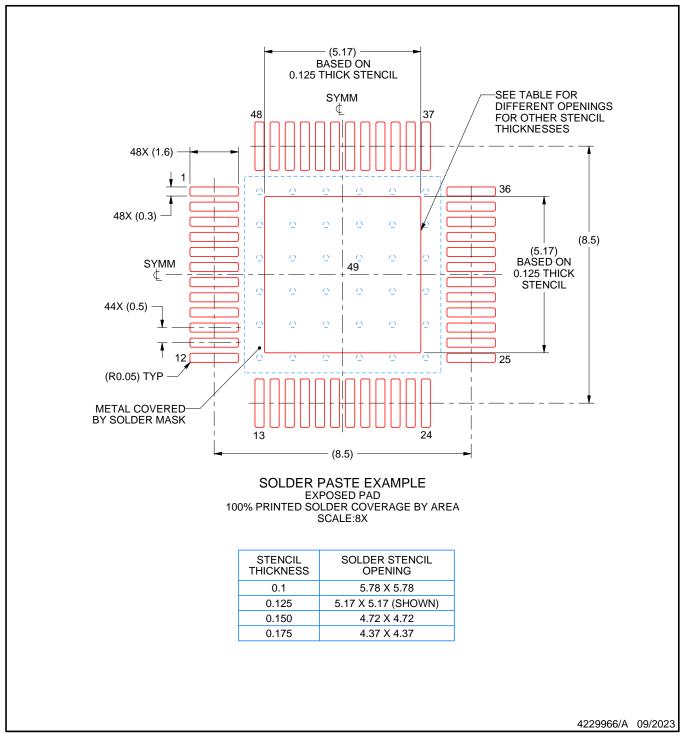

- 熱特性が強化された 48 ピン HTQFP

- 保護機能

- フォルト診断と MCU ウォッチドッグ

- プログラム可能なデッド・タイム制御

- MOSFET 貫通電流防止

- MOSFET V<sub>DS</sub> 過電流監視

- ゲート・ドライバのフォルト検出

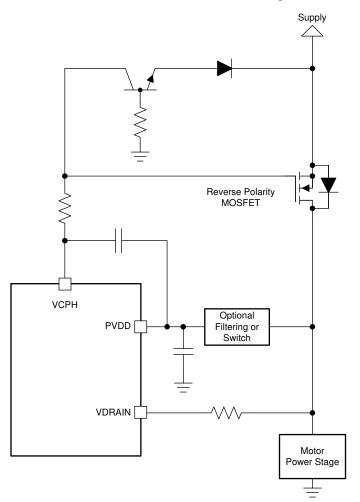

- バッテリ逆極性保護のサポート

- リンプホーム・モードのサポート

- 過熱警告およびシャットダウン

# 2 アプリケーション

- 3 相 BLDC および PMSM モータ

- 車載用の燃料および水ポンプ

- 車載用のファンおよびブロワー

## 3 概要

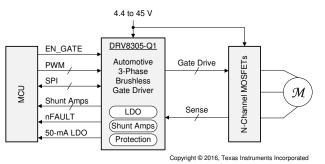

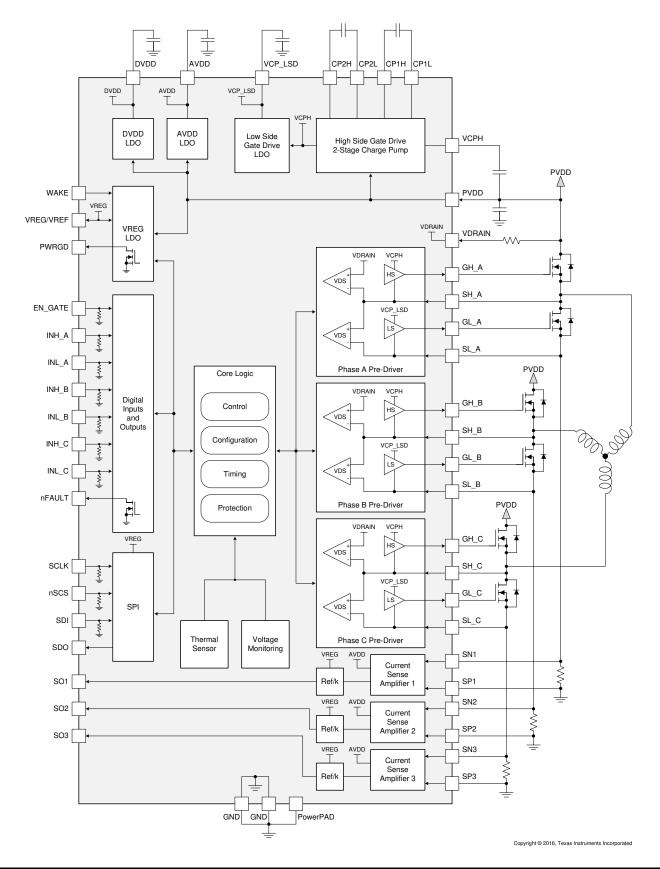

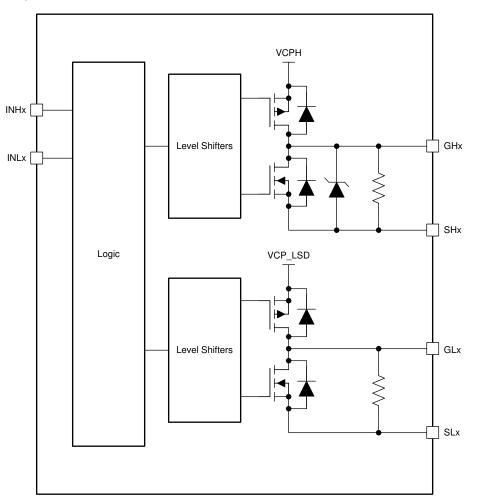

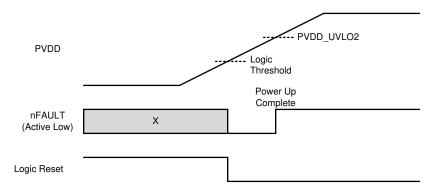

DRV8305-Q1 デバイスは、3 相モータ・ドライブ・アプリ ケーション用のゲート・ドライバ IC です。このデバイスは 3 つの高精度ハーフ・ブリッジ・ドライバを備えており、それ ぞれがハイサイドおよびローサイド N チャネル MOSFET を駆動できます。チャージ・ポンプ・ドライバにより、コール ド・クランク状況に対応して 100% のデューティ・サイクル と低電圧動作をサポートしています。このデバイスは、最 大 45V の負荷ダンプ電圧に耐えられます。

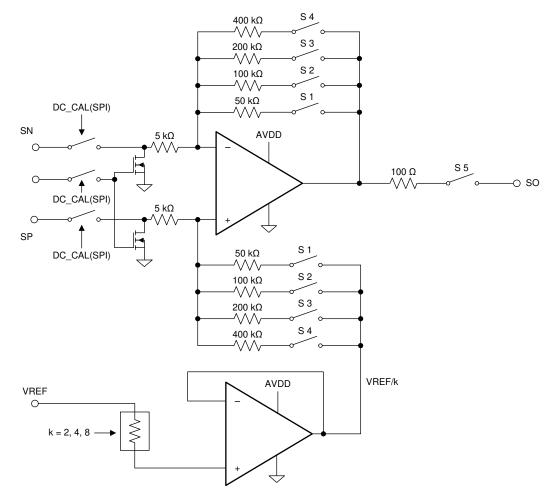

DRV8305-Q1 デバイスは、可変ゲイン設定と可変オフ セット基準をサポートする高精度ローサイド電流測定のた めの3つの双方向電流シャント・アンプを内蔵していま す。

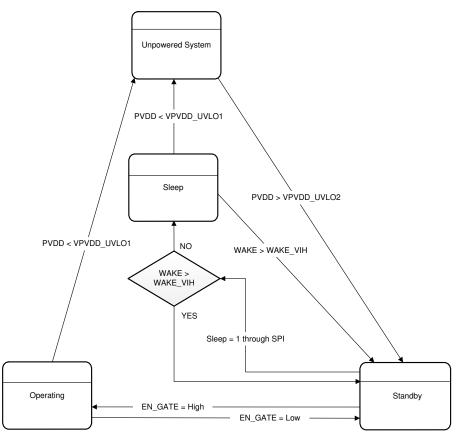

DRV8305-Q1 デバイスは、MCU またはその他のシステムの電力要件をサポートするために電圧レギュレータを内蔵しています。この電圧レギュレータを LIN 物理インターフェイスで直接制御することで、システム・スタンバイおよびスリープ電流を低減できます。

#### 製品情報 (1)

| 型番         | パッケージ     | 本体サイズ(公称)     |

|------------|-----------|---------------|

| DRV8305-Q1 | HTQFP(48) | 7.00mm×7.00mm |

(1) 提供されているすべてのパッケージについては、巻末の注文情報 を参照してください。

概略回路図

# 目次

| 1 | 特長   | :                                            |

|---|------|----------------------------------------------|

| 2 | アプ   | リケーション1                                      |

| 3 | 概要   |                                              |

| 4 | 改訂   | '履歴2                                         |

| 5 | 概要   | 〔(続き)                                        |

| 6 | Pin  | Configuration and Functions 5                |

| 7 | Spe  | cifications7                                 |

|   | 7.1  | Absolute Maximum Ratings 7                   |

|   | 7.2  | ESD Ratings7                                 |

|   | 7.3  | Recommended Operating Conditions 8           |

|   | 7.4  | Thermal Information 8                        |

|   | 7.5  | Electrical Characteristics                   |

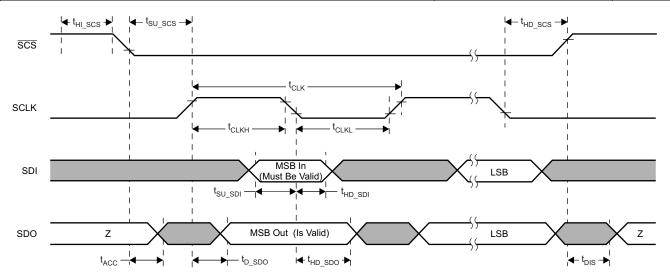

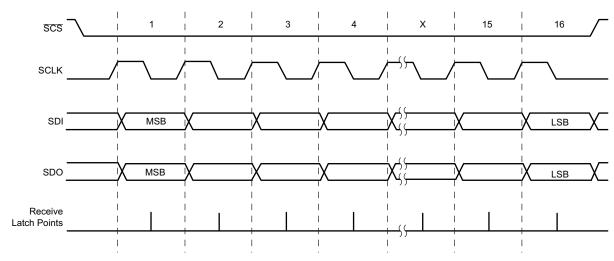

|   | 7.6  | SPI Timing Requirements (Slave Mode Only) 15 |

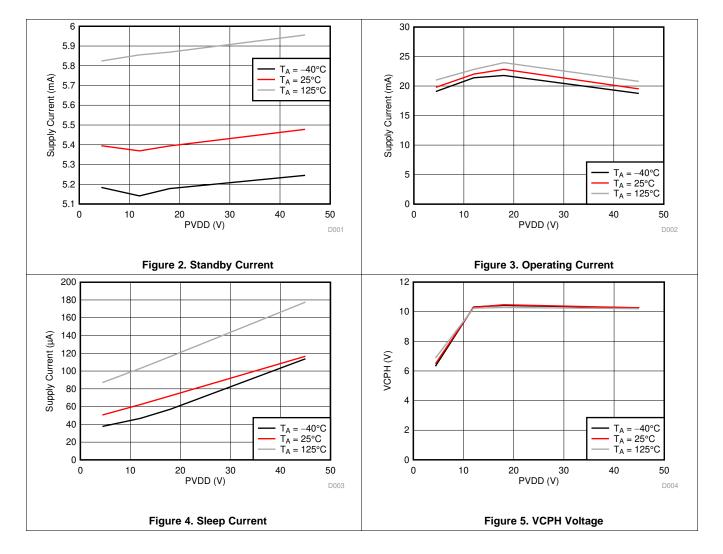

|   | 7.7  | Typical Characteristics 16                   |

| 8 | Deta | ailed Description 17                         |

|   | 8.1  | Overview 17                                  |

|   | 8.2  | Functional Block Diagram 18                  |

|   | 8.3  | Feature Description 19                       |

|   | 8.4  | Device Functional Modes                      |

|    | 8.5  | Programming                                  | . 36 |

|----|------|----------------------------------------------|------|

|    | 8.6  | Register Maps                                | . 38 |

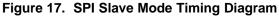

| 9  | Appl | ication and Implementation                   | 46   |

|    | 9.1  | Application Information                      | . 46 |

|    | 9.2  | Typical Application                          | . 47 |

| 10 | Pow  | er Supply Recommendations                    | 51   |

|    | 10.1 | Power Supply Consideration in Generator Mode | . 51 |

|    | 10.2 | Bulk Capacitance                             | . 51 |

| 11 | Layo | out                                          | 53   |

|    | 11.1 | Layout Guidelines                            | . 53 |

|    | 11.2 | Layout Example                               | . 53 |

| 12 | デバ   | イスおよびドキュメントのサポート                             | 54   |

|    | 12.1 | ドキュメントのサポート                                  | . 54 |

|    | 12.2 | ドキュメントの更新通知を受け取る方法                           | . 54 |

|    | 12.3 | コミュニティ・リソース                                  | . 54 |

|    | 12.4 | 商標                                           | . 54 |

|    | 12.5 | 静電気放電に関する注意事項                                | . 54 |

|    | 12.6 | Glossary                                     | . 54 |

| 13 | メカニ  | ニカル、パッケージ、および注文情報                            | 54   |

|    |      |                                              |      |

# 4 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| <b>Revision C</b> | (September | 2017) | から Revision | Dに変更 |

|-------------------|------------|-------|-------------|------|

|-------------------|------------|-------|-------------|------|

| • | Added content to the VREG pin description                      | . 6 |

|---|----------------------------------------------------------------|-----|

| • | Added ESD classification levels to the ESD Ratings table       | . 7 |

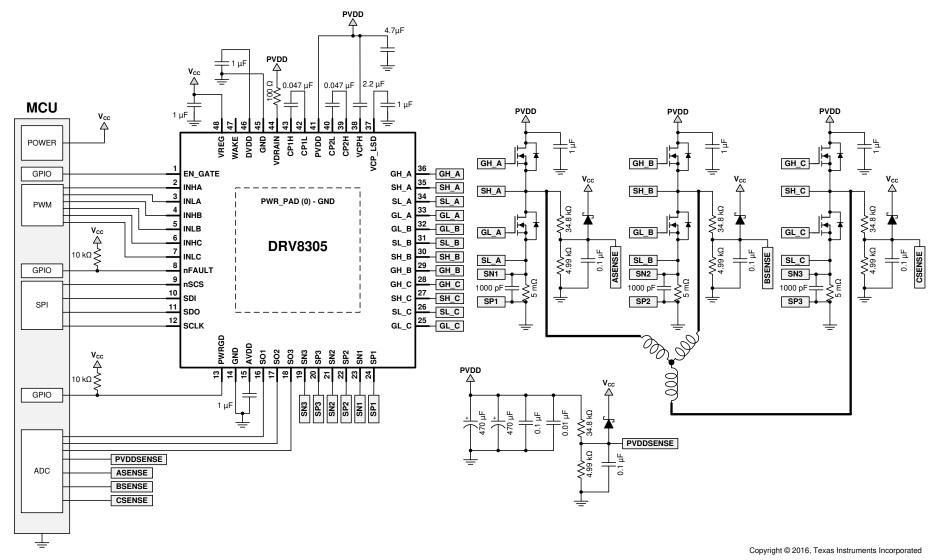

| • | Added the VREG Reference Voltage Input (DRV8305N) section      | 49  |

| • | Added the Power Supply Consideration in Generator Mode section | 51  |

## Revision B (May 2016) から Revision C に変更

| • | Added transient specification for GHx, SLx, SPx, and SNx                                                                                                                                                | 7    |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| • | Changed SPx and SNx rating from -2 V to -3 V                                                                                                                                                            | 7    |

| • | Changed the test condition for the V <sub>AVDD_UVLO</sub> , V <sub>VCPH_UVFL</sub> , V <sub>VCPH_UVLO2</sub> , and V <sub>VCP_LSD_UVLO2</sub> parameters in the <i>Electrical Characteristics</i> table | . 12 |

| • | Changed the maximum V <sub>AVDD_UVLO</sub> and V <sub>PVDD_UVLO2</sub> parameters in the <i>Electrical Characteristics</i> table                                                                        | . 12 |

| • | Moved the External Components table from the Pin Configuration and Functions section to the Feature Description section                                                                                 | . 19 |

| • | Added the description for latch fault reset methods to the Undervoltage Warning (UVFL), Undervoltage Lockout (UVLO), and Overvoltage (OV) Protection section                                            | . 33 |

| • | Changed the description of FLIP_OTSD register bit in the IC Operation Register Description                                                                                                              | . 43 |

| • | 追加「ドキュメントの更新通知を受け取る方法」セクション                                                                                                                                                                             | . 54 |

| Re | evision A (March 2016) から Revision B に変更 | Page |

|----|------------------------------------------|------|

| •  | 完全版のデータシートをリリースし、「製品プレビュー」から「量産データ」に変更   | 1    |

#### www.tij.co.jp

STRUMENTS

ÈXAS

Page

Page

#### www.tij.co.jp

| 20 | 115年5月発行のものから更新 Page                           |

|----|------------------------------------------------|

| •  | デバイスのプレビュー版データシートを更新し、暫定版の電気的特性と機能の説明を追加       |

| •  | Updated the y-axis units to µA for Figure 4 16 |

#### DRV8305-Q1

JAJSHP7D-MAY 2015-REVISED JULY 2019

www.ti.com

# 5 概要(続き)

ゲート・ドライバは、貫通電流を防止するためスイッチング時に自動ハンドシェイクを使用します。外部 MOSFET を過電流 条件から保護するため、ハイサイドとローサイドの両方の MOSFET の V<sub>DS</sub> が正確に測定されます。SPI は詳細なフォルト 通知、診断、デバイス構成 (例:電流シャント・アンプのゲイン・オプション、各 MOSFET の過電流検出、ゲート駆動のス ルーレート制御) に使用できます。

## デバイスの選択肢

- DRV8305NQ:グレード 1、基準電圧付き

- DRV83053Q:グレード 1、3.3V、50mA LDO 付き

- DRV83055Q:グレード 1、5V、50mA LDO 付き

- DRV8305NE:グレード 0、基準電圧付き

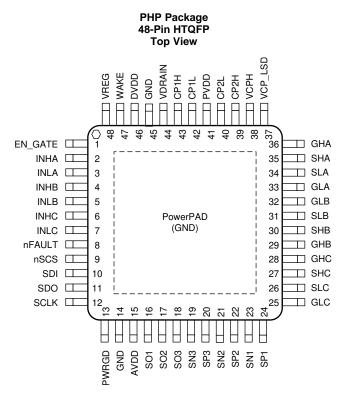

# 6 Pin Configuration and Functions

#### **Pin Functions**

| Р       | IN     | 1/0 | DESCRIPTION                                                                                             |                                                                                                                                   |  |

|---------|--------|-----|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|--|

| NAME    | NO.    | 1/0 |                                                                                                         | DESCRIPTION                                                                                                                       |  |

| EN_GATE | 1      | I   | Enable gate                                                                                             | Enables the gate driver and current shunt amplifiers; internal pulldown.                                                          |  |

| INHA    | 2      | I   | Bridge PWM input                                                                                        | PWM input signal for bridge A high-side.                                                                                          |  |

| INLA    | 3      | I   | Bridge PWM input                                                                                        | PWM input signal for bridge A low-side.                                                                                           |  |

| INHB    | 4      | I   | Bridge PWM input                                                                                        | PWM input signal for bridge B high-side.                                                                                          |  |

| INLB    | 5      | I   | Bridge PWM input                                                                                        | PWM input signal for bridge B low-side.                                                                                           |  |

| INHC    | 6      | I   | Bridge PWM input                                                                                        | PWM input signal for bridge C high-side.                                                                                          |  |

| INLC    | 7      | I   | Bridge PWM input                                                                                        | PWM input signal for bridge C low-side.                                                                                           |  |

| nFAULT  | 8      | OD  | Fault indicator                                                                                         | When low indicates a fault has occurred; open drain; external pullup to MCU power supply needed (1 k $\Omega$ to 10 k $\Omega$ ). |  |

| nSCS    | 9      | I   | SPI chip select                                                                                         | Select/enable for SPI; active low.                                                                                                |  |

| SDI     | 10     | I   | SPI input                                                                                               | Pl input SPl input signal.                                                                                                        |  |

| SDO     | 11     | 0   | SPI output                                                                                              | SPI output signal.                                                                                                                |  |

| SCLK    | 12     | I   | SPI clock                                                                                               | SPI clock signal.                                                                                                                 |  |

| PWRGD   | 13     | OD  | Power good                                                                                              | VREG and MCU watchdog fault indication; open drain; external pullup to MCU power supply needed (1 k $\Omega$ to 10 k $\Omega$ ).  |  |

| GND     | 14, 45 | Р   | Device ground                                                                                           | Must be connected to ground.                                                                                                      |  |

| AVDD    | 15     | Р   | Analog regulator 5-V internal analog supply regulator; bypass to GND wit 6.3-V, 1-µF ceramic capacitor. |                                                                                                                                   |  |

| SO1     | 16     | 0   | Current amplifier output Output of current sense amplifier 1.                                           |                                                                                                                                   |  |

| SO2     | 17     | 0   | Current amplifier output                                                                                | Output of current sense amplifier 2.                                                                                              |  |

| SO3     | 18     | 0   | Current amplifier output                                                                                | Output of current sense amplifier 3.                                                                                              |  |

DRV8305-Q1 JAJSHP7D-MAY 2015-REVISED JULY 2019 TEXAS INSTRUMENTS

www.ti.com

# Pin Functions (continued)

| F       | PIN  |     |                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                |

|---------|------|-----|-----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME    | NO.  | I/O |                                                                       | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                    |

| SN3     | 19   | I   | Current amplifier negative input                                      | Negative input of current sense amplifier 3.                                                                                                                                                                                                                                                                                                                                                   |

| SP3     | 20   | I   | Current amplifier positive input                                      | Positive input of current sense amplifier 3.                                                                                                                                                                                                                                                                                                                                                   |

| SN2     | 21   | I   | Current amplifier negative input                                      | Negative input of current sense amplifier 2.                                                                                                                                                                                                                                                                                                                                                   |

| SP2     | 22   | I   | Current amplifier positive input                                      | Positive input of current sense amplifier 2.                                                                                                                                                                                                                                                                                                                                                   |

| SN1     | 23   | I   | Current amplifier negative input                                      | Negative input of current sense amplifier 1.                                                                                                                                                                                                                                                                                                                                                   |

| SP1     | 24   | I   | Current amplifier positive input                                      | Positive input of current sense amplifier 1.                                                                                                                                                                                                                                                                                                                                                   |

| GLC     | 25   | 0   | Low-side gate driver                                                  | Low-side gate driver output for half-bridge C.                                                                                                                                                                                                                                                                                                                                                 |

| SLC     | 26   | I   | Low-side source connection                                            | Low-side source connection for half-bridge C.                                                                                                                                                                                                                                                                                                                                                  |

| SHC     | 27   | I   | High-side source connection                                           | High-side source connection for half-bridge C.                                                                                                                                                                                                                                                                                                                                                 |

| GHC     | 28   | 0   | High-side gate driver                                                 | High-side gate driver output for half-bridge C.                                                                                                                                                                                                                                                                                                                                                |

| GHB     | 29   | 0   | High-side gate driver                                                 | High-side gate driver output for half-bridge B.                                                                                                                                                                                                                                                                                                                                                |

| SHB     | 30   | I   | High-side source connection                                           | High-side source connection for half-bridge B.                                                                                                                                                                                                                                                                                                                                                 |

| SLB     | 31   | I   | Low-side source connection                                            | Low-side source connection for half-bridge B.                                                                                                                                                                                                                                                                                                                                                  |

| GLB     | 32   | 0   | Low-side gate driver                                                  | Low side gate driver output for half-bridge B.                                                                                                                                                                                                                                                                                                                                                 |

| GLA     | 33   | 0   | Low-side gate driver                                                  | Low-side gate driver output for half-bridge A.                                                                                                                                                                                                                                                                                                                                                 |

| SLA     | 34   | I   | Low-side source connection                                            | Low-side source connection for half-bridge A.                                                                                                                                                                                                                                                                                                                                                  |

| SHA     | 35   | I   | High-side source connection                                           | High-side source connection for half-bridge A.                                                                                                                                                                                                                                                                                                                                                 |

| GHA     | 36   | 0   | ligh-side gate driver High-side gate driver output for half-bridge A. |                                                                                                                                                                                                                                                                                                                                                                                                |

| VCP_LSD | 37   | Р   | Low-side gate driver regulator                                        | Internal voltage regulator for low-side gate driver; connect 1- $\mu$ F capacitor to GND.                                                                                                                                                                                                                                                                                                      |

| VCPH    | 38   | Р   | High-side gate driver regulator                                       | Internal charge pump for high-side gate driver; connect 2.2- $\mu\text{F}$ capacitor to PVDD.                                                                                                                                                                                                                                                                                                  |

| CP2H    | 39   | Р   | Charge pump flying capacitor                                          | Flying capacitor for charge pump; connect 0.047-µF                                                                                                                                                                                                                                                                                                                                             |

| CP2L    | 40   | Р   | Charge pump hying capacitor                                           | capacitor between CP2H and CP2L.                                                                                                                                                                                                                                                                                                                                                               |

| PVDD    | 41   | Р   | Power supply                                                          | Device power supply; minimum 4.7- $\mu$ F ceramic capacitor to GND.                                                                                                                                                                                                                                                                                                                            |

| CP1L    | 42   | Р   | Charge nume flying conseitor                                          | Flying capacitor for charge pump; connect 0.047-µF                                                                                                                                                                                                                                                                                                                                             |

| CP1H    | 43   | Р   | Charge pump flying capacitor                                          | capacitor between CP1H and CP1L.                                                                                                                                                                                                                                                                                                                                                               |

| VDRAIN  | 44   | Р   | High-side drain                                                       | High-side MOSFET drain connection; common for all three half bridges.                                                                                                                                                                                                                                                                                                                          |

| DVDD    | 46   | Р   | Digital regulator                                                     | 3.3-V internal digital-supply regulator; bypass to GND with a 6.3-V, 1- $\mu F$ ceramic capacitor.                                                                                                                                                                                                                                                                                             |

| WAKE    | 47   | I   | Wake up from sleep control pin                                        | High voltage tolerant input pin to wake-up device from SLEEP; pin cannot be used to disable LDO; driver needs to be enabled and disabled separately.                                                                                                                                                                                                                                           |

| VREG    | 48   | Ρ   | VREG/VREF                                                             | Dual purpose pin based on part number; also supplies<br>internal amplifier reference voltage and SDO pullup.<br>VREG: 3.3-V or 5-V, 50-mA LDO; connect 1-µF to GND.<br>VREF: Reference voltage; LDO disabled.<br>If PVDD voltage is lower than VREF pin voltage, there is a<br>current path from VREF to PVDD through the internal LDO.<br>The current must be limited to 50 mA by the system. |

| GND     | PPAD | Р   | Device ground                                                         | Must be connected to ground.                                                                                                                                                                                                                                                                                                                                                                   |

# 7 Specifications

## 7.1 Absolute Maximum Ratings

over operating temperature range with respect to GND (unless otherwise noted)<sup>(1)</sup>

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | MIN                                                                                                                                        | MAX       | UNIT |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-----------|------|

| High-side charge pump pin voltage (VCPH)         Low-side regulator pin voltage (VCP_LSD)         Charge pump 1 positive switching pin voltage (CP1H)         PV         Charge pump 2 positive switching pin voltage (CP2H)         P         Charge pump negative switching pin voltage (CP2L)         High-side gate driver pin voltage (GHx)         Gate-to-source voltage difference (GHx-SHx), (GLx-SLx)         Low-side gate driver pin voltage (GLx)         High-side gate driver source voltage (SHx)         Transient 200-ns high-side gate driver source voltage (SHx)         Low-side gate driver source voltage (SLx)         Transient 200-ns low-side gate driver source voltage (SLx)         Drain pin voltage (INHx, INLx, EN_GATE, SCLK, SDI, SCS, SDO, nFAULT, PWRGD)         Wake pin voltage (WAKE)         Sense amplifier voltage (SPx, SNx)         Transient 200-ns sense amplifier voltage (SPx, SNx)         Sense amplifier voltage (SPx, SNx)         Sense amplifier voltage (VDRAIN)         Control pin voltage (WAKE)         Sense amplifier voltage (SPx, SNx)         Transient 200-ns sense amplifier voltage (SPx, SNx)         Sense amplifier voltage (SPx, SNx)         Sense amplifier voltage (SPx, SNx)         Sense amplifier voltage (DVD)         Internal digital regulator voltage (DVDD)         Interna                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -0.3                                                                                                                                       | 45        | V    |

| Low-side regulator pin voltage (VCP_LSD)       P         Charge pump 1 positive switching pin voltage (CP1H)       PV         Charge pump 2 positive switching pin voltage (CP2H)       P         Charge pump negative switching pin voltage (CP2L)       P         High-side gate driver pin voltage (GHx)       Gate-to-source voltage difference (GHx-SHx), (GLx-SLx)       P         Low-side gate driver pin voltage (GLx)       High-side gate driver source voltage (SHx)       P         High-side gate driver source voltage (SHx)       Transient 200-ns high-side gate driver source voltage (SHx)       P         Low-side gate driver source voltage (SLx)       Transient 200-ns low-side gate driver source voltage (SLx)       P         Transient 200-ns low-side gate driver source voltage (SLx)       P       P         Drain pin voltage (VDRAIN)       Control pin voltage (VDRAIN)       P         Control pin voltage (WAKE)       Sense amplifier voltage (SPx, SNx)       P         Transient 200-ns sense amplifier voltage (SPx, SNx)       P       P         Sense amplifier voltage (SPx, SNx)       P       P         Transient 200-ns sense amplifier voltage (SPx, SNx)       P       P         Sense amplifier voltage (SPx, SNx)       P       P         Sense amplifier voltage (DVD)       P       P         Internal digital regulator voltage (DVDD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0                                                                                                                                          | 2         | V/µs |

| Charge pump 1 positive switching pin voltage (CP1H)PVCharge pump 2 positive switching pin voltage (CP2H)PCharge pump negative switching pin voltage (CP2L)PHigh-side gate driver pin voltage (GHx)GGate-to-source voltage difference (GHx-SHx), (GLx-SLx)ILow-side gate driver source voltage (SHx)IHigh-side gate driver source voltage (SHx)ITransient 200-ns high-side gate driver source voltage (SHx)ILow-side gate driver source voltage (SHx)ILow-side gate driver source voltage (SLx)IDrain pin voltage (VDRAIN)IControl pin voltage (SPx, SNx)ISense amplifier voltage (SPx, SNx)ITransient 200-ns sense amplifier voltage (SPx, SNx)ISense amplifier voltage (SPx, SNx)ITransient 200-ns sense amplifier voltage (SPx, SNx)ISense amplifier voltage (SPx, SNx)ITransient 200-ns sense amplifier voltage (SPx, SNx)ISense amplifier voltage (SDx)IExternally applied reference sink current, DRV8305N (VREG)IInternal digital regulator voltage (AVDD)IOpen drain pins sink current (nFAULT, PWRGD)IWake pin sink current (mFAULT, PWRGD)IWake pin sink current (WAKE) – limit current with external resistorIIurction temperature TIDRV8305XQPHPQ1I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -0.3                                                                                                                                       | PVDD + 12 | V    |

| Charge pump 2 positive switching pin voltage (CP2H)       P         Charge pump negative switching pin voltage (CP2L)       I         High-side gate driver pin voltage (GHx)       Gate-to-source voltage difference (GHx-SHx), (GLx-SLx)       I         Low-side gate driver pin voltage (GLx)       I         High-side gate driver source voltage (SHx)       I         Transient 200-ns high-side gate driver source voltage (SHx)       I         Low-side gate driver source voltage (SLx)       I         Transient 200-ns high-side gate driver source voltage (SLx)       I         Drain pin voltage (VDRAIN)       I         Control pin voltage (NAKE)       I         Sense amplifier voltage (SPx, SNx)       I         Transient 200-ns sense amplifier voltage (SPx, SNx)       I         Transient 200-ns sense amplifier voltage (SPx, SNx)       I         Sense amplifier output pin voltage (SOx)       I         Externally applied reference voltage (DVDD)       I         Internal digital regulator voltage (AVDD)       I         Open drain pins sink current (nFAULT, PWRGD)       I         Wake pin sink current (NFAULT, PWRGD)       I         Make pin sink current (NFAULT, PWRGD)       I         Internal analog regulator voltage (AVDD)       I         Open drain pins sink current (nFAULT, PWRGD)       <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -0.3                                                                                                                                       | 12        | V    |

| Charge pump negative switching pin voltage (CPxL)<br>High-side gate driver pin voltage (GHx)<br>Gate-to-source voltage difference (GHx-SHx), (GLx-SLx)<br>Low-side gate driver pin voltage (GLx)<br>High-side gate driver source voltage (SHx)<br>Transient 200-ns high-side gate driver source voltage (SHx)<br>High-side gate driver source voltage (SHx)<br>Low-side gate driver source voltage (SHx)<br>Low-side gate driver source voltage (SLx)<br>Transient 200-ns low-side gate driver source voltage (SLx)<br>Transient 200-ns low-side gate driver source voltage (SLx)<br>Drain pin voltage (VDRAIN)<br>Control pin voltage (VDRAIN)<br>Control pin voltage (INHx, INLx, EN_GATE, SCLK, SDI, SCS, SDO, nFAULT, PWRGD)<br>Wake pin voltage (WAKE)<br>Sense amplifier voltage (SPx, SNx)<br>Transient 200-ns sense amplifier voltage (SPx, SNx)<br>Sense amplifier output pin voltage (SOx)<br>Externally applied reference voltage, DRV8305N (VREG)<br>Externally applied reference sink current, DRV8305N (VREG)<br>Internal analog regulator voltage (AVDD)<br>Open drain pins sink current (nFAULT, PWRGD)<br>Wake pin sink current (NFAULT, PWRGD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | PVDD – 1.5                                                                                                                                 | PVDD + 12 | V    |

| High-side gate driver pin voltage (GHx)       Gate-to-source voltage difference (GHx-SHx), (GLx-SLx)         Low-side gate driver pin voltage (GLx)       High-side gate driver pin voltage (GLx)         High-side gate driver source voltage (SHx)       Transient 200-ns high-side gate driver source voltage (SHx)         Low-side gate driver source voltage (SHx)       Low-side gate driver source voltage (SHx)         Low-side gate driver source voltage (SLx)       Transient 200-ns low-side gate driver source voltage (SLx)         Transient 200-ns low-side gate driver source voltage (SLx)       Drain pin voltage (VDRAIN)         Control pin voltage (INHx, INLx, EN_GATE, SCLK, SDI, SCS, SDO, nFAULT, PWRGD)       Wake pin voltage (WAKE)         Sense amplifier voltage (SPx, SNx)       Transient 200-ns sense amplifier voltage (SPx, SNx)         Sense amplifier output pin voltage (SOx)       Externally applied reference voltage, DRV8305N (VREG)         Externally applied reference sink current, DRV8305N (VREG)       Internal digital regulator voltage (AVDD)         Open drain pins sink current (nFAULT, PWRGD)       Wake pin sink current (wAKE) – limit current with external resistor         Wake pin sink current (WAKE) – limit current with external resistor       DRV8305XQPHPQ1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | PVDD – 3                                                                                                                                   | PVDD + 12 | V    |

| Gate-to-source voltage difference (GHx-SHx), (GLx-SLx)       I         Low-side gate driver pin voltage (GLx)       I         High-side gate driver source voltage (SHx)       I         Transient 200-ns high-side gate driver source voltage (SHx)       I         High-side gate driver source voltage (SLx)       I         Transient 200-ns high-side gate driver source voltage (SLx)       I         Transient 200-ns low-side gate driver source voltage (SLx)       I         Transient 200-ns low-side gate driver source voltage (SLx)       I         Drain pin voltage (VDRAIN)       I         Control pin voltage (INHx, INLx, EN_GATE, SCLK, SDI, SCS, SDO, nFAULT, PWRGD)       I         Wake pin voltage (WAKE)       I         Sense amplifier voltage (SPx, SNx)       I         Transient 200-ns sense amplifier voltage (SOx)       I         Externally applied reference voltage, DRV8305N (VREG)       I         Externally applied reference sink current, DRV8305N (VREG)       I         Internal digital regulator voltage (AVDD)       I         Open drain pins sink current (nFAULT, PWRGD)       I         Wake pin sink current (WAKE) – limit current with external resistor       I         Internal resistor       I       I         Internal resistor       I       I         Internal resistor resident r                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -0.3                                                                                                                                       | PVDD      | V    |

| Low-side gate driver pin voltage (GLx)<br>High-side gate driver source voltage (SHx)<br>Transient 200-ns high-side gate driver source voltage (SHx)<br>High-side gate driver source voltage (SHx)<br>Low-side gate driver source voltage (SLx)<br>Transient 200-ns low-side gate driver source voltage (SLx)<br>Drain pin voltage (VDRAIN)<br>Control pin voltage (VDRAIN)<br>Control pin voltage (INHx, INLx, EN_GATE, SCLK, SDI, SCS, SDO, nFAULT, PWRGD)<br>Wake pin voltage (WAKE)<br>Sense amplifier voltage (SPx, SNx)<br>Transient 200-ns sense amplifier voltage (SPx, SNx)<br>Sense amplifier output pin voltage (SOx)<br>Externally applied reference voltage, DRV8305N (VREG)<br>Externally applied reference sink current, DRV8305N (VREG)<br>Internal digital regulator voltage (AVDD)<br>Open drain pins sink current (nFAULT, PWRGD)<br>Wake pin sink current (WAKE) – limit current with external resistor<br>Income temperature, T, DRV8305XQPHPQ1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | -5                                                                                                                                         | 57        | V    |

| High-side gate driver source voltage (SHx)         Transient 200-ns high-side gate driver source voltage (SHx)         High-side gate driver source voltage (SHx)         Low-side gate driver source voltage (SLx)         Transient 200-ns low-side gate driver source voltage (SLx)         Drain pin voltage (VDRAIN)         Control pin voltage (INHx, INLx, EN_GATE, SCLK, SDI, SCS, SDO, nFAULT, PWRGD)         Wake pin voltage (WAKE)         Sense amplifier voltage (SPx, SNx)         Transient 200-ns sense amplifier voltage (SPx, SNx)         Sense amplifier output pin voltage (SOx)         Externally applied reference voltage (DVDD)         Internal digital regulator voltage (AVDD)         Open drain pins sink current (nFAULT, PWRGD)         Wake pin sink current (WAKE) – limit current with external resistor         Junction temperature, T,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -0.3                                                                                                                                       | 15        | V    |

| Transient 200-ns high-side gate driver source voltage (SHx)         High-side gate driver source voltage (SHx)         Low-side gate driver source voltage (SLx)         Transient 200-ns low-side gate driver source voltage (SLx)         Drain pin voltage (VDRAIN)         Control pin voltage (INHx, INLx, EN_GATE, SCLK, SDI, SCS, SDO, nFAULT, PWRGD)         Wake pin voltage (WAKE)         Sense amplifier voltage (SPx, SNx)         Transient 200-ns sense amplifier voltage (SPx, SNx)         Sense amplifier output pin voltage (SOx)         Externally applied reference voltage (SOx)         Externally applied reference sink current, DRV8305N (VREG)         Internal analog regulator voltage (AVDD)         Open drain pins sink current (nFAULT, PWRGD)         Wake pin sink current (WAKE) – limit current with external resistor         Unction temperature T.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -3                                                                                                                                         | 12        | V    |

| High-side gate driver source voltage (SHx)       Image: Construct of the state of | -5                                                                                                                                         | 45        | V    |

| Low-side gate driver source voltage (SLx) Transient 200-ns low-side gate driver source voltage (SLx) Drain pin voltage (VDRAIN) Control pin voltage (INHx, INLx, EN_GATE, SCLK, SDI, SCS, SDO, nFAULT, PWRGD) Wake pin voltage (WAKE) Sense amplifier voltage (SPx, SNx) Transient 200-ns sense amplifier voltage (SPx, SNx) Sense amplifier output pin voltage (SOx) Externally applied reference voltage, DRV8305N (VREG) Externally applied reference sink current, DRV8305N (VREG) Internal digital regulator voltage (DVDD) Internal analog regulator voltage (AVDD) Open drain pins sink current (nFAULT, PWRGD) Wake pin sink current (WAKE) – limit current with external resistor Internal resistor DRV8305xQPHPQ1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -7                                                                                                                                         | 45        | V    |

| Transient 200-ns low-side gate driver source voltage (SLx)         Drain pin voltage (VDRAIN)         Control pin voltage (INHx, INLx, EN_GATE, SCLK, SDI, SCS, SDO, nFAULT, PWRGD)         Wake pin voltage (WAKE)         Sense amplifier voltage (SPx, SNx)         Transient 200-ns sense amplifier voltage (SPx, SNx)         Sense amplifier output pin voltage (SOx)         Externally applied reference voltage, DRV8305N (VREG)         Externally applied reference sink current, DRV8305N (VREG)         Internal digital regulator voltage (AVDD)         Open drain pins sink current (nFAULT, PWRGD)         Wake pin sink current (WAKE) – limit current with external resistor         Unction temperature, T,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -5                                                                                                                                         | PVDD + 5  | V    |

| Drain pin voltage (VDRAIN) Control pin voltage (INHx, INLx, EN_GATE, SCLK, SDI, SCS, SDO, nFAULT, PWRGD) Wake pin voltage (WAKE) Sense amplifier voltage (SPx, SNx) Transient 200-ns sense amplifier voltage (SPx, SNx) Sense amplifier output pin voltage (SOx) Externally applied reference voltage, DRV8305N (VREG) Externally applied reference sink current, DRV8305N (VREG) Internal digital regulator voltage (DVDD) Internal analog regulator voltage (AVDD) Open drain pins sink current (nFAULT, PWRGD) Wake pin sink current (WAKE) – limit current with external resistor Unction temperature, T,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -3                                                                                                                                         | 5         | V    |

| Control pin voltage (INHx, INLx, EN_GATE, SCLK, SDI, SCS, SDO, nFAULT, PWRGD) Wake pin voltage (WAKE) Sense amplifier voltage (SPx, SNx) Transient 200-ns sense amplifier voltage (SPx, SNx) Sense amplifier output pin voltage (SOx) Externally applied reference voltage, DRV8305N (VREG) Externally applied reference sink current, DRV8305N (VREG) Internal digital regulator voltage (DVDD) Internal analog regulator voltage (AVDD) Open drain pins sink current (nFAULT, PWRGD) Wake pin sink current (WAKE) – limit current with external resistor Internal resistor DRV8305xQPHPQ1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -5                                                                                                                                         | 5         | V    |

| Wake pin voltage (WAKE)         Sense amplifier voltage (SPx, SNx)         Transient 200-ns sense amplifier voltage (SPx, SNx)         Sense amplifier output pin voltage (SOx)         Externally applied reference voltage, DRV8305N (VREG)         Externally applied reference sink current, DRV8305N (VREG)         Internal digital regulator voltage (DVDD)         Internal analog regulator voltage (AVDD)         Open drain pins sink current (nFAULT, PWRGD)         Wake pin sink current (WAKE) – limit current with external resistor         Incrian amperature, T,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | -0.3                                                                                                                                       | 45        | V    |

| Sense amplifier voltage (SPx, SNx)         Transient 200-ns sense amplifier voltage (SPx, SNx)         Sense amplifier output pin voltage (SOx)         Externally applied reference voltage, DRV8305N (VREG)         Externally applied reference sink current, DRV8305N (VREG)         Internal digital regulator voltage (DVDD)         Internal analog regulator voltage (AVDD)         Open drain pins sink current (nFAULT, PWRGD)         Wake pin sink current (WAKE) – limit current with external resistor         Incrian temperature, T,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -0.3                                                                                                                                       | 5.5       | V    |

| Transient 200-ns sense amplifier voltage (SPx, SNx)         Sense amplifier output pin voltage (SOx)         Externally applied reference voltage, DRV8305N (VREG)         Externally applied reference sink current, DRV8305N (VREG)         Internal digital regulator voltage (DVDD)         Internal analog regulator voltage (AVDD)         Open drain pins sink current (nFAULT, PWRGD)         Wake pin sink current (WAKE) – limit current with external resistor         Incrian amograture, T,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | -0.3                                                                                                                                       | 45        | V    |

| Sense amplifier output pin voltage (SOx)         Externally applied reference voltage, DRV8305N (VREG)         Externally applied reference sink current, DRV8305N (VREG)         Internal digital regulator voltage (DVDD)         Internal analog regulator voltage (AVDD)         Open drain pins sink current (nFAULT, PWRGD)         Wake pin sink current (WAKE) – limit current with external resistor         Incrian analog regulator T,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -3                                                                                                                                         | 5         | V    |

| Externally applied reference voltage, DRV8305N (VREG)         Externally applied reference sink current, DRV8305N (VREG)         Internal digital regulator voltage (DVDD)         Internal analog regulator voltage (AVDD)         Open drain pins sink current (nFAULT, PWRGD)         Wake pin sink current (WAKE) – limit current with external resistor         Internal resistor         DRV8305xQPHPQ1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -5                                                                                                                                         | 5         | V    |

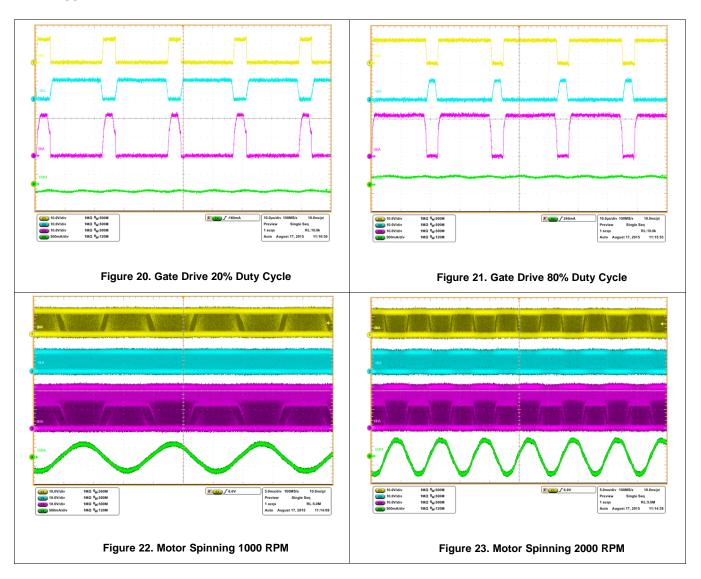

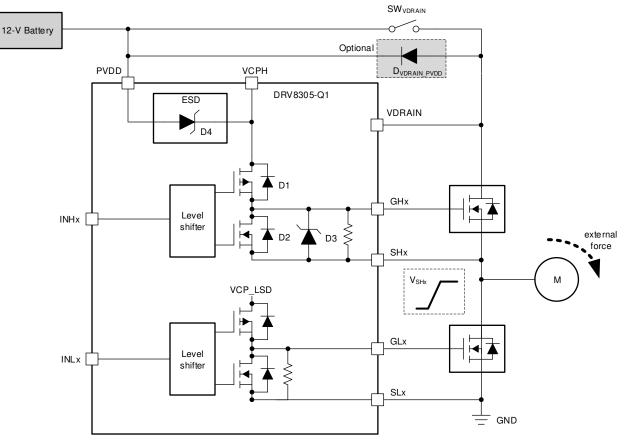

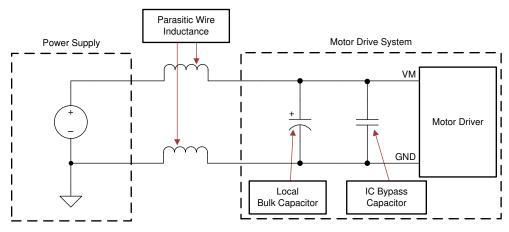

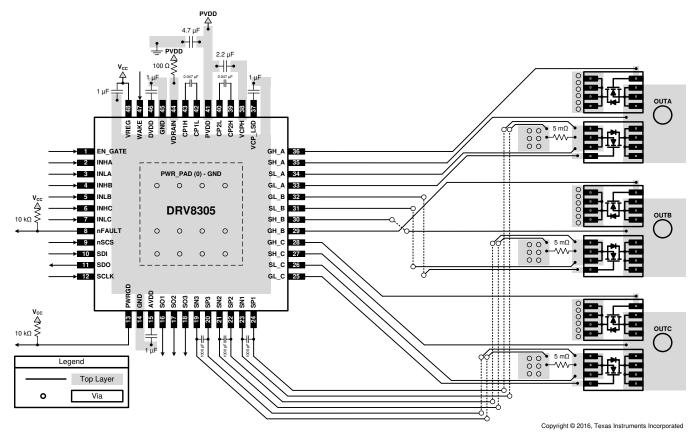

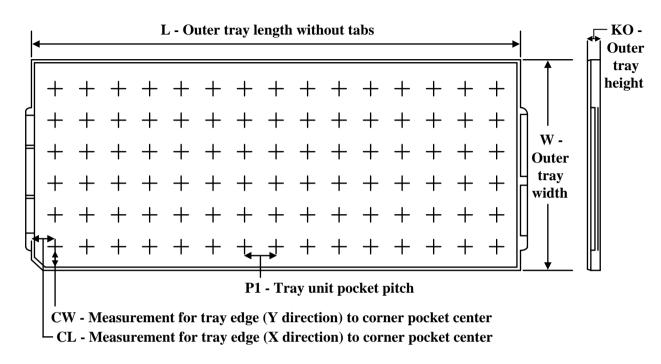

| Externally applied reference sink current, DRV8305N (VREG) Internal digital regulator voltage (DVDD) Internal analog regulator voltage (AVDD) Open drain pins sink current (nFAULT, PWRGD) Wake pin sink current (WAKE) – limit current with external resistor Unction temperature, T, DRV8305xQPHPQ1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -0.3                                                                                                                                       | 5.5       | V    |