**DS280BR810**

JAJSI55C - NOVEMBER 2015 - REVISED OCTOBER 2019

# DS280BR810 低消費電力、28Gbps、8チャネル・リニア・リピータ

### 1 特長

- 8 チャネルのマルチプロトコル・リニア・イコラ イザーで、最高 28Gbps のインターフェイスをサポート

- 低消費電力:93mW とチャネル (標準値)

- ヒートシンク不要

- リニア・イコライゼーションにより CR4/KR4 リンク・トレーニングをシームレスにサポート

- チャネルの範囲を、通常のACIS-to-ACIS能力より も15dB以上拡張

- 非常に短いレイテンシ:100ps (標準値)

- 低い付加的ランダム・ジッタ

- 小型の 8mm x 13mm BGA パッケージに RX および TX AC カップリング・コンデンサを内蔵し、フロースルー配線が簡単

- 独自のピン配置により、パッケージの下に高速信号の配線が可能

- ピン互換のRetimerを利用可能

- 単一の2.5V ±5%電源

- -40℃~+85℃の動作温度範囲

# 2 アプリケーション

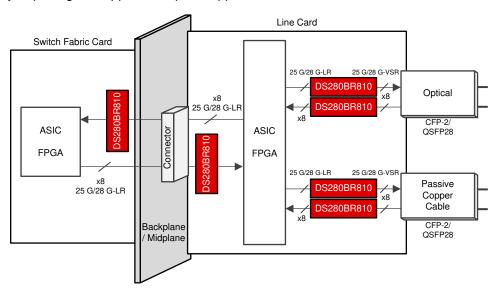

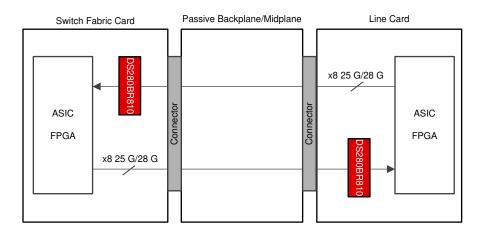

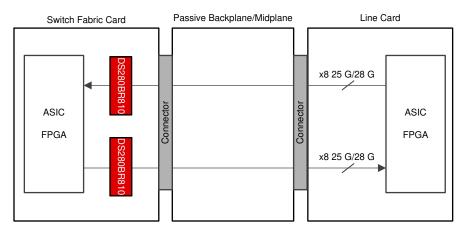

- バックプレーンおよびミッドプレーンの範囲拡張

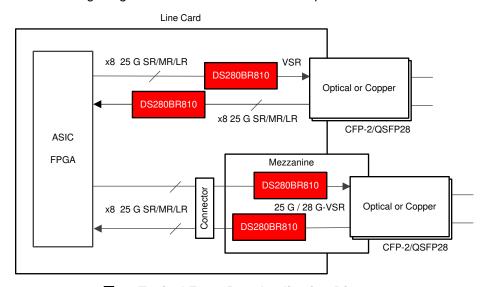

- 光およびパッシブ銅線(100G-SR4/LR4/CR4)用の フロントポート・アイ・オープナー

- QSFP28、SFP28、CFP2、CFP4、CDFP

### 3 概要

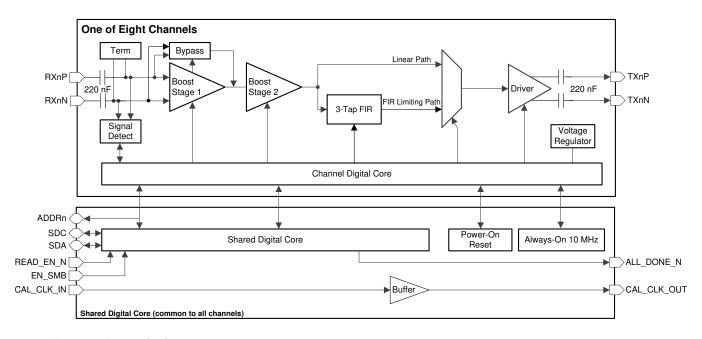

DS280BR810は非常に消費電力が低く高パフォーマンスの8チャネル・リニア・イコライザーで、マルチレート、マルチプロトコルで最大28Gbpsのインターフェイスをサポートします。フロントポート、バックプレーン、チップ・ツー・チップのアプリケーションにおいて、高速シリアル・リンクの到達範囲を拡張し、堅牢性を強化するために使用されます。

DS280BR810の均等化の直線性から、送信信号の特性が保持され、ホストとリンク・パートナーのASICが、送信イコライザーの係数を自由にネゴシエーションできるようになります(100G-CR4/KR4)。このリンク・トレーニング・プロトコルへの透過性により、レイテンシへの影響を最小限に抑えながら、システム・レベルの相互運用性を向上できます。各チャネルは独立に動作するため、DS280BR810は個別のレーン・フォワード・エラー訂正(FEC)パススルーをサポートできます。

DS280BR810 はパッケージの寸法が小さく、高速信号エスケープが最適化され、リタイマのポートフォリオとピン互換なため、高密度のバックプレーン・アプリケーションに理想的です。単純化された均等化制御、低い消費電力、非常に低い付加的ジッタから、100G-SR4/LR4/CR4などのフロントポート・インターフェイスに適しています。フットプリントが8mm×13mmと小さいため、QSFP28、SFP28、CFP2/CFP4、CDFPなど各種の標準フロントポート・コネクタに簡単に収まり、ヒートシンクの必要もありません。

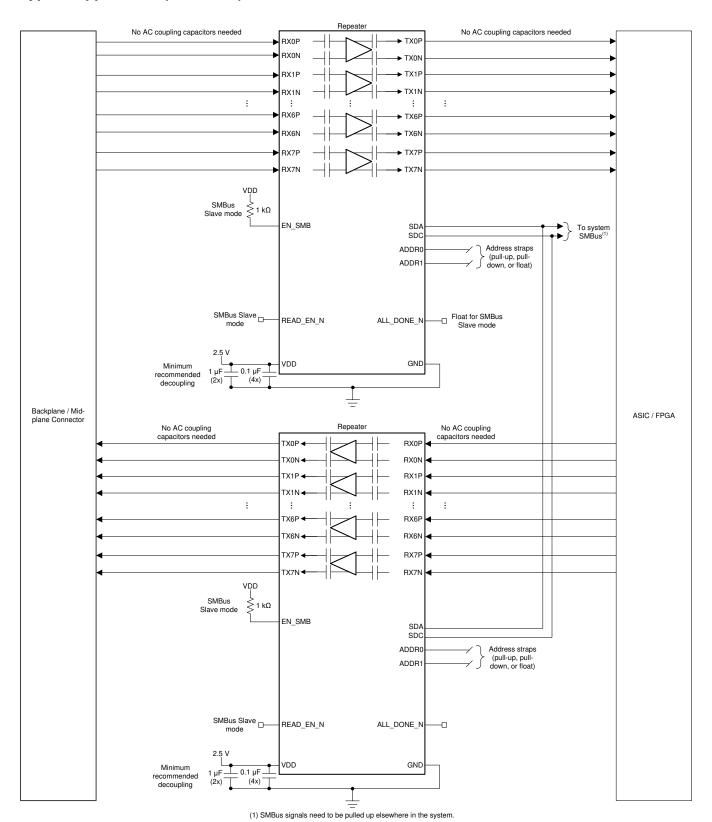

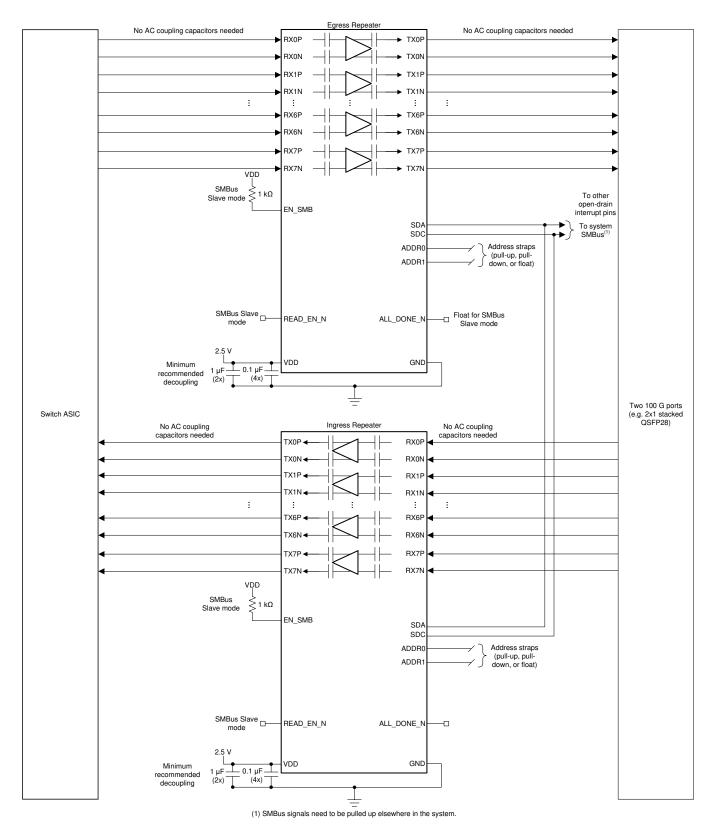

AC カップリング・コンデンサ (RX および TX) が内蔵されているため、PCB 上に外付けのコンデンサが必要ありません。DS280BR810は単一電源で、必要な外部コンポーネントも最小限です。これらの特長により、PCBの配線の複雑性と、部品表(BOM)コストを低減できます。

より到達範囲の長いアプリケーション用には、ピン互換のリタイマ・デバイスを利用可能です。

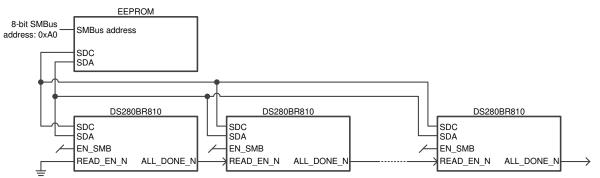

DS280BR810はSMBus経由、または外付けのEEPROM により構成可能です。単一のEEPROMを、最大16個のデバイスで共有できます。

#### 製品情報(1)

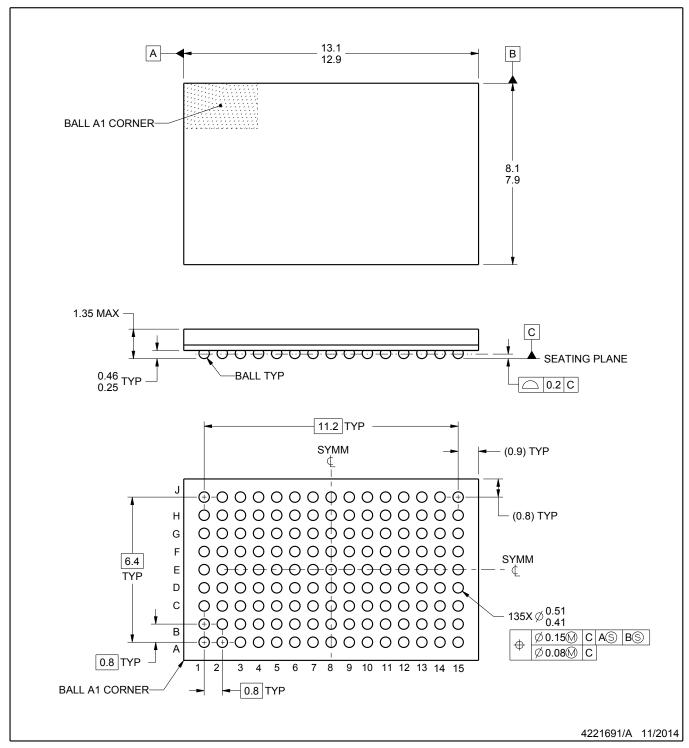

| 型番         | パッケージ       | 本体サイズ(公称)      |

|------------|-------------|----------------|

| DS280BR810 | nFBGA (135) | 8.00mm×13.00mm |

(1) 利用可能なすべてのパッケージについては、このデータシートの末 尾にある注文情報を参照してください。

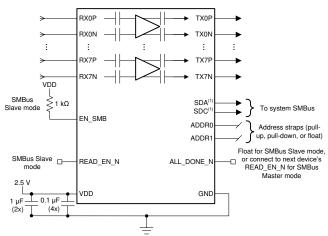

#### 概略回路図

(1) SMBus signals need to be pulled up elsewhere in the system

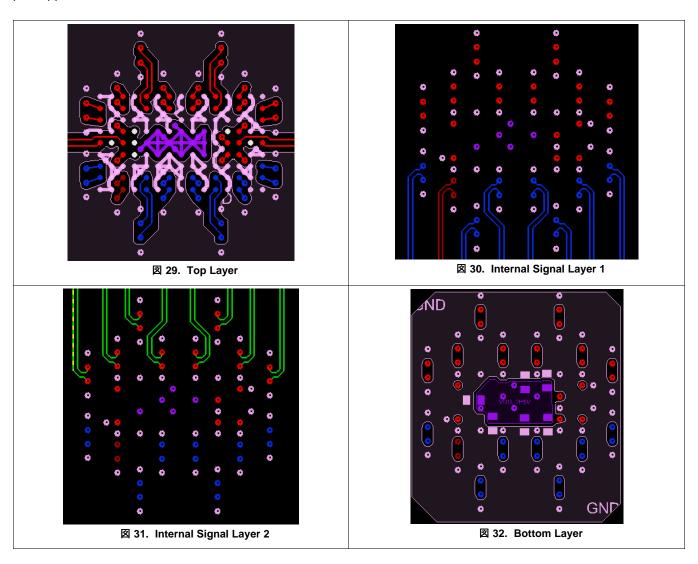

#### 目次 Device Functional Modes...... 17 特長......1 2 アプリケーション......1 Register Maps ......19 3 Application and Implementation ...... 29 4 改訂履歴.......2 5 Pin Configuration and Functions ...... 3 Specifications...... 6 8.3 Initialization Set Up .......41 Absolute Maximum Ratings ...... 6 Power Supply Recommendations......41 ESD Ratings......6 10 Layout...... 41 Recommended Operating Conditions......6 6.3 10.1 Layout Guidelines ...... 41 10.2 Layout Example ...... 41 Electrical Characteristics -- Serial Management Bus 11.1 ドキュメントのサポート......43 Timing Requirements -- Serial Management Bus ドキュメントの更新通知を受け取る方法......43 サポート・リソース......43 商標.......43 Detailed Description ...... 14 Overview ...... 14

### 4 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

Functional Block Diagram ...... 14

| Re | evision B (October 2017) から Revision C に変更 | Page |

|----|--------------------------------------------|------|

| •  | 最初の公開リリース                                  | 1    |

12 メカニカル、パッケージ、および注文情報 .......44

12.1 Package Option Addendum ...... 45

# 5 Pin Configuration and Functions

### ZBF Package 135-Pin nfBGA Top View

|   | 15                  | 14        | 13                | 12  | 11   | 10  | 9    | 8   | 7    | 6   | 5    | 4   | 3                  | 2         | 1                  |   |

|---|---------------------|-----------|-------------------|-----|------|-----|------|-----|------|-----|------|-----|--------------------|-----------|--------------------|---|

| J | GND                 | GND       | TX1N              | GND | TX2N | GND | TX3N | GND | TX4N | GND | TX5N | GND | TX6N               | GND       | GND                | J |

| Н | TX0N                | GND       | TX1P              | GND | TX2P | GND | ТХЗР | GND | TX4P | GND | TX5P | GND | TX6P               | GND       | TX7N               | Н |

| G | TX0P                | GND       | GND               | GND | GND  | GND | GND  | GND | GND  | GND | GND  | GND | GND                | GND       | ТХ7Р               | G |

| F | GND                 | GND       | READ<br>_EN_<br>N | SDC | GND  | VDD | GND  | VDD | GND  | VDD | GND  | GND | INT_N<br>(NC)      | GND       | GND                | F |

| Ε | CAL_<br>CLK_<br>OUT | TEST<br>1 | ADDR<br>1         | SDA | GND  | VDD | VDD  | VDD | VDD  | VDD | VDD  | GND | EN_S<br>MB         | TEST<br>0 | CAL_<br>CLK_<br>IN | E |

| D | GND                 | GND       | ADDR<br>0         | GND | GND  | VDD | GND  | VDD | GND  | VDD | GND  | GND | ALL_<br>DONE<br>_N | GND       | GND                | D |

| С | RX0P                | GND       | GND               | GND | GND  | GND | GND  | GND | GND  | GND | GND  | GND | GND                | GND       | RX7P               | С |

| В | RX0N                | GND       | RX1P              | GND | RX2P | GND | RX3P | GND | RX4P | GND | RX5P | GND | RX6P               | GND       | RX7N               | В |

| Α | GND                 | GND       | RX1N              | GND | RX2N | GND | RX3N | GND | RX4N | GND | RX5N | GND | RX6N               | GND       | GND                | Α |

|   | 15                  | 14        | 13                | 12  | 11   | 10  | 9    | 8   | 7    | 6   | 5    | 4   | 3                  | 2         | 1                  |   |

#### **Pin Functions**

|            | PIN         |        |                                                                                                                      |  |  |  |

|------------|-------------|--------|----------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME       | NO.         |        | DESCRIPTION                                                                                                          |  |  |  |

| HIGH SPEED | DIFFERENTIA | L I/O  |                                                                                                                      |  |  |  |

| RX0N       | B15         | Input  | Inverting and non-inverting differential inputs to the equalizer. An on-chip 100-Ω termination                       |  |  |  |

| RX0P       | C15         | Input  | resistor connects RXP to RXN. These inputs are AC coupled with 220-nF capacitors assembled on the package substrate. |  |  |  |

| RX1N       | A13         | Input  | Inverting and non-inverting differential inputs to the equalizer. An on-chip 100- $\Omega$ termination               |  |  |  |

| RX1P       | B13         | Input  | resistor connects RXP to RXN. These inputs are AC coupled with 220-nF capacitors assembled on the package substrate. |  |  |  |

| RX2N       | A11         | Input  | Inverting and non-inverting differential inputs to the equalizer. An on-chip 100- $\Omega$ termination               |  |  |  |

| RX2P       | B11         | Input  | resistor connects RXP to RXN. These inputs are AC coupled with 220-nF capacitors assembled on the package substrate. |  |  |  |

| RX3N       | A9          | Input  | Inverting and non-inverting differential inputs to the equalizer. An on-chip 100- $\Omega$ termination               |  |  |  |

| RX3P       | В9          | Input  | resistor connects RXP to RXN. These inputs are AC coupled with 220-nF capacitors assembled on the package substrate. |  |  |  |

| RX4N       | A7          | Input  | Inverting and non-inverting differential inputs to the equalizer. An on-chip 100- $\Omega$ termination               |  |  |  |

| RX4P       | В7          | Input  | resistor connects RXP to RXN. These inputs are AC coupled with 220-nF capacitors assembled on the package substrate. |  |  |  |

| RX5N       | A5          | Input  | Inverting and non-inverting differential inputs to the equalizer. An on-chip 100- $\Omega$ termination               |  |  |  |

| RX5P       | B5          | Input  | resistor connects RXP to RXN. These inputs are AC coupled with 220-nF capacitors assembled on the package substrate. |  |  |  |

| RX6N       | А3          | Input  | Inverting and non-inverting differential inputs to the equalizer. An on-chip 100- $\Omega$ termination               |  |  |  |

| RX6P       | В3          | Input  | resistor connects RXP to RXN. These inputs are AC coupled with 220-nF capacitors assembled on the package substrate. |  |  |  |

| RX7N       | B1          | Input  | Inverting and non-inverting differential inputs to the equalizer. An on-chip 100- $\Omega$ termination               |  |  |  |

| RX7P       | C1          | Input  | resistor connects RXP to RXN. These inputs are AC coupled with 220-nF capacitors assembled on the package substrate. |  |  |  |

| TX0N       | H15         | Output | Inverting and non-inverting 50-Ω driver outputs. Compatible with AC-coupled differential                             |  |  |  |

| TX0P       | G15         | Output | inputs. These outputs are AC coupled with 220-nF capacitors assembled on the package substrate.                      |  |  |  |

# Pin Functions (continued)

| PI              | PIN          |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

|-----------------|--------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| NAME            | NO.          | 1/0               | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| TX1N            | J13          | Output            | Inverting and non-inverting 50-Ω driver outputs. Compatible with AC-coupled differential                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| TX1P            | H13          | Output            | inputs. These outputs are AC coupled with 220-nF capacitors assembled on the package substrate.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| TX2N            | J11          | Output            | Inverting and non-inverting 50-Ω driver outputs. Compatible with AC-coupled differential                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| TX2P            | H11          | Output            | inputs. These outputs are AC coupled with 220-nF capacitors assembled on the package substrate.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| TX3N            | J9           | Output            | Inverting and non-inverting 50-Ω driver outputs. Compatible with AC-coupled differential                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| TX3P            | H9           | Output            | inputs. These outputs are AC coupled with 220-nF capacitors assembled on the package substrate.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| TX4N            | J7           | Output            | Inverting and non-inverting 50-Ω driver outputs. Compatible with AC-coupled differential                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| TX4P            | H7           | Output            | inputs. These outputs are AC coupled with 220-nF capacitors assembled on the package substrate.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| TX5N            | J5           | Output            | Inverting and non-inverting 50-Ω driver outputs. Compatible with AC-coupled differential                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| TX5P            | H5           | Output            | inputs. These outputs are AC coupled with 220-nF capacitors assembled on the package substrate.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| TX6N            | J3           | Output            | Inverting and non-inverting 50-Ω driver outputs. Compatible with AC-coupled differential                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| TX6P            | H3           | Output            | inputs. These outputs are AC coupled with 220-nF capacitors assembled on the package substrate.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| TX7N            | H1           | Output            | Inverting and non-inverting 50-Ω driver outputs. Compatible with AC-coupled differential                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| TX7P            | G1           | Output            | inputs. These outputs are AC coupled with 220-nF capacitors assembled on the package substrate.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| CALIBRATION     | I CLOCK PINS | (FOR SUPPOR       | RTING UPGRADE PATH TO PIN-COMPATIBLE RETIMER DEVICE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| CAL_CLK_IN      | E1           | Input             | 25-MHz (±100 PPM) 2.5-V single-ended clock from external oscillator. No stringent phase noise or jitter requirements on this clock. <i>A 25-MHz input clock is only required if there is a need to support a future upgrade to the pin-compatible Retimer device.</i> If there is no need to support a future upgrade to a pin-compatible Retimer device, then a 25-MHz clock is not required. this pin can be left floating. This input pin has a weak active pull down and can be left floating if the CAL_CLK feature is not required.                           |  |  |  |  |  |

| CAL_CLK_O<br>UT | E15          | Output            | 2.5-V buffered replica of calibration clock input (pin E1) for connecting multiple devices in a daisy-chained fashion.                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| SYSTEM MAN      | AGEMENT BU   | JS (SMBus) PIN    | S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| ADDR0           | D13<br>E13   | Input, 4-Level    | 4-level strap pins used to set the SMBus address of the device. The pin state is read on power-up. The multi-level nature of these pins allows for 16 unique device addresses. The four strap options include: 0: 1 k $\Omega$ to GND R: 10 k $\Omega$ to GND F: Float 1: 1 k $\Omega$ to VDD                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| ALL_DONE_<br>N  | D3           | Output,<br>LVCMOS | Indicates the completion of a valid EEPROM register load operation when in SMBus master mode (EN_SMB = Float): High = External EEPROM load failed or incomplete. Low = External EEPROM load successful and complete. When in SMBus slave mode (EN_SMB = 1), this output will be high-Z until READ_EN_N is driven low, at which point ALL_DONE_N will be driven low. This behavior allows the reset signal connected to READ_EN_N of one device to propagate to the subsequent devices when ALL_DONE_N is connected to READ_EN_N in an SMBus slave mode application. |  |  |  |  |  |

| EN_SMB          | E3           | Input, 4-Level    | 4-level 2.5 V input used to select between SMBus master mode (float) and SMBus slave mode (high). The four defined levels are: 0: 1 k $\Omega$ to GND - RESERVED R: 10 k $\Omega$ to GND - RESERVED F: Float - SMBus master mode 1: 1 k $\Omega$ to VDD - SMBus slave mode                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

# Pin Functions (continued)

| PIN        |                                                                                                                                                                                                                                                                                                                                                            | 1/0                                 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME       | NO.                                                                                                                                                                                                                                                                                                                                                        | I/O                                 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|            |                                                                                                                                                                                                                                                                                                                                                            |                                     | Pin has weak pull-up. This pin is 3.3 V tolerant.                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| READ_EN_N  | F13                                                                                                                                                                                                                                                                                                                                                        | Input,<br>LVCMOS                    | SMBus master mode (EN_SMB = Float): When asserted low, initiates the SMBus master mode EEPROM read function. Once EEPROM read is complete (indicated by assertion of ALL_DONE_N low), this pin can be held low for normal device operation.                                                                                                                                                                                                                                   |  |  |  |

|            |                                                                                                                                                                                                                                                                                                                                                            |                                     | SMBus slave mode (EN_SMB = 1): When asserted low, this causes the device to be held in reset (SMBus state machine reset and register reset). This pin should be pulled high or left floating for normal operation in SMBus slave mode.                                                                                                                                                                                                                                        |  |  |  |

| SDA        | E12                                                                                                                                                                                                                                                                                                                                                        | I/O, 3.3-V<br>LVCMOS,<br>Open Drain | SMBus data input or open drain output. External 2 - $\Omega$ to 5-k $\Omega$ pull-up resistor is required. This pin is 3.3-V LVCMOS tolerant.                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| SDC        | F12                                                                                                                                                                                                                                                                                                                                                        | I/O, 3.3-V<br>LVCMOS,<br>Open Drain | SMBus clock input or open drain clock output. External 2-k $\Omega$ to 5-k $\Omega$ pull-up resistor is required. This pin is 3.3-V LVCMOS tolerant.                                                                                                                                                                                                                                                                                                                          |  |  |  |

| MISCELLANE | OUS PINS                                                                                                                                                                                                                                                                                                                                                   | 1.                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| INT_N      | F3                                                                                                                                                                                                                                                                                                                                                         | No Connect                          | No connect on package. For applications using multiple repeaters and retimers, this pin should be connected to other devices' INT_N pins. This is only a recommendation for cases where there is a need to support a potential future upgrade to the pin-compatible retimer device, which uses this pin as an interrupt signal to a system controller.                                                                                                                        |  |  |  |

| TEST0      | E2                                                                                                                                                                                                                                                                                                                                                         | Input,<br>LVCMOS                    | Reserved test pin. During normal (non-test-mode) operation, this pin is configured as an input and therefore is not affected by the presence of a signal. This pin may be left floating,                                                                                                                                                                                                                                                                                      |  |  |  |

| TEST1      | E14                                                                                                                                                                                                                                                                                                                                                        | Input,<br>LVCMOS                    | tied to GND, or connected to a 2.5-V (max) output.                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| POWER      |                                                                                                                                                                                                                                                                                                                                                            |                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| GND        | A1, A2, A4, A6, A8, A10, A12, A14, A15, B2, B4, B6, B8, B10, B12, B14, C2, C3, C4, C5, C6, C7, C8, C9, C10, C11, C12, C13, C14, D1, D2, D4, D5, D7, D9, D11, D12, D14, D15, E4, E11, F1, F2, F4, F5, F7, F9, F11, F14, F15, G2, G3, G4, G5, G6, G7, G8, G9, G10, G11, G12, G13, G14, H2, H4, H6, H8, H10, H12, H14, J1, J2, J4, J6, J8, J10, J12, J14, J15 | Power                               | Ground reference. The GND pins on this device should be connected through a low-impedance path to the board GND plane.                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| VDD        | D6, D8, D10,<br>E5, E6, E7,<br>E8, E9, E10,<br>F6, F8, F10                                                                                                                                                                                                                                                                                                 | Power                               | Power supply, VDD = 2.5 V $\pm$ 5%. Use at least six de-coupling capacitors between the Repeater's VDD plane and GND as close to the Repeater as possible. For example, four 0.1- $\mu$ F capacitors and two 1- $\mu$ F capacitors directly beneath the device or as close to the VDD pins as possible. The VDD pins on this device should be connected through a low-resistance path to the board VDD plane. For more information, see <i>Power Supply Recommendations</i> . |  |  |  |

### 6 Specifications

### 6.1 Absolute Maximum Ratings

Over operating free-air temperature range (unless otherwise noted). (1)

|                            |                                                                  | MIN  | MAX  | UNIT |

|----------------------------|------------------------------------------------------------------|------|------|------|

| VDD <sub>ABSMAX</sub>      | Supply voltage (VDD)                                             | -0.5 | 2.75 | V    |

| VIO <sub>2.5V,ABSMAX</sub> | 2.5 V I/O voltage (LVCMOS and CMOS)                              | -0.5 | 2.75 | V    |

| VIO <sub>3.3V,ABSMAX</sub> | Open drain and 3.3 V-tolerance I/O voltage (SDA, SDC, READ_EN_N) | -0.5 | 4    | V    |

| VIO <sub>HS,ABSMAX</sub>   | High-speed I/O voltage (RXnP, RXnN, TXnP, TXnN)                  | -0.5 | 2.75 | V    |

| TJ <sub>ABSMAX</sub>       | Junction temperature                                             |      | 150  | °C   |

| T <sub>stg</sub>           | Storage temperature                                              | -40  | 150  | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 6.2 ESD Ratings

|                    |                         |                                                                 | VALUE | UNIT |

|--------------------|-------------------------|-----------------------------------------------------------------|-------|------|

|                    |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)          | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 | ±1000 | V    |

JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. Pins listed as ±2 kV may actually have higher performance.

### 6.3 Recommended Operating Conditions

Over operating free-air temperature range (unless otherwise noted).

|                      |                                                     |                                                 | MIN   | NOM | MAX   | UNIT |

|----------------------|-----------------------------------------------------|-------------------------------------------------|-------|-----|-------|------|

| VDD                  | Supply voltage, VDD to GND                          | DC plus AC power should not exceed these limits | 2.375 | 2.5 | 2.625 | V    |

|                      |                                                     | Supply noise, DC to <50 Hz, sinusoidal          |       |     | 250   | mVpp |

| N <sub>VDD</sub>     | Supply noise tolerance (1)                          | Supply noise, 50 Hz to 10 MHz, sinusoidal       |       |     | 20    | mVpp |

|                      |                                                     | Supply noise, >10 MHz, sinusoidal               |       |     | 10    | mVpp |

| $T_{RampVDD}$        | VDD supply ramp time                                | From 0 V to 2.375 V                             | 150   |     |       | μs   |

| $T_{J}$              | Operating junction temperature                      |                                                 | -40   |     | 110   | С    |

| T <sub>A</sub>       | Operating ambient temperature                       |                                                 | -40   |     | 85    | С    |

| VDD <sub>SMBUS</sub> | SMBus SDA and SDC Open<br>Drain Termination Voltage | Supply voltage for open drain pull-up resistor  |       |     | 3.6   | V    |

| F <sub>SMBus</sub>   | SMBus clock (SDC) frequency in SMBus slave mode     |                                                 |       |     | 400   | kHz  |

<sup>(1)</sup> Sinusoidal noise is superimposed to supply voltage with negligeable impact to device function or critical performance shown in the Electrical Table.

#### 6.4 Thermal Information

|                 | THERMAL METRIC (1)                     | CONDITIONS / ASSUMPTIONS   | VALUE | UNIT |

|-----------------|----------------------------------------|----------------------------|-------|------|

|                 | Junction-to-ambient thermal resistance | 4-layer JEDEC board        | 44.8  |      |

| D               |                                        | 10-layer 8-in x 6-in board | 26.8  | 0000 |

| $R_{\theta JA}$ |                                        | 20-layer 8-in x 6-in board | 25.1  | °C/W |

|                 |                                        | 30-layer 8-in x 6-in board | 25.4  |      |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# **Thermal Information (continued)**

|                      | THERMAL METRIC (1)                                                                                                           | CONDITIONS / ASSUMPTIONS   | VALUE | UNIT  |

|----------------------|------------------------------------------------------------------------------------------------------------------------------|----------------------------|-------|-------|

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance                                                                                    |                            | 26.5  | °C/W  |

| $R_{\theta JB}$      | Junction-to-board thermal resistance                                                                                         |                            | 28.4  | °C/W  |

|                      |                                                                                                                              | 4-layer JEDEC board        | 13.1  |       |

|                      | Junction-to-top characterization parameter  10-layer 8-in x 6-in board 20-layer 8-in x 6-in board 30-layer 8-in x 6-in board | 10-layer 8-in x 6-in board | 13.1  | 9C/M  |

| ΨJT                  |                                                                                                                              | 20-layer 8-in x 6-in board | 13.2  | °C/W  |

|                      |                                                                                                                              | 30-layer 8-in x 6-in board | 13.2  |       |

|                      |                                                                                                                              | 4-layer JEDEC board        | 25.4  |       |

|                      | lunction to board oberactorization necessary                                                                                 | 10-layer 8-in x 6-in board | 22.2  | °C/W  |

| ΨЈВ                  | Junction-to-board characterization parameter                                                                                 | 20-layer 8-in x 6-in board | 21.8  | 3C/VV |

|                      |                                                                                                                              | 30-layer 8-in x 6-in board | 21.7  |       |

# 6.5 Electrical Characteristics

|                           | PARAMETER                                                  | TEST CONDITIONS                                                                                                                         | MIN | TYP | MAX                | UNIT |

|---------------------------|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----|-----|--------------------|------|

| POWER                     |                                                            |                                                                                                                                         |     |     |                    |      |

| W                         | Dower apparentian per active channel                       | Channel enabled and in linear mode with maximum driver VOD (DRV_SEL_VOD = 3). Static power consumption not included.                    |     | 82  | 97 <sup>(1)</sup>  | mW   |

| W <sub>channel</sub>      | Power consumption per active channel                       | Channel enabled and in linear mode with minimum driver VOD (DRV_SEL_VOD = 0). Static power consumption not included.                    |     | 75  | 89 <sup>(1)</sup>  | mW   |

| W                         | Power consumption per active channel                       | Channel enabled and in FIR limiting mode with C0 = 31 and maximum driver VOD (DRV_SEL_VOD = 3).  Static power consumption not included. |     | 105 | 123 <sup>(1)</sup> | mW   |

| W <sub>channel_</sub> FIR | Power consumption per active channel                       | Channel enabled and in FIR limiting mode with C0 = 31 and minimum driver VOD (DRV_SEL_VOD = 0). Static power consumption not included.  |     | 97  | 115 <sup>(1)</sup> | mW   |

| W <sub>static_total</sub> | Idle (static) mode total device power consumption          | Channels disabled and powered down (DRV_PD = 1, EQ_PD = 1).                                                                             |     | 110 | 132 (1)            | mW   |

|                           | Active mode total device supply                            | All channels enabled and in linear mode with maximum driver VOD (DRV_SEL_VOD = 3).                                                      |     | 307 | 347                | mA   |

| I <sub>total</sub>        | current consumption                                        | All channels enabled and in linear mode with minimum driver VOD (DRV_SEL_VOD = 0).                                                      |     | 283 | 322                | mA   |

|                           | Active mode total device supply                            | All channels enabled and in FIR limiting mode with C0 = 31 and maximum driver VOD (DRV_SEL_VOD = 3).                                    |     | 380 | 426                | mA   |

| I <sub>total_</sub> FIR   | current consumption                                        | All channels enabled and in FIR limiting mode with C0 = 31 and minimum driver VOD (DRV_SEL_VOD = 0).                                    |     | 355 | 401                | mA   |

| I <sub>static_total</sub> | Idle (static) mode total device supply current consumption | All channels disabled and powered down (DRV_PD = 1, EQ_PD = 1).                                                                         |     | 44  | 50                 | mA   |

<sup>(1)</sup> Max values assume VDD = 2.5 V + 5%.

|                 | PARAMETER                        | TEST CONDITIONS                                                                                                                                                                 | MIN         | TYP           | MAX       | UNIT   |

|-----------------|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---------------|-----------|--------|

| LVCMOS          | DC SPECIFICATIONS (CAL_CLK_IN,   | CAL_CLK_OUT, READ_EN_N, ALL_DONE_I                                                                                                                                              | N, TEST[1:  | 0])           |           |        |

| 1/              | High level innertualteer         |                                                                                                                                                                                 | 1.75        |               | VDD       | V      |

| $V_{IH}$        | High level input voltage         | READ_EN_N pin only                                                                                                                                                              | 1.75        |               | 3.6       | V      |

| V <sub>IL</sub> | Low level input voltage          |                                                                                                                                                                                 | GND         |               | 0.7       | V      |

| V <sub>OH</sub> | High level output voltage        | IOH = 4 mA                                                                                                                                                                      | 2           |               |           | V      |

| V <sub>OL</sub> | Low level output voltage         | IOL = -4 mA                                                                                                                                                                     |             |               | 0.4       | V      |

|                 |                                  | Vinput = VDD, TEST[1:0] pins                                                                                                                                                    |             |               | 16        | μA     |

| I <sub>IH</sub> | Input high leakage current       | Vinput = VDD, CAL_CLK_IN pin                                                                                                                                                    |             |               | 66        | μA     |

|                 |                                  | Vinput = VDD, READ_EN_N pin (2)                                                                                                                                                 |             |               | 1         | μA     |

|                 |                                  | Vinput = 0 V, TEST[1:0] pins                                                                                                                                                    | -38         |               |           | μA     |

| I <sub>IL</sub> | Input low leakage current        | Vinput = 0 V, CAL_CLK_IN pin (3)                                                                                                                                                | -1          |               |           | μA     |

|                 |                                  | Vinput = 0 V, READ_EN_N pin (2)                                                                                                                                                 | <b>-</b> 55 |               |           | μA     |

| 4-LEVEL         | LOGIC ELECTRICAL SPECIFICATION   | S (APPLIES TO 4-LEVEL INPUT CONTROL                                                                                                                                             | PINS ADD    | R0, ADDR      | 1, and EN | N_SMB) |

| I <sub>IH</sub> | Input high leakage current       |                                                                                                                                                                                 |             |               | 105       | μA     |

| I <sub>IL</sub> | Input low leakage current        |                                                                                                                                                                                 | -253        |               |           | μA     |

|                 | High level (1) input voltage     |                                                                                                                                                                                 |             | 0.95 ×<br>VDD |           | V      |

| $V_{TH}$        | Float level input voltage        |                                                                                                                                                                                 |             | 0.67 ×<br>VDD |           | V      |

|                 | 10K to GND input voltage         |                                                                                                                                                                                 |             | 0.33 ×<br>VDD |           | V      |

|                 | Low level (0) input voltage      |                                                                                                                                                                                 |             | 0.1           |           | V      |

| HIGH-SP         | EED DIFFERENTIAL INPUTS (RXnP, R | XnN)                                                                                                                                                                            |             |               |           |        |

| DOT             |                                  | Measured with maximum CTLE setting and maximum BW setting (EQ_BST1 = 7, EQ_BST2 = 7, EQ_BW = 3).  Boost is defined as the gain at 14 GHz relative to 20 MHz.                    |             | 22.5          |           | dB     |

| BST             | CTLE high-frequency boost        | Measured with maximum CTLE setting and maximum BW setting (EQ_BST1 = 7, EQ_BST2 = 7, EQ_BW = 3).  Boost is defined as the gain at 12.9 GHz relative to 20 MHz.                  |             | 23            |           | dB     |

| BST             | CTI E high frequency baset       | Measured with minimum CTLE setting and minimum BW setting (EQ_BST1 = 0, EQ_BST2 = 0, EQ_BW = 0, EQ_EN_BYPASS = 1). Boost is defined as the gain at 14 Ghz relative to 20 MHz.   |             | 0.5           |           | dB     |

|                 | CTLE high-frequency boost        | Measured with minimum CTLE setting and minimum BW setting (EQ_BST1 = 0, EQ_BST2 = 0, EQ_BW = 0, EQ_EN_BYPASS = 1). Boost is defined as the gain at 12.9 Ghz relative to 20 MHz. |             | 1             |           | dB     |

This pin has an internal weak pull-up. This pin has an internal weak pull-down. (2) (3)

|                             | PARAMETER                                                             | TEST CONDITIONS                                                                                                                                                                              | MIN TYP | MAX | UNIT |

|-----------------------------|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----|------|

| Det                         | CTI C high fraguency gain variation                                   | Measured with maximum CTLE setting (EQ_BST1 = 7, EQ_BST2 = 7). Gain variation is defined as the total change in gain at 14 GHz due to temperature and voltage variation.                     | < 3     |     | dB   |

| BST <sub>delta</sub>        | CTLE high-frequency gain variation                                    | Measured with maximum CTLE setting (EQ_BST1 = 7, EQ_BST2 = 7). Gain variation is defined as the total change in gain at 12.9 GHz due to temperature and voltage variation.                   | < 3     |     | dB   |

| BST <sub>delta</sub> CTLE h | CTLE high frequency gain verticing                                    | Measured with minimum CTLE setting (EQ_BST1 = 0, EQ_BST2 = 0, EQ_EN_BYPASS = 1). Gain variation is defined as the total change in gain at 14 GHz due to temperature and voltage variation.   | < 2     |     | dB   |

|                             | CTLE high-frequency gain variation                                    | Measured with minimum CTLE setting (EQ_BST1 = 0, EQ_BST2 = 0, EQ_EN_BYPASS = 1). Gain variation is defined as the total change in gain at 12.9 GHz due to temperature and voltage variation. | < 2     |     | dB   |

|                             |                                                                       | 50 MHz to 3.7 GHz                                                                                                                                                                            | < -12   |     | dB   |

| RL <sub>SDD11</sub>         | Input differential return loss                                        | 3.7 GHz to 10 GHz                                                                                                                                                                            | < -10   |     | dB   |

| NLSDD11                     |                                                                       | 10 GHz to 14.1 GHz                                                                                                                                                                           | < -8    |     | dB   |

|                             |                                                                       | 14.1 GHz to 20 GHz                                                                                                                                                                           | < -6    |     | dB   |

|                             | land differential to assume a seed                                    | 100 MHz to 3.3 GHz                                                                                                                                                                           | < -35   |     | dB   |

| RL <sub>SDC11</sub>         | Input differential-to-common-mode return loss                         | 3.3 GHz to 12.9 GHz                                                                                                                                                                          | < -26   |     | dB   |

|                             |                                                                       | 12.9 GHz to 20 GHz                                                                                                                                                                           | < -22   |     | dB   |

| RL <sub>SCC11</sub>         | Input common-mode return loss                                         | 100 MHz to 10 GHz                                                                                                                                                                            | < -7    |     | dB   |

| N-SCC11                     | input common mode return 1033                                         | 10 GHz to 20 GHz                                                                                                                                                                             | < -7    |     | dB   |

| $V_{SDAT}$                  | AC signal detect assert (ON) differential voltage threshold level     | Minimum input peak-to-peak amplitude level at device pins required to assert signal detect. 25.78125 Gbps with PRBS7 pattern and 20 dB loss channel.                                         | 196     |     | mVpp |

| V <sub>SDDT</sub>           | AC signal detect de-assert (OFF) differential voltage threshold level | Maximum input peak-to-peak amplitude level at device pins which causes signal detect to de-assert. 25.78125 Gbps with PRBS7 pattern and 20 dB loss channel.                                  | 147     |     | mVpp |

| PARAMETER              |                                                                      | TEST CONDITIONS                                                                                                                                                                                                                       | MIN TYP | MAX | UNIT |

|------------------------|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----|------|

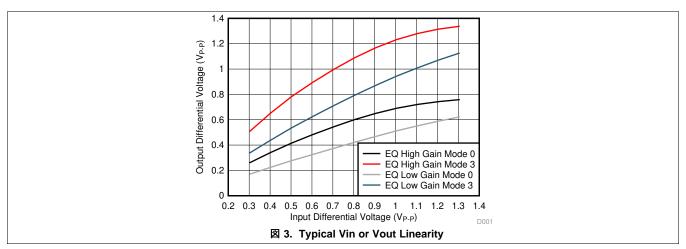

|                        |                                                                      | Measured with the highest wide-band gain setting (EQ_HIGH_GAIN = 1, DRV_SEL_VOD = 3). Measured with minimal input channel and minimum EQ using a 1 GHz signal.                                                                        | 850     | )   | mVpp |

| VID <sub>linear</sub>  | Input amplitude linear range. The maximum VID for which the repeater | Measured with a mid wide-band gain setting (EQ_HIGH_GAIN = 1, DRV_SEL_VOD = 0). Measured with minimal input channel and minimum EQ using a 1 GHz signal.                                                                              | 900     | )   | mVpp |

| VIDlinear              | remains linear, defined as ≤1 dB compression of Vout/Vin.            | Measured with a mid wide-band gain setting (EQ_HIGH_GAIN = 0, DRV_SEL_VOD = 3). Measured with minimal input channel and minimum EQ using a 1 GHz signal.                                                                              | 1050    | )   | mVpp |

|                        |                                                                      | Measured with the lowest wide-band gain setting (EQ_HIGH_GAIN = 0, DRV_SEL_VOD = 0). Measured with minimal input channel and minimum EQ using a 1 GHz signal.                                                                         | 1250    | )   | mVpp |

| HIGH-SPEED             | DIFFERENTIAL OUTPUTS (TXnP, TXn                                      | N)                                                                                                                                                                                                                                    |         |     |      |

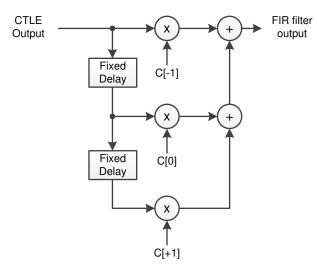

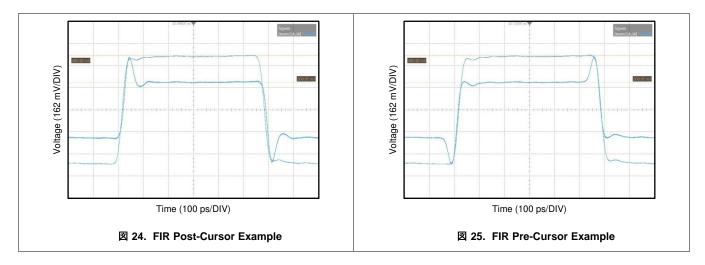

| PRE <sub>DEM-MAX</sub> | Maximum pre-cursor de-emphasis in FIR limiting mode                  | Measured with an 16T pattern at 28.125 Gbps using C(0), Reg_0x0B[4:0], set to 0x0C, C(-1), Reg_0x0D[3:0], set to 0xF, and C(+1), Reg_0x0C[3:0], set to 0x0. TX drv_sel_fir, Reg_0x06[0], set to 0x1.                                  | -11     |     | dB   |

| PST <sub>DEM-MAX</sub> | Maximum post-cursor de-emphasis in FIR limiting mode                 | Measured with an 16T pattern at 28.125 Gbps using C(0), Reg_0x0B[4:0], set to 0x0C, C(-1), Reg_0x0D[3:0], set to 0x0, and C(+1), Reg_0x0C[3:0], set to 0xF. TX drv_sel_fir, Reg_0x06[0], set to 0x1.                                  | -11     |     | dB   |

| T <sub>PRE</sub>       | Pre-cursor FIR tap delay in FIR limiting mode                        | Independent of data rate                                                                                                                                                                                                              | 28      | 3   | ps   |

| T <sub>PST</sub>       | Post-cursor FIR tap delay in FIR limiting mode                       | Independent of data rate                                                                                                                                                                                                              | 25      | 5   | ps   |

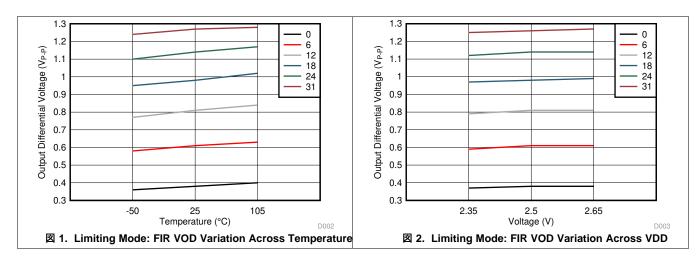

| VOD <sub>LIM-MIN</sub> | Minimum differential output amplitude in FIR limiting mode           | Measured with a 16T pattern at 25.78125 Gbps using C(0), Reg_0x0B[4:0], set to 0x00, C(-1), Reg_0x0D[3:0], set to 0x0, and C(+1), Reg_0x0C[3:0], set to 0x0. TX drv_sel_fir, Reg_0x06[0], set to 0x1. VOD, Reg_0x06[7:6], set to 0x0. | 185     | 5   | mVpp |

|                        |                                                                      | Measured with a 16T pattern at 25.78125 Gbps using C(0), Reg_0x0B[4:0], set to 0x00, C(-1), Reg_0x0D[3:0], set to 0x0, and C(+1), Reg_0x0C[3:0], set to 0x0. TX drv_sel_fir, Reg_0x06[0], set to 0x1. VOD, Reg_0x06[7:6], set to 0x3. | 360     | )   | mVpp |

|                                 | PARAMETER                                                     | TEST CONDITIONS                                                                                                                                                                                                                       | MIN TYP MA | X UNIT  |

|---------------------------------|---------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------|

| VOD                             | Maximum differential output amplitude                         | Measured with a 16T pattern at 25.78125 Gbps using C(0), Reg_0x0B[4:0], set to 0x1F, C(-1), Reg_0x0D[3:0], set to 0x0, and C(+1), Reg_0x0C[3:0], set to 0x0. TX drv_sel_fir, Reg_0x06[0], set to 0x1. VOD, Reg_0x06[7:6], set to 0x0. | 705        | mVpp    |

| VOD <sub>LIM-MAX</sub>          | in FIR limiting mode                                          | Measured with a 16T pattern at 25.78125 Gbps using C(0), Reg_0x0B[4:0], set to 0x1F, C(-1), Reg_0x0D[3:0], set to 0x0, and C(+1), Reg_0x0C[3:0], set to 0x0. TX drv_sel_fir, Reg_0x06[0], set to 0x1. VOD, Reg_0x06[7:6], set to 0x3. | 1260       | mVpp    |

| VOD <sub>idle</sub>             | Differential output amplitude, TX disabled or otherwise muted |                                                                                                                                                                                                                                       | < 10       | mVpp    |

| 0                               | Vout/Vin wide-band amplitude gain in                          | Measured with the highest wide-band gain setting (EQ_HIGH_GAIN = 1, DRV_SEL_VOD = 3) at 20 MHz.                                                                                                                                       | 4.5        | -ID     |

| $G_DC$                          | linear mode                                                   | Measured with the lowest wide-band gain setting (EQ_HIGH_GAIN = 0, DRV_SEL_VOD = 0) at 20 MHz.                                                                                                                                        | <b>-</b> 5 | dB      |

| V <sub>cm-TX-AC</sub>           | Common-mode AC output noise                                   | Defined as (TXP + TXN)/2. Measured with a low-pass filter with 3-dB bandwidth at 33 GHz.                                                                                                                                              | 6          | mV, RMS |

| RJ <sub>ADD-RMS</sub>           | Additive random jitter                                        | Measured single-endedly on a<br>Keysight E5505A phase noise<br>measurement solution with a 28-Gbps<br>1010 pattern, from 2 kHz to 20 MHz.                                                                                             | 11         | fs RMS  |

|                                 | Output differential-to-differential return loss               | 50 MHz to 4.8 GHz                                                                                                                                                                                                                     | < -12      |         |

| DI                              |                                                               | 4.8 GHz to 10 GHz                                                                                                                                                                                                                     | < -11      | -ID     |

| RL <sub>SDD22</sub>             |                                                               | 10 GHz to 14.1 GHz                                                                                                                                                                                                                    | < -7       | dB      |

|                                 |                                                               | 14.1 GHz to 20 GHz                                                                                                                                                                                                                    | <-6        |         |

|                                 |                                                               | 50 MHz to 6.0 GHz                                                                                                                                                                                                                     | < -21      |         |

| DI                              | Output common-mode-to-differential                            | 6.0 GHz to 12.9 GHz                                                                                                                                                                                                                   | < -22      | dB      |

| RL <sub>SCD22</sub>             | return loss                                                   | 12.9 GHz to 14.1 GHz                                                                                                                                                                                                                  | < –21      | UB      |

|                                 |                                                               | 14.1 GHz to 20 GHz                                                                                                                                                                                                                    | < -20      |         |

|                                 |                                                               | 50 MHz to 3.3 GHz                                                                                                                                                                                                                     | < -13      |         |

| RL <sub>SCC22</sub>             | Output common-mode return loss                                | 3.3 GHz to 10.3 GHz                                                                                                                                                                                                                   | < -11      | dB      |

|                                 |                                                               | 10.3 GHz to 20 GHz                                                                                                                                                                                                                    | < -8       |         |

| t <sub>r</sub> , t <sub>f</sub> | Transition time (20%-80%) in FIR                              | Measured at 28.125 Gbps with 16T data pattern using C(0), Reg_0x0B[4:0], set to 0x00, C(-1), Reg_0x0D[3:0], set to 0x0, and C(+1), Reg_0x0C[3:0], set to 0x0. TX drv_sel_fir, Reg_0x06[0], set to 0x1.                                | 19.9       | ps      |

|                                 | limiting mode                                                 | Measured at 28.125 Gbps with 16T data pattern using C(0), Reg_0x0B[4:0], set to 0x1F, C(-1), Reg_0x0D[3:0], set to 0x0, and C(+1), Reg_0x0C[3:0], set to 0x0. TX drv_sel_fir, Reg_0x06[0], set to 0x1.                                | 25.8       | ps      |

Over operating free-air temperature range (unless otherwise noted).

|                                               | PARAMETER                                                     | TEST CONDITIONS                                                                                                                                                                                                                                                        | MIN | TYP | MAX | UNIT |

|-----------------------------------------------|---------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| OTHER PA                                      | RAMETERS                                                      |                                                                                                                                                                                                                                                                        |     |     |     |      |

| t <sub>D</sub>                                | Input-to-output latency (propagation delay) through a channel | Linear mode                                                                                                                                                                                                                                                            | 100 |     |     | ps   |

| t <sub>D</sub>                                | Input-to-output latency (propagation delay) through a channel | FIR limiting mode, Reg_0x06[0]=1                                                                                                                                                                                                                                       |     | 160 |     | ps   |

| t <sub>SK</sub>                               | Channel-to-channel interpair skew                             | Latency difference between channels                                                                                                                                                                                                                                    |     | <14 |     | ps   |

| T <sub>EEPROM</sub> EEPROM configuration load | EEDDOM confirmation load time                                 | Time to assert ALL_DONE_N after REAN_EN_N has been asserted. Single device reading its configuration from an EEPROM with common channel configuration. This time scales with the number of devices reading from the same EEPROM. Does not include power-on reset time. |     |     | 4   |      |

|                                               | EEPROM configuration load time                                | Time to assert ALL_DONE_N after REAN_EN_N has been asserted. Single device reading its configuration from an EEPROM. Noncommon channel configuration. This time scales with the number of devices reading from the same EEPROM. Does not include power-on reset time.  |     |     | 7   | ms   |

| T <sub>POR</sub>                              | Power-on reset assertion time                                 | Internal power-on reset (PoR) stretch between stable power supply and deassertion of internal PoR. The SMBus address is latched on the completion of the PoR stretch, and SMBus accesses are permitted once PoR completes.                                             |     |     | 60  | ms   |

# 6.6 Electrical Characteristics -- Serial Management Bus Interface

|                 | PARAMETER                | TEST CONDITIONS                        | MIN  | TYP | MAX | UNIT |

|-----------------|--------------------------|----------------------------------------|------|-----|-----|------|

| $V_{IH}$        | Input high level voltage | SDA and SDC                            | 1.75 |     | 3.6 | V    |

| $V_{IL}$        | Input low level voltage  | SDA and SDC                            | GND  |     | 8.0 | V    |

| V <sub>OL</sub> | Output low level voltage | SDA and SDC, I <sub>OL</sub> = 1.25 mA | GND  |     | 0.4 | V    |

| C <sub>IN</sub> | Input pin capacitance    | SDA and SDC                            |      | 15  |     | pF   |

| I <sub>IN</sub> | Input current            | SDA or SDC, VINPUT = VIN, VDD,<br>GND  | -18  |     | 18  | μΑ   |

# 6.7 Timing Requirements -- Serial Management Bus Interface

|                       | PARAMETER                                                      | TEST CONDITIONS                              | MIN  | TYP  | MAX  | UNIT |  |  |  |  |

|-----------------------|----------------------------------------------------------------|----------------------------------------------|------|------|------|------|--|--|--|--|

| RECOMMEN              | RECOMMENDED SMBus SWITCHING CHARACTERISTICS (SMBus SLAVE MODE) |                                              |      |      |      |      |  |  |  |  |