**ISO6163**

# ISO6163 低消費電力、高速 6 チャネル デジタル アイソレータ、自動イネーブ ル付き

#### 1 特長

- 高エネルギー効率アプリケーションの要件をサポート する、業界標準の 6 チャネル デジタル アイソレータの ピン互換低消費電力代替品

- 高速チャネルの自動イネーブルにより、スタンバイ状態 の超低静止電流で双方向ウェークアップをサポート: V<sub>CC</sub> = 3.3V でのサイドあたりの電流 442µA (最大) (85°C)

- 高速データ チャネルで 50Mbps のデータレート

- 低速制御チャネルで 4Mbps のデータレート、自動イ ネーブル付き

- 小さい伝搬遅延:3.3V で 13.75ns (最大値)

- 堅牢な SiO<sub>2</sub> 絶縁バリア:

- 幅広い温度範囲:-40℃~125℃

- 最高 5000V<sub>RMS</sub> の絶縁定格

- 最高 10.4kV のサージ耐量

- CMTI:±50kV/µs (代表値)

- 電源電圧範囲:2.5~5.5V

- 2.5~5.5V への電圧変換

- デフォルト出力が HIGH (ISO6163)とLOW (ISO6163F)のオプション

- 堅牢な電磁両立性 (EMC)

- システムレベルでの ESD、EFT、サージ耐性

- 低い放射

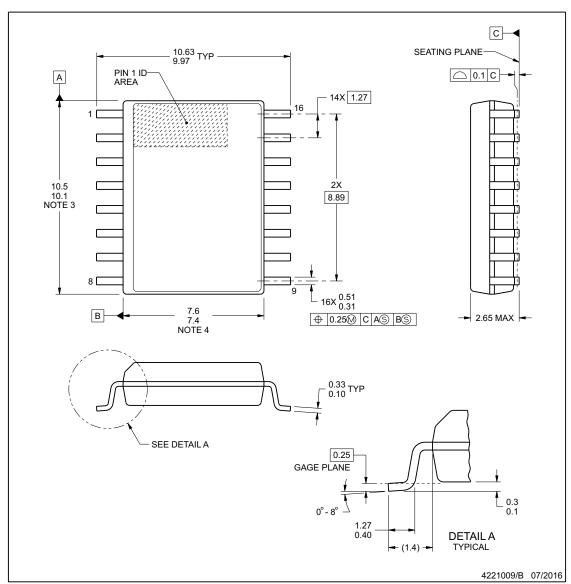

- ワイド SOIC (DW-16) パッケージ

- 安全関連の認証:

- DIN EN IEC 60747-17 (VDE 0884-17)

- UL 1577 部品認定プログラム

- IEC 62368-1, IEC 61010-1, IEC 60601-1, GB 4943.1 認定

# 2 アプリケーション

- エネルギー効率の高い製品を含む家電製品

- 電気メーターおよびグリッド

- 電源

- ファクトリ オートメーション

- ビルオートメーション

- 照明器具

- モータードライブ

#### 3 概要

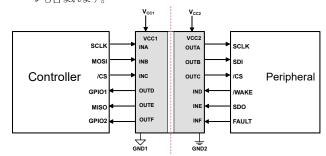

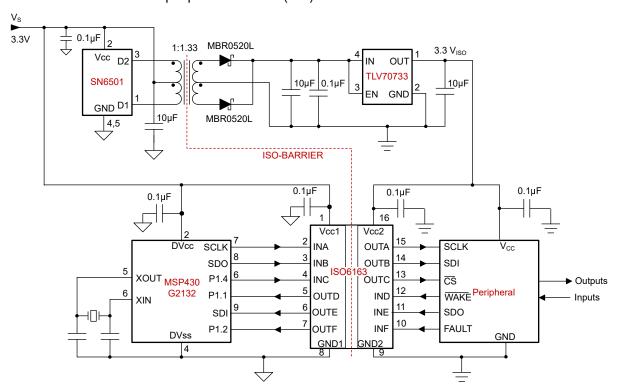

ISO6163 デバイスは、UL 1577 準拠の最大 5000V<sub>RMS</sub> の絶縁定格を必要とする、エネルギー効率が高く、コスト 重視のアプリケーション向けに設計された高性能 6 チャネ ル デジタル アイソレータです。これらのデバイスは VDE、 TUV、CSA、CQC の認定も受けています。

ISO6163 デバイスは、低静止電流で、高速データ チャネ ルの双方向自動イネーブルで最適化されており、家電製 品、バッテリ監視、メーター、グリッドなどエネルギー効率 の高いアプリケーションで使用できます。

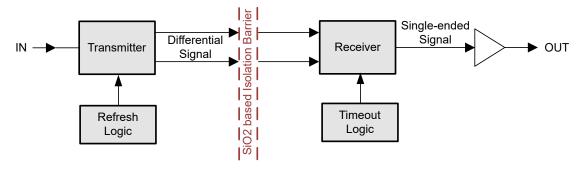

これらのデバイスは、低消費電力、高い電磁気耐性、低い 放射を実現すると同時に、以下のような CMOS または LVCMOS デジタル I/O 信号を絶縁するように設計されて います。GPIO、SPI (ADC、DAC、その他のペリフェラ ル)、UART、RS-485、RS-232、および CAN。各チャネ ルは、テキサス・インスツルメンツ独自の二酸化ケイ素 (SiO<sub>2</sub>) 絶縁バリアで分離されたロジック入力および出力バ ッファを備えています。

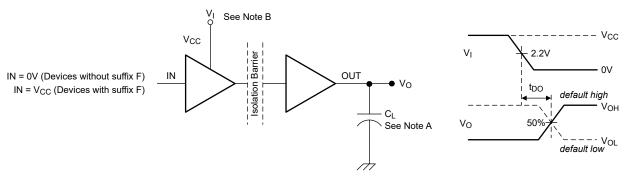

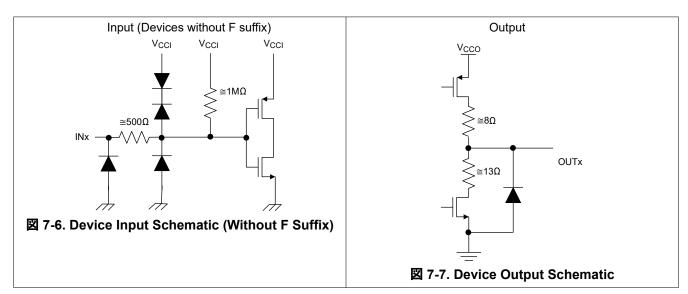

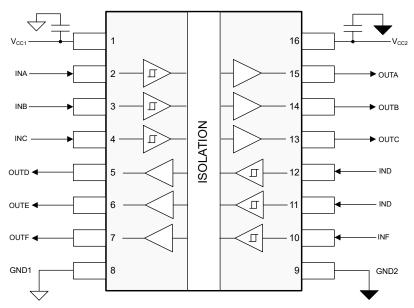

この ISO6163 デバイスには、3 本の順方向チャネルと3 本の逆方向チャネルがあります。このデバイスには、双方 向の自動イネーブル制御機能を備えた2本の低速デー タ チャネルがあります。低速制御チャネルは、必要に応じ て自動的に高速チャネルを有効にするか、システムで高 速データ転送が不要な場合にはオフにして (高インピーダ ンス出力)、消費電力をさらに低減します。入力電力または 入力信号が失われた場合のデフォルト出力レベルは、接 尾辞 F のないデバイスでは HIGH、接尾辞 F のあるデバ イスでは LOW です。

#### パッケージ情報

| 部品番号 (1) | パッケージ         | パッケージ サイズ <sup>(2)</sup> |

|----------|---------------|--------------------------|

| ISO6163  | DW (SOIC, 16) | 10.30mm × 10.30mm        |

- 詳細については、セクション 11 を参照してください。 (1)

- パッケージ サイズ (長さ×幅) は公称値であり、該当する場合はピ ンも含まれます。

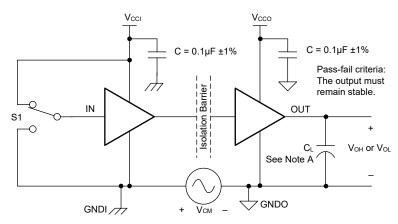

概略回路図

## **Table of Contents**

| 1 | 特長                                                 | . 1 |

|---|----------------------------------------------------|-----|

| 2 | アプリケーション                                           | 1   |

|   | 概要                                                 |     |

| 4 | Pin Configuration and Functions                    | .3  |

|   | Specifications                                     |     |

|   | 5.1 Absolute Maximum Ratings                       | . 4 |

|   | 5.2 ESD Ratings                                    |     |

|   | 5.3 Recommended Operating Conditions               |     |

|   | 5.4 Thermal Information                            | . 5 |

|   | 5.5 Power Ratings                                  |     |

|   | 5.6 Insulation Specifications                      |     |

|   | 5.7 Safety-Related Certifications                  |     |

|   | 5.8 Safety Limiting Values                         |     |

|   | 5.9 Electrical Characteristics—5V Supply (±10%)    | . 8 |

|   | 5.10 Supply Current Characteristics—5V             |     |

|   | Supply (±10%)                                      | 8   |

|   | 5.11 Electrical Characteristics—3.3V Supply (±10%) | . 9 |

|   | 5.12 Supply Current Characteristics—3.3V           |     |

|   | Supply (±10%)                                      | 9   |

|   | 5.13 Electrical Characteristics—2.5V               |     |

|   | Supply (Minimum)                                   | 10  |

|   | 5.14 Supply Current Characteristics—2.5V           |     |

|   | Supply (Minimum)                                   |     |

|   | 5.15 Switching Characteristics—5V Supply (±10%)    |     |

|   | 5.16 Switching Characteristics—3.3V Supply (±10%)  | 12  |

|   | 5.17 Switching Characteristics—2.5V                |     |

|   | Supply (Minimum)                                   | 13  |

| 5.18 Insulation Characteristics Curves               | 14 |

|------------------------------------------------------|----|

| 5.19 Typical Characteristics                         | 15 |

| 6 Parameter Measurement Information                  | 20 |

| 7 Detailed Description                               |    |

| 7.1 Overview                                         | 22 |

| 7.2 High-Speed Data Channels: A, B, E and F          | 23 |

| 7.3 Low-Speed Control Channels With Automatic        |    |

| Enable: C and D                                      | 23 |

| 7.4 Device Functional Modes                          | 26 |

| 8 Application and Implementation                     | 27 |

| 8.1 Application Information                          | 27 |

| 8.2 Typical Application                              | 27 |

| 8.3 Power Supply Recommendations                     | 29 |

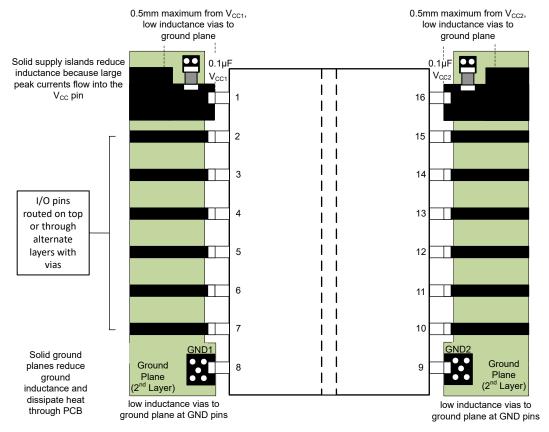

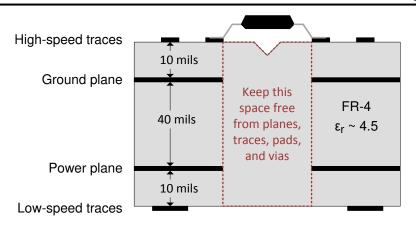

| 8.4 Layout                                           | 29 |

| 9 Device and Documentation Support                   | 32 |

| 9.1 Documentation Support                            |    |

| 9.2 Receiving Notification of Documentation Updates. | 32 |

| 9.3 サポート・リソース                                        | 32 |

| 9.4 Trademarks                                       | 32 |

| 9.5 静電気放電に関する注意事項                                    | 32 |

| 9.6 用語集                                              | 32 |

| 10 Revision History                                  |    |

| 11 Mechanical, Packaging, and Orderable              |    |

| Information                                          | 32 |

| 11.1 Package Option Addendum                         | 33 |

| 11.2 Tape and Reel Information                       | 35 |

|                                                      |    |

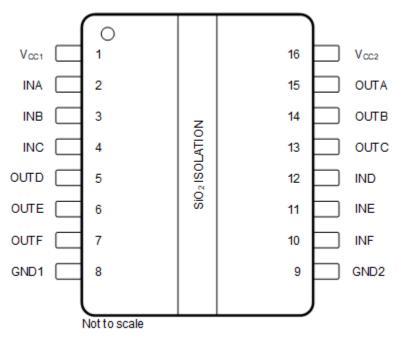

# 4 Pin Configuration and Functions

図 4-1. DW Package, 16-Pin ワイド SOIC (Top View)

表 4-1. Pin Functions

|                  | PIN | TYPE <sup>(1)</sup> | DESCRIPTION                                                                  |  |

|------------------|-----|---------------------|------------------------------------------------------------------------------|--|

| NAME             | NO. | I TPE(")            | DESCRIPTION                                                                  |  |

| V <sub>CC1</sub> | 1   | Р                   | Power supply, side 1                                                         |  |

| INA              | 2   | I                   | High-speed digital input, channel A                                          |  |

| INB              | 3   | I                   | High-speed digital input, channel B                                          |  |

| INC              | 4   | I                   | Low-speed control channel with automatic enable, channel C                   |  |

| OUTD             | 5   | 0                   | Digital output, channel D                                                    |  |

| OUTE             | 6   | 0                   | Digital output, channel E                                                    |  |

| OUTF             | 7   | 0                   | Digital output, channel F                                                    |  |

| GND1             | 8   | GND                 | Ground connection for V <sub>CC2</sub> , INA, INB, INC, OUTD, OUTE, and OUTF |  |

| GND2             | 9   | GND                 | Ground connection for V <sub>CC2</sub> , OUTA, OUTB, OUTC, IND, INE, and INF |  |

| INF              | 10  | I                   | High-speed digital input, channel F                                          |  |

| INE              | 11  | I                   | High-speed digital input, channel E                                          |  |

| IND              | 12  | I                   | Low-speed control channel with automatic enable, channel D                   |  |

| OUTC             | 13  | 0                   | Digital output, channel C                                                    |  |

| OUTB             | 14  | 0                   | Digital output, channel B                                                    |  |

| OUTA             | 15  | 0                   | Digital output, channel A                                                    |  |

| V <sub>CC2</sub> | 16  | Р                   | Power supply, side 2                                                         |  |

<sup>(1)</sup> I = input, O = output, P = power, GND = ground

## **5 Specifications**

## 5.1 Absolute Maximum Ratings

See(1)

|                    |                                                | MIN  | MAX                   | UNIT |

|--------------------|------------------------------------------------|------|-----------------------|------|

| Supply voltage (2) | V <sub>CC1</sub> to GND1                       | -0.5 | 6                     | V    |

| Supply voltage V   | V <sub>CC2</sub> to GND2                       | -0.5 | 6                     | V    |

| Input/Output       | INx to GNDx                                    | -0.5 | 6                     | V    |

| Voltage            | OUTx to GNDx                                   | -0.5 | $V_{CCX} + 0.5^{(3)}$ | V    |

| Output current     | lo                                             | -15  | 15                    | mA   |

| Temperature        | Operating junction temperature, T <sub>J</sub> |      | 150                   | °C   |

| Temperature        | Storage temperature, T <sub>stg</sub>          | -65  | 150                   | °C   |

- (1) Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

- (2) All voltage values except differential I/O bus voltages are with respect to the local ground terminal (GND1 or GND2) and are peak voltage values

- (3) Maximum voltage must not exceed 6V.

## 5.2 ESD Ratings

|                    |                         |                                                                                          | VALUE | UNIT |

|--------------------|-------------------------|------------------------------------------------------------------------------------------|-------|------|

|                    |                         | Human body model (HBM), per ANSI/<br>ESDA/JEDEC JS-001, all pins <sup>(1)</sup>          | ±4000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins <sup>(2)</sup> | ±1000 | V    |

- (1) JEDEC document JEP155 states that 500V HBM allows safe manufacturing with a standard ESD control process.

- JEDEC document JEP157 states that 250V CDM allows safe manufacturing with a standard ESD control process.

資料に関するフィードバック(ご意見やお問い合わせ)を送信

## **5.3 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)

|                      |                                |                        | MIN                                   | NOM  | MAX                                                                      | UNIT |

|----------------------|--------------------------------|------------------------|---------------------------------------|------|--------------------------------------------------------------------------|------|

| V <sub>CC1</sub> (1) | Supply Voltage Side 1          |                        | 2.5                                   |      | 5.5                                                                      | V    |

| V <sub>CC2</sub> (1) | Supply Voltage Side 2          |                        | 2.5                                   |      | 5.5                                                                      | V    |

| Vcc<br>(UVLO+)       | UVLO threshold when supply     | voltage is rising      |                                       |      | 2.45                                                                     | V    |

| Vcc<br>(UVLO-)       | UVLO threshold when supply     | voltage is falling     | 2.09                                  |      |                                                                          | V    |

| Vhys<br>(UVLO)       | Supply voltage UVLO hystere    | sis                    |                                       | 0.08 |                                                                          | V    |

| V <sub>IH</sub>      | High level Input voltage       |                        | 0.7 x V <sub>CCI</sub> <sup>(2)</sup> |      | V <sub>CCI</sub> <sup>(2)</sup>                                          | V    |

| V <sub>IL</sub>      | Low level Input voltage        |                        | 0                                     |      | 0.3 x V <sub>CCI</sub> <sup>(2)</sup>                                    | V    |

|                      |                                | $V_{CCO}^{(2)} = 5V$   | -4                                    |      |                                                                          | mA   |

| I <sub>OH</sub>      | High level output current      | $V_{CCO}^{(2)} = 3.3V$ | -4                                    |      |                                                                          | mA   |

|                      |                                | $V_{CCO}^{(2)} = 2.5V$ | -2                                    |      |                                                                          | mA   |

|                      |                                | $V_{CCO}^{(2)} = 5V$   |                                       |      | 4                                                                        | mA   |

| I <sub>OL</sub>      | Low level output current       | $V_{CCO}^{(2)} = 3.3V$ |                                       |      | 4                                                                        | mA   |

|                      |                                | $V_{CCO}^{(2)} = 2.5V$ |                                       |      | 5.5<br>5.5<br>2.45<br>V <sub>CCI</sub> (2)<br>0.3 x V <sub>CCI</sub> (2) | mA   |

| DR                   | Data Rate for channels A, B, I | E, and F               | 0                                     |      | 50                                                                       | Mhna |

| שט                   | Data Rate for channels C and   | D                      | 0                                     |      | 4                                                                        | Mbps |

| T <sub>A</sub>       | Ambient temperature            |                        | -40                                   | 25   | 125                                                                      | °C   |

$V_{CC1}$  and  $V_{CC2}$  can be set independent of one another  $V_{CCI}$  = Input-side  $V_{CC}$ ;  $V_{CCO}$  = Output-side  $V_{CC}$

## **5.4 Thermal Information**

|                      |                                                                                                                         | ISO616x   |      |

|----------------------|-------------------------------------------------------------------------------------------------------------------------|-----------|------|

|                      | Junction-to-ambient thermal resistance  Junction-to-case (top) thermal resistance  Junction-to-board thermal resistance | DW (SOIC) | UNIT |

|                      |                                                                                                                         | 16 PINS   |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance                                                                                  | 61.5      | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance                                                                               | 28.9      | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance                                                                                    | 27.8      | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter                                                                              | 9.1       | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter                                                                            | 27.3      | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance                                                                            | _         | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application

## 5.5 Power Ratings

|                 | PARAMETER                                    | TEST CONDITIONS                                                                      | MIN | TYP | MAX | UNIT |

|-----------------|----------------------------------------------|--------------------------------------------------------------------------------------|-----|-----|-----|------|

| P <sub>D</sub>  | Maximum power dissipation (both sides)       | V <sub>CC1</sub> = V <sub>CC2</sub> = 5.5V, T <sub>J</sub> = 150°C, C <sub>L</sub> = |     |     | 120 | mW   |

| P <sub>Dx</sub> | Maximum power dissipation (side-1 or side-2) | 15pF, Input a 25MHz 50% duty cycle square wave                                       |     |     | 60  | mW   |

## 5.6 Insulation Specifications

|                   | DADAMETED TEST CONDITIONS                             |                                                                                                                                                                                                                             | VALUE              | LINUT            |  |

|-------------------|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------------------|--|

|                   | PARAMETER                                             | TEST CONDITIONS                                                                                                                                                                                                             | 16-DW              | UNIT             |  |

| IEC 606           | 64-1                                                  |                                                                                                                                                                                                                             |                    |                  |  |

| CLR               | External clearance <sup>(1)</sup>                     | Side 1 to side 2 distance through air                                                                                                                                                                                       | >8                 | mm               |  |

| CPG               | External creepage <sup>(1)</sup>                      | Side 1 to side 2 distance across package surface                                                                                                                                                                            | >8                 | mm               |  |

| DTI               | Distance through the insulation                       | Minimum internal gap (internal clearance)                                                                                                                                                                                   | >17                | μm               |  |

| СТІ               | Comparative tracking index                            | IEC 60112                                                                                                                                                                                                                   | > 600              | V                |  |

|                   | Material Group                                        | According to IEC 60664-1                                                                                                                                                                                                    | I                  |                  |  |

|                   | O                                                     | Rated mains voltage ≤ 600V <sub>RMS</sub>                                                                                                                                                                                   | I-IV               | 1                |  |

|                   | Overvoltage category                                  | Rated mains voltage ≤ 1000V <sub>RMS</sub>                                                                                                                                                                                  | 1-111              | 1                |  |

| DIN EN            | IEC 60747-17 (VDE 0884-17) <sup>(2)</sup>             |                                                                                                                                                                                                                             |                    |                  |  |

| V <sub>IOTM</sub> | Maximum transient isolation voltage                   | V <sub>TEST</sub> = V <sub>IOTM</sub> , t = 60s (qualification);<br>V <sub>TEST</sub> = 1.2 x V <sub>IOTM</sub> , t= 1s (100% production)                                                                                   | 7071               | V <sub>PK</sub>  |  |

| V <sub>IMP</sub>  | Maximum impulse voltage <sup>(3)</sup>                | Tested in air, 1.2/50µs waveform per IEC 62368-1                                                                                                                                                                            | 8000               | V <sub>PK</sub>  |  |

| V <sub>IOSM</sub> | Maximum surge isolation voltage <sup>(4)</sup>        | V <sub>IOSM</sub> ≥ 1.3 x V <sub>IMP</sub> ; Tested in oil (qualification test),<br>1.2/50µs waveform per IEC 62368-1                                                                                                       | 10400              | V <sub>PK</sub>  |  |

|                   |                                                       | Method a, After Input-output safety test subgroup 2/3, $V_{ini} = V_{IOTM}$ , $t_{ini} = 60s$ ; $V_{pd(m)} = 1.2 \text{ x } V_{IORM}$ , $t_m = 10s$                                                                         | ≤ 5                |                  |  |

| q <sub>pd</sub>   | Apparent charge <sup>(5)</sup>                        | Method a, After environmental tests subgroup 1, $V_{ini} = V_{IOTM}, t_{ini} = 60s;$ $V_{pd(m)} = 1.6 \text{ x } V_{IORM}, t_m = 10s$                                                                                       | ≤ 5                | pC               |  |

|                   |                                                       | Method b: At routine test (100% production); $V_{ini} = 1.2 \times V_{IOTM}, \ t_{ini} = 1s; \\ V_{pd(m)} = 1.875 \times V_{IORM}, \ t_m = 1s \ (method \ b1) \ or \\ V_{pd(m)} = V_{ini}, \ t_m = t_{ini} \ (method \ b2)$ | ≤ 5                |                  |  |

| C <sub>IO</sub>   | Barrier capacitance, input to output <sup>(6)</sup>   | $V_{IO} = 0.4 \times \sin(2 \pi f t), f = 1MHz$                                                                                                                                                                             | ≅2.4               | pF               |  |

|                   |                                                       | V <sub>IO</sub> = 500V, T <sub>A</sub> = 25°C                                                                                                                                                                               | > 10 <sup>12</sup> |                  |  |

| R <sub>IO</sub>   | Insulation resistance, input to output <sup>(6)</sup> | V <sub>IO</sub> = 500V, 100°C ≤ T <sub>A</sub> ≤ 125°C                                                                                                                                                                      | > 10 <sup>11</sup> | Ω                |  |

|                   |                                                       | V <sub>IO</sub> = 500V at T <sub>S</sub> = 150°C                                                                                                                                                                            | > 10 <sup>9</sup>  |                  |  |

|                   | Pollution degree                                      |                                                                                                                                                                                                                             | 2                  |                  |  |

|                   | Climatic category                                     |                                                                                                                                                                                                                             | 40/125/21          |                  |  |

| UL 1577           |                                                       |                                                                                                                                                                                                                             |                    |                  |  |

| V <sub>ISO</sub>  | Withstand isolation voltage                           | $V_{TEST} = V_{ISO}$ , t = 60s (qualification); $V_{TEST} = 1.2 \times V_{ISO}$ , t = 1s (100% production)                                                                                                                  | 5000               | V <sub>RMS</sub> |  |

- (1) Creepage and clearance requirements should be applied according to the specific equipment isolation standards of an application. Care should be taken to maintain the creepage and clearance distance of a board design to ensure that the mounting pads of the isolator on the printed-circuit board do not reduce this distance. Creepage and clearance on a printed-circuit board become equal in certain cases. Techniques such as inserting grooves, ribs, or both on a printed circuit board are used to help increase these specifications.

- (2) This coupler is suitable for *safe electrical insulation* only within the safety ratings. Compliance with the safety ratings shall be ensured by means of suitable protective circuits.

- (3) Testing is carried out in air to determine the surge immunity of the package.

- (4) Testing is carried out in oil to determine the intrinsic surge immunity of the isolation barrier.

- (5) Apparent charge is electrical discharge caused by a partial discharge (pd).

- (6) All pins on each side of the barrier tied together creating a two-pin device.

## 5.7 Safety-Related Certifications

| VDE                                                                  | CSA                 | UL                                                                       | CQC                                   | TUV                                                          |

|----------------------------------------------------------------------|---------------------|--------------------------------------------------------------------------|---------------------------------------|--------------------------------------------------------------|

| Plan to certify according to<br>DIN EN IEC 60747-17<br>(VDE 0884-17) |                     | Plan to certify according to<br>UL 1577 Component<br>Recognition Program | Plan to certify according to GB4943.1 | Plan to certify according to<br>EN 61010-1 and EN<br>62368-1 |

| Certificate planned                                                  | Certificate planned | Certificate planned                                                      | Certificate planned                   | Certificate planned                                          |

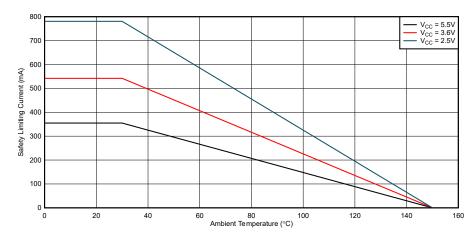

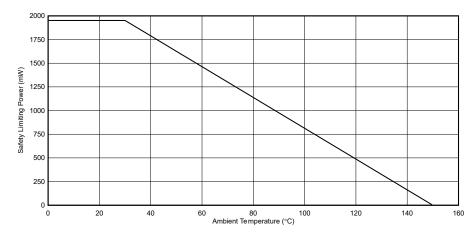

#### 5.8 Safety Limiting Values

Safety limiting<sup>(1)</sup> intends to minimize potential damage to the isolation barrier upon failure of input or output circuitry.

|                | PARAMETER                               | TEST CONDITIONS                                                                                     | MIN | TYP | MAX  | UNIT |

|----------------|-----------------------------------------|-----------------------------------------------------------------------------------------------------|-----|-----|------|------|

| DW-16          | 6 PACKAGE                               |                                                                                                     |     |     |      |      |

|                |                                         | R <sub>θJA</sub> =61.5°C/W, V <sub>I</sub> = 5.5V, T <sub>J</sub> = 150°C,<br>T <sub>A</sub> = 25°C |     |     | 369  |      |

| Is             | Safety input, output, or supply current | $R_{\theta JA} = 61.5^{\circ}C/W, V_I = 3.6V, T_J = 150^{\circ}C, T_A = 25^{\circ}C$                |     |     | 564  | mA   |

|                |                                         | $R_{\theta JA} = 61.5$ °C/W, $V_I = 2.75$ V, $T_J = 150$ °C, $T_A = 25$ °C                          |     |     | 739  |      |

| Ps             | Safety input, output, or total power    | R <sub>0JA</sub> = 61.5°C/W, T <sub>J</sub> = 150°C, T <sub>A</sub> = 25°C                          |     |     | 2032 | mW   |

| T <sub>S</sub> | Maximum safety temperature              |                                                                                                     |     |     | 150  | °C   |

(1) The maximum safety temperature, T<sub>S</sub>, has the same value as the maximum junction temperature, T<sub>J</sub>, specified for the device. The I<sub>S</sub> and P<sub>S</sub> parameters represent the safety current and safety power respectively. The maximum limits of I<sub>S</sub> and P<sub>S</sub> must not be exceeded. These limits vary with the ambient temperature, T<sub>A</sub>.

The junction-to-air thermal resistance,  $R_{\theta JA}$ , in the table is that of a device installed on a high-K test board for leaded surface-mount packages. Use these equations to calculate the value for each parameter:

$T_J = T_A + R_{\theta JA} \times P$ , where P is the power dissipated in the device.

$T_{J(max)} = T_S = T_A + R_{\theta JA} \times P_S$ , where  $T_{J(max)}$  is the maximum allowed junction temperature.  $P_S = I_S \times V_I$ , where  $V_I$  is the maximum input voltage.

## 5.9 Electrical Characteristics—5V Supply (±10%)

V<sub>CC1</sub> = V<sub>CC2</sub> = 5V ±10% (over recommended operating conditions unless otherwise noted)

|                      | PARAMETER                          | TEST CONDITIONS                                                               | MIN                                   | TYP MAX                               | UNIT  |

|----------------------|------------------------------------|-------------------------------------------------------------------------------|---------------------------------------|---------------------------------------|-------|

| V <sub>OH</sub>      | High-level output voltage          | I <sub>OH</sub> = -4mA; See 図 6-1                                             | V <sub>CCO</sub> - 0.4 <sup>(1)</sup> |                                       | V     |

| V <sub>OL</sub>      | Low-level output voltage           | I <sub>OL</sub> = 4mA; See 図 6-1                                              |                                       | 0.4                                   | V     |

| V <sub>IT+(IN)</sub> | Rising input threshold             |                                                                               |                                       | 0.7 x V <sub>CCI</sub> <sup>(1)</sup> | V     |

| V <sub>IT-(IN)</sub> | Falling input threshold            |                                                                               | 0.3 x V <sub>CCI</sub>                |                                       | V     |

| V <sub>I(HYS)</sub>  | Input threshold voltage hysteresis |                                                                               | 0.04 x V <sub>CCI</sub>               |                                       | V     |

| I <sub>IH</sub>      | High-level input current           | V <sub>IH</sub> = V <sub>CCI</sub> <sup>(1)</sup> at INx                      |                                       | 10                                    | μA    |

| I <sub>IL</sub>      | Low-level input current            | V <sub>IL</sub> = 0V at INx                                                   | -10                                   |                                       | μA    |

| I <sub>O_LP</sub>    | Low-Power mode output current      |                                                                               |                                       | 5                                     | nA    |

| СМТІ                 | Common mode transient immunity     | V <sub>I</sub> = V <sub>CC</sub> or 0V, V <sub>CM</sub> = 1200V;<br>See ☑ 6-4 | 25                                    | 50                                    | kV/µs |

| C <sub>i</sub>       | Input Capacitance (2)              | $V_I = V_{CC} + 0.4 \times \sin(2\pi ft), f = 2$<br>MHz, $V_{CC} = 5V$        |                                       | 1.7                                   | pF    |

- (1)  $V_{CCI} = Input\text{-side } V_{CC}; V_{CCO} = Output\text{-side } V_{CC}$

- (2) Measured from input pin to same side ground.

## 5.10 Supply Current Characteristics—5V Supply (±10%)

V<sub>CC1</sub> = V<sub>CC2</sub> = 5V ±10% (over recommended operating conditions unless otherwise noted)

| PARAMETER                        | TEST CONDITIONS                                                                                  |                  | SUPPLY<br>CURRENT | MIN | TYP   | MAX   | UNIT |

|----------------------------------|--------------------------------------------------------------------------------------------------|------------------|-------------------|-----|-------|-------|------|

|                                  | Device in STANDBY state. V <sub>I</sub> = VCC <sub>I</sub> on                                    | -40°C to 125°C   |                   |     | 0.375 | 0.478 |      |

|                                  | channels C and D (default level). $V_l = VCC_l$ on channels A, B, E, F (default level).          | -40°C to 85°C    |                   |     | 0.375 | 0.460 |      |

|                                  | Device in STANDBY state. $V_1 = VCC_1$ on shappeds $C_1$ and $D_2$ (default level) $V_2 = 0$ (or | –40°C to 125°C   | Icc1              |     | 0.385 | 0.495 |      |

| Supply current -<br>STANDBY (Low | channels C and D (default level). $V_I$ = 0V on channels A, B, E, F.                             | -40°C to 85°C    |                   |     | 0.385 | 0.475 |      |

| Power) <sup>(1)</sup>            | Device in STANDBY state. V <sub>I</sub> = VCC <sub>I</sub> on                                    | –40°C to 125°C   |                   |     | 0.375 | 0.478 |      |

|                                  | channels C and D (default level). $V_I = VCC_I$ on channels A, B, E, F (default level).          | -40°C to 85°C    |                   |     | 0.375 | 0.460 |      |

|                                  | Device in STANDBY state. V <sub>I</sub> = VCC <sub>I</sub> on                                    | -40°C to 125°C   | I <sub>CC2</sub>  |     | 0.385 | 0.495 |      |

|                                  | channels C and D (default level). $V_I$ = 0V on channels A, B, E, F.                             | -40°C to 85°C    |                   |     | 0.385 | 0.475 |      |

| Supply current -                 |                                                                                                  |                  | I <sub>CC1</sub>  |     | 1.3   | 1.72  |      |

| ACTIVE - DC signal (2)           | $V_I = V_{CC1}$ or $V_I = 0V$                                                                    | I <sub>CC2</sub> |                   | 1.3 | 1.72  | mA    |      |

|                                  | All channels switching with square wave clock                                                    | 1Mbps            | I <sub>CC1</sub>  |     | 1.4   | 1.86  |      |

|                                  | inputs; C <sub>L</sub> = 0pF                                                                     | Tivibps          | I <sub>CC2</sub>  |     | 1.4   | 1.86  |      |

|                                  |                                                                                                  | 10Mbps           | I <sub>CC1</sub>  |     | 2.3   | 3.01  |      |

|                                  |                                                                                                  | Томврз           | I <sub>CC2</sub>  |     | 2.3   | 3.01  |      |

| Supply current -<br>ACTIVE - AC  |                                                                                                  | 20Mbps           | I <sub>CC1</sub>  |     | 3.1   | 4.19  |      |

| signal (2)                       | A, B, E, and F channels switching with square wave clock input; C and D channels switching at    |                  | I <sub>CC2</sub>  |     | 3.1   | 4.19  |      |

|                                  | 4Mbps; C <sub>L</sub> = 0pF                                                                      | 25Mbps           | I <sub>CC1</sub>  |     | 3.5   | 4.7   |      |

|                                  |                                                                                                  | ZOMBPO           | I <sub>CC2</sub>  |     | 3.5   | 4.7   |      |

|                                  |                                                                                                  | 50Mbps           | I <sub>CC1</sub>  |     | 5.6   | 7.5   |      |

|                                  | БОМВР                                                                                            |                  | I <sub>CC2</sub>  |     | 5.6   | 7.5   |      |

- (1) Supply current valid for both INC and IND HIGH for STANDBY state.

- (2) Supply current valid for at least one of INC or IND LOW for ACTIVE state.

資料に関するフィードバック(ご意見やお問い合わせ)を送信

## 5.11 Electrical Characteristics—3.3V Supply (±10%)

$V_{CC1} = V_{CC2} = 3.3V \pm 10\%$  (over recommended operating conditions unless otherwise noted)

|                      | PARAMETER                          | TEST CONDITIONS                                                               | MIN                                   | TYP | MAX                                  | UNIT  |

|----------------------|------------------------------------|-------------------------------------------------------------------------------|---------------------------------------|-----|--------------------------------------|-------|

| V <sub>OH</sub>      | High-level output voltage          | I <sub>OH</sub> = -4mA; See 図 6-1                                             | V <sub>CCO</sub> - 0.4 <sup>(1)</sup> |     |                                      | V     |

| V <sub>OL</sub>      | Low-level output voltage           | I <sub>OL</sub> = 4mA; See 図 6-1                                              |                                       |     | 0.4                                  | V     |

| V <sub>IT+(IN)</sub> | Rising input threshold             |                                                                               |                                       | 0   | .7 x V <sub>CCI</sub> <sup>(1)</sup> | V     |

| V <sub>IT-(IN)</sub> | Falling input threshold            |                                                                               | 0.3 x V <sub>CCI</sub>                |     |                                      | V     |

| V <sub>I(HYS)</sub>  | Input threshold voltage hysteresis |                                                                               | 0.04 x V <sub>CCI</sub>               |     |                                      | V     |

| I <sub>IH</sub>      | High-level input current           | V <sub>IH</sub> = V <sub>CCI</sub> <sup>(1)</sup> at INx                      |                                       |     | 10                                   | μΑ    |

| I <sub>IL</sub>      | Low-level input current            | V <sub>IL</sub> = 0V at INx                                                   | -10                                   |     |                                      | μΑ    |

| I <sub>O_LP</sub>    | Low-Power mode output current      |                                                                               |                                       | 3   |                                      | nA    |

| СМТІ                 | Common mode transient immunity     | V <sub>I</sub> = V <sub>CC</sub> or 0V, V <sub>CM</sub> = 1200V;<br>See ⊠ 6-4 | 25                                    | 50  |                                      | kV/µs |

| C <sub>i</sub>       | Input Capacitance (2)              | $V_I = V_{CC} + 0.4 \times \sin(2\pi ft), f = 2MHz, V_{CC} = 3.3V$            |                                       | 1.7 |                                      | pF    |

- (1)  $V_{CCI} = Input-side V_{CC}$ ;  $V_{CCO} = Output-side V_{CC}$

- (2) Measured from input pin to same side ground.

# 5.12 Supply Current Characteristics—3.3V Supply (±10%)

$V_{CC1} = V_{CC2} = 3.3V \pm 10\%$  (over recommended operating conditions unless otherwise noted)

| PARAMETER                            | TEST CONDITIONS                                                                               |                                                     | SUPPLY<br>CURRENT | MIN | TYP   | MAX   | UNIT |

|--------------------------------------|-----------------------------------------------------------------------------------------------|-----------------------------------------------------|-------------------|-----|-------|-------|------|

|                                      | Device in STANDBY state. V <sub>I</sub> = VCC <sub>I</sub> on                                 | -40°C to 125°C                                      |                   |     | 0.36  | 0.458 |      |

|                                      | channels C and D (default level). $V_l = VCC_l$ on channels A, B, E, F (default level).       | –40°C to 85°C                                       | [                 |     | 0.36  | 0.442 |      |

|                                      | Device in STANDBY state. V <sub>I</sub> = VCC <sub>I</sub> on                                 | -40°C to 125°C                                      | ICC1              |     | 0.366 | 0.465 |      |

| Supply current -<br>STANDBY (Low     | channels C and D (default level). $V_I$ = 0V on channels A, B, E, F.                          | -40°C to 85°C                                       |                   |     | 0.366 | 0.448 |      |

| Power) (1)                           | Device in STANDBY state. V <sub>I</sub> = VCC <sub>I</sub> on                                 | -40°C to 125°C                                      |                   |     | 0.36  | 0.458 |      |

|                                      | channels C and D (default level). $V_l = VCC_l$ on channels A, B, E, F (default level).       | –40°C to 85°C                                       |                   |     | 0.36  | 0.442 |      |

|                                      | Device in STANDBY state. $V_1 = VCC_1$ on                                                     | -40°C to 125°C                                      | ICC2              |     | 0.366 | 0.465 |      |

|                                      | channels C and D (default level). $V_I$ = 0V on channels A, B, E, F.                          | 1). $V_1 = 0V$ on $-40^{\circ}$ C to $85^{\circ}$ C |                   |     | 0.366 | 0.448 |      |

| Supply current -                     |                                                                                               |                                                     | I <sub>CC1</sub>  |     | 1.24  | 1.67  |      |

| ACTIVE - DC<br>signal <sup>(2)</sup> | $V_I = V_{CC1}$ or $V_I = 0V$                                                                 |                                                     | I <sub>CC2</sub>  |     | 1.24  | 1.67  | mA   |

|                                      | All channels switching with square wave clock                                                 | 1Mbps                                               | I <sub>CC1</sub>  |     | 1.31  | 1.77  |      |

|                                      | inputs; C <sub>L</sub> = 0pF                                                                  | Пипре                                               | I <sub>CC2</sub>  |     | 1.31  | 1.77  |      |

|                                      |                                                                                               | 10Mbps                                              | I <sub>CC1</sub>  |     | 2.03  | 2.7   |      |

|                                      |                                                                                               | Tolvibps                                            | I <sub>CC2</sub>  |     | 2.03  | 2.7   |      |

| Supply current -<br>ACTIVE - AC      |                                                                                               | 20Mbps                                              | I <sub>CC1</sub>  |     | 2.75  | 3.64  |      |

| signal (2)                           | A, B, E, and F channels switching with square wave clock input; C and D channels switching at |                                                     | I <sub>CC2</sub>  |     | 2.75  | 3.64  |      |

|                                      | 4Mbps; C <sub>L</sub> = 0pF                                                                   | 25Mbps                                              | I <sub>CC1</sub>  |     | 3.06  | 4.06  |      |

|                                      |                                                                                               | ZOMOPS                                              | I <sub>CC2</sub>  |     | 3.06  | 4.06  |      |

|                                      |                                                                                               | 50Mbps                                              | I <sub>CC1</sub>  |     | 4.73  | 6.3   |      |

|                                      |                                                                                               | Sqalviuc                                            | I <sub>CC2</sub>  |     | 4.73  | 6.3   |      |

- (1) Supply current valid for both INC and IND HIGH for STANDBY state.

- (2) Supply current valid for at least one of INC or IND LOW for ACTIVE state.

## 5.13 Electrical Characteristics—2.5V Supply (Minimum)

$V_{CC1} = V_{CC2} = 2.5V$  min (over recommended operating conditions unless otherwise noted)

|                      | PARAMETER                          | TEST CONDITIONS                                                    | MIN                                   | TYP | MAX                                   | UNIT  |

|----------------------|------------------------------------|--------------------------------------------------------------------|---------------------------------------|-----|---------------------------------------|-------|

| V <sub>OH</sub>      | High-level output voltage          | I <sub>OH</sub> = -4mA; See 図 6-1                                  | V <sub>CCO</sub> - 0.4 <sup>(1)</sup> |     |                                       | V     |

| V <sub>OL</sub>      | Low-level output voltage           | I <sub>OL</sub> = 4mA; See 図 6-1                                   |                                       |     | 0.4                                   | V     |

| V <sub>IT+(IN)</sub> | Rising input threshold             |                                                                    |                                       |     | 0.7 x V <sub>CCI</sub> <sup>(1)</sup> | V     |

| V <sub>IT-(IN)</sub> | Falling input threshold            |                                                                    | 0.3 x V <sub>CCI</sub>                |     |                                       | V     |

| V <sub>I(HYS)</sub>  | Input threshold voltage hysteresis |                                                                    | 0.04 x V <sub>CCI</sub>               |     |                                       | V     |

| I <sub>IH</sub>      | High-level input current           | V <sub>IH</sub> = V <sub>CCI</sub> <sup>(1)</sup> at INx           |                                       |     | 10                                    | μΑ    |

| I <sub>IL</sub>      | Low-level input current            | V <sub>IL</sub> = 0V at INx                                        | -10                                   |     |                                       | μA    |

| I <sub>O_LP</sub>    | Low-Power mode output current      |                                                                    |                                       | 2.2 |                                       | nA    |

| СМТІ                 | Common mode transient immunity     | $V_I = V_{CC}$ or 0V, $V_{CM} = 1200V$ ;<br>See $\boxtimes$ 6-4    | 25                                    | 50  |                                       | kV/μs |

| Ci                   | Input Capacitance (2)              | $V_I = V_{CC} + 0.4 \times \sin(2\pi ft), f = 2MHz, V_{CC} = 2.5V$ |                                       | 1.7 |                                       | pF    |

- (1)  $V_{CCI} = Input\text{-side } V_{CC}; V_{CCO} = Output\text{-side } V_{CC}$

- (2) Measured from input pin to same side ground.

## 5.14 Supply Current Characteristics—2.5V Supply (Minimum)

$V_{CC1} = V_{CC2} = 2.5V$  min (over recommended operating conditions unless otherwise noted)

| PARAMETER                        | TEST CONDITIONS                                                                               |                | SUPPLY<br>CURRENT | MIN TYP | MAX   | UNIT |

|----------------------------------|-----------------------------------------------------------------------------------------------|----------------|-------------------|---------|-------|------|

|                                  | Device in STANDBY state. V <sub>I</sub> = VCC <sub>I</sub> on                                 | -40°C to 125°C |                   | 0.35    | 0.448 |      |

|                                  | channels C and D (default level). $V_l = VCC_l$ on channels A, B, E, F (default level).       | –40°C to 85°C  |                   | 0.35    | 0.432 |      |

|                                  | Device in STANDBY state. $V_1 = VCC_1$ on                                                     | –40°C to 125°C | I <sub>CC1</sub>  | 0.356   | 0.455 |      |

| Supply current -<br>STANBDY (Low | channels C and D (default level). $V_I$ = 0V on channels A, B, E, F.                          | -40°C to 85°C  |                   | 0.356   | 0.438 |      |

| Power) (1)                       | Device in STANDBY state. V <sub>I</sub> = VCC <sub>I</sub> on                                 | –40°C to 125°C |                   | 0.35    | 0.448 |      |

|                                  | channels C and D (default level). $V_l = VCC_l$ on channels A, B, E, F (default level).       | –40°C to 85°C  | ]. [              | 0.35    | 0.432 |      |

|                                  | Device in STANDBY state. V <sub>I</sub> = VCC <sub>I</sub> on                                 | -40°C to 125°C | I <sub>CC2</sub>  | 0.356   | 0.455 |      |

|                                  | channels C and D (default level). $V_I$ = 0V on channels A, B, E, F.                          | -40°C to 85°C  |                   | 0.356   | 0.438 |      |

| Supply current -                 | Supply current - ACTIVE - DC signal $^{(2)}$ $V_I = V_{CC1}$ or $V_I = 0V$                    |                | I <sub>CC1</sub>  | 1.23    | 1.65  |      |

|                                  |                                                                                               |                | I <sub>CC2</sub>  | 1.23    | 1.65  | mA   |

|                                  | All channels switching with square wave clock                                                 | 1Mbps          | I <sub>CC1</sub>  | 1.29    | 1.73  |      |

|                                  | inputs; C <sub>L</sub> = 0pF                                                                  | Пиврз          | I <sub>CC2</sub>  | 1.29    | 1.73  |      |

|                                  |                                                                                               | 10Mbps         | I <sub>CC1</sub>  | 1.9     | 2.5   |      |

|                                  |                                                                                               | Томврз         | I <sub>CC2</sub>  | 1.9     | 2.5   |      |

| Supply current -<br>ACTIVE - AC  |                                                                                               | 20Mbps         | I <sub>CC1</sub>  | 2.53    | 3.28  |      |

| signal (2)                       | A, B, E, and F channels switching with square wave clock input; C and D channels switching at |                | I <sub>CC2</sub>  | 2.53    | 3.28  |      |

|                                  | 4Mbps; C <sub>L</sub> = 0pF                                                                   | 25Mbps         | I <sub>CC1</sub>  | 2.79    | 3.62  |      |

|                                  |                                                                                               | ZOMDPS         | I <sub>CC2</sub>  | 2.79    | 3.62  |      |

|                                  |                                                                                               | 50Mbps         | I <sub>CC1</sub>  | 4.22    | 5.46  |      |

|                                  |                                                                                               | ООМБРЗ         | I <sub>CC2</sub>  | 4.22    | 5.46  |      |

- (1) Supply current valid for both INC and IND HIGH for STANDBY state.

- (2) Supply current valid for at least one of INC or IND LOW for ACTIVE state.

資料に関するフィードバック (ご意見やお問い合わせ) を送信

Copyright © 2024 Texas Instruments Incorporated

10

## 5.15 Switching Characteristics—5V Supply (±10%)

$V_{CC1} = V_{CC2} = 5V \pm 10\%$  (over recommended operating conditions unless otherwise noted)

| PARAMETER                           |                                                                            | TEST CONDITIONS                                                                                                                    | MIN | TYP  | MAX  | UNIT |

|-------------------------------------|----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----|------|------|------|

| t <sub>PLH</sub> , t <sub>PHL</sub> | Propagation delay time                                                     |                                                                                                                                    |     | 9    | 12   | ns   |

| PWD                                 | Pulse width distortion <sup>(1)</sup>  t <sub>PHL</sub> - t <sub>PLH</sub> | Channels A, B, E, and F. See 図 6-1                                                                                                 |     |      | 1    | ns   |

| t <sub>PLH</sub> , t <sub>PHL</sub> | Propagation delay time                                                     | 0 10 10 0                                                                                                                          |     | 9    | 12   | ns   |

| PWD                                 | Pulse width distortion <sup>(1)</sup>  t <sub>PHL</sub> - t <sub>PLH</sub> | Channels C and D. See 図 6-1                                                                                                        |     |      | 1    | ns   |

| t <sub>sk(o)</sub>                  | Channel-to-channel output skew time <sup>(2)</sup>                         | Channels A and B or E and F (consecutive channels in active mode)                                                                  |     |      | 1    | ns   |

| t <sub>sk(pp)</sub>                 | Part-to-part skew time <sup>(3)</sup>                                      |                                                                                                                                    |     |      | 3    | ns   |

| t <sub>r</sub>                      | Output signal rise time                                                    | 0 70 04                                                                                                                            |     | 2.0  | 3.5  | ns   |

| t <sub>f</sub>                      | Output signal fall time                                                    | See 図 6-1                                                                                                                          |     | 2.0  | 3.5  | ns   |

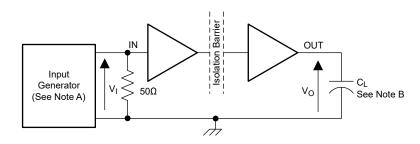

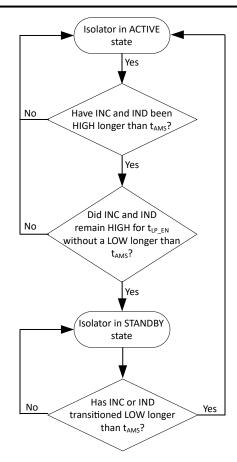

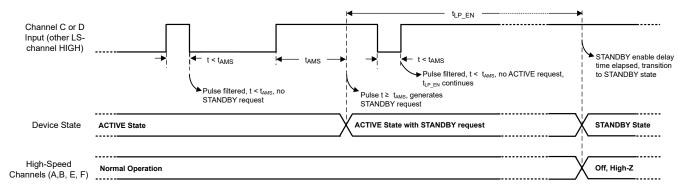

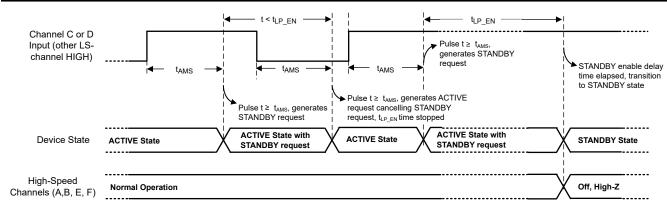

| t <sub>LP_EN</sub>                  | STANDBY State (low power) enable delay time                                | Time required transition to STANDBY state once channels C and D are in the inactive and HIGH states. See ☑ 6-2                     | 700 | 1000 | 1400 | ms   |

| t <sub>AMS</sub>                    | ACTIVE sample time (portion of $t_{LP\_{EN}}$ ), either C or D going LOW   | ACTIVE sample deglitch time for STANDBY state enable delay time. See 🗵 6-2                                                         | 10  |      | 28   | μs   |

| t <sub>LPN</sub>                    | STANDBY to ACTIVE (Low power to normal) transition time                    |                                                                                                                                    | 20  |      | 52   | μs   |

| t <sub>PU_HS_CH</sub>               | Time from UVLO to valid output data on channels A, B, E, and F             |                                                                                                                                    |     |      | 120  | μs   |

| t <sub>PU_LS_CH</sub>               | Time from UVLO to valid output data on channels C and D                    |                                                                                                                                    |     |      | 100  | μs   |

| t <sub>DO</sub>                     | Default output delay time from input power loss                            | Measured from the time $V_{CC}$ goes below 2.2V if the remaining device signals require normal mode operation. See $\boxtimes$ 6-3 |     |      | 13.5 | μs   |

| TIE                                 | Time Interval Error                                                        | Channels A, B, E, and F. 2 <sup>16</sup> – 1 PRBS data at 50Mbps                                                                   |     | 0.08 | 2    | ns   |

|                                     |                                                                            | Channels C and D. 2 <sup>16</sup> – 1 PRBS data at 4Mbps                                                                           |     | 0.12 | 2    | ns   |

| t <sub>JIT(RJ)</sub>                | Random jitter                                                              |                                                                                                                                    |     |      | 1    | ns   |

- (1) Also known as pulse skew.

- (2) t<sub>sk(o)</sub> is the skew between outputs of a single device with all driving inputs connected together and the outputs switching in the same direction while driving identical loads.

- (3)  $t_{sk(pp)}$  is the magnitude of the difference in propagation delay times between any terminals of different devices switching in the same direction while operating at identical supply voltages, temperature, input signals and loads.

## 5.16 Switching Characteristics—3.3V Supply (±10%)

$V_{CC1} = V_{CC2} = 3.3V \pm 10\%$  (over recommended operating conditions unless otherwise noted)

| <u> </u>                            | PARAMETER                                                                  | TEST CONDITIONS                                                                                                                    | MIN | TYP  | MAX   | UNIT |

|-------------------------------------|----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----|------|-------|------|

| t <sub>PLH</sub> , t <sub>PHL</sub> | Propagation delay time                                                     | Channala A D E and E Cas M C 4                                                                                                     |     | 9.6  | 13.75 | ns   |

| PWD                                 | Pulse width distortion <sup>(1)</sup>  t <sub>PHL</sub> - t <sub>PLH</sub> | Channels A, B, E, and F. See ⊠ 6-1                                                                                                 |     |      | 1     | ns   |

| t <sub>PLH</sub> , t <sub>PHL</sub> | Propagation delay time                                                     | Channala Cand D. Caa 🖼 C. 4                                                                                                        |     | 9.6  | 13.75 | ns   |

| PWD                                 | Pulse width distortion <sup>(1)</sup>  t <sub>PHL</sub> - t <sub>PLH</sub> | Channels C and D. See 図 6-1                                                                                                        |     |      | 1     | ns   |

| t <sub>sk(o)</sub>                  | Channel-to-channel output skew time <sup>(2)</sup>                         | Channels A and B or E and F (consecutive channels in active mode)                                                                  |     |      | 1     | ns   |

| t <sub>sk(pp)</sub>                 | Part-to-part skew time <sup>(3)</sup>                                      |                                                                                                                                    |     |      | 5     | ns   |

| t <sub>r</sub>                      | Output signal rise time                                                    | 0 50 0.4                                                                                                                           |     | 2.1  | 3.5   | ns   |

| t <sub>f</sub>                      | Output signal fall time                                                    | - See 図 6-1                                                                                                                        |     | 2.1  | 3.5   | ns   |

| t <sub>LP_EN</sub>                  | STANDBY State (low power) enable delay time                                | Time required transition to STANDBY state once channels C and D are in the inactive and HIGH states. See ☑ 6-2                     | 700 | 1000 | 1400  | ms   |

| t <sub>AMS</sub>                    | ACTIVE sample time (portion of $t_{LP\_EN}$ ), either C or D going LOW     | ACTIVE sample deglitch time for STANDBY state enable delay time. See 🗵 6-2                                                         | 10  |      | 28    | μs   |

| t <sub>LPN</sub>                    | STANDBY to ACTIVE (Low power to normal) transition time                    |                                                                                                                                    | 20  |      | 52    | μs   |

| t <sub>PU_HS_CH</sub>               | Time from UVLO to valid output data on channels A, B, E, and F             |                                                                                                                                    |     |      | 120   | μs   |

| t <sub>PU_LS_CH</sub>               | Time from UVLO to valid output data on channels C and D                    |                                                                                                                                    |     |      | 100   | μs   |

| t <sub>DO</sub>                     | Default output delay time from input power loss                            | Measured from the time $V_{CC}$ goes below 2.2V if the remaining device signals require normal mode operation. See $\boxtimes$ 6-3 |     |      | 13.5  | μs   |

|                                     | Time Interval Error                                                        | Channels A, B, E, and F. 2 <sup>16</sup> – 1 PRBS data at 50Mbps                                                                   |     | 0.06 | 2     | ns   |

|                                     |                                                                            | Channels C and D. 2 <sup>16</sup> – 1 PRBS data at 4Mbps                                                                           |     | 0.12 | 2     | ns   |

| t <sub>JIT(RJ)</sub>                | Random jitter                                                              |                                                                                                                                    |     |      | 1     | ns   |

- (1) Also known as pulse skew.

- (2) t<sub>sk(o)</sub> is the skew between outputs of a single device with all driving inputs connected together and the outputs switching in the same direction while driving identical loads.

- (3) t<sub>sk(pp)</sub> is the magnitude of the difference in propagation delay times between any terminals of different devices switching in the same direction while operating at identical supply voltages, temperature, input signals and loads.

資料に関するフィードバック(ご意見やお問い合わせ)を送信

## 5.17 Switching Characteristics—2.5V Supply (Minimum)

$V_{CC1} = V_{CC2} = 2.5V$  min (over recommended operating conditions unless otherwise noted)

| PARAMETER                           |                                                                            | TEST CONDITIONS                                                                                                                 | MIN | TYP  | TYP MAX | UNIT |

|-------------------------------------|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-----|------|---------|------|

| t <sub>PLH</sub> , t <sub>PHL</sub> | Propagation delay time                                                     |                                                                                                                                 |     | 11   | 17      | ns   |

| PWD                                 | Pulse width distortion <sup>(1)</sup>  t <sub>PHL</sub> - t <sub>PLH</sub> | - Channels A, B, E, and F. See 図 6-1                                                                                            |     |      | 1.2     | ns   |

| t <sub>PLH</sub> , t <sub>PHL</sub> | Propagation delay time                                                     | 01 10 10 0 11 04                                                                                                                |     | 11   | 17      | ns   |

| PWD                                 | Pulse width distortion <sup>(1)</sup>  t <sub>PHL</sub> - t <sub>PLH</sub> | - Channels C and D. See 図 6-1                                                                                                   |     |      | 1.2     | ns   |

| t <sub>sk(o)</sub>                  | Channel-to-channel output skew time <sup>(2)</sup>                         | Channels A and B or E and F (consecutive channels in active mode)                                                               |     |      | 1       | ns   |

| t <sub>sk(pp)</sub>                 | Part-to-part skew time <sup>(3)</sup>                                      |                                                                                                                                 |     |      | 5       | ns   |

| t <sub>r</sub>                      | Output signal rise time                                                    | 0 50 0.4                                                                                                                        |     | 2.2  | 4.1     | ns   |

| t <sub>f</sub>                      | Output signal fall time                                                    | - See 図 6-1                                                                                                                     |     | 2.2  | 4.1     | ns   |

| t <sub>LP_EN</sub>                  | STANDBY State (low power) enable delay time                                | Time required transition to STANDBY state once channels C and D are in the inactive and HIGH states. See ☑ 6-2                  | 700 | 1000 | 1400    | ms   |

| t <sub>AMS</sub>                    | ACTIVE sample time (portion of $t_{LP\_{EN}}$ ), either C or D going LOW   | ACTIVE sample deglitch time for STANDBY state enable delay time. See 🗵 6-2                                                      | 10  |      | 28      | μs   |

| t <sub>LPN</sub>                    | STANDBY to ACTIVE (Low power to normal) transition time                    |                                                                                                                                 | 20  |      | 52      | μs   |

| t <sub>PU_HS_CH</sub>               | Time from UVLO to valid output data on channels A, B, E, and F             |                                                                                                                                 |     |      | 120     | μs   |

| t <sub>PU_LS_CH</sub>               | Time from UVLO to valid output data on channels C and D                    |                                                                                                                                 |     |      | 100     | μs   |

| t <sub>DO</sub>                     | Default output delay time from input power loss                            | Measured from the time V <sub>CC</sub> goes below 2.2V if the remaining device signals require normal mode operation. See ☑ 6-3 |     |      | 13.5    | μs   |

| TIE                                 | Time Interval Error                                                        | Channels A, B, E, and F. 2 <sup>16</sup> – 1 PRBS data at 50Mbps                                                                |     | 0.06 | 2       | ns   |

| C   C                               |                                                                            | Channels C and D. 2 <sup>16</sup> – 1 PRBS data at 4Mbps                                                                        |     | 0.13 | 2       | ns   |

| t <sub>JIT(RJ)</sub>                | Random jitter                                                              |                                                                                                                                 |     |      | 1       | ns   |

<sup>(1)</sup> Also known as pulse skew.

<sup>(2)</sup> t<sub>sk(o)</sub> is the skew between outputs of a single device with all driving inputs connected together and the outputs switching in the same direction while driving identical loads.

<sup>(3)</sup> t<sub>sk(pp)</sub> is the magnitude of the difference in propagation delay times between any terminals of different devices switching in the same direction while operating at identical supply voltages, temperature, input signals and loads.

## 5.18 Insulation Characteristics Curves

図 5-1. Thermal Derating Curve for Safety Limiting Current (mA) for DW-16 Package

図 5-2. Thermal Derating Curve for Safety Limiting Power (mW) for DW-16 Package

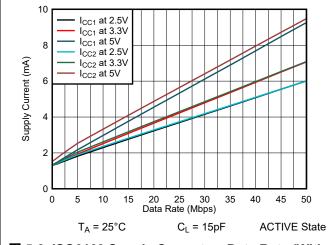

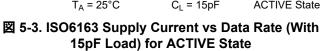

## **5.19 Typical Characteristics**

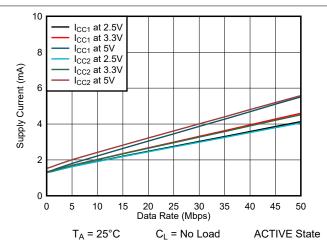

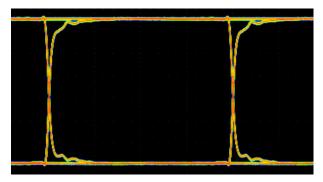

## 5.19.1 Typical Characteristics: Supply Current ACTIVE state

ACTIVE state is forced with one low-speed control channel held LOW, the high-speed data and second low-speed control channel data rate is swept per the chart. Once the data-rate reaches 4Mbps, the second low-speed control channel data rate is held at 4Mbps as the high-speed data channels continue to rise until 50Mbps.

図 5-4. ISO6163 Supply Current vs Data Rate (With 15pF Load) for ACTIVE State

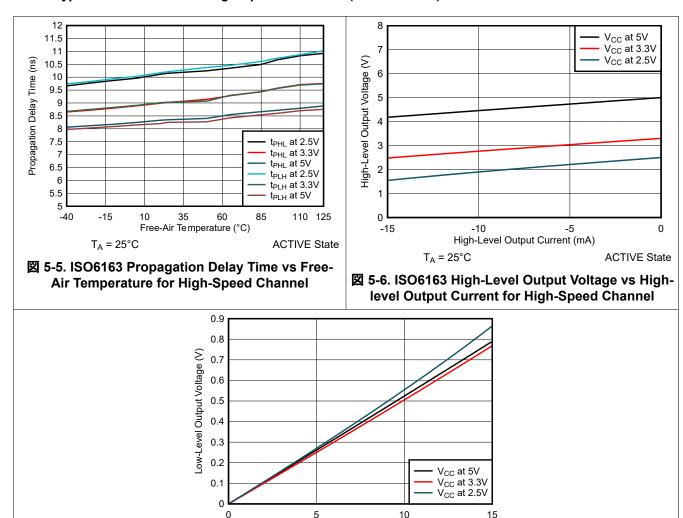

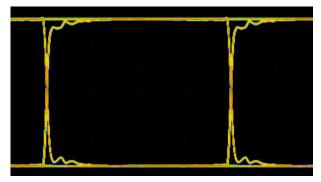

## 5.19.2 Typical Characteristics: High-Speed Channels (ACTIVE state)

$T_A = 25^{\circ}C$

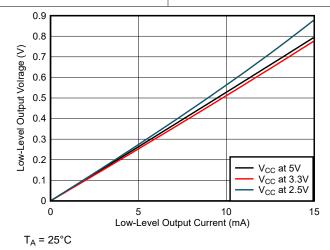

図 5-7. ISO6163 Low-Level Output Voltage vs Low-Level Output Current for High-Speed Channel

Low-Level Output Current (mA)

**ACTIVE State**

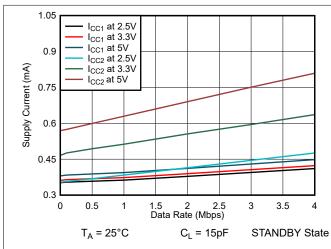

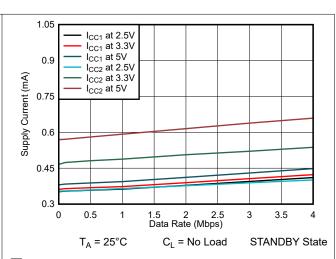

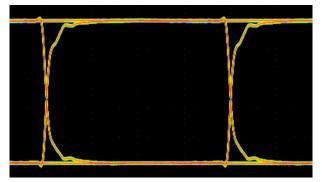

## 5.19.3 Typical Characteristics: Supply Current STANDBY State

STANDBY state is held with one low-speed control channel held HIGH while second channel is swept. The data rates swept are selected to avoid LOW durations longer than t<sub>AMS</sub> which transition the device to ACTIVE state.

注

The high-speed channels are turned off (high impedance) in the device STANDBY state.

注

For  $I_{CC1}$  and  $I_{CC2}$  at with DC signals on the low-speed control channels, please refer to the Supply Characteristics table for the supply voltage,  $V_{CC1}$  and  $V_{CC2}$ , supplied to each side of the isolator.

図 5-8. ISO6163 Supply Current vs Data Rate (With 15pF Load) for Low-Speed Channel in STANDBY state

図 5-9. ISO6163 Supply Current vs Data Rate (With No Load) for Low-Speed Channel in STANDBY state

## 5.19.4 Typical Characteristics: Low-Speed Control Channels (ACTIVE and STANDBY States)

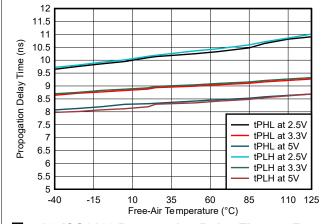

図 5-10. ISO6163 Propagation Delay Time vs Free-Air Temperature for Low-Speed Control Channel

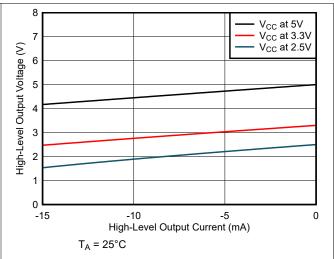

図 5-11. ISO6163 High-Level Output Voltage vs High-level Output Current for Low-Speed Control Channel

図 5-12. ISO6163 Low-Level Output Voltage vs Low-Level Output Current for Low-Speed Control Channel

資料に関するフィードバック(ご意見やお問い合わせ) を送信

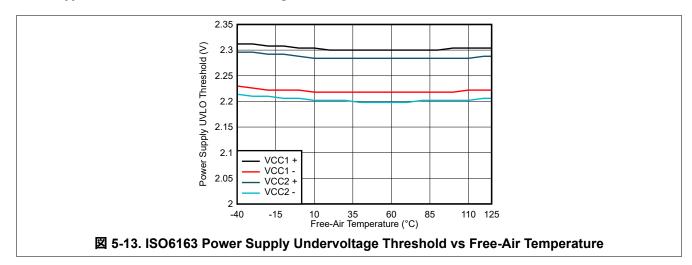

## 5.19.5 Typical Characteristics: Undervoltage Threshold

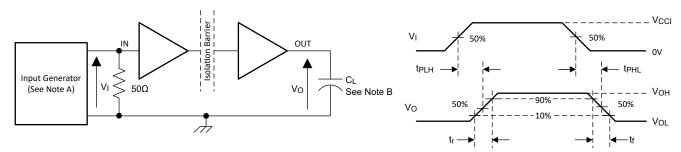

#### **6 Parameter Measurement Information**

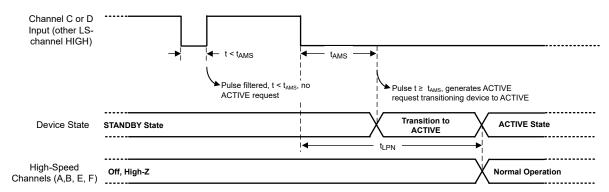

- A. The input pulse is supplied by a generator having the following characteristics: PRR  $\leq$  50kHz, 50% duty cycle,  $t_r \leq$  3ns,  $t_f \leq$  3ns,  $Z_O = 50\Omega$ . At the input,  $50\Omega$  resistor is required to terminate Input Generator signal. The  $50\Omega$  resistor is not needed in the actual application.

- B.  $C_L = 15$ pF and includes instrumentation and fixture capacitance within ±20%.

## 図 6-1. Switching Characteristics Test Circuit and Voltage Waveforms

- A. The input pulse is supplied by a generator having the following characteristics:  $t_f \le 3$ ns,  $t_f \le 3$ ns

- B.  $C_L = 15 pF$  and includes instrumentation and fixture capacitance within  $\pm 20\%$ .

- C. Low-Speed Control Channel not under test has a HIGH input.

#### 図 6-2. Low-Speed Control Channel Automatic Enable Time Test Circuit and Waveform

資料に関するフィードバック(ご意見やお問い合わせ)を送信

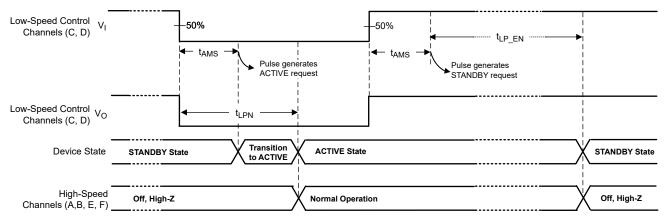

- A. C<sub>L</sub> = 15pF and includes instrumentation and fixture capacitance within ±20%.

- B. Power Supply Ramp Rate = 10mV/ns

## 図 6-3. Default Output Delay Time Test Circuit and Voltage Waveforms

A. C<sub>L</sub> = 15pF and includes instrumentation and fixture capacitance within ±20%.

図 6-4. Common-Mode Transient Immunity Test Circuit

## 7 Detailed Description

#### 7.1 Overview

The ISO6163 family of devices transmit digital data across a silicon dioxide based isolation barrier.