# LM20146

LM20146 6A, Adjustable Frequency Synchronous Buck Regulator

Literature Number: JAJSAY4

National Semiconductor

# LM20146

2009年2月

# 6A、 可変周波数同期整流降圧型レギュレータ

#### 概要

LM20146 は、最大 6A の連続出力電流を供給できる、必要な機能がすべて揃った周波数可変の同期整流降圧型レギュレータです。電流モード制御ループは、実質的にどのタイプの出力コンデンサでも安定するように補償できます。 大半の場合デバイスの補償は2つの外付け部品を必要とするだけで、最大の柔軟性と使いやすさを実現します。 デバイスは 2.95V ~ 5.5Vの入力電圧範囲で動作するように最適化され、低電圧システムに適しています。

デバイスは、オーバーボルテージ保護 (OVP) および過電流保護 (OCP) 回路を内蔵し、システムの信頼性を高めています。デバイスの起動は、高精度イネーブル・ピンおよび内蔵されたアンダーボルテージ・ロックアウトにより、正確なシーケンス制御を実現できます。スタートアップ時の突入電流は、内部固定および外部で調整可能なソフトスタート回路の両方で制限されます。内蔵パワーグッド回路により、異常検出や電源シーケンスが可能です。

LM20146 は、マルチレール電源アーキテクチャで最適に稼動するように設計されています。デバイスの出力電圧は、SS/TRKピンを使ってより高い電圧レールをトラッキングするように設定できます。LM20146 の出力がスタートアップ時にプリバイアスされた場合、出力を低下させません。

このデバイスの周波数は、RT ピンとグラウンドの間に外部抵抗を接続することにより、 $250 \mathrm{kHz} \sim 750 \mathrm{kHz}$  の範囲で調節可能です。

LM20146 は露出パッド付き 16 ピン eTSSOP パッケージで提供されるため、PCB にハンダ付けができ、大きなヒートシンクの必要がありません。

#### 特長

- 入力電圧範囲: 2.95V ~ 5.5V

- 高精度の電流制限によりインダクタのサイズを最小化

- ピーク効率:97%

- スイッチング周波数の調節可能範囲: 250kHz~750kHz

- 16mΩ と 20mΩ の内蔵 FET スイッチ

- 出力プリバイアス・スタートアップ

- 出力電圧トラッキング

- ピーク電流モード制御

- 出力電圧は最低 0.8V まで対応

- 外付けコンデンサによりソフトスタートを調整可能

- ヒステリシス付き高精度イネーブル・ピン

- オーバーボルテージ保護、アンダーボルテージ・ロックアウト、パワーグッドおよびサーマル・シャットダウン回路内蔵

- eTSSOP-16 露出パッド・パッケージ

## アプリケーション

- 回路設計がシンプルで、効率の高い 5V または 3.3V バスからのポイント・オブ・ロード・レギュレーション

- 高性能 DSP、FPGA、ASIC およびマイクロプロセッサ

- 広帯域、ネットワークおよび光通信のインフラ

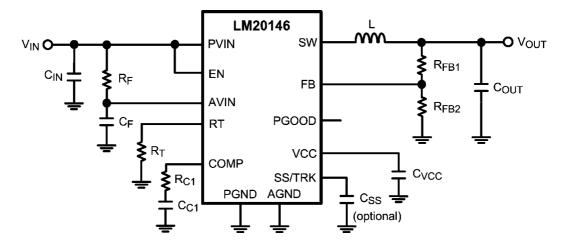

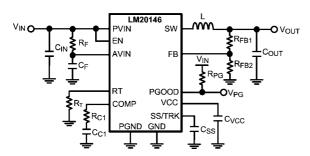

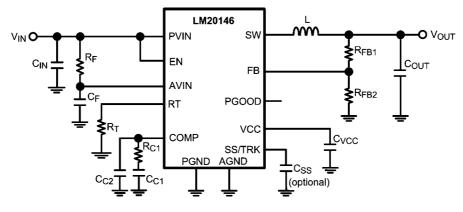

## 代表的なアプリケーション回路

PowerWise® はナショナル セミコンダクターの登録商標です。

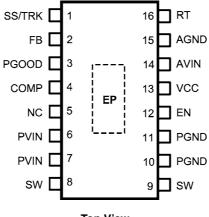

# ピン配置図

Top View eTSSOP-16 Package

# 製品情報

| Order Number | Package Type | NSC Package Drawing | Package Marking | Supplied As                 |

|--------------|--------------|---------------------|-----------------|-----------------------------|

| LM20146MH    | eTSSOP-16    | MXA16A              | 20146MH         | 92 Units of Rail            |

| LM20146MHE   |              |                     |                 | 250 Units of Tape and Reel  |

| LM20146MHX   |              |                     |                 | 2500 Units of Tape and Reel |

# ピン説明

| ピン番号  | ピン名    | 説明                                                                                                                                                                                                    |

|-------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | SS/TRK | ソフトスタートまたはトラッキング制御入力。 $5 \mu$ A の内部電流源により、ソフトスタート上昇速度を設定する外付けコンデンサを充電します。 このピンが $800 \text{mV}$ 未満の外部ソースによってドライブされると、出力電圧を設定する内部リファレンスがディスエーブルされます。 オープン状態の場合、内部の $1 \text{ms}$ ソフトスタート上昇がアクティブとなります。 |

| 2     | FB     | レギュレート出力からエラー・アンプへの電圧帰還入力。 内部トランスコンダクタンス・エラー・アンプの反転入力に接続されています。 800mV リファレンスがエラー・アンプの非反転入力に接続されると、 FB ピンの閉ループ・レギュレーション電圧が設定されます。                                                                      |

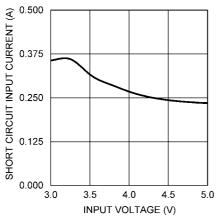

| 3     | PGOOD  | パワーグッド出力信号。 出力電圧を示すオープン・ドレインの出力は許容誤差内でレギュレートしています。 そのため大半のアプリケーションでは $10 \mathrm{k}\Omega\sim 100 \mathrm{k}\Omega$ のプルアップ抵抗を推奨します。                                                                   |

| 4     | COMP   | 外部補償ピン。このピンに抵抗とコンデンサを接続して、デバイスを補償します。                                                                                                                                                                 |

| 5     | NC     | 正常に動作させるには、このピンを GND に接続します。                                                                                                                                                                          |

| 6,7   | PVIN   | デバイス内部の電源スイッチへの入力電圧。 これらのピンはデバイス部分で 1 つに接続してください。 入力電圧を安定させるため、 低 ESR コンデンサはこれらのピンの近くに配置してください。                                                                                                       |

| 8,9   | SW     | スイッチング・ピン。 内蔵パワー・スイッチの PWM 出力。                                                                                                                                                                        |

| 10,11 | PGND   | 内蔵パワー・スイッチ用の電源グラウンド・ピン。                                                                                                                                                                               |

| 12    | EN     | デバイス用の高精度イネーブル入力。 外付けの分圧回路を使うと、 電源のターンオン・スレッショルドの設定が可能です。 EN ピンを使用しない場合は、 PVIN に接続してください。                                                                                                             |

| 13    | VCC    | 2.7V サブ・レギュレータ内蔵。 このピンは、 1 μ F セラミック・コンデンサでバイパスしてください。                                                                                                                                                |

| 14    | AVIN   | 内部バイアスを発生するアナログ入力電源ピン。 ローパス RC フィルタを使って PVIN に接続する必要があります。                                                                                                                                            |

| 15    | AGND   | 内部バイアス回路用のノイズの少ないアナログ・グラウンドです。                                                                                                                                                                        |

| 16    | RT     | 周波数調節用ピン。このピンとグラウンド間に抵抗を接続し、内蔵発振回路の周波数を設定します。                                                                                                                                                         |

| EP    | 露出パッド  | グラウンドへの電気的接続が弱い、 パッケージ裏面の露出金属パッド。 熱放散特性を向上させるために、このパッドをプリント基板のグラウンド・プレーンに接続することを推奨します。                                                                                                                |

2.6W

260 ℃

$\pm 2kV$

## 絶対最大定格 (Note 1)

本データシートには軍用・航空宇宙用の規格は記載されていません。 関連する電気的信頼性試験方法の規格を参照ください。

特に指定のない限り、表記の各ピンとGND間の電圧

AVIN, PVIN, EN, PGOOD, SS/  $-0.3V \sim + 6V$

TRK, COMP, FB, RT

保存温度範囲 - 65 ℃~+ 150 ℃

接合部温度 150℃

# 動作定格

消費電力 (Note 2)

最小 ESD 定格 (Note 3)

リード温度(ハンダ付け、10秒間)

GND 基準の PVIN、 AVIN 各電圧 2.95V ~+ 5.5V

接合部温度 - 40 ℃~+ 125 ℃

# 電気的特性

特記のない限り、以下の条件が適用されます。 AVIN = PVIN = VIN = 5V。 標準字体で記載されたリミット値は  $T_J=25\,$   $\mathbb C$  の場合に限ります。太字で記載されたリミット値は  $-40\,$   $\mathbb C$   $\sim+125\,$   $\mathbb C$  の接合部温度  $(T_J)$  範囲にわたって適用されます。最小リミット (Min) 値と最大リミット (Max) 値は、試験、設計、または統計的相関によって保証されます。 代表  $(T_J)$  値は  $T_J=25\,$   $\mathbb C$  でのパラメータ の最も標準と考えられる値を表し、参照を目的としてのみ提示されます。

| Symbol                          | Parameter                                          | Conditions                                         | Min   | Тур  | Max   | Unit |

|---------------------------------|----------------------------------------------------|----------------------------------------------------|-------|------|-------|------|

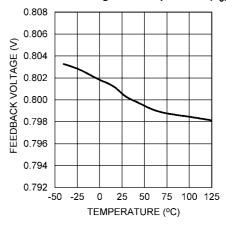

| V <sub>FB</sub>                 | Feedback pin voltage                               | V <sub>IN</sub> = 2.95V to 5.5V                    | 0.788 | 0.8  | 0.812 | V    |

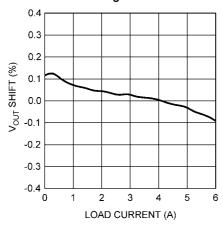

| $\Delta V_{OUT}/\Delta I_{OUT}$ | Load Regulation                                    | I <sub>OUT</sub> = 100 mA to 6A                    |       | 0.08 |       | %/A  |

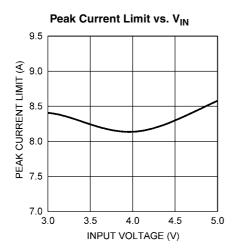

| I <sub>CL</sub>                 | Switch Current Limit Threshold                     | $V_{IN} = 3.3V$                                    | 7.35  | 8.5  | 9.35  | Α    |

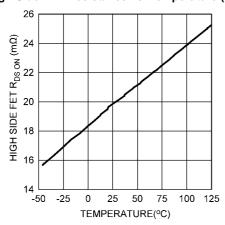

| R <sub>DS_ON</sub>              | High-Side Switch On Resistance                     | I <sub>SW</sub> = 3.5A                             |       | 20   | 27    | mΩ   |

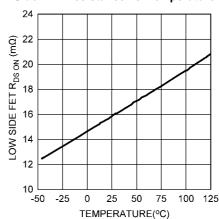

| R <sub>DS_ON</sub>              | Low-Side Switch On Resistance                      | I <sub>SW</sub> = 3.5A                             |       | 16   | 23    | mΩ   |

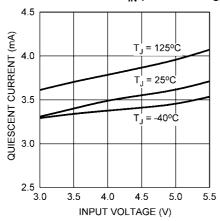

| I <sub>Q</sub>                  | Operating Quiescent Current                        | Non-switching, V <sub>FB</sub> = V <sub>COMP</sub> |       | 3.5  | 6     | mA   |

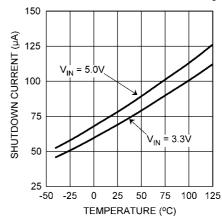

| I <sub>SD</sub>                 | Shutdown Quiescent current                         | V <sub>EN</sub> = 0V                               |       | 75   | 180   | μA   |

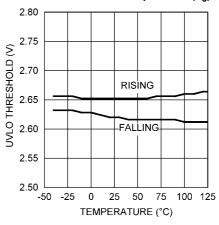

| V <sub>UVLO</sub>               | VIN Under Voltage Lockout                          | Rising V <sub>IN</sub>                             | 2.45  | 2.7  | 2.95  | V    |

| V <sub>UVLO_HYS</sub>           | VIN Under Voltage Lockout Hysteresis               | Falling V <sub>IN</sub>                            |       | 45   | 100   | mV   |

| V <sub>VCC</sub>                | VCC Voltage                                        | I <sub>VCC</sub> = 0 μA                            | 2.45  | 2.7  | 2.95  | V    |

| I <sub>SS</sub>                 | Soft-Start Pin Source Current                      | V <sub>SS/TRK</sub> = 0V                           | 2     | 4.5  | 7     | μA   |

| V <sub>TRACK</sub>              | SS/TRK Accuracy, V <sub>SS</sub> - V <sub>FB</sub> | V <sub>SS/TRK</sub> = 0.4V                         | -10   | 3    | 15    | mV   |

| Oscillator                      |                                                    | •                                                  | •     |      |       |      |

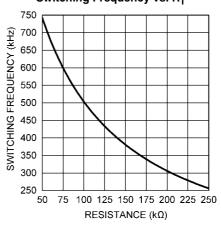

| F <sub>OSCH</sub>               | Oscillator Frequency                               | $R_T = 49.9 \text{ k}\Omega$                       | 675   | 750  | 825   | kHz  |

| F <sub>OSCL</sub>               | Oscillator Frequency                               | $R_T = 249 \text{ k}\Omega$                        | 225   | 260  | 290   | kHz  |

| DC <sub>MAX</sub>               | Maximum Duty Cycle                                 | I <sub>LOAD</sub> = 0A                             |       | 85   |       | %    |

| T <sub>ON_TIME</sub>            | Minimum On Time                                    |                                                    |       | 100  |       | ns   |

| T <sub>CL_BLANK</sub>           | Current Sense Blanking Time                        | After Rising V <sub>SW</sub>                       |       | 80   |       | ns   |

| Error Amplifier                 | and Modulator                                      |                                                    |       |      |       |      |

| I <sub>FB</sub>                 | Feedback pin bias current                          | V <sub>FB</sub> = 0.8V                             |       | 1    | 100   | nA   |

| I <sub>COMP_SRC</sub>           | COMP Output Source Current                         | $V_{FB} = 0.6V, V_{COMP} = 0.5V$                   | 80    | 100  |       | μA   |

| I <sub>COMP_SNK</sub>           | COMP Output Sink Current                           | $V_{FB} = 1.0V, V_{COMP} = 0.6V$                   | 80    | 100  |       | μΑ   |

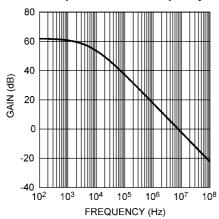

| Gm                              | Error Amplifier Transconductance                   | I <sub>COMP</sub> = ± 50 μA                        | 450   | 510  | 600   | μmho |

| A <sub>VOL</sub>                | Error Amplifier Voltage Gain                       |                                                    |       | 2000 |       | V/V  |

| Power Good                      |                                                    | •                                                  | •     | •    |       |      |

| V <sub>OVP</sub>                | Over Voltage Protection Rising Threshold           | With respect to V <sub>FB</sub>                    | 105   | 108  | 111   | %    |

| V <sub>OVP_HYS</sub>            | Over Voltage Protection Hysteresis                 |                                                    |       | 2    | 3     | %    |

| V <sub>PGTH</sub>               | PGOOD Rising Threshold                             | With respect to V <sub>FB</sub>                    | 92    | 94   | 96    | %    |

| V <sub>PGHYS</sub>              | PGOOD Falling Hysteresis                           |                                                    |       | 2    | 3     | %    |

| T <sub>PGOOD</sub>              | PGOOD deglitch time                                |                                                    |       | 16   |       | μs   |

| l <sub>oL</sub>                 | PGOOD Low Sink Current                             | $V_{PGOOD} = 0.4V$                                 | 0.6   | 1    |       | mA   |

| I <sub>OH</sub>                 | PGOOD High Leakage Current                         | V <sub>PGOOD</sub> = 5V                            |       | 5    | 100   | nA   |

## 電気的特性(つづき)

特記のない限り、以下の条件が適用されます。 AVIN = PVIN = VIN = 5V。 標準字体で記載されたリミット値は  $T_J = 25$   $\mathbb C$  の場合に限ります。太字で記載されたリミット値は -40  $\mathbb C \sim +125$   $\mathbb C$  の接合部温度  $(T_J)$  範囲にわたって適用されます。最小リミット (Min) 値と最大リミット (Max) 値は、試験、設計、または統計的相関によって保証されます。 代表 (Typ) 値は  $T_J = 25$   $\mathbb C$  でのパラメータ の最も標準と考えられる値を表し、参照を目的としてのみ提示されます。

| Symbol               | Parameter                   | Conditions             | Min  | Тур  | Max  | Unit |

|----------------------|-----------------------------|------------------------|------|------|------|------|

| nable                |                             | •                      |      |      |      |      |

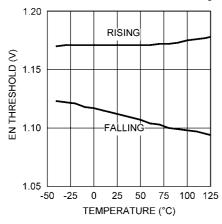

| V <sub>IH_EN</sub>   | EN Pin turn-on Threshold    | V <sub>EN</sub> Rising | 1.08 | 1.18 | 1.28 | ٧    |

| V <sub>EN_HY\$</sub> | EN Pin Hysteresis           |                        |      | 66   |      | mV   |

| Thermal Shutd        | lown                        | •                      | •    |      |      |      |

| T <sub>SD</sub>      | Thermal Shutdown            |                        |      | 160  |      | °C   |

| T <sub>SD_HYS</sub>  | Thermal Shutdown Hysteresis |                        |      | 10   |      | °C   |

| Thermal Resist       | tance                       |                        |      |      |      |      |

| $\theta_{JA}$        | Junction to Ambient         | (Note 2)               |      | 25   |      | °C/W |

Note 1: 「絶対最大定格」とは、デバイスに破壊を生じさせる可能性がある上限または下限値のことです。「動作定格」とはデバイスが機能する条件を示しますが、特定の性能リミット値を保証するものではありません。 保証されている仕様および試験条件については「電気的特性」を参照してください。

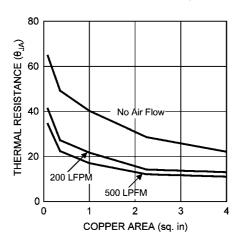

Note 2: 最大許容消費電力は、最大接合部温度 TJ\_MAX、接合部-周囲雰囲気間熱抵抗  $\theta$  JA、周囲温度 TA の関数です。任意の周囲温度での最大 許容消費電力は次式から求めます。PD\_MAX = (TJ\_MAX - TA)/ $\theta$  JA。 2.6W という最大消費電力の値は、TA = 25  $^{\circ}$  C、 $\theta$  JA = 25  $^{\circ}$  C、W TJ\_MAX = 125  $^{\circ}$  Cを代入して求めたものです。「電気的特性」の表に示す 25  $^{\circ}$  C/W の  $\theta$  JA の仕様は、2" × 2" FR4 の 4 層基板の表面実装部品で測定しています。  $\theta$  JA の詳細は、Figure 10 を参照してください。

Note 3: 人体モデルでは、100pF のコンデンサから  $1.5k\Omega$  の抵抗を介して各ピンへ放電させます。

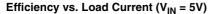

#### 代表的な性能特性

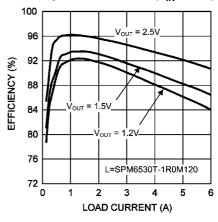

特記のない限り、効率曲線、ループ・ゲイン・プロットと波形の場合は  $C_{\rm IN}=C_{\rm OUT}=100\,\mu$  F、L =  $1.0\,\mu$  H (TDK SPM6530T-1R0M120)、 $V_{\rm IN}=5$ V、 $V_{\rm OUT}=1.2$ V、 $R_{\rm LOAD}=1.2\,\Omega$ 、 $f_{\rm SW}=500$ kHz、 $T_{\rm A}=25\,^{\circ}$ C、それ以外の場合は  $T_{\rm J}=25\,^{\circ}$ Cになります。

Efficiency vs. Load Current (V<sub>IN</sub> = 3.3V)

High-Side FET Resistance vs. Temperature (T<sub>,I</sub>)

Low-Side FET Resistance vs. Temperature (T,I)

特記のない限り、 効率曲線、 ループ・ゲイン・プロットと波形の場合は  $C_{\rm IN}=C_{\rm OUT}=100\,\mu$  F、  $L=1.0\,\mu$  H (TDK SPM6530T-1R0M120)、  $V_{\rm IN}=5$ V、 $V_{\rm OUT}=1.2$ V、 $R_{\rm LOAD}=1.2\Omega$ 、 $f_{\rm SW}=500$ kHz、 $T_{\rm A}=25\,$ °C、それ以外の場合は  $T_{\rm J}=25\,$ °Cになります。

**Error Amplifier Gain vs. Frequency**

#### **Load Regulation**

#### Feedback Pin Voltage vs. Temperature (T<sub>J</sub>)

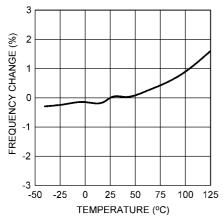

## Switching Frequency vs. Temperature (T<sub>J</sub>)

## Switching Frequency vs. R<sub>T</sub>

特記のない限り、 効率曲線、 ループ・ゲイン・プロットと波形の場合は  $C_{\rm IN}=C_{\rm OUT}=100\,\mu$  F、 L =  $1.0\,\mu$  H (TDK SPM6530T-1R0M120)、  $V_{\rm IN}=5$ V、 $V_{\rm OUT}=1.2$ V、 $R_{\rm LOAD}=1.2\,\Omega$ 、 $f_{\rm SW}=500$ kHz、 $T_{\rm A}=25\,^{\circ}$ C、それ以外の場合は  $T_{\rm J}=25\,^{\circ}$ Cになります。

## Quiescent Current vs. V<sub>IN</sub> (Not Switching)

## Shutdown Current vs. Temperature (T<sub>J</sub>)

#### Enable Threshold vs. Temperature (T<sub>J</sub>)

UVLO Threshold vs. Temperature (T<sub>.I</sub>)

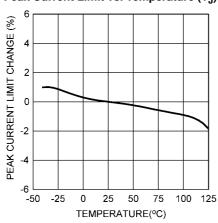

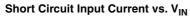

# Peak Current Limit vs. Temperature (T<sub>J</sub>)

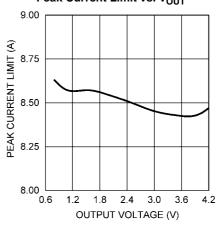

# Peak Current Limit vs. V<sub>OUT</sub>

特記のない限り、 効率曲線、 ループ・ゲイン・プロットと波形の場合は  $C_{\rm IN}=C_{\rm OUT}=100\,\mu$  F、 L =  $1.0\,\mu$  H (TDK SPM6530T-1R0M120)、  $V_{\rm IN}=5$ V、 $V_{\rm OUT}=1.2$ V、 $R_{\rm LOAD}=1.2\,\Omega$ 、 $f_{\rm SW}=500$ kHz、 $T_{\rm A}=25\,^{\circ}$ C、それ以外の場合は  $T_{\rm J}=25\,^{\circ}$ Cになります。

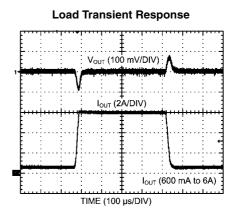

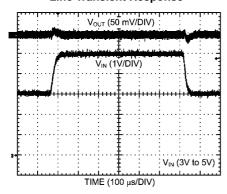

## **Line Transient Response**

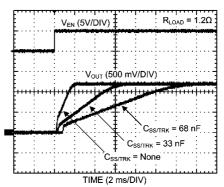

## Start-Up (Soft-Start)

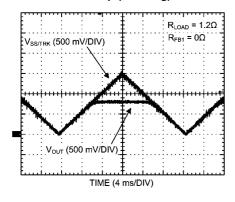

## Start-Up (Tracking)

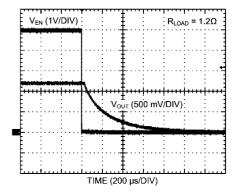

#### Power Down

特記のない限り、 効率曲線、 ループ・ゲイン・プロットと波形の場合は  $C_{\rm IN}=C_{\rm OUT}=100\,\mu$  F、  $L=1.0\,\mu$  H (TDK SPM6530T-1R0M120)、  $V_{\rm IN}=5$ V、 $V_{\rm OUT}=1.2$ V、 $R_{\rm LOAD}=1.2$  Q、 $f_{\rm SW}=500$ kHz、 $T_{\rm A}=25\,^{\circ}$ C、それ以外の場合は  $T_{\rm J}=25\,^{\circ}$ Cになります。

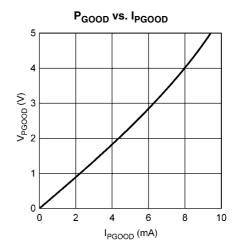

# ブロック図

#### 動作の説明

#### 概要

LM20146は、できる限り少ない外付け部品で効率的な低電圧 降圧レギュレータを実装するために必要なすべての機能を備え たスイッチング・レギュレータです。この使いやすいレギュレータは、2つのスイッチ素子を内蔵し、最大6Aの連続出力電流 を供給できます。レギュレータは非線形スロープ補償によるピー ク電流モード制御により、出力電圧範囲全体にわたり最適な安 定性および過渡応答を実現します。ピーク電流モード制御は、 入力電圧フィードフォワード、サイクルごとの電流制限、ループ 補償が簡単という特長を原理的に備えています。スイッチング 周波数は 250kHz ~ 750kHz の範囲で可変です。 デバイスは 高いスイッチング周波数で動作可能で、小型のインダクタを使 用しながら高い効率を達成します。高精度な内部電圧リファレ ンスにより、出力を 0.8V という低電圧に設定できます。保護機 能として、電流制限、サーマル・シャットダウン、オーバーボ ルテージ保護、シャットダウン機能を備えています。 デバイス は放熱を助ける露出パッドを組み込んだeTSSOP-16パッケージ で供給されます。5Vまたは3.3Vバスから効率的に降圧する目 的で、LM20146 は数多くのアプリケーションに適用可能です。 LM20146 の一般的なアプリケーション回路は設計ガイドライン の Figure 3 に示しています。

#### 高精度イネーブル

イネーブル (EN) ピンから、デバイスの出力を外部制御信号によりイネーブルまたはディスエーブルできます。このピンは、電圧が 1.18V (typ) を超えた場合にデバイスをイネーブルにできる高精度アナログ入力です。EN ピンには 66mV のヒステリシスがあり、イネーブル電圧が 1.11V (typ)を下回ると出力をディスエーブルします。EN ピンを使用しない場合は、 $V_{\rm IN}$  に接続してください。イネーブル・ピンには高精度なターンオン・スレッショルドがあるため、 $V_{\rm IN}$  からの外部抵抗分圧ネットワークと一緒に使用することにより、デバイスがターンオンする入力電圧を高精度に設定できます。高精度イネーブル回路は、デバイスがディスエーブルされてもアクティブのままです。

#### ピーク電流モード制御

多くの場合、LM20146で使用されているピーク電流モード制御アーキテクチャが安定した設計を実現するために必要とする外付け部品は2つだけです。補償を選択すると、どのような種類または値の出力コンデンサにも対応します。外部機器により、ユーザーはクロスオーバー周波数を設定でき、デバイスの過渡特性を最適化できます。

デューティ・サイクル 50% 以上では、低調波発振を避けるために、すべての電流モード制御降圧型コンバータではランプを追加する必要があります。この非線形ランプは、通常スロープ補償と呼ばれます。LM20146 の特長は、スロープ補償の量が出力電圧に応じて変化する点です。高出力電圧での動作時は、低出力電圧での動作時に比べスロープ補償量が大きくなります。これは、スロープ補償に非線形放物線ランプを使用することにより実現されます。LM20146 の放物線スロープ補償は、出力電圧範囲全体にわたってデバイスの安定性を最適化するため、従来の非線形スロープ補償より優れています。

#### 電流制限

LM20146の高精度な電流制限は、工場出荷時に動作温度範囲全体にわたって 10%以内に設定されています。このため、デバイスは飽和電流の低い小さなインダクタで動作できます。ピーク・インダクタ電流が電流制限スレッショルドに達すると、過電流イベントが起動して IC 内部のハイサイドの FET はオフになり、ローサイドの FET はオンになるため、インダクタ電流は次のスイッチング・サイクルまで減少し続けます。順次発生する

過電流イベントではリファレンス電圧が減少し PWM パルスがスキップされるため、短い過電流イベントでは過電流制限は積極的にフォールドバックしませんが、ハードがショートしている間周波数および電圧のフォールドバック保護を行います。

#### ソフトスタートおよび電圧トラッキング

SS/TRK ピンは、スタートアップ時間の設定または外部電源のトラッキングに使用できる二重機能のピンです。スタートアップまたはソフトスタートの時間は、コンデンサを SS/TRK ピンとグラウンドの間に接続することにより調節できます。ソフトスタート機能を使用すると、レギュレータ出力は、設定電圧に緩やかに到達できるため、電源入力時のストレスを軽減しスタートアップ時の電流を制御できます。ソフトスタート・コンデンサを使わない場合、デバイスはデフォルトで内部ソフトスタート回路を起動するため、スタートアップ時間はおよそ 1ms です。単調なスタートアップが必要なアプリケーションや、PGOOD ピンを使用するアプリケーションでは、外部ソフトスタート・コンデンサを推奨します。SS/TRK ピンを設定して外部電源をトラッキングすることもできます。設計ガイドラインの Figure 8 に示すとおり、SS/TRK ピンに接続された 2 つの外部抵抗によりトラッキング動作を調節できます。

#### プリバイアス・スタートアップ機能

出力電圧がゼロより大きい状態で起動することをプリバイアスといいます。この状態は、FPGA、ASIC または DSP に電源を供給するようなマルチレール・アプリケーションで数多く見られます。これらのアプリケーションでは、出力は 1 つの電源から別の電源へ続く寄生伝導経路を通じてプリバイアスされます。LM20146 は同期コンバータですが、プリバイアス状態が発生しても出力は低下させません。スタートアップ時、LM20146 はソフトスタート電圧がFBピンの電圧を超えない限り電流シンクを行いません。電流シンクしないため、デバイスは電流が負荷の寄生経路を介して導通することによって、発生する被害から負荷を保護します。

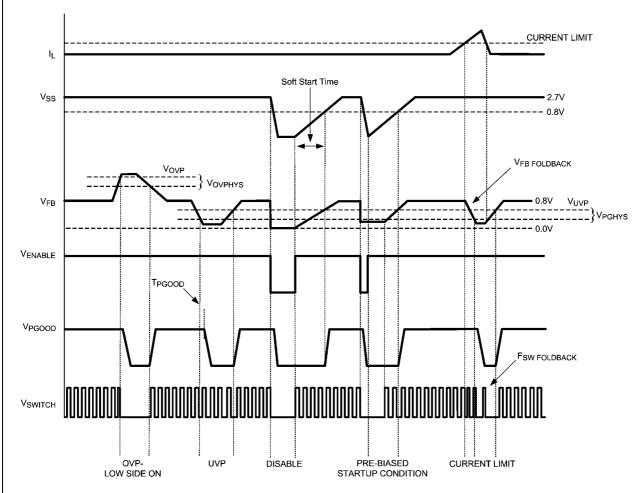

### パワーグッドおよびオーバーボルテージの異常処理

LM20146 は、出力のアンダーボルテージとオーバーボルテージを検出するコンパレータを内蔵しています。設定したオーバーボルテージ保護スレッショルドを超えた出力電圧で異常急変が発生すると、デバイスは現在のオン・パルスを終了し、ローサイド FET をオンし、PGOOD ピンを Low にします。 ローサイド FET は、FB 電圧が安定状態に戻るか、またはゼロクロス検出が起動して FET を TRI-STATE にするまで、オンのままです。出力がアンダーボルテージ保護のスレッショルドに達すると、デバイスはスイッチングを継続し、PGOOD ピンは Low になります。PGOOD 抵抗の代表値は、100k  $\Omega$  のオーダーまたはそれ未満です。 一時的なグリッチの間の誤ったトリップを避けるため、PGOOD ピンには立ち上がりおよび立ち下がりの両方に  $16 \mu s$  のデグリッチ時間があります。 障害状態でのパワーグッド動作の例を Figure 1 に示します。

### 動作の説明(つづき)

FIGURE 1. Powergood Behavior

#### アンダーボルテージ・ロックアウト

LM20146 は、入力電圧が 2.7V (typ) に達しない限りスイッチングしないように、アンダーボルテージ・ロックアウト保護回路を内蔵しています。アンダーボルテージ・ロックアウト・スレッショルドには 45mV のヒステリシスがあり、デバイスが起動中にパワー・オン・グリッチに応答するのを防ぎます。 設計ガイドラインの Figure 7 に示すとおり、必要に応じて、高精度イネーブル・ピンと  $V_{\rm IN}$  に接続された抵抗分圧ネットワークを使うことにより、電源のターンオン点を変更できます。

#### 過熱保護

最大接合部温度を超えた場合に集積回路を保護する目的でサーマル・シャットダウン回路が内蔵されています。 通常 160 ℃でアクティブになると、 LM20146 はパワー FET を TRI-STATE にし、ソフト・スタートをリセットします。 接合部がおよそ 150 ℃まで冷却された後、デバイスは通常のスタートアップ動作によって起動します。この機能はデバイスの予期せぬ過熱に対して致命的な障害を防止します。

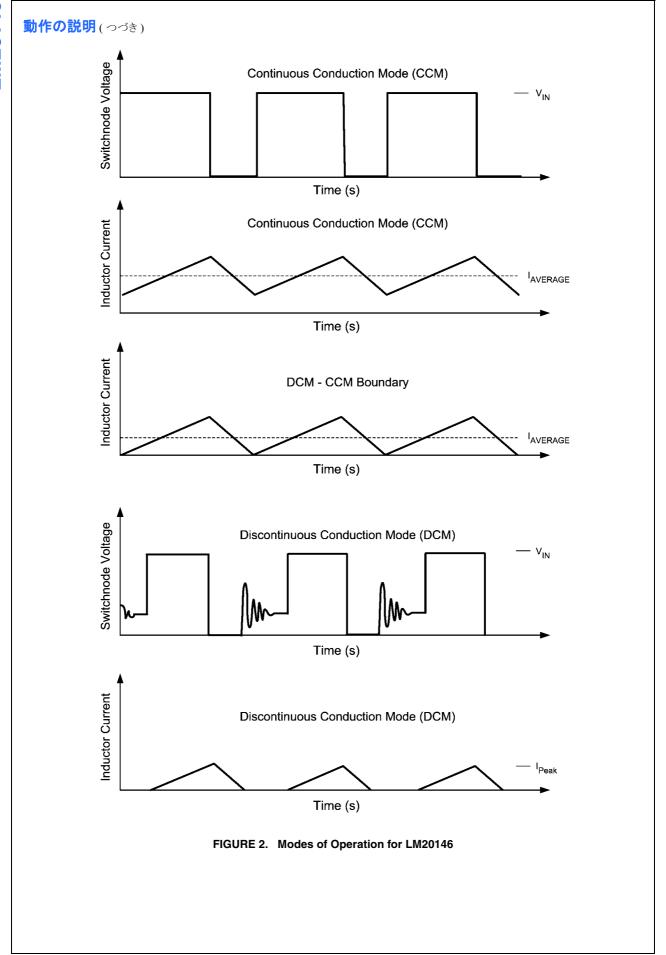

#### 軽負荷動作

LM20146 は、軽負荷で動作する際に高い効率を実現します。 ピーク・ツー・ピークのインダクタのリップル電流が負荷電流の 2 倍になる値まで負荷電流を減少させると、デバイスはダイオード・エミュレーション・モードに入り、大きな負のインダクタ電流を防止します。この状況が発生する値は連続モードの限界となる境界であり、次式で計算できます。

$$I_{\text{BOUNDARY}} = \frac{(V_{\text{IN}} - V_{\text{OUT}}) \times D}{2 \times L \times f_{\text{SW}}}$$

Figure 2 に、連続モード (CCM)、不連続モード、境界条件を示す図を示します。

ダイオード・エミュレーション・モードでは、インダクタ電流がゼロに達すると、SW ノードは必ずハイ・インピーダンスになります。SW ノードがハイ・インピーダンスになると、インダクタとSW ノードの寄生容量によって形成されるLC タンク回路のために、このピンでリンギングが発生します。このリンギングが問題となる場合、スイッチ・ノードからグラウンドへのRC スナバ回路が追加される場合があります。

通常 100mA 未満の非常に軽い負荷では、スイッチング・サイクルの間でいくつかのパルスがスキップされ、スイッチング周波数が効果的に低下し、さらに軽負荷効率が向上します。

### 設計ガイドライン

ここでは、全機能を有する電源の構築に必要な外付け部品の 選定方法を段階を踏んで説明します。どのような DC-DC コン バータの設計であっても、効率、実装面積、性能が最適化の トレードオフになります。このセクションではこれらの設計条件に ついて詳しく取り上げます。 部品選定を簡易化するために、 Figure 3 に示す回路を参考として使用します。特記のない限り、 すべての式で単位は電流をアンペア(A)、容量をファラッド(F)、 インダクタンスをヘンリー(H)、電圧をボルト(V)とします。

FIGURE 3. Typical Application Circuit

降圧コンバータの設計では最初に登場する式はデューティ・サイクルです。 FET によって生じる導通損失と寄生抵抗を無視すると、デューティ・サイクルは次のように近似されます。

$$D = \frac{V_{OUT}}{V_{IN}}$$

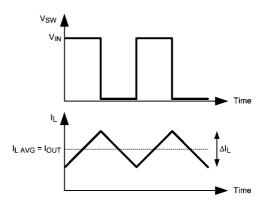

#### インダクタの選択 (L)

インダクタンス値は、動作周波数、負荷電流、リップル電流、 デューティ・サイクルをもとに決定します。

デバイスのピーク電流制限よりも大きな飽和電流定格を持つインダクタを選択します。規定の電流制限は電流制限コンパレータの遅延を考慮していないため、アプリケーションの電流制限は規定値より高くなる可能性があることを念頭においてください。性能を最適化し、デバイスが最大負荷時に電流制限モードに入ることを防止するために、通常リップル電流 Δi<sub>L</sub> が定格出力電流の30%より低くなるようにインダクタンスを選定します。Figure 4 は、スイッチおよびインダクタ・リップル電流波形を示しています。入力電圧、出力電圧、動作周波数、目標のリップル電流がわかれば、次式によりインダクタの最小値を計算できます。

$$L_{MIN} = \frac{(V_{IN} - V_{OUT}) \times D}{\Delta i_L \times f_{SW}}$$

FIGURE 4. Switch and Inductor Current Waveforms

必要に応じて、若干小さい値のインダクタを使用することもできますが、ピーク・インダクタ電流  $I_{OUT}+\Delta i_L/2$  はデバイスのピーク電流制限を超えないようにする必要があります。一般に、電流モード制御ループに適切な電流センス情報を提供するために、インダクタ・リップル電流  $\Delta i_L$  は、定格出力電流の10%以上必要です。インダクタのリップル電流が低すぎる場合、制御ループに充分な電流センス情報がなく、不安定になる場合があります。

# 出力コンデンサの選択 (COUT)

出力コンデンサ COUT は、インダクタ・リップル電流を平滑化するとともに、負荷の変動に対して電荷を供給します。幅広い出力コンデンサを LM20146 と併用し、優れた性能を実現できます。通常セラミック、SP または OSCON コンデンサなどのケミカル・コンデンサを使うことにより、最高性能が得られます。一般的なトレードオフとして、セラミック・コンデンサはきわめて小さな ESR を持ち、出力リップル電圧とノイズ・スパイクを吸収する一方で、SP および OSCON コンデンサは小型大容量のバルク・コンデンサとして負荷変動に対応します。

出力コンデンサの値を選択する際、考慮すべき 2 つの性能規格は出力電圧リップルと過渡応答です。 出力電圧リップルは、次式で近似されます。

$$\Delta V_{OUT} = \Delta i_L x \left[ R_{ESR} + \frac{1}{8 \times f_{SW} \times C_{OUT}} \right]$$

$\Delta V_{OUT}(V)$  は電源出力におけるピーク・ツー・ピーク電圧リップル量、 $R_{ESR}(\Omega)$  は出力コンデンサの直列抵抗、 $f_{SW}$  (Hz) はスイッチング周波数、 $C_{OUT}(F)$  は設計時に使用した出力容量を示します。 許容できる出力リップルの量はアプリケーション固有ですが、一般的に定格出力電圧の 1% 未満に抑えることを推奨します。 セラミック・コンデンサは ESR が非常に低いため適していることがありますが、パッケージおよびコンデンサの電圧定格によっては、印加電圧により容量値が著しく落ちる可能性があることを念頭においてください。出力コンデンサの選択は、負荷変動時の出力電圧低下にも影響します。負荷変動時の出力電圧のピーク低下は、多くの要因に依存します。しかし次式を使うことにより、ループ帯域を無視した変動低下量の近似を得られます。

$$V_{DROOP} = \Delta I_{OUTSTEP} \times R_{ESR} + \frac{L \times \Delta I_{OUTSTEP}^{2}}{C_{OUT} \times (V_{IN} - V_{OUT})}$$

$C_{OUT}$  (F) は必要な出力容量の最小値、L (H) はインダクタの値、 $V_{DROOP}$  (V) はループ帯域幅を無視した出力電圧低下、 $\Delta I_{OUTSTEP}$  (A) は負荷ステップ変動、 $R_{ESR}$  ( $\Omega$ ) は出力コンデンサ ESR、 $V_{IN}$  (V) は入力電圧、 $V_{OUT}$  (V) はレギュレータの出力電圧設定値です。特定の出力リップルまたは変動低下目標で設計する際、コンデンサの誤差および電圧係数の両方を考慮する必要があります。

#### 入力コンデンサの選択 (CIN)

$V_{IN}$ ピンに発生するリップル電圧を抑え、かつ、オン期間中のスイッチ電流の大半を供給する目的で、良質の入力コンデンサが必要です。一般に入力コンデンサには、インピーダンスが低く実装面積が小さいセラミック・コンデンサを推奨します。このとき、X5R や X7R など、適切な誘電体特性のセラミック・コンデンサを選択することが重要です。これらは動作温度が変化しても良好な特性を示し、Y5V コンデンサで生じる DC 電圧のディレーティングを抑えます。大半のアプリケーションでは、 $22\,\mu\,F$ 、X5R、6.3Vの入力コンデンサで充分ですが、入力電源への接続が PVIN ピンから遠い場合はコンデンサを追加しなければならない場合があります。また入力コンデンサを PVIN ピンおよび PGND ピンの可能な限り近くに配置してください。

セラミック以外の入力コンデンサは、RMS 電流定格と最小リップル電圧で選択します。以下の関係式からリップル電流定格の適切な近似が得られます。

$$I_{\text{IN-RMS}} = I_{\text{OUT}} \sqrt{D(1 - D)}$$

RMS リップル電流式で示したとおり、RMS 電流定格が最も必要なのはデューティ・サイクル 50% のときです。この場合、入力コンデンサのRMSリップル電流定格は出力電流の半分より大きい必要があります。 最高性能を引き出すには、低 ESR セラミック・コンデンサはより高容量のコンデンサと並列に配置して、デバイスに最適な入力フィルタリングを行ってください。

# 出力電圧の設定 (R<sub>FB1</sub>、R<sub>FB2</sub>)

デバイスの出力電圧を設定するには、抵抗  $R_{FB1}$  および  $R_{FB2}$  を選択します。 以下の Table 1 に、一般的な出力電圧における  $R_{FB1}$  および  $R_{FB2}$  の推奨値を示します。

TABLE 4. Suggested Values for R<sub>FB1</sub> and R<sub>FB2</sub>

| $R_{FB1}(k\Omega)$ | $R_{FB2}(k\Omega)$ | V <sub>OUT</sub> |

|--------------------|--------------------|------------------|

| short              | open               | 0.8              |

| 4.99               | 10                 | 1.2              |

| 8.87               | 10.2               | 1.5              |

| 12.7               | 10.2               | 1.8              |

| 21.5               | 10.2               | 2.5              |

| 31.6               | 10.2               | 3.3              |

異なる出力電圧が必要な場合、 $R_{FB2}$  に 4.99k  $\Omega\sim$  49.9k  $\Omega$  を 選択し、次式を使って  $R_{FB1}$  を計算してください。

$$R_{FB1} = \left(\frac{V_{OUT}}{0.8} - 1\right) \times R_{FB2}$$

#### 動作周波数の調節 (R<sub>T</sub>)

LM20146 の動作周波数は、RT ピンとグラウンドの間に抵抗を接続することにより調節可能です。特定の動作周波数における  $R_T$  の値は次式を使って計算します。

$$R_T = \left(\frac{78000}{f_{SW}}\right) - 55$$

$f_{SW}$  はスイッチング周波数 (単位: kHz)、 $R_T$  は周波数調節用の抵抗 (単位:  $k\Omega$ )です。「代表的な性能特性」で、発振回路の周波数と $R_T$  の関係の曲線を参照してください。抵抗  $R_T$  を使用しないと、デバイスは動作しません。

## ループ補償 (R<sub>C1</sub>、C<sub>C1</sub>)

ループ補償の目的は、充分な安定性の維持と静的および動的な性能要件を両立させることです。 最適なループ補償は、出力コンデンサ、インダクタ、負荷、デバイス本体に依存します。 Table 2 に、 $100\,\mu\,\mathrm{F}$ 、6.3V のセラミック X5R 出力コンデンサと $1\,\mu\,\mathrm{H}$  のインダクタを使用した際にシステムが安定する補償ネットワークの値を示します。

TABLE 5. Recommended Compensation for  $C_{OUT} = 100 \mu F$ , L = 1.5  $\mu$  H & f<sub>SW</sub> = 500kHz

| V <sub>IN</sub> | V <sub>out</sub> | C <sub>C1</sub> (nF) | $\mathbf{R}_{C1}$ ( $\mathbf{k}\Omega$ ) |

|-----------------|------------------|----------------------|------------------------------------------|

| 5.00            | 3.30             | 2.2                  | 15.4                                     |

| 5.00            | 2.50             | 2.2                  | 13.3                                     |

| 5.00            | 1.80             | 2.2                  | 10.7                                     |

| 5.00            | 1.50             | 2.2                  | 9.31                                     |

| 5.00            | 1.20             | 2.2                  | 7.87                                     |

| 5.00            | 0.80             | 2.7                  | 4.42                                     |

| 3.30            | 2.50             | 2.7                  | 8.45                                     |

| 3.30            | 1.80             | 2.7                  | 7.5                                      |

| 3.30            | 1.50             | 2.7                  | 6.81                                     |

| 3.30            | 1.20             | 2.7                  | 5.9                                      |

| 3.30            | 0.80             | 2.7                  | 4.32                                     |

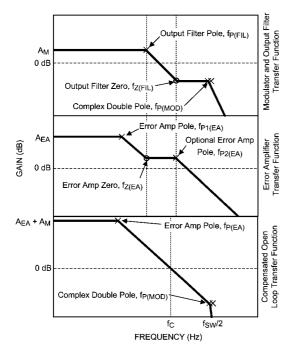

必要なソリューションが上の表と異なる場合、ループ伝達関数を分析してループ補償を最適化してください。全体ループ伝達関数は、パワー段と帰還ネットワーク伝達関数の積になります。安定性を確保するには、きわめて低い周波数からクロスオーバー周波数を超える周波数まで、ループ・ゲインの傾きを - 20dB/dec とすることが目標になります。Figure 5 に、LM20146のパワー段、帰還/補償ネットワーク、その結果生じる閉ループ・システムについて、伝達関数を示します。

FIGURE 5. LM20146 Loop Compensation

パワー段伝達関数は、変調器、出力 LC フィルタおよび負荷によって記述されます。一方帰還伝達関数は、フィードバック抵抗比、エラー・アンプ・ゲイン、外部補償ネットワークにより設定されます。

-20dB/dec の傾きを実現するには、 $f_{Z(EA)}$ のエラー・アンプ・ゼロを配置し出力フィルタ・ポール  $(f_{P(FIL)})$ をキャンセルします。 $f_{P2(EA)}$  にエラー・アンプ・ポールを追加し、 $f_{Z(FIL)}$  の出力フィルタ・ゼロをキャンセルできます。 値の大きいセラミック以外の出力コンデンサを使用する場合、出力フィルタ・ゼロのキャンセルを推奨します。

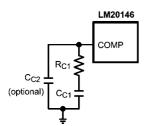

Figure 6 の RC ネットワークを追加することにより、 LM20146 の 補償は終了です。

FIGURE 6. Compensation Network for LM20146

大半のアプリケーションで、 $C_{C1}$ の初期値は 3.3nF が適切です。  $C_{C1}$  の値を選択した後、次式を使って RC の値を計算し、 Figure 5 に示したとおり出力フィルタ・ポール  $(f_{P(FIL)})$  をキャン セルしてください。

$$R_{C1} = \left[ \frac{C_{C1}}{C_{OUT}} \times \left[ \frac{I_{OUT}}{V_{OUT}} + \frac{1-D}{f_{SW} \times L} + \frac{D \times f_{SW}}{48750^* V_{IN}} - \frac{1}{2 \times f_{SW} \times L} \right] \right]^{-1}$$

通常位相マージンを犠牲にして  $C_{C1}$  を下げ、 $R_{C1}$  の値を再度計算することにより、高いクロスオーバー周波数を取得できます。同様に、 $C_{C1}$  を上げ、 $R_{C1}$  を再度計算することにより、よ

り低いクロスオーバー周波数において位相マージンを追加します。LM20146 の補償を試みると同時に、必要な変動低下量およびセトリング・タイムでのシステムの安定性を確保してください。

出力フィルタ・ゼロ、 $f_{Z(FIL)}$ からクロスオーバー周波数  $(f_c)$ に アプローチする場合、追加のコンデンサ  $(C_{C2})$ を COMP ピンからグラウンドに配置してください。このコンデンサはポールを追加して出力フィルタ・ゼロをキャンセルし、 $f_{SW}/2$ のダブル・ポールで位相マージンが低下する前にクロスオーバー周波数が発生することを保証します。出力フィルタ・ゼロは、次式に示すとおり、出力コンデンサの値と ESR によって設定されます。

$$f_{Z(F|L)} = \frac{1}{2 \times \pi \times C_{OUT} \times R_{ESR}}$$

必要に応じて、次式を使って $C_{C2}$ の値を計算してください。

$$C_{C2} = \frac{C_{OUT} \times R_{ESR}}{R_{C1}}$$

$R_{\rm ESR}$  は出力コンデンサ直列抵抗、 $R_{\rm Cl}$  は補償抵抗の計算値です。

### AVIN フィルタ部品 (CF および RF)

高周波ノイズのスパイクによって AVIN ピンおよび AGND ピンに接続された高感度のアナログ回路が妨害されることを防ぐため、PVIN と AVIN の間に高周波数 RC フィルタが必要となります。これらの部品は Figure 3 に  $C_F$  および  $R_F$  として示されています。  $R_F$  に必要な値は  $1\Omega$  です。  $C_F$  は必ず使用してください。  $C_F$  の推奨値は  $1.0\,\mu$  F です。 フィルタ・コンデンサ  $C_F$  は、AVIN と AGND を直接接続し、可能な限り IC の近くに配置してください。このとき、 $C_F$  には X5R や X7R など、適切なセラミック・コンデンサを選択すべきです。

## サブレギュレータ・バイパス・コンデンサ (Cvcc)

VCC ピンに配置したコンデンサは、ノイズをフィルタする効果と内部のサブレギュレータを安定化する働きがあります。 $C_{VCC}$ の推奨値は  $1\mu$  F 以上  $10\mu$  F 以下です。 品質が良い X5R または X7R のセラミック・コンデンサを使用してください。 一般的なアプリケーションでは  $1\mu$  F のセラミック・コンデンサを推奨します。

#### スタートアップ時間の設定 (CSS)

SS ピンとグラウンド間にコンデンサを追加することにより、出力電圧が最終レギュレート値に達する時間を設定できます。  $C_{SS}$  の値が大きいほど、スタートアップ時間は長くなります。 Table 3 に、ソフトスタート・コンデンサの一覧と対応する標準的なスタートアップ時間を示します。

TABLE 6. Start Up Times for Different Soft-Start Capacitors

| Start Up Time (ms) | C <sub>SS</sub> (nF) |

|--------------------|----------------------|

| 1                  | none                 |

| 5                  | 33                   |

| 10                 | 68                   |

| 15                 | 100                  |

| 20                 | 120                  |

スタートアップ時間の変更が必要な場合、次式を使ってスタートアップ時間を計算できます。

$$t_{SS} = \frac{0.8V \times C_{SS}}{I_{SS}}$$

この式が示すとおり、スタートアップ時間はソフトスタート・コンデンサ $C_{SS}$  (F) と、 $5\mu$  A ソフトスタート・ピン電流  $I_{SS}$  (A) の値によって影響を受けます。

ソフトスタート・コンデンサの容量は複数の起動要件を満足するように選択できますが、この容量には制限があります。スタートアップ時間は内部のデフォルト仕様が 1ms になっているため、ソフトスタート時間をこの値より短くすることはできません。 デバイスがイネーブルになっているとき、ソフトスタート・コンデンサが、ソフトスタート上昇の直前に放電する場合、およそ  $50\mu s$ のインターバルがあります。 イネーブル・ピンが急激なパルス状になっている場合、またはソフトスタート・コンデンサが大容量の場合、 $C_{SS}$ が完全に放電するために充分な時間がなく、スタートアップ時間が予想より短くなる場合があります。長いディスエーブル期間中のソフトスタート・コンデンサの放電を助けるために、SS/TRKピンとグラウンドの間に外部の  $1M\Omega$  抵抗を接続できます。スタートアップ時間には大きな影響を与えません。

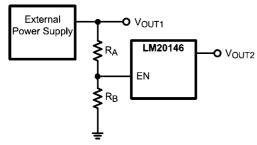

#### 高精度イネーブル・ピンおよびパワーグッド・ピンの使用

LM20146 の高精度イネーブル (EN) ピンとパワーグッド (PGOOD) ピンを使って、多くのシーケンス要件に対応できます。 Figure 7 に示すとおり、2 つの外部抵抗を使用すれば、高精度イネーブル・ピンで LM20146 のターンオンを制御できます

FIGURE 7. Sequencing LM20146 with Precision Enable

抵抗  $R_B$  の値はユーザーが選択でき、分圧抵抗によって電流を制御できます。 通常、この抵抗は  $10k\Omega\sim 1M\Omega$  の間で選択されます。  $R_B$  の値を選択すると次式を使って抵抗  $R_A$  が求められ、必要なターンオン電圧を設定できます。

$$R_A = \left(\frac{V_{TO}}{V_{IH\_EN}} - 1\right) x R_B$$

特定のターンオン・スレッショルド  $(V_{TO})$  に設計する場合、入力電源の許容誤差、イネーブル・スレッショルド  $(V_{IH\ EN})$  および外部抵抗を考慮して、デバイスに適切なターンオンを確定する必要があります。

LM20146 の特長は、オープン・ドレイン・パワーグッド (PGOOD) ピンが外部電源または負荷のシーケンス制御を行い、 異常検 出を行うことです。このピンには、 PGOOD を High にする外部 抵抗 ( $R_{PG}$ ) が必要です。 同時に出力が PGOOD 許容誤差ウィンドウ内にある必要があります。この抵抗の一般的な値は、  $10k\,\Omega\sim 100k\,\Omega$  です。

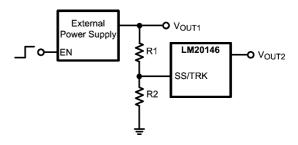

#### 外部電源のトラッキング

Figure 8 に示すとおり、SS/TRK ピンにつながる分圧抵抗ネットワークを適切に選択することにより、LM20146 の出力を外部電

源をトラッキングするよう設定し、同時スタートアップまたはレシ オメトリック・スタートアップを実現できます。

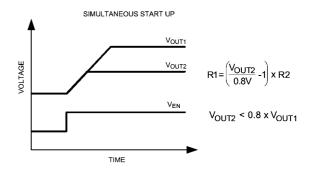

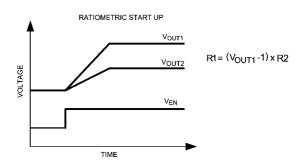

FIGURE 8. Tracking an External Supply

SS/TRK ピンは常に電流  $I_{SS}$  を充電するソフトスタートのため、R2 の容量は  $10k\Omega$  未満とし、トラッキング出力のエラーを最小限に抑える必要があります。R2 の値を選択すると、Figure 9 の適切な式を使って R1 の値を計算し、必要なスタートアップを求められます。Figure 9 に、2 種類の一般的なスタートアップ・シーケンスを示します。上の波形は同時スタートアップを、下の波形はレシオメトリック・スタートアップを示しています。

FIGURE 9. Common Start Up Sequences

同時スタートアップは、大半の FPGA、DSP またはその他のマイクロプロセッサに電源供給する際に適しています。これらのシステムでは、通常高い電圧 VOUTI が I/O の電源を供給し、低い電圧 VOUT2 がコアの電源を供給します。同時スタートアップでは、プロセッサのコアと I/O ピン間に存在する可能性のある寄生伝導経路をオンすることを避けるため、これらのアプリケーションに対しより堅牢な電源供給を行います。

2番目に一般的な電源供給は、レシオメトリック・スタートアップ として知られています。このスタートアップは、両方の電源を同 時に最終値にする必要のあるアプリケーションに適しています。

ソフトスタート機能と同様、最速のスタートアップは、トラッキング電圧の立ち上がり時間に関係なく、1ms が可能です。トラッキング機能を使う場合、充分なオーバードライブと過渡変動に対する耐性を持つために、SS/TRACK ピンによって見られる最終電圧は 1V を超える必要があります。

#### 熱に関する考慮事項

LM20146の放熱特性は、接合部温度と周囲温度とを関係付ける  $\theta_{\rm JA}$  パラメータを使用して規定します。  $\theta_{\rm JA}$  の値は多くの変数に依存しますが、デバイス動作時の接合部温度を概算するために使えます。

デバイスの接合部温度を概算するには、次の関係式を使用します。

$$T_{J} = P_D \theta_{JA} + T_A$$

および

$P_D = P_{IN} \times (1 - Efficiency) - 1.1 \times I_{OUT}2 \times DCR$  各項の詳細は次のとおりです。

T<sub>I</sub> は接合部温度(単位:℃)

$P_{IN}$  は入力電力 ( 単位 : W) ( $P_{IN} = V_{IN} \times I_{IN}$ )

θ IA は LM20146 の接合部-周囲間熱抵抗

T<sub>A</sub> は周囲温度 (単位:℃)

I<sub>OUT</sub> は出力負荷電流

DCR はインダクタ直列抵抗

動作の信頼性を保つには、動作時の接合部温度  $(\Gamma_J)$  を常に 125  $\mathbb{C}$ 未満に保つことが重要です。接合部温度が 160  $\mathbb{C}$ を超えると、デバイスはサーマル・シャットダウンを繰り返します。サーマル・シャットダウンが発生するのは、デバイス内で不適切なヒートシンクまたは過度な電力消費が発生している徴候です。

Figure 10 に、4 層基板上の特定 PCB の銅エリアにおける  $\theta$  JA の適切な概算値を示します。 PCB の放熱板には、eTSSOP 露出パッドの直下に、PCB の最下層にある 2oz の銅が含まれています。 最下層の銅は、 $4 \times 4$  列の 12mil のスルーホールにより、eTSSOP 露出パッドに接続されています。

FIGURE 10. Thermal Resistance vs PCB Area

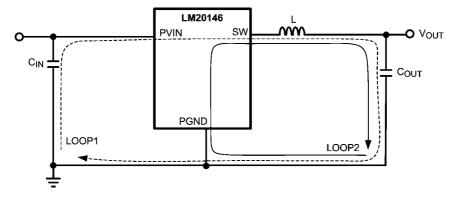

## PCB レイアウトの考慮事項

プリント基板のレイアウトはDC/DCコンバータの設計で重要な部分を占めています。設計が適切ではないプリント基板を使用すると、EMI、グラウンド・バウンス、配線での電圧降下などにより、DC/DCコンバータの性能と周辺回路の動作に影響を与えます。不適切な基板では、DC/DCコンバータに不正な信号が入力され、制御性と安定度が低下します。

次に述べる基本的な設計ルールに従い、適切なプリント基板設 計を行ってください。

1. スイッチングされた電流ループの面積を最小限に抑えます。降圧型レギュレータには電流が急速にスイッチする 2 個のループが存在します。最初のループは入力コンデンサから始まり、レギュレータの VIN ピン、レギュレータの SW ピン、インダクタ、そして出力コンデンサおよび出力負荷につながる経路です。もう1 つは、出力コンデンサのグラウンドから始まり、レギュレータの PGND ピンを通って、インダクタから出力負荷へと至るループです (Figure 11 参照)。両方のループ面積を最小化するために、入力コンデンサを PVIN ピンの可能な限り近くに配置してください。入出力コンデンサ両方の接地には、PGNDに接続する小型の局部的な上側プレーンおよびダイ・アタッチ・パッド (DAP) があります。インダクタを SW ピンおよび出力コンデンサの可能な限り近くに配置してください。

2. スイッチ・ノードの銅エリアを最小限に抑えます。 LM20146 にはパッケージの反対側に SW ピンがあるため、各 SW ピンから 2 ~ 4 個のスルーホールを介して、下層または基板内部の層と接続することを推奨します。 SW ピンはパッケージ下を通るパターンにより直接接続してください。 IR 損失を最小限に抑えるために、このパターンの幅は 50mil を下回らないものとしますが、銅エリアを最小限にするため、100mil を超えないものとします。一般に、SW ピンは電源グラウンドへのグラウンド・リターン経路をブロックする可能性があるため、上層には接続しないでください。インダクタは SW ピンの 1 つに可能な限り近付けて配置し、スイッチ・ノードの同エリアを最小化してください。

3. DAP の下に位置するすべてのデバイス・アナログ・グラウンドは、一点アースとしてください。 補償、帰還、ソフトスタート部品のためのグラウンドはまとめて接続し、デバイスの AGND ピンに配線してください。 AGND ピンは DAP の下にある PGND に接続してください。 このことにより、 すべてのスイッチ電流または負荷電流がアナログ・グラウンド層に流れるのを防ぎます。 グラウンドが適切に処理されていない場合、負荷制御特性の劣化またはスイッチング動作の不定につながります。

4. FB ピンへの基板配線を最小限に抑えます。 帰還ノードのインピーダンスが高くなる可能性があるため、 出力の分圧抵抗から FB ピンまでのパターンは可能な限り短くしてください。 値の高い抵抗を使って出力電圧を設定している場合、最も重要な点です。 帰還配線は SW ピンおよびインダクタから遠ざけ、スイッチ・ノイズで帰還信号に干渉を与えないようにしてください。

5. 入出力バス接続は、可能な限り広くします。これで、コンバータ入出力時の電圧降下を和らげ、効率を良くします。 負荷の電圧精度が重要な場合、帰還電圧センスを必ず負荷側にしてください。このことにより、負荷の電圧降下を修正し、最適な出力精度を実現します。

6. 適切なデバイスのヒートシンクを行います。 可能な限り多くの スルーホールを使い、DAP を電力消費放熱板に接続します。 最適な結果を得るために、4 × 4 列のスルーホールを使い、最小のスルーホールの直径を 12mil とします。 「熱に関する考慮事項」を参照し、充分な銅の放熱面積を使って接合部温度を125℃未満に保ちます。

FIGURE 11. Schematic of LM20146 Highlighting Layout Sensitive Nodes

# 代表的なアプリケーション回路

このセクションでは、アプリケーションのソリューション用に部品 リストを示します。以下の図はすべての部品リストから参照しま す。これらのソリューションの補償は、幅広い入出力電圧にわ たって動作するよう最適化されています。 過渡応答を速くする 必要がある場合は、 $C_{C1}$  の値を下げ、 設計ガイドラインに沿って新たに  $R_{C1}$  の値を計算してください。

FIGURE 12.

# 部品表 (VIN = 5V、VOUT = 3.3V、FSW = 500kHz、IOUTMAX = 6A)

| Designator       | Description                | Part Number       | Manufacturer           | Qty |

|------------------|----------------------------|-------------------|------------------------|-----|

| U1               | Synchronous Buck Regulator | LM20146           | National Semiconductor | 1   |

| C <sub>IN</sub>  | 100μF, 1210, X5R, 6.3V     | C3225X5R0J107M    | TDK                    | 1   |

| C <sub>OUT</sub> | 100μF, 1210, X5R, 6.3V     | C3225X5R0J107M    | TDK                    | 1   |

| L                | 1μH, 7.8 mΩ                | SPM6530T-1R0M120  | TDK                    | 1   |

| R <sub>F</sub>   | 1Ω, 0603                   | CRCW06031R0J-e3   | Vishay-Dale            | 1   |

| C <sub>F</sub>   | 100nF, 0603, X7R, 16V      | GRM188R71C104KA01 | Murata                 | 1   |

| C <sub>VCC</sub> | 1μF, 0603, X5R, 6.3V       | GRM188R60J105KA01 | Murata                 | 1   |

| R <sub>C1</sub>  | 14.3 kΩ, 0603              | CRCW06031432F-e3  | Vishay-Dale            | 1   |

| C <sub>C1</sub>  | 1nF, 0603, COG, 50V        | GRM1885C1H102JA01 | Murata                 | 1   |

| C <sub>SS</sub>  | 33nF, 0603, X7R, 25V       | VJ0603Y333KXXA    | Vishay-Vitramon        | 1   |

| R <sub>T</sub>   | 100kΩ, 0603                | CRCW06031003F-e3  | Vishay-Dale            | 1   |

| R <sub>FB1</sub> | 31.6kΩ, 0603               | CRCW06033162F-e3  | Vishay-Dale            | 1   |

| R <sub>FB2</sub> | 10.2kΩ, 0603               | CRCW06031022F-e3  | Vishay-Dale            | 1   |

# 部品表 (VIN = 3.3V ~ 5V、VOUT = 1.2V、FSW = 750kHz、IOUTMAX = 6A)

| Designator       | Description                | Part Number       | Manufacturer           | Qty |

|------------------|----------------------------|-------------------|------------------------|-----|

| U1               | Synchronous Buck Regulator | LM20146           | National Semiconductor | 1   |

| C <sub>IN</sub>  | 100μF, 1210, X5R, 6.3V     | C3225X5R0J107M    | TDK                    | 1   |

| C <sub>OUT</sub> | 100μF, 1210, X5R, 6.3V     | C3225X5R0J107M    | TDK                    | 1   |

| L                | 0.68μH, 5.39 mΩ            | SPM6530T-R68M140  | TDK                    | 1   |

| R <sub>F</sub>   | 1Ω, 0603                   | CRCW06031R0J-e3   | Vishay-Dale            | 1   |

| C <sub>F</sub>   | 100nF, 0603, X7R, 16V      | GRM188R71C104KA01 | Murata                 | 1   |

| C <sub>vcc</sub> | 1μF, 0603, X5R, 6.3V       | GRM188R60J105KA01 | Murata                 | 1   |

| R <sub>C1</sub>  | 4.53kΩ, 0603               | CRCW06034532F-e3  | Vishay-Dale            | 1   |

| C <sub>C1</sub>  | 1.8nF, 0603, X7R, 25V      | VJ0603Y182KXXA    | Vishay-Vitramon        | 1   |

| C <sub>SS</sub>  | 33nF, 0603, X7R, 25V       | VJ0603Y333KXXA    | Vishay-Vitramon        | 1   |

| R <sub>T</sub>   | 48.7kΩ, 0603               | CRCW06034872F-e3  | Vishay-Dale            | 1   |

| R <sub>FB1</sub> | 4.99kΩ, 0603               | CRCW06034991F-e3  | Vishay-Dale            | 1   |

| R <sub>FB2</sub> | 10kΩ, 0603                 | CRCW06031002F-e3  | Vishay-Dale            | 1   |

20 www.national.com/jpn/

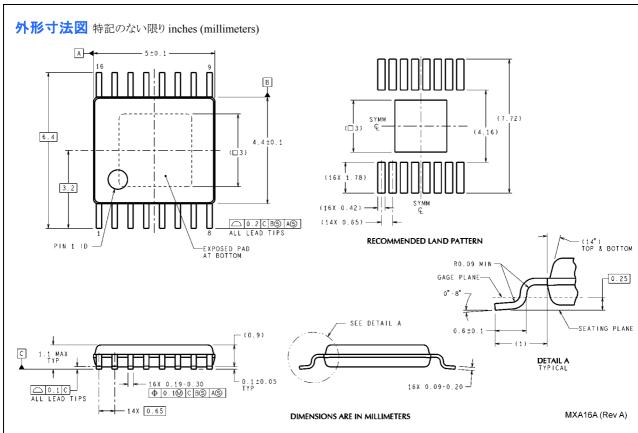

16-Lead eTSSOP Package NS Package Number MXA16A

このドキュメントの内容はナショナル セミコンダクター社製品の関連情報として提供されます。ナショナル セミコンダクター社 は、この発行物の内容の正確性または完全性について、いかなる表明または保証もいたしません。また、仕様と製品説明を予告なく変更する権利を有します。このドキュメントはいかなる知的財産権に対するライセンスも、明示的、黙示的、禁反言による惹起、またはその他を問わず、付与するものではありません。

試験や品質管理は、ナショナル セミコンダクター社が自社の製品保証を維持するために必要と考える範囲に用いられます。政府が 課す要件によって指定される場合を除き、各製品のすべてのパラメータの試験を必ずしも実施するわけではありません。ナショナ ル セミコンダクター社は製品適用の援助や購入者の製品設計に対する義務は負いかねます。ナショナル セミコンダクター社の部品 を使用した製品および製品適用の責任は購入者にあります。ナショナル セミコンダクター社の製品を用いたいかなる製品の使用ま たは供給に先立ち、購入者は、適切な設計、試験、および動作上の安全手段を講じなければなりません。

それら製品の販売に関するナショナル セミコンダクター社との取引条件で規定される場合を除き、ナショナル セミコンダクター社 は一切の義務を負わないものとし、また、ナショナル セミコンダクター社の製品の販売か使用、またはその両方に関連する特定目的への適合性、商品の機能性、ないしは特許、著作権、または他の知的財産権の侵害に関連した義務または保証を含むいかなる表明または黙示的保証も行いません。

#### 生命維持装置への使用について

ナショナル セミコンダクター社の製品は、ナショナル セミコンダクター社の最高経営責任者 (CEO) および法務部門 (GENERAL COUNSEL) の事前の書面による承諾がない限り、生命維持装置または生命維持システム内のきわめて重要な部品に使用することは 認められていません。

をいるしているとん。 ここで、生命維持装置またはシステムとは (a) 体内に外科的に使用されることを意図されたもの、または (b) 生命を維持あるいは 支持するものをいい、ラベルにより表示される使用法に従って適切に使用された場合に、これの不具合が使用者に身体的障害を与 えると予想されるものをいいます。重要な部品とは、生命維持にかかわる装置またはシステム内のすべての部品をいい、これの不 具合が生命維持用の装置またはシステムの不具合の原因となりそれらの安全性や機能に影響を及ぼすことが予想されるものをいい ます。

National Semiconductor とナショナル セミコンダクターのロゴはナショナル セミコンダクター コーポレーションの登録商標です。その他のブランド や製品名は各権利所有者の商標または登録商標です。

Copyright © 2010 National Semiconductor Corporation

製品の最新情報については www.national.com をご覧ください。

# ナショナル セミコンダクター ジャパン株式会社

本社/〒 135-0042 東京都江東区木場 2-17-16

技術資料(日本語/英語)はホームページより入手可能です。

www.national.com/jpn/

TEL.(03)5639-7300

本資料に掲載されているすべての回路の使用に起因する第三者の特許権その他の権利侵害に関して、弊社ではその責を負いません。また掲載内容は予告無く変更されることがありますのでご了承ください。

# ご注意

日本テキサス・インスツルメンツ株式会社(以下TIJといいます)及びTexas Instruments Incorporated(TIJの親会社、以下TIJないしTexas Instruments Incorporatedを総称してTIといいます)は、その製品及びサービスを任意に修正し、改善、改良、その他の変更をし、もしくは製品の製造中止またはサービスの提供を中止する権利を留保します。従いまして、お客様は、発注される前に、関連する最新の情報を取得して頂き、その情報が現在有効かつ完全なものであるかどうかご確認下さい。全ての製品は、お客様とTIJとの間に取引契約が締結されている場合は、当該契約条件に基づき、また当該取引契約が締結されていない場合は、ご注文の受諾の際に提示されるTIJの標準販売契約約款に従って販売されます。

TIは、そのハードウェア製品が、TIの標準保証条件に従い販売時の仕様に対応した性能を有していること、またはお客様とTIJとの間で合意された保証条件に従い合意された仕様に対応した性能を有していることを保証します。検査およびその他の品質管理技法は、TIが当該保証を支援するのに必要とみなす範囲で行なわれております。各デバイスの全てのパラメーターに関する固有の検査は、政府がそれ等の実行を義務づけている場合を除き、必ずしも行なわれておりません。

TIは、製品のアプリケーションに関する支援もしくはお客様の製品の設計について責任を負うことはありません。TI製部品を使用しているお客様の製品及びそのアプリケーションについての責任はお客様にあります。TI製部品を使用したお客様の製品及びアプリケーションについて想定されうる危険を最小のものとするため、適切な設計上および操作上の安全対策は、必ずお客様にてお取り下さい。

TIは、TIの製品もしくはサービスが使用されている組み合せ、機械装置、もしくは方法に関連しているTIの特許権、著作権、回路配置利用権、その他のTIの知的財産権に基づいて何らかのライセンスを許諾するということは明示的にも黙示的にも保証も表明もしておりません。TIが第三者の製品もしくはサービスについて情報を提供することは、TIが当該製品もしくはサービスを使用することについてライセンスを与えるとか、保証もしくは是認するということを意味しません。そのような情報を使用するには第三者の特許その他の知的財産権に基づき当該第三者からライセンスを得なければならない場合もあり、またTIの特許その他の知的財産権に基づきTIからライセンスを得て頂かなければならない場合もあります。

TIのデータ・ブックもしくはデータ・シートの中にある情報を複製することは、その情報に一切の変更を加えること無く、かつその情報と結び付られた全ての保証、条件、制限及び通知と共に複製がなされる限りにおいて許されるものとします。当該情報に変更を加えて複製することは不公正で誤認を生じさせる行為です。TIは、そのような変更された情報や複製については何の義務も責任も負いません。

TIの製品もしくはサービスについてTIにより示された数値、特性、条件その他のパラメーターと異なる、あるいは、それを超えてなされた説明で当該TI製品もしくはサービスを再販売することは、当該TI製品もしくはサービスに対する全ての明示的保証、及び何らかの黙示的保証を無効にし、かつ不公正で誤認を生じさせる行為です。TIは、そのような説明については何の義務も責任もありません。

TIは、TIの製品が、安全でないことが致命的となる用途ないしアプリケーション(例えば、生命維持装置のように、TI製品に不良があった場合に、その不良により相当な確率で死傷等の重篤な事故が発生するようなもの)に使用されることを認めておりません。但し、お客様とTIの双方の権限有る役員が書面でそのような使用について明確に合意した場合は除きます。たとえTIがアプリケーションに関連した情報やサポートを提供したとしても、お客様は、そのようなアプリケーションの安全面及び規制面から見た諸問題を解決するために必要とされる専門的知識及び技術を持ち、かつ、お客様の製品について、またTI製品をそのような安全でないことが致命的となる用途に使用することについて、お客様が全ての法的責任、規制を遵守する責任、及び安全に関する要求事項を満足させる責任を負っていることを認め、かつそのことに同意します。さらに、もし万一、TIの製品がそのような安全でないことが致命的となる用途に使用されたことによって損害が発生し、TIないしその代表者がその損害を賠償した場合は、お客様がTIないしその代表者にその全額の補償をするものとします。

TI製品は、軍事的用途もしくは宇宙航空アプリケーションないし軍事的環境、航空宇宙環境にて使用されるようには設計もされていませんし、使用されることを意図されておりません。但し、当該TI製品が、軍需対応グレード品、若しくは「強化プラスティック」製品としてTIが特別に指定した製品である場合は除きます。TIが軍需対応グレード品として指定した製品のみが軍需品の仕様書に合致いたします。お客様は、TIが軍需対応グレード品として指定して収ない製品を、軍事的用途もしくは軍事的環境下で使用することは、もっぱらお客様の危険負担においてなされるということ、及び、お客様がもっぱら責任をもって、そのような使用に関して必要とされる全ての法的要求事項及び規制上の要求事項を満足させなければならないことを認め、かつ同意します。

TI製品は、自動車用アプリケーションないし自動車の環境において使用されるようには設計されていませんし、また使用されることを意図されておりません。但し、TIがISO/TS 16949の要求事項を満たしていると特別に指定したTI製品は除きます。お客様は、お客様が当該TI指定品以外のTI製品を自動車用アプリケーションに使用しても、TIは当該要求事項を満たしていなかったことについて、いかなる責任も負わないことを認め、かつ同意します。

Copyright © 2011, Texas Instruments Incorporated 日本語版 日本テキサス・インスツルメンツ株式会社

#### 弊社半導体製品の取り扱い・保管について

半導体製品は、取り扱い、保管・輸送環境、基板実装条件によっては、お客様での実装前後に破壊/劣化、または故障を起こすことがあります。

弊社半導体製品のお取り扱い、ご使用にあたっては下記の点を遵守して下さい。 1. 熱電気

- 素手で半導体製品単体を触らないこと。どうしても触る必要がある場合は、リストストラップ等で人体からアースをとり、導電性手袋等をして取り扱うこと。

- 弊社出荷梱包単位(外装から取り出された内装及び個装)又は製品 単品で取り扱いを行う場合は、接地された導電性のテーブル上で(導 電性マットにアースをとったもの等)、アースをした作業者が行う こと。また、コンテナ等も、導電性のものを使うこと。

- マウンタやはんだ付け設備等、半導体の実装に関わる全ての装置類は、静電気の帯電を防止する措置を施すこと。

- 前記のリストストラップ・導電性手袋・テーブル表面及び実装装置 類の接地等の静電気帯電防止措置は、常に管理されその機能が確認 されていること。

#### 2. 温·湿度環境

■ 温度:0~40℃、相対湿度:40~85%で保管・輸送及び取り扱いを行うこと。(但し、結露しないこと。)

- 直射日光があたる状態で保管・輸送しないこと。

- 3. 防湿梱包

- 防湿梱包品は、開封後は個別推奨保管環境及び期間に従い基板実装すること。

- 4. 機械的衝擊

- 梱包品(外装、内装、個装)及び製品単品を落下させたり、衝撃を 与えないこと。

- 5. 熱衝撃

- はんだ付け時は、最低限260℃以上の高温状態に、10秒以上さら さないこと。(個別推奨条件がある時はそれに従うこと。)

- 6. 汚染

- はんだ付け性を損なう、又はアルミ配線腐食の原因となるような汚染物質(硫黄、塩素等ハロゲン)のある環境で保管・輸送しないこと。

- はんだ付け後は十分にフラックスの洗浄を行うこと。(不純物含有率が一定以下に保証された無洗浄タイプのフラックスは除く。)

以上