order

Now

## LM25119Q

### JAJSFB3-APRIL 2018

# LM25119Q 入力電圧範囲の広いデュアル同期整流降圧型コントローラ

## 1 特長

- 車載アプリケーションに対応

- 下記内容でAEC-Q100認定済み:

- デバイス温度グレード1: 動作時周囲温度範囲 -40°C~125°C

- デバイスHBM ESD分類レベル1C

- デバイスCDM ESD分類レベルC4A

- エミュレーションによるピーク電流モード制御

- 広い動作電圧範囲(4.5V~42V)

- デュアル出力またはインタリーブ単一出力に容易 に構成可能

- 堅牢な3.3Aピーク・ゲート駆動

- スイッチング周波数は750kHzまでプログラム可能

- (オプション)ダイオード・エミュレーション・ モード

- 0.8Vから設定可能な出力電圧

- 精度1.5%の基準電圧

- 電流制限をプログラム可能

- ヒカップ・モード過負荷保護

- ソフトスタートをプログラム可能

- ライン低電圧誤動作防止をプログラム可能

- 外部バイアス電源への自動切り替え

- チャネル2イネーブルのロジック入力

- サーマル・シャットダウン

ΔĀ

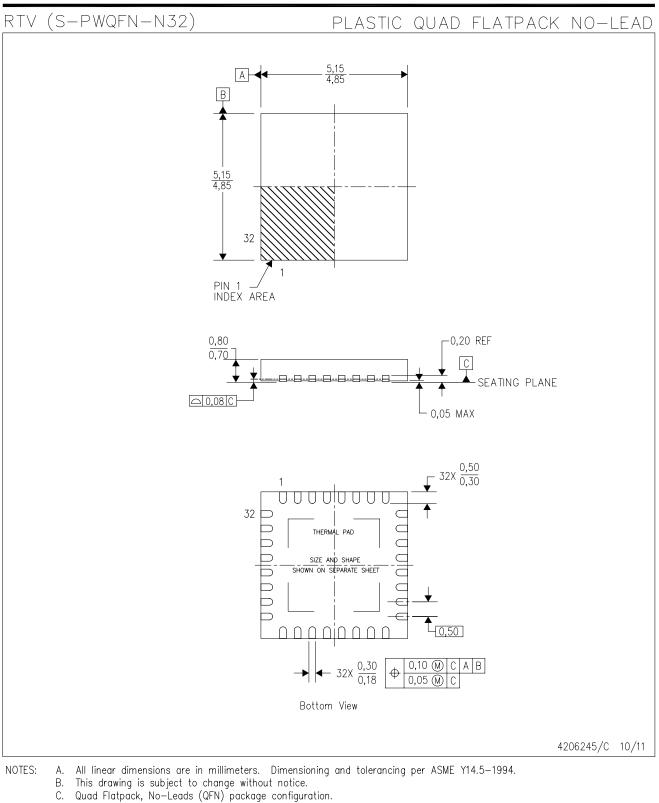

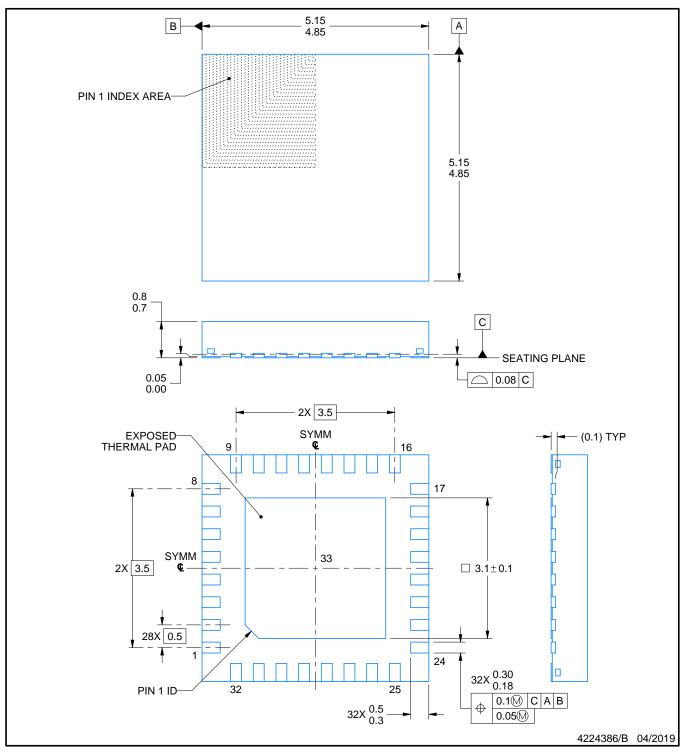

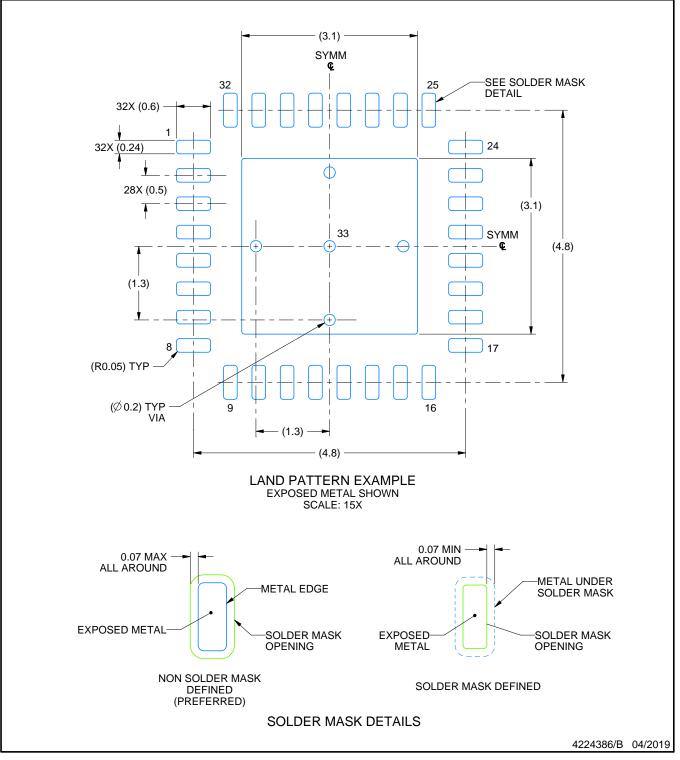

• リードレス32ピンWQFNパッケージ

2 アプリケーション

Tools &

Software

- 車載インフォテインメント

- 車載用USBアクセサリ・アダプタ

## 3 概要

LM25119Qデバイスは降圧レギュレータ・アプリケーション 用に開発されたデュアル同期整流降圧型コントローラで、 高電圧または変動幅が大きい入力電源で動作します。制 御方法は、エミュレート電流ランプを使用した電流モード 制御です。電流モード制御は、入力電圧フィードフォワー ド、サイクルごとの電流制限、簡単なループ補償という特 長を原理的に備えています。エミュレート電流ランプの使 用によって、パルス幅変調回路のノイズによる影響を抑え るとともに、入力電圧の高いアプリケーションでデューティ・ サイクルがきわめて小さい状態でも信頼性の高い制御を 実現します。スイッチング周波数は50kHz~750kHzの範 囲で設定可能です。LM25119Qデバイスはアダプティブ・ デッドタイム制御を用いて、ハイサイドとローサイドの外付 けNチャネルMOSパワー・スイッチを駆動します。また、ダ イオード・エミュレーション・モードをユーザーが選択可能 で、不連続モードの動作が可能になり、軽負荷状況で効 率が向上します。

#### 製品情報<sup>(1)</sup>

| 型番       | パッケージ    | 本体サイズ(公称)     |  |  |  |

|----------|----------|---------------|--|--|--|

| LM25119Q | WQFN(32) | 5.00mm×5.00mm |  |  |  |

|          |          |               |  |  |  |

(1) 利用可能なすべてのパッケージについては、このデータシートの末尾にある注文情報を参照してください。

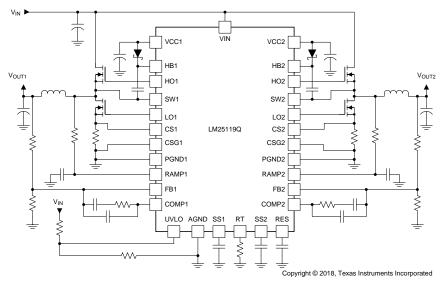

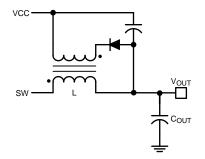

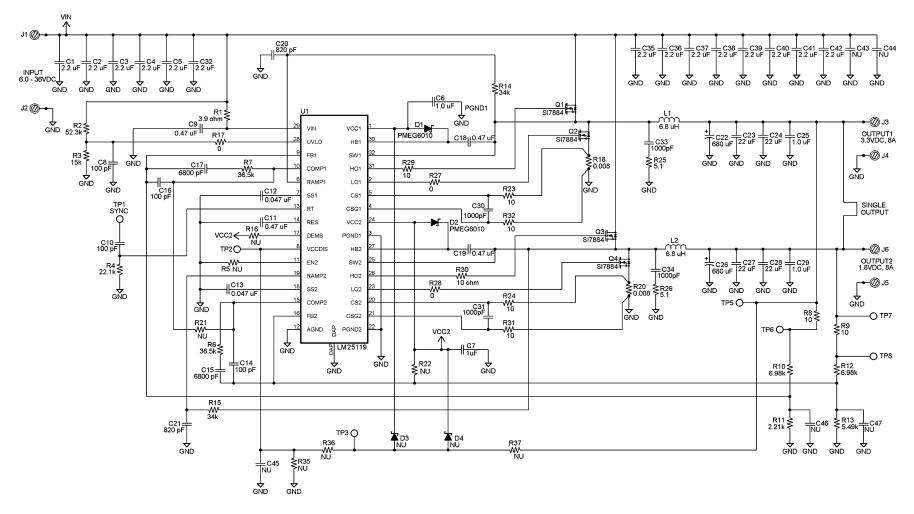

## 代表的なアプリケーション回路

英語版のTI製品についての情報を翻訳したこの資料は、製品の概要を確認する目的で便宜的に提供しているものです。該当する正式な英語版の最新情報は、www.ti.comで閲覧でき、その内 容が常に優先されます。TIでは翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、必ず最新版の英語版をご参照くださいますようお願いいたします。 English Data Sheet: SLUSD97

# 目次

| 1 | 特長   |                                  | 1              |

|---|------|----------------------------------|----------------|

| 2 | アプ   | リケーション                           | 1              |

| 3 | 概要   | <u>.</u>                         | 1              |

| 4 | 改訂   | `履歴                              | 2              |

| 5 | 概要   | 〔(続き)                            | 3              |

| 6 | Pin  | Configuration and Functions      | 4              |

| 7 | Spe  | cifications                      | <mark>6</mark> |

|   | 7.1  | Absolute Maximum Ratings         | <mark>6</mark> |

|   | 7.2  | ESD Ratings                      | 6              |

|   | 7.3  | Recommended Operating Conditions | <mark>6</mark> |

|   | 7.4  | Thermal Information              | 7              |

|   | 7.5  | Electrical Characteristics       | 7              |

|   | 7.6  | Switching Characteristics        | 9              |

|   | 7.7  | Typical Characteristics          | 10             |

| 8 | Deta | ailed Description                | 12             |

|   | 8.1  | Overview                         | 12             |

|    | 8.2  | Functional Block Diagram   | . 13 |

|----|------|----------------------------|------|

|    | 8.3  | Feature Description        | . 14 |

|    | 8.4  | Device Functional Modes    | . 19 |

| 9  | Appl | ication and Implementation | 20   |

|    | 9.1  | Application Information    | . 20 |

|    | 9.2  | Typical Applications       | . 21 |

| 10 | Pow  | er Supply Recommendations  | 36   |

| 11 | Layo | out                        | 36   |

|    | 11.1 | Layout Guidelines          | . 36 |

|    | 11.2 | Layout Example             | . 37 |

| 12 | デバ   | イスおよびドキュメントのサポート           | 38   |

|    | 12.1 | コミュニティ・リソース                | . 38 |

|    | 12.2 | 商標                         | . 38 |

|    | 12.3 | 静電気放電に関する注意事項              | . 38 |

|    | 12.4 | Glossary                   | . 38 |

| 13 | メカニ  | ニカル、パッケージ、および注文情報          | 38   |

|    |      |                            |      |

# 4 改訂履歴

| 日付      | リビジョン | 注                                                                   |

|---------|-------|---------------------------------------------------------------------|

| 2018年4月 | *     | 初版これ以前はLM25119データシートに含まれ<br>ていました。以前の改訂履歴については<br>SNVS680を参照してください。 |

www.tij.co.jp

## 5 概要(続き)

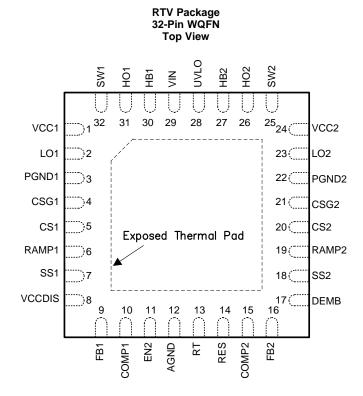

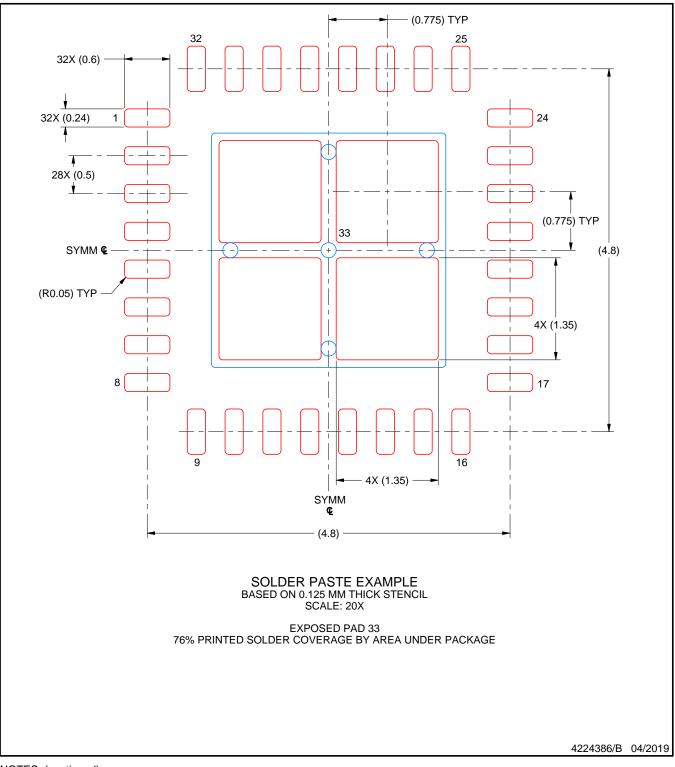

また、外部バイアスへの自動切換えに対応した高耐圧バイアス・レギュレータによって、さらに効率化を図っています。その 他に、サーマル・シャットダウン、周波数の同期化、サイクルごとの電流制限、ヒカップ・モード電流制限、電圧を設定可能な ライン低電圧誤動作防止などの機能を搭載しています。放熱を助ける露出ダイ接続パッドを備えて消費可能電力を増大さ せたリードレス32ピンWQFNパッケージで供給されます。

# 6 Pin Configuration and Functions

#### **Pin Functions**

| PI    | N   | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------|-----|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME  | NO. | ITFE''              | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| AGND  | 12  | G                   | Analog ground. Return for the internal 0.8-V voltage reference and analog circuits.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| COMP1 | 10  | 0                   | Output of the channel1 internal error amplifier. The loop compensation network must be connected between this pin and the FB1 pin.                                                                                                                                                                                                                                                                                                                                                                                     |

| COMP2 | 15  | 0                   | Output of the channel2 internal error amplifier. The loop compensation network must be connected between this pin and the FB2 pin.                                                                                                                                                                                                                                                                                                                                                                                     |

| CS1   | 5   | I                   | Current sense amplifier input. Connect to the high side of the channel1 current sense resistor.                                                                                                                                                                                                                                                                                                                                                                                                                        |

| CS2   | 20  | I                   | Current sense amplifier input. Connect to the high side of the channel2 current sense resistor.                                                                                                                                                                                                                                                                                                                                                                                                                        |

| CSG1  | 4   | I                   | Kelvin ground connection to the external current sense resistor. Connect directly to the low side of the channel1 current sense resistor.                                                                                                                                                                                                                                                                                                                                                                              |

| CSG2  | 21  | I                   | Kelvin ground connection to the external current sense resistor. Connect directly to the low side of the channel2 current sense resistor.                                                                                                                                                                                                                                                                                                                                                                              |

| DEMB  | 17  | I                   | Logic input that enables diode emulation when in the low state. In diode emulation mode, the low-side MOSFET is latched off for the remainder of the PWM cycle when the buck inductor current reverses direction (current flow from output to ground). When DEMB is high, diode emulation is disabled allowing current to flow in either direction through the low-side MOSFET. A 50-k $\Omega$ pulldown resistor internal to the LM25119Q holds DEMB pin low and enables diode emulation if the pin is left floating. |

| EN2   | 11  | I                   | If the EN2 pin is low, channel2 is disabled. Channel1 and all other functions remain active. The EN2 has a $50$ -k $\Omega$ pullup resistor to enable channel2 when the pin is left floating.                                                                                                                                                                                                                                                                                                                          |

| FB1   | 9   | Ι                   | Feedback input and inverting input of the channel1 internal error amplifier. A resistor divider from the channel1 output to this pin sets the output voltage level. The regulation threshold at the FB1 pin is 0.8 V.                                                                                                                                                                                                                                                                                                  |

| FB2   | 16  | I                   | Feedback input and inverting input of the channel2 internal error amplifier. A resistor divider from the channel2 output to this pin sets the output voltage level. The regulation threshold at the FB2 pin is 0.8 V.                                                                                                                                                                                                                                                                                                  |

| HB1   | 30  | Р                   | High-side driver supply for bootstrap gate drive. Connect to the cathode of the channel1 external bootstrap diode and to the bootstrap capacitor. The bootstrap capacitor supplies current to charge the high-side MOSFET gate and must be placed as close to controller as possible.                                                                                                                                                                                                                                  |

(1) G = Ground, I = Input, O = Output, P = Power

## Pin Functions (continued)

| PI         | N   | TYPE <sup>(1)</sup> DESCRIPTION |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|------------|-----|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME       | NO. | TYPE."                          | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| HB2        | 27  | Р                               | High-side driver supply for bootstrap gate drive. Connect to the cathode of the channel2 external bootstrap diode and to the bootstrap capacitor. The bootstrap capacitor supplies current to charge the high-side MOSFET gate and must be placed as close to the controller as possible.                                                                                                                                                                                                                                                                                                                                                     |  |

| HO1        | 31  | 0                               | High-side MOSFET gate drive output. Connect to the gate of the channel1 high-side MOSFET through a short, low inductance path.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| HO2        | 26  | 0                               | High-side MOSFET gate drive output. Connect to the gate of the channel2 high-side MOSFET through a short, low inductance path.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| LO1        | 2   | 0                               | Low-side MOSFET gate drive output. Connect to the gate of the channel1 low-side synchronous MOSFET through a short, low inductance path.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| LO2        | 23  | 0                               | Low-side MOSFET gate drive output. Connect to the gate of the channel2 low-side synchronous MOSFET through a short, low inductance path.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| PGND1      | 3   | G                               | Power ground return pin for low-side MOSFET gate driver. Connect directly to the low side of the channel1 current sense resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| PGND2      | 22  | G                               | Power ground return pin for low-side MOSFET gate driver. Connect directly to the low side of the channel2 current sense resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| RAMP1      | 6   | I                               | PWM ramp signal. An external resistor and capacitor connected between the SW1 pin, the RAMP1 pin and the AGND pin sets the channel1 PWM ramp slope. Proper selection of component values produces a RAMP1 signal that emulates the current in the buck inductor.                                                                                                                                                                                                                                                                                                                                                                              |  |

| RAMP2      | 19  | I                               | PWM ramp signal. An external resistor and capacitor connected between the SW2 pin, the RAMP2 pin and the AGND pin sets the channel2 PWM ramp slope. Proper selection of component values produces a RAMP2 signal that emulates the current in the buck inductor.                                                                                                                                                                                                                                                                                                                                                                              |  |

| RES        | 14  | 0                               | The restart timer pin for an external capacitor that configures the hiccup mode current limiting. A capacitor on the RES pin determines the time the controller remains off before automatically restarting in hiccup mode. The two regulator channels operate independently. One channel may operate in normal mode while the other is in hiccup mode overload protection. The hiccup mode commences when either channel experiences 256 consecutive PWM cycles with cycle-by-cycle current limiting. After this occurs, a 10-µA current source charges the RES pin capacitor to the 1.25-V threshold which restarts the overloaded channel. |  |

| RT         | 13  | I                               | The internal oscillator is set with a single resistor between RT and AGND. The recommended maximum oscillator frequency is 1.5 MHz which corresponds to a maximum switching frequency of 750 kHz for either channel. The internal oscillator can be synchronized to an external clock by coupling a positive pulse into RT through a small coupling capacitor.                                                                                                                                                                                                                                                                                |  |

| SS1        | 7   | I                               | An external capacitor and an internal 10-μA current source set the ramp rate of the channel1 error amp reference. The SS1 pin is held low when VCC1 or VCC2 < 4 V, UVLO < 1.25 V or during thermal shutdown.                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| SS2        | 18  | I                               | An external capacitor and an internal 10-μA current source set the ramp rate of the channel2 error amp reference. The SS2 pin is held low when VCC1 or VCC2 < 4 V, UVLO < 1.25 V or during thermal shutdown.                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| SW1        | 32  | I/O                             | Switching node of the buck regulator. Connect to channel1 bootstrap capacitor, the source terminal of the high-side MOSFET and the drain terminal of the low-side MOSFET.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| SW2        | 25  | I/O                             | Switching node of the buck regulator. Connect to channel2 bootstrap capacitor, the source terminal of the high-side MOSFET and the drain terminal of the low-side MOSFET.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| UVLO       | 28  | I                               | Undervoltage lockout programming pin. If the UVLO pin is below 0.4 V, the regulator is in the shutdown mode with all function disabled. If the UVLO pin is greater than 0.4 V and below 1.25 V, the regulator is in standby mode with the VCC regulators operational, the SS pins grounded and no switching at the HO and LO outputs. If the UVLO pin voltage is above 1.25 V, the SS pins are allowed to ramp and pulse width modulated gate drive signals are delivered at the LO and HO pins. A 20-µA current source is enabled when UVLO exceeds 1.25 V and flows through the external UVLO resistors to provide hysteresis.              |  |

| VCCDIS     | 8   | I                               | Optional input that disables the internal VCC regulators when external biasing is supplied. If VCCDIS > 1.25 V, the internal VCC regulators are disabled. The externally supplied bias must be coupled to the VCC pins through a diode. VCCDIS has a 500-k $\Omega$ pulldown resistor to ground to enable the VCC regulators when the pin is left floating. The pulldown resistor can be overridden by pulling VCCDIS above 1.25 V with a resistor divider connected to the external bias supply.                                                                                                                                             |  |

| VIN        | 29  | Р                               | Supply voltage input source for the VCC regulators.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| Thermal Pa | ad  |                                 | Thermal pad of WQFN package. No internal electrical connections. Solder to the ground plane to reduce thermal resistance.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

## 7 Specifications

## 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                           | MIN  | MAX                    | UNIT |

|-------------------------------------------|------|------------------------|------|

| VIN to AGND                               | -0.3 | 45                     | V    |

| SW1, SW2 to AGND                          | -3   | 45                     | V    |

| HB1 to SW1, HB2 to SW2                    | -0.3 | 15                     | V    |

| VCC1, VCC2 to AGND <sup>(2)</sup>         | -0.3 | 15                     | V    |

| FB1, FB2, DEMB, RES, VCCDIS, UVLO to AGND | -0.3 | 15                     | V    |

| HO1 to SW1, HO2 to SW2                    | -0.3 | V <sub>HB</sub> + 0.3  | V    |

| LO1, LO2 to AGND                          | -0.3 | V <sub>VCC</sub> + 0.3 | V    |

| SS1, SS2 to AGND                          | -0.3 | 7                      | V    |

| EN2, RT to AGND                           | -0.3 | 7                      | V    |

| CS1, CS2, CSG1, CSG2 to AGND              | -0.3 | 0.3                    | V    |

| PGND to AGND                              | -0.3 | 0.3                    | V    |

| Junction temperature, T <sub>J</sub>      |      | 150                    | °C   |

| Storage temperature, T <sub>stg</sub>     | -55  | 150                    | °C   |

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) These pins must not exceed VIN.

## 7.2 ESD Ratings

|                                                  |                                                         |                                              | VALUE | UNIT |

|--------------------------------------------------|---------------------------------------------------------|----------------------------------------------|-------|------|

| V <sub>(ESD)</sub><br>Electrostatic<br>discharge | Human-body model (HBM), per AEC Q100-002 <sup>(1)</sup> | ±2000                                        | N/    |      |

| V(ESD)                                           | discharge                                               | Charged-device model (CDM), per AEC Q100-011 | ±750  | V    |

(1) AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

## 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                     | MIN | MAX | UNIT |

|-------------------------------------|-----|-----|------|

| VIN                                 | 4.5 | 42  | V    |

| VCC                                 | 4.5 | 14  | V    |

| HB to SW                            | 4.5 | 14  | V    |

| T <sub>J</sub> Junction temperature | -40 | 125 | °C   |

(1) COMP1, COMP2, RAMP1, and RAMP2 are output pins. As such they are not specified to have an external voltage applied.

|                       |                                              | LM25119Q   |      |

|-----------------------|----------------------------------------------|------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | RTV (WQFN) | UNIT |

|                       |                                              | 32 PINS    |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 36.7       | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 20.9       | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 9          | °C/W |

| ΨJT                   | Junction-to-top characterization parameter   | 0.2        | °C/W |

| ΨJB                   | Junction-to-board characterization parameter | 8.9        | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 2.2        | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

## 7.5 Electrical Characteristics

Typical values correspond to  $T_J = 25^{\circ}$ C. Minimum and maximum limits apply over  $-40^{\circ}$ C to  $125^{\circ}$ C junction temperature range. VIN = 36 V, VCC = 8 V, VCCDIS = 0 V, EN2 = 5 V,  $R_T = 25 \text{ k}\Omega$ , and no load on LO or HO (unless otherwise noted).

|                             | PARAMETER                   | TEST CONDITIONS                             | MIN <sup>(1)</sup> | TYP  | MAX <sup>(1)</sup> | UNIT |

|-----------------------------|-----------------------------|---------------------------------------------|--------------------|------|--------------------|------|

| VIN SUPPLY                  |                             |                                             |                    |      |                    |      |

|                             | VIN operating ourrept       | $V_{SS1} = V_{SS2} = 0 V$                   |                    | 6    | 7.3                | mA   |

| IBIAS                       | VIN operating current       | $V_{VCCDIS} = 2 V, V_{SS1} = V_{SS2} = 0 V$ |                    | 340  | 500                | μA   |

|                             | VCC1 operating current      | $V_{VCCDIS} = 2 V, V_{SS1} = V_{SS2} = 0 V$ |                    | 3.9  | 4.5                | mA   |

| Ivcc                        | VCC2 operating current      | $V_{VCCDIS} = 2 V, V_{SS1} = V_{SS2} = 0 V$ |                    | 1.4  | 2                  | mA   |

| <b>I<sub>SHUTDOWN</sub></b> | VIN shutdown current        | $V_{UVLO} = 0 V, V_{SS1} = V_{SS2} = 0 V$   |                    | 15   | 33                 | μA   |

| VCC REGULA                  | ATOR <sup>(2)</sup>         |                                             |                    |      |                    |      |

| N/                          |                             |                                             | 6.77               | 7.6  | 8.34               | V    |

| V <sub>CC(REG)</sub>        | VCC regulation              | $V_{IN}$ = 4.5 V, No external load          | 4.4                | 4.46 |                    | V    |

|                             | Sourcing current limit      | $V_{CC} = 0 V$                              | 25                 | 40   |                    | mA   |

|                             | VCCDIS switch threshold     | V <sub>VCCDIS</sub> rising                  | 1.19               | 1.25 | 1.29               | V    |

|                             | VCCDIS switch hysteresis    |                                             |                    | 0.07 |                    | V    |

|                             | VCCDIS input current        | V <sub>VCCDIS</sub> = 0 V                   |                    | -20  |                    | nA   |

|                             | Undervoltage threshold      | Positive going VCC                          | 3.8                | 4    | 4.2                | V    |

|                             | Undervoltage hysteresis     |                                             |                    | 0.2  |                    | V    |

| EN2 INPUT                   |                             |                                             |                    |      |                    |      |

| V <sub>IL</sub>             | EN2 input low threshold     |                                             |                    | 2    | 1.5                | V    |

| VIH                         | EN2 input high threshold    |                                             | 2.9                | 2.5  |                    | V    |

|                             | EN2 input pullup resistor   |                                             |                    | 50   |                    | kΩ   |

| UVLO                        |                             |                                             |                    |      |                    |      |

|                             | Threshold                   | UVLO rising                                 | 1.2                | 1.25 | 1.29               | V    |

|                             | Hysterisis current          | $V_{UVLO} = 1.4 V$                          | 15                 | 20   | 25                 | μA   |

|                             | Shutdown threshold          |                                             |                    | 0.4  |                    | V    |

|                             | Shutdown hysteresis voltage |                                             |                    | 0.1  |                    | V    |

| SOFT START                  |                             | •                                           | ,                  |      | ŀ                  |      |

|                             | Current source              | $V_{SS} = 0 V$                              | 7                  | 10   | 13                 | μA   |

|                             | Pulldown R <sub>DSON</sub>  |                                             |                    | 10   |                    | Ω    |

|                             |                             | 1                                           |                    |      |                    |      |

(1) Minimum and maximum limits are 100% production tested at 25°C. Limits over the operating temperature range are specified through correlation using Statistical Quality Control (SQC) methods. Limits are used to calculate Texas Instrument's Average Outgoing Quality Level (AOQL).

(2) Per VCC Regulator.

## **Electrical Characteristics (continued)**

Typical values correspond to  $T_J = 25^{\circ}$ C. Minimum and maximum limits apply over  $-40^{\circ}$ C to  $125^{\circ}$ C junction temperature range. VIN = 36 V, VCC = 8 V, VCCDIS = 0 V, EN2 = 5 V,  $R_T = 25 \text{ k}\Omega$ , and no load on LO or HO (unless otherwise noted).

|                      | PARAMETER                                         | TEST CONDITIONS                                                   | MIN <sup>(1)</sup> | TYP  | MAX <sup>(1)</sup> | UNIT   |

|----------------------|---------------------------------------------------|-------------------------------------------------------------------|--------------------|------|--------------------|--------|

| ERROR AMP            | PLIFIER                                           |                                                                   |                    |      |                    |        |

| V <sub>REF</sub>     | FB reference voltage                              | Measured at FB pin, FB = COMP                                     | 0.788              | 0.8  | 0.812              | V      |

|                      | FB input bias current                             | V <sub>FB</sub> = 0.8 V                                           |                    | 1    |                    | nA     |

|                      | FB disable threshold                              | Interleaved threshold                                             |                    | 2.5  |                    | V      |

|                      | COMP VOH                                          | I <sub>SOURCE</sub> = 3 mA                                        | 2.8                |      |                    | V      |

|                      | COMP VOL                                          | I <sub>SINK</sub> = 3 mA                                          |                    |      | 0.31               | V      |

| A <sub>OL</sub>      | DC gain                                           |                                                                   |                    | 80   |                    | dB     |

| f <sub>BW</sub>      | Unity gain bandwidth                              |                                                                   |                    | 3    |                    | MHz    |

| PWM COMP             |                                                   |                                                                   |                    |      |                    |        |

| t <sub>HO(OFF)</sub> | Forced HO OFF-time                                |                                                                   | 220                | 320  | 430                | ns     |

| t <sub>ON(min)</sub> | Minimum HO ON-time                                | C <sub>RAMP</sub> = 50 pF                                         |                    | 100  |                    | ns     |

| OSCILLATO            |                                                   |                                                                   |                    |      |                    |        |

| f <sub>SW1</sub>     | Frequency 1                                       | R <sub>T</sub> = 25 kΩ                                            | 180                | 200  | 220                | kHz    |

| f <sub>SW2</sub>     | Frequency 2                                       | $R_T = 10 \text{ k}\Omega$                                        | 430                | 480  | 530                | kHz    |

|                      | RT output voltage                                 |                                                                   |                    | 1.25 |                    | V      |

|                      | RT sync positive threshold                        | T <sub>J</sub> = 25°C                                             | 2.5                | 3.2  | 4                  | V      |

|                      | Sync pulse minimum width                          |                                                                   | 100                |      |                    | ns     |

| CURRENT L            | IMIT                                              |                                                                   |                    |      |                    |        |

| V <sub>CS(TH)</sub>  | Cycle-by-cycle sense voltage threshold (CS – CSG) | RAMP = 0                                                          | 106                | 120  | 134                | mV     |

|                      | CS bias current                                   | $V_{CS} = 0 V$                                                    |                    | -70  | -95                | μA     |

|                      | Hiccup mode fault timer                           |                                                                   |                    | 256  |                    | Cycles |

| RES                  |                                                   |                                                                   |                    |      |                    |        |

| I <sub>RES</sub>     | Current source                                    |                                                                   |                    | 9.7  |                    | μA     |

| V <sub>RES</sub>     | Threshold                                         | C <sub>RES</sub> charging                                         | 1.2                | 1.25 | 1.3                | V      |

| DIODE EMU            | LATION                                            |                                                                   |                    |      |                    |        |

| V <sub>IL</sub>      | DEMB input low threshold                          |                                                                   |                    | 2    | 1.65               | V      |

| V <sub>IH</sub>      | DEMB input high threshold                         |                                                                   | 2.9                | 2.6  |                    | V      |

|                      | DEMB input pulldown resistance                    |                                                                   |                    | 50   |                    | kΩ     |

|                      | SW zero cross threshold                           |                                                                   |                    | -5   |                    | mV     |

| LO GATE DE           | RIVER                                             |                                                                   |                    |      |                    |        |

| V <sub>OLL</sub>     | LO low-state output voltage                       | I <sub>LO</sub> = 100 mA                                          |                    | 0.1  | 0.18               | V      |

| V <sub>OHL</sub>     | LO high-state output voltage                      | $I_{LO} = -100 \text{ mA}, V_{OHL} = VCC - V_{LO}$                |                    | 0.17 | 0.26               | V      |

|                      | LO rise time                                      | C <sub>LOAD</sub> = 1000 pF                                       |                    | 6    |                    | ns     |

|                      | LO fall time                                      | C <sub>LOAD</sub> = 1000 pF                                       |                    | 5    |                    | ns     |

| I <sub>OHL</sub>     | Peak LO source current                            | $V_{LO} = 0 V$                                                    |                    | 2.5  |                    | А      |

| I <sub>OLL</sub>     | Peak LO sink current                              | V <sub>LO</sub> = VCC                                             |                    | 3.3  |                    | А      |

| HO GATE D            | RIVER                                             |                                                                   |                    |      |                    |        |

| V <sub>OLH</sub>     | HO low-state output voltage                       | I <sub>HO</sub> = 100 mA                                          |                    | 0.11 | 0.19               | V      |

| V <sub>OHH</sub>     | HO high-state output voltage                      | $I_{HO} = -100 \text{ mA}, V_{OHH} = V_{HB} - V_{HO}$             |                    | 0.18 | 0.27               | V      |

|                      | HO rise time                                      | C <sub>LOAD</sub> = 1000 pF                                       |                    | 6    |                    | ns     |

|                      | HO fall time                                      | C <sub>LOAD</sub> = 1000 pF                                       |                    | 5    |                    | ns     |

| I <sub>OHH</sub>     | Peak HO Source current                            | V <sub>HO</sub> = 0 V, V <sub>SW</sub> = 0, V <sub>HB</sub> = 8 V |                    | 2.2  |                    | А      |

| I <sub>OLH</sub>     | Peak HO sink current                              | $V_{HO} = V_{HB} = 8 V$                                           |                    | 3.3  |                    | А      |

|                      | HB to SW undervoltage                             |                                                                   |                    | 3    |                    | V      |

## **Electrical Characteristics (continued)**

Typical values correspond to  $T_J = 25^{\circ}$ C. Minimum and maximum limits apply over  $-40^{\circ}$ C to  $125^{\circ}$ C junction temperature range. VIN = 36 V, VCC = 8 V, VCCDIS = 0 V, EN2 = 5 V,  $R_T = 25 \text{ k}\Omega$ , and no load on LO or HO (unless otherwise noted).

|                 |                              |                         | ,<br>,             |     |                    | ,    |

|-----------------|------------------------------|-------------------------|--------------------|-----|--------------------|------|

|                 | PARAMETER                    | TEST CONDITIONS         | MIN <sup>(1)</sup> | TYP | MAX <sup>(1)</sup> | UNIT |

|                 | HB DC bias current           | $V_{HB} - V_{SW} = 8 V$ |                    | 70  | 100                | μA   |

| THERMAL         |                              |                         | •                  |     |                    |      |

| T <sub>SD</sub> | Thermal shutdown             | Rising                  |                    | 165 |                    | °C   |

|                 | Thermal shutdown hysteresis  |                         |                    | 25  |                    | °C   |

|                 | I hermal shutdown hysteresis |                         |                    | 25  |                    | Ů    |

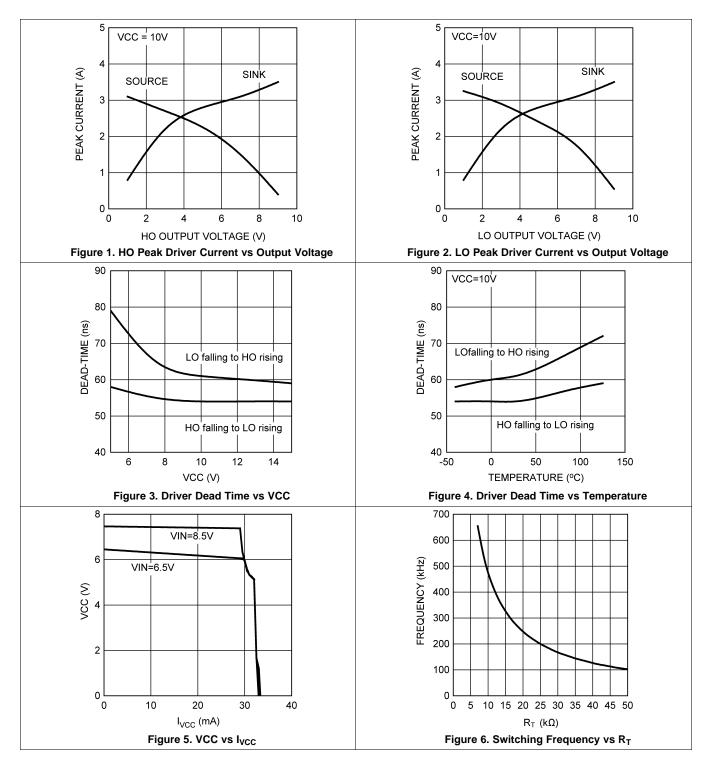

## 7.6 Switching Characteristics

Typical values correspond to  $T_J = 25^{\circ}$ C. Minimum and maximum limits apply over -40°C to 125°C junction temperature range.  $V_{IN} = 36$  V,  $V_{CC} = 8$  V,  $V_{VCCDIS} = 0$  V,  $V_{EN2} = 5$  V,  $R_T = 25$  k $\Omega$ , and no load on LO or HO (unless otherwise noted).

| PARAMETER                | TEST CONDITIONS | MIN | TYP MAX | UNIT |

|--------------------------|-----------------|-----|---------|------|

| LO fall to HO rise delay | No load         |     | 70      | ns   |

| HO fall to LO rise delay | No load         |     | 60      | ns   |

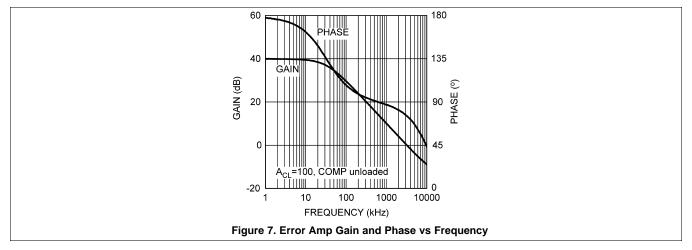

## 7.7 Typical Characteristics

## **Typical Characteristics (continued)**

## 8 Detailed Description

### 8.1 Overview

The LM25119 high voltage switching regulator features all of the functions necessary to implement an efficient dual-channel buck regulator that operates over a very wide input voltage range. The LM25119 may be configured as two independent regulators or as a single high-current regulator with two interleaved channels. This easy-to-use regulator integrates high-side and low-side MOSFET drivers capable of supplying peak currents of 2.5 A (VCC = 8 V). The regulator control method is based on current mode control using an emulated current ramp. Emulated peak current mode control provides inherent line feedforward, cycle-by-cycle current limiting and ease-of-loop compensation. The use of an emulated control ramp reduces noise sensitivity of the pulse-width modulation circuit, allowing reliable processing of the very small duty cycles necessary in high input voltage applications. The switching frequency is user programmable from 50 kHz to 750 kHz. An oscillator or synchronization pin allows the operating frequency to be set by a single resistor or synchronized to an external clock. An undervoltage lockout and channel2 enable pin allows either both regulators to be disabled or channel2 to be disabled with full operation of channel1. Fault protection features include current limiting, thermal shutdown and remote shutdown capability. The undervoltage lockout input enables both channels when the input voltage reaches a user selected threshold and provides a very low quiescent shutdown current when pulled low. The 32-pin WQFN package features an exposed pad to aid in thermal dissipation.

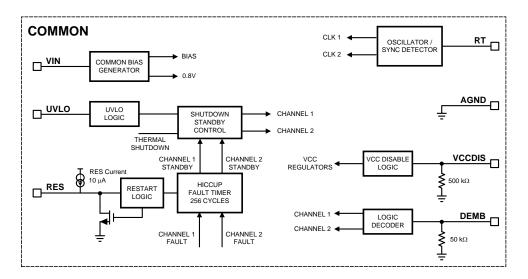

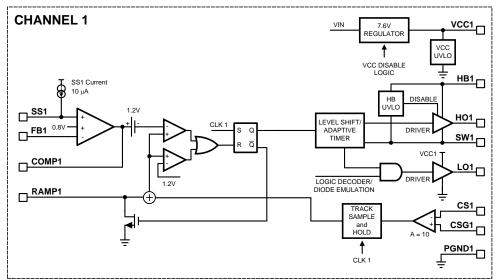

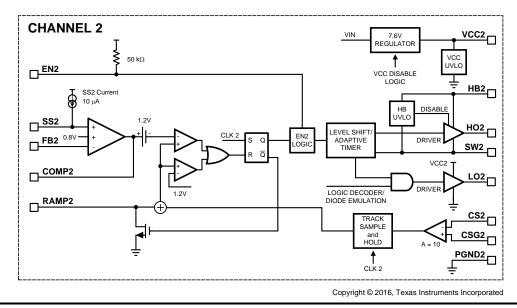

#### 8.2 Functional Block Diagram

### 8.3 Feature Description

#### 8.3.1 High Voltage Start-Up Regulator

The LM25119 contains two internal high voltage bias regulators, VCC1 and VCC2, that provide the bias supply for the PWM controllers and gate drive for the MOSFETs of each regulator channel. The input pin (VIN) can be connected directly to an input voltage source as high as 42 V. The outputs of the VCC regulators are set to 7.6 V. When the input voltage is below the VCC set-point level, the VCC output tracks the VIN with a small dropout voltage. If VCC1 is in an undervoltage condition, channel2 is disabled. This interdependence is necessary to prevent channel2 from running open-loop in the single output interleaved mode when the channel2 error amplifier is disabled (if either VCC is in UV, both channels are disabled).

The outputs of the VCC regulators are current limited at 25-mA (minimum) output capability. Upon power up, the regulators source current into the capacitors connected to the VCC pins. When the voltage at the VCC pins exceed 4 V and the UVLO pin is greater than 1.25 V, both channels are enabled and a soft-start sequence begins. Both channels remain enabled until either VCC pin falls below 3.8 V, the UVLO pin falls below 1.25 V or the die temperature exceeds the thermal limit threshold.

When operating at higher input voltages the bias power dissipation within the controller can be excessive. An output voltage derived bias supply can be applied to a VCC pins to reduce the IC power dissipation. The VCCDIS input can be used to disable the internal VCC regulators when external biasing is supplied. If VCCDIS > 1.25 V, the internal VCC regulators are disabled. The externally supplied bias must be coupled to the VCC pins through a diode, preferably a Schottky (low forward voltage). VCCDIS has a 500-k $\Omega$  internal pulldown resistance to ground for normal operation with no external bias. The internal pulldown resistance can be overridden by pulling VCCDIS above 1.25 V through a resistor divider connected to an external bias supply.

The VCC regulator series pass transistor includes a diode between VCC and VIN that must not be forwardbiased in normal operation.

If the external bias winding can supply VCC greater than VIN, an external blocking diode is required from the input power supply to the VIN pin to prevent the external bias supply from passing current to the input supply through the VCC pins. For VOUT between 5 V and 14.5 V, VOUT can be connected directly to VCC through a diode. For VOUT < 5 V, a bias winding on the output inductor can be added as shown in Figure 8.

Figure 8. VCC Bias Supply With Additional Inductor Winding

In high voltage applications, take extra care to ensure the VIN pin does not exceed the absolute maximum voltage rating of 45 V. During line or load transients, voltage ringing on the VIN line that exceeds the absolute maximum rating can damage the IC. Both careful PCB layout and the use of quality bypass capacitors located close to the VIN and AGND pins are essential.

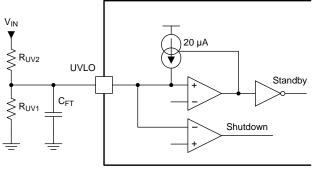

#### 8.3.2 UVLO

The LM25119 contains a dual-level undervoltage lockout (UVLO) circuit. When the UVLO pin is less than 0.4 V, the LM25119 is in shutdown mode. The shutdown comparator provides 100 mV of hysteresis to avoid chatter during transitions. When the UVLO pin voltage is greater than 0.4 V but less than 1.25 V, the controller is in standby mode. In the standby mode the VCC bias regulators are active but the controller outputs are disabled. This feature allows the UVLO pin to be used as a remote enable or disable function. When the VCC outputs exceed their respective undervoltage thresholds (4 V) and the UVLO pin voltage is greater than 1.25 V, the outputs are enabled and normal operation begins.

#### **Feature Description (continued)**

An external set-point voltage divider from the VIN to GND is used to set the minimum VIN operating voltage of the regulator. The divider must be designed such that the voltage at the UVLO pin is greater than 1.25 V when the input voltage is in the desired operating range. UVLO hysteresis is accomplished with an internal  $20-\mu$ A current source that is switched on or off into the impedance of the set-point divider. When the UVLO pin voltage exceeds 1.25-V threshold, the current source is activated to quickly raise the voltage at the UVLO pin. When the UVLO pin voltage falls below the 1.25-V threshold, the current source is turned off causing the voltage at the UVLO pin to quickly fall. The UVLO pin must not be left floating.

#### 8.3.3 Enable 2

The LM25119 contains an enable function allowing shutdown control of channel2, independent of channel1. If the EN2 pin is pulled below 2 V, channel2 enters shutdown mode. If the EN2 input is greater than 2.5 V, channel2 returns to normal operation. An internal 50-k $\Omega$  pullup resistor on the EN2 pin allows this pin to be left floating for normal operation. The EN2 input can be used in conjunction with the UVLO pin to sequence the two regulator channels. If EN2 is held low as the UVLO pin increases to a voltage greater than the 1.25-V UVLO threshold, channel1 begins operation while channel2 remains off. Both channels become operational when the UVLO, EN2, VCC1, and VCC2 pins are above their respective operating thresholds. Either channel of the LM25119 can also be disabled independently by pulling the corresponding SS pin to AGND.

#### 8.3.4 Oscillator and Sync Capability

The LM25119 switching frequency is set by a single external resistor connected between the RT pin and the AGND pin ( $R_T$ ). The resistor must be located very close to the device and connected directly to the pins of the IC (RT and AGND). To set a desired switching frequency ( $f_{SW}$ ) of each channel, the resistor can be calculated with Equation 1.

$$\mathsf{R}_{\mathsf{T}} = \frac{5.2 \times 10^9}{\mathsf{f}_{\mathsf{SW}}} - 948$$

where

- RT is in ohms (Ω)

- f<sub>SW</sub> is in hertz (Hz)

(1)

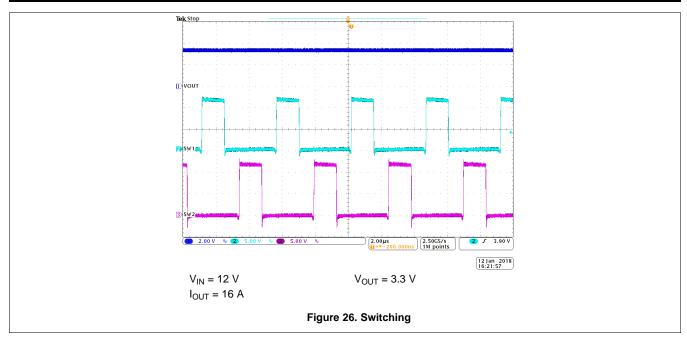

The frequency  $f_{SW}$  is the output switching frequency of each channel. The internal oscillator runs at twice the switching frequency and an internal frequency divider interleaves the two channels with 180° phase shift between PWM pulses at the HO pins.

The RT pin can be used to synchronize the internal oscillator to an external clock. The internal oscillator can be synchronized by AC coupling a positive edge into the RT pin. The voltage at the RT pin is nominally 1.25 V and the voltage at the RT pin must exceed 4 V to trip the internal synchronization pulse detector. A 5-V amplitude signal and 100-pF coupling capacitor are recommended. Synchronizing at greater than twice the free-running frequency may result in abnormal behavior of the pulse width modulator. Also, note that the output switching frequency of each channel is one-half the applied synchronization frequency.

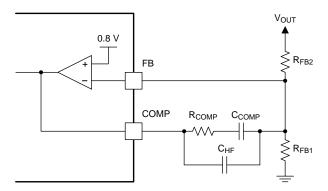

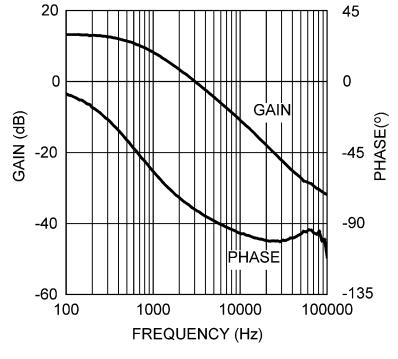

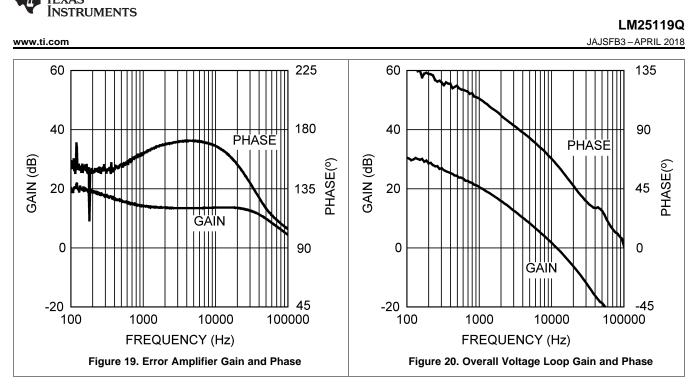

#### 8.3.5 Error Amplifiers and PWM Comparators

Each of the two internal high-gain error amplifiers generates an error signal proportional to the difference between the regulated output voltage and an internal precision reference (0.8 V). The output of each error amplifier is connected to the COMP pin allowing the user to provide loop compensation components. Generally a Type II network is recommended. This network creates a pole at 0 Hz, a mid-band zero, and a noise-reducing, high-frequency pole. The PWM comparator compares the emulated current sense signal from the RAMP generator to the error amplifier output voltage at the COMP pin. Only one error amplifier is required when configuring the controller as a two channel, single output interleaved regulator. For these applications, the channel1 error amplifier (FB1, COMP1) is configured as the master error amplifier. The channel2 error amplifier must be disabled by connecting the FB2 pin to the VCC2 pin. When configured in this manner the output of the channel2 error amplifier (COMP2) is disabled and have a high output impedance. To complete the interleaved configuration, the COMP1 and the COMP2 pins must be connected together to facilitate PWM control of channel2 and current sharing between channels.

### Feature Description (continued)

#### 8.3.6 Ramp Generator

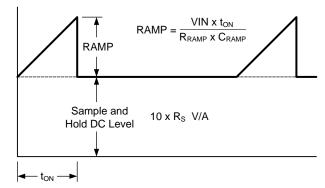

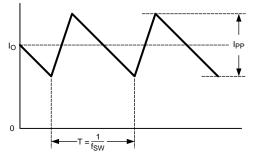

The ramp signal used in the pulse width modulator for current mode control is typically derived directly from the buck switch current. This switch current corresponds to the positive slope portion of the inductor current. Using this signal for the PWM ramp simplifies the control loop transfer function to a single pole response and provides inherent input voltage feedforward compensation. The disadvantage of using the buck switch current signal for PWM control is the large leading edge spike due to circuit parasitics that must be filtered or blanked. Also, the current measurement may introduce significant propagation delays. The filtering, blanking time, and propagation delay limit the minimum achievable pulse width. In applications where the input voltage may be relatively large in comparison to the output voltage, controlling small pulse widths and duty cycles are necessary for regulation. The LM25119 uses a unique ramp generator which does not actually measure the buck switch current but rather reconstructs the signal. Representing or emulating the inductor current provides a ramp signal to the PWM comparator that is free of leading edge spikes and measurement or filtering delays. The current reconstruction is comprised of two elements; a sample-and-hold DC level and the emulated inductor current ramp as shown in Figure 9.

Figure 9. Composition of Current Sense Signal

The sample-and-hold DC level is derived from a measurement of the recirculating current flowing through the current sense resistor. The voltage across the sense resistor is sampled and held just prior to the onset of the next conduction interval of the buck switch. The current sensing and sample-and-hold provide the DC level of the reconstructed current signal. The positive slope inductor current ramp is emulated by an external capacitor connected from RAMP pin to AGND and a series resistor connected between SW and RAMP. The ramp resistor must not be connected to VIN directly because the RAMP pin voltage rating could be exceeded under high VIN conditions. The ramp created by the external resistor and capacitor has a slope proportional to the rising inductor current plus some additional slope required for slope compensation. Connecting the RAMP pin resistor to SW provides optimum slope compensation with a RAMP capacitor slope that is proportional to VIN. This *adaptive slope compensation* eliminates the requirement for additional slope compensation circuitry with high output voltage set points and frees the user from additional concerns in this area. The emulated ramp signal is approximately linear and the ramp slope is given in Equation 2.

$$\frac{dV_{RAMP}}{dt} = \frac{10 \times K \times V_{IN} \times R_S}{L}$$

(2)

The factor of 10 Equation 2 corresponds to the internal current sense amplifier gain of the LM25119. The K factor is a constant which adds additional slope for robust pulse-width modulation control at lower input voltages. In practice this constant can be varied from 1 to 3.  $R_s$  is the external sense resistor value.

The voltage on the ramp capacitor is given with Equation 3 and Equation 4.

$$V_{RAMP} = V_{IN} \times \left(1 - e \frac{t_{PERIOD}}{R_{RAMP} \times C_{RAMP}}\right)$$

(3)

$$V_{RAMP} \approx \frac{V_{IN} \times t_{PERIOD}}{R_{RAMP} \times C_{RAMP}}$$

(4)

The approximation is the first order term in a Taylor Series expansion of the exponential and is valid because t<sub>PERIOD</sub> is small relative to the RAMP pin R-C time constant.

#### Feature Description (continued)

ı.

Multiplying Equation 2 by  $t_{PERIOD}$  to convert the slope to a peak voltage, and then equating Equation 2 with Equation 4 allows us to solve for  $C_{RAMP}$  using Equation 5.

$$C_{\text{RAMP}} = \frac{L}{10 \times R_{\text{S}} \times K \times R_{\text{RAMP}}}$$

(5)

Choose either C<sub>RAMP</sub> or R<sub>RAMP</sub> and use Equation 5 to calculate the other component.

The difference between the average inductor current and the DC value of the sampled inductor current can cause instability for certain operating conditions. This instability is known as sub-harmonic oscillation, which occurs when the inductor ripple current does not return to its initial value by the start of next switching cycle. Sub-harmonic oscillation is normally characterized by alternating wide and narrow pulses at the switch node. The ramp equation above contains the optimum amount of slope compensation, however extra slope compensation is easily added by selecting a lower value for  $R_{RAMP}$  or  $C_{RAMP}$ .

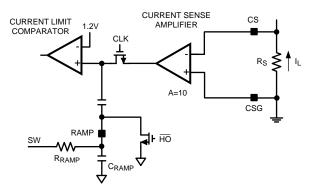

#### 8.3.7 Current Limit

The LM25119 contains a current limit monitoring scheme to protect the regulator from possible overcurrent conditions. When set correctly, the emulated current signal is proportional to the buck switch current with a scale factor determined by the current limit sense resistor, R<sub>S</sub>, and current sense amplifier gain. The emulated signal is applied to the current limit comparator. If the emulated ramp signal exceeds 1.2 V, the present cycle is terminated (cycle-by-cycle current limiting). Shown in Figure 10 is the current limit comparator and a simplified current measurement schematic. In applications with small output inductance and high input voltage, the switch current may overshoot due to the propagation delay of the current limit comparator. If an overshoot must occur, the sample-and-hold circuit detects the excess recirculating current before the buck switch is turned on again. If the sample-and-hold DC level exceeds the internal current limit threshold, the buck switch is disabled and skip pulses until the current has decayed below the current limit threshold. This approach prevents current runaway conditions due to propagation delays or inductor saturation because the inductor current is forced to decay to a controlled level following any current overshoot.

Figure 10. Current Limit and Ramp Circuit

#### 8.3.8 Hiccup Mode Current Limiting

To further protect the regulator during prolonged current limit conditions, an internal counter counts the PWM clock cycles during which cycle-by-cycle current limiting occurs. When the counter detects 256 consecutive cycles of current limiting, the regulator enters a low power dissipation hiccup mode with the HO and LO outputs disabled. The restart timer pin, RES, and an external capacitor configure the hiccup mode current limiting. A capacitor on the RES pin ( $C_{RES}$ ) determines the time the controller remains in low power standby mode before automatically restarting. A 10-µA current source charges the RES pin capacitor to the 1.25-V threshold which restarts the overloaded channel. The two regulator channels operate independently. One channel may operate normally while the other is in the hiccup mode overload protection. The hiccup mode commences when either channel experiences 256 consecutive PWM cycles with cycle-by-cycle current limiting. If that occurs, the overloaded channel turns off and remains off for the duration of the RES pin timer.

The hiccup mode current-limiting function can be disabled. The RES configuration is latched during initial power up when UVLO is above 1.25 V and VCC1 and VCC2 are above their UV thresholds, determining hiccup or non-hiccup current limiting. If the RES pin is tied to VCC at initial power on, hiccup current limit is disabled.

## **Feature Description (continued)**

#### 8.3.9 Soft Start

The soft-start feature allows the regulator to gradually reach the steady-state operating point, thus reducing startup stresses and surges. The LM25119 regulates the FB pin to the SS pin voltage or the internal 0.8-V reference, whichever is lower. At the beginning of the soft-start sequence when SS = 0 V, the internal 10- $\mu$ A soft-start current source gradually increases the voltage on an external soft-start capacitor (C<sub>SS</sub>) connected to the SS pin resulting in a gradual rise of the FB and output voltages.

Either regulator channel of the LM25119 can be disabled by pulling the corresponding SS pin to AGND.

#### 8.3.10 HO and LO Output Drivers

The LM25119 contains a high-current, high-side driver and associated high voltage level shift to drive the buck switch of each regulator channel. This gate driver circuit works in conjunction with an external diode and bootstrap capacitor. A 0.1  $\mu$ F or larger ceramic capacitor, connected with short traces between the HB pin and SW pin, is recommended. During the OFF-time of the high-side MOSFET, the SW pin voltage is approximately 0 V and the bootstrap capacitor charges from VCC through the external bootstrap diode. When operating with a high PWM duty cycle, the buck switch is forced off each cycle for 320 ns to ensure that the bootstrap capacitor is recharged.

The LO and HO outputs are controlled with an adaptive dead-time methodology which insures that both outputs are never enabled at the same time. When the controller commands HO to be enabled, the adaptive dead-time logic first disables LO and waits for the LO voltage to drop. HO is then enabled after a small delay. Similarly, the LO turnon is disabled until the HO voltage has discharged. This methodology insures adequate dead-time for any size MOSFET.

Exercise care in selecting an output MOSFET with the appropriate threshold voltage, especially if VCC is supplied from the regulator output. During start-up at low input voltages the MOSFET threshold must be lower than the 4-V VCC undervoltage lockout threshold. Otherwise, there may be insufficient VCC voltage to completely turn on the MOSFET as VCC undervoltage lockout is released during start-up. If the buck switch MOSFET gate drive is not sufficient, the regulator may not start or it may hang up momentarily in a high power dissipation state. This condition can be avoided by selecting a MOSFET with a lower threshold voltage or if VCC is supplied from an external source higher than the output voltage. If the minimum input voltage programmed by the UVLO pin resistor divider is above the VCC regulation level, this precaution is of no concern.

#### 8.3.11 Maximum Duty Cycle

When operating with a high PWM duty cycle, the buck switch is forced off each cycle for 320 ns to ensure the bootstrap capacitor is recharged and to allow time to sample and hold the current in the low-side MOSFET. This forced OFF-time limits the maximum duty cycle of the controller. When designing a regulator with high switching frequency and high duty cycle requirements, make sure to check the required maximum duty cycle (including losses) against the graph shown in Figure 11.

The actual maximum duty cycle varies with the operating frequency in Equation 6.

$$D_{MAX} = 1 - f_{SW} \times 320 \times 10^{-9}$$

0.95 0.90 0.90 0.85 0.80 0.75 0.70 0.00 200 300 400 500 600 FREQUENCY (kHz)

Figure 11. Maximum Duty Cycle vs Switching Frequency

(6)

#### Feature Description (continued)

#### 8.3.12 Thermal Protection

Internal thermal shutdown circuitry is provided to protect the integrated circuit in the event the maximum junction temperature is exceeded. When activated, typically at 165°C, the controller is forced into a low-power reset state, disabling the output driver and the VCC bias regulators. This feature is designed to prevent catastrophic failures from overheating and destroying the device.

### 8.4 Device Functional Modes

#### 8.4.1 Diode Emulation

A fully synchronous buck regulator implemented with a free-wheel MOSFET rather than a diode has the capability to sink current from the output in certain conditions such as light load, overvoltage, or prebias start-up. The LM25119Q device provides a diode emulation feature that can be enabled to prevent reverse (drain to source) current flow in the low-side, free-wheel MOSFET. When configured for diode emulation, the low-side MOSFET is disabled when reverse current flow is detected. The benefit of this configuration is lower power loss at no load or light load conditions and the ability to turn on into a prebiased output without discharging the output. The diode emulation mode allows for start-up into prebiased loads, because it prevents reverse current flow as the soft-start capacitor charges to the regulation level during start-up. The negative effect of diode emulation is degraded light load transient response times. Enabling the diode emulation feature is recommended and allows discontinuous conduction operation. The diode emulation feature is configured with the DEMB pin. To enable diode emulation, connect the DEMB pin to ground or leave the pin floating. If continuous conduction operation is desired, the DEMB pin must be tied to either VCC1 or VCC2.

TEXAS INSTRUMENTS

www.ti.com

## 9 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

### 9.1 Application Information

#### 9.1.1 Miscellaneous Functions

EN2 is left floating which allows channel2 to always remain enabled. If EN2 is pulled below 2 V, channel2 is disabled.

The DEMB pin is left floating because the design sample uses diode emulation. For fully synchronous (continuous conduction) operation, connect the DEMB to a voltage greater than 2.6 V.

VCCDIS is left floating to enable the internal VCC regulators. To disable the internal VCC regulators, connect this pin to a voltage greater than 1.25 V.

#### 9.1.2 Interleaved Two-Phase Operation

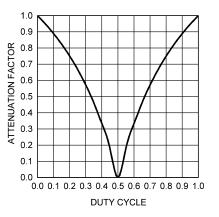

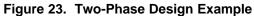

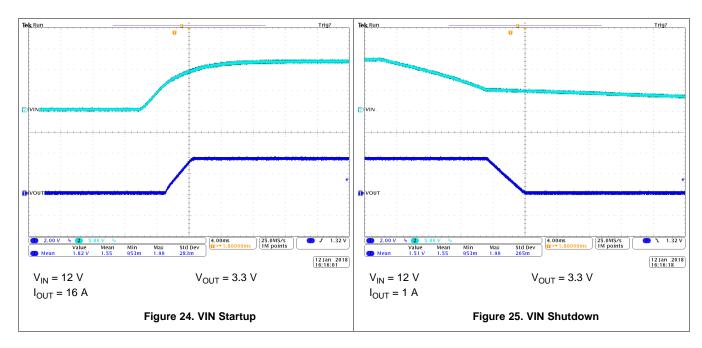

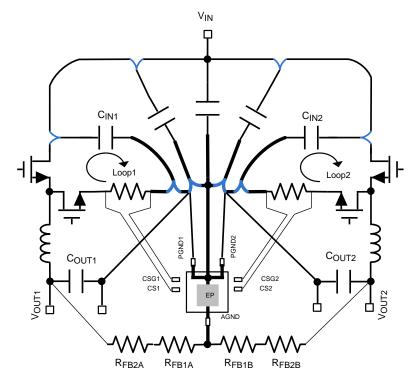

Interleaved operation offers many advantages in single-output, high-current applications. The output power path is split between two identical channels reducing the current in each channel by one-half. Ripple current reduction in the output capacitors is reduced significantly because each channel operates 180 degrees out of phase from the other. Ripple reduction is greatest at 50% duty cycle and decreases as the duty cycle varies away from 50%.

Refer to Figure 12 to estimate the ripple current reduction. Also, the effective ripple in the input and output capacitors occurs at twice the frequency of a single-channel design due to the combining of the two channels. All of these factors are advantageous in managing the higher currents and their effects in a high power design.

Figure 12. Cancellation Factor vs Duty Cycle for Output Capacitor

To begin an interleaved design, use the previous equations in this datasheet to first calculate the required value of components using one-half the current in the output power path. The attenuation factor in Figure 12 is the ratio of the output capacitor ripple to the inductor ripple versus duty cycle. The inductor ripple used in this calculation is the ripple in either inductor in a two phase design, not the ripple calculated for a single phase design of the same output power. It can be observed that operation around 50% duty cycle results in almost complete ripple attenuation in the output capacitor. Figure 12 can be used to calculate the amount of ripple attenuation in the output capacitors.

## **Application Information (continued)**

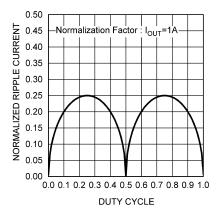

Figure 13. Normalized Input Capacitor RMS Ripple Current vs Duty Cycle

Figure 13 illustrates the ripple current reduction in the input capacitors due to interleaving. As with the output capacitors, there is near perfect ripple reduction near 50% duty cycle. This plot can be used to calculate the ripple in the input capacitors at any duty cycle. In designs with large duty cycle swings, use the worst-case ripple reduction for the design.

To configure the LM25119Q device for interleaved operation, connect COMP1 and COMP2 pins together at the IC. Connecting the FB2 pin to VCC2 pin disables the channel2 error amplifier with a high output impedance at COMP2. Connect the compensation network between FB1 and the common COMP pins. Connect the two power stages together at the output capacitors. Finally use the plots in Figure 12 and Figure 13 along with the duty cycle range to determine the amount of output and input capacitor ripple reduction. Frequently more capacitance than necessary is used in a design just to meet ESR requirements. Reducing the capacitance based solely on ripple reduction graphs alone may violate this requirement.

#### 9.1.3 Interleaved 4-Phase Operation

Two LM25119Q devices can be designed for 4-phase operation with below configurations. The VCC shutdown and thermal shutdown on master device will shut down all four channels eventually by pulling down COMP bus. The VCC shutdown and thermal shutdown on slave device will only shut down the device under fault.

- To synchronize two devices and achieve phase shift, a 90 degree shifted clock should be applied to RT pins of master and slave devices

- Connect COMP pins of master and slave channels together.

- Connect FB pin of slave channel to local VCC pin.

- Connect RES pin to local VCC pin. This means hiccup model should be disabled.

- Connect all UVLO pins of master and slave channels together. This means the UVLO hysteresis current will be 4 times of 20-μA.

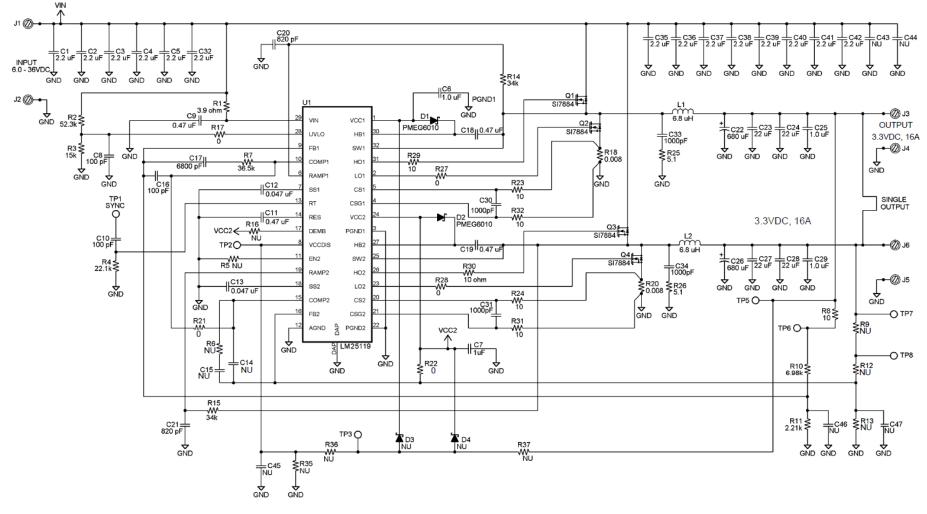

## 9.2 Typical Applications

LM25119Q JAJSFB3-APRIL 2018

## 9.2.1 Dual-output Design Example

Figure 14. 3.3-V 8-A, 1.8-V 8-A Dual-Output Application

#### 9.2.1.1 Design Requirements

#### 9.2.1.1.1 External Components

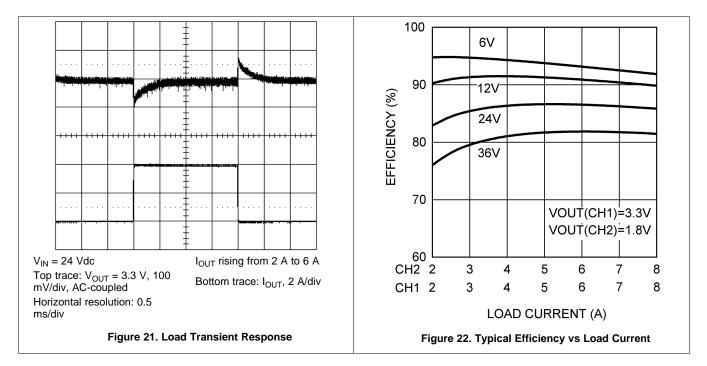

The procedure for calculating the external components is illustrated with the following design example. Only the values for the 3.3 V output are calculated because the procedure is the same for the 1.8-V output. The circuit shown in Figure 14 is configured for the following specifications:

- CH1 output voltage, V<sub>OUT1</sub> = 3.3 V

- CH2 output voltage, V<sub>OUT2</sub> = 1.8 V

- CH1 maximum load current, I<sub>OUT1</sub> = 8 A

- CH2 maximum load current, I<sub>OUT2</sub> = 8 A

- Minimum input voltage, V<sub>IN(min)</sub> = 6 V

- Maximum input voltage, V<sub>IN(max)</sub> = 36 V

- Switching frequency,  $f_{SW} = 230$  kHz

Some component values were chosen as a compromise between the 3.3-V and 1.8-V outputs to allow identical components to be used on both outputs. This design can be reconfigured in a dual-channel interleaved configuration with a single 3.3-V output which requires identical power channels.

#### 9.2.1.2 Detailed Design Procedure

#### 9.2.1.2.1 Timing Resistor

$R_T$  sets the switching frequency of each regulator channel. Generally, higher frequency applications are smaller but have higher losses. Operation at 230 kHz was selected for this example as a reasonable compromise between small size and high efficiency. The value of  $R_T$  for 230-kHz switching frequency is calculated with Equation 7.

$$R_{\rm T} = \frac{5.2 \times 10^9}{f_{\rm SW}} - 948 = 21.66 \, \rm k\Omega$$

<sup>(7)</sup>