Order Folder Now

LM324-N-MIL

JAJSDC6-JUNE 2017

# LM324-N-MIL 低消費電力クワッド・オペアンプ

## 特長

- ユニティ・ゲインのため内部的に周波数を補償

- 大きなDC電圧ゲイン: 100dB

- 広い帯域幅(ユニティ・ゲイン): 1MHz (温度補償後)

- 広い電源電圧範囲:

- 単一電源3V~32V

- またはデュアル電源±1.5V~±16V

- 非常に低い電源消費電流: 700µA

- 本質的に電源電圧の値には無関係

- 低い入力バイアス電流: 45nA (温度補償後)

- 低い入力オフセット電圧: 2mV およびオフセット電流: 5nA

- 入力同相電圧範囲にグランドを含む

- 差動入力電圧範囲は電源電圧に等しい

- 大きな出力電圧スイング: 0V~V+ 1.5V

- 利点

- デュアル電源が不要

- 4つの内部補償オペアンプを単一のパッケージに

- 直接GNDレベル近くまでセンシング可能、Vour もGNDレベルまで遷移可能

- すべての形式のロジックと互換

- バッテリ動作に適した消費電力

- リニア・モードでは、入力同相電圧範囲にグランド および出力電圧を含む

- 単一の電源電圧で動作しながら、グランドまでスイ ング可能

- ユニティ・ゲインのクロス周波数を温度補償

- 入力バイアス電流も温度補償

## 2 アプリケーション

- トランスデューサ・アンプ

- DCゲイン・ブロック

- 従来型のオペアンプ回路

## 3 概要

LM324-N-MILデバイスは4つの独立した高ゲインの内部 周波数補償付きオペアンプで構成され、単一の電源か ら、広い電圧範囲で動作するよう設計されています。分割 電源からも動作でき、低消費電力で、電源からの消費電 流は電源電圧の大きさに依存しません。

応用分野として、トランスデューサ・アンプ、DCゲイン・ブ ロック、各種の従来型オペアンプ回路があり、これらを単 一の電源システムで、より簡単に実装できます。たとえば、 LM324-N-MILデバイスは、デジタル・システムで使用され る標準の5V電源電圧で直接動作し、追加の±15V電源の 必要なしに、必要なインターフェイス電子回路を簡単に提 供できます。

## 製品情報(1)

| 型番          | パッケージ      | 本体サイズ(公称)       |

|-------------|------------|-----------------|

|             | CDIP (14)  | 19.56mm×6.67mm  |

| LM324-N-MIL | PDIP (14)  | 19.177mm×6.35mm |

|             | SOIC (14)  | 8.65mm×3.91mm   |

|             | TSSOP (14) | 5.00mm×4.40mm   |

(1) 利用可能なすべてのパッケージについては、このデータシートの末 尾にある注文情報を参照してください。

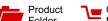

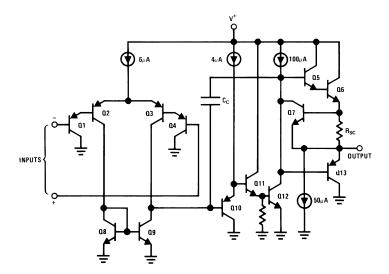

## 回路図

# 目次

| 1 | 特長1                                  | 7.4 Device Functional Modes 8       |

|---|--------------------------------------|-------------------------------------|

| 2 | アプリケーション1                            | 8 Application and Implementation 10 |

| 3 | 概要1                                  | 8.1 Application Information 10      |

| 4 | 改訂履歴2                                | 8.2 Typical Applications 10         |

| 5 | Pin Configuration and Functions      | 9 Power Supply Recommendations 20   |

| 6 | Specifications4                      | 10 Layout 20                        |

| • | 6.1 Absolute Maximum Ratings 4       | 10.1 Layout Guidelines              |

|   | 6.2 ESD Ratings                      | 10.2 Layout Example                 |

|   | 6.3 Recommended Operating Conditions | 11 デバイスおよびドキュメントのサポート               |

|   | 6.4 Thermal Information              | 11.1 ドキュメントの更新通知を受け取る方法21           |

|   | 6.5 Electrical Characteristics 5     | 11.2 コミュニティ・リソース21                  |

|   | 6.6 Typical Characteristics          | 11.3 商標21                           |

| 7 | Detailed Description 8               | 11.4 静電気放電に関する注意事項21                |

|   | 7.1 Overview 8                       | 11.5 Glossary21                     |

|   | 7.2 Functional Block Diagram 8       | 12 メカニカル、パッケージ、および注文情報 21           |

|   | 7.3 Feature Description 8            |                                     |

# 4 改訂履歴

| 日付      | 改訂内容 | 注  |

|---------|------|----|

| 2017年6月 | *    | 初版 |

**INSTRUMENTS**

www.ti.com JAJSDC6-JUNE 2017

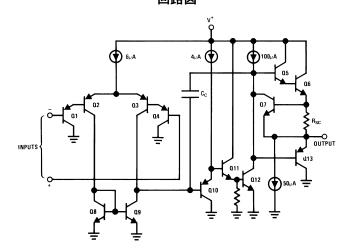

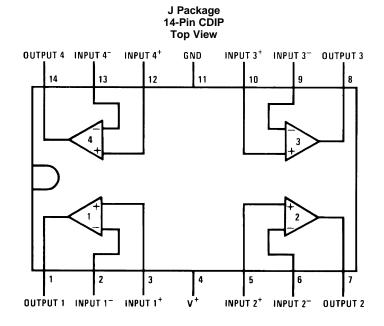

# 5 Pin Configuration and Functions

**Pin Functions**

| Р       | IN  | TVDE | DESCRIPTION                       |  |  |  |  |

|---------|-----|------|-----------------------------------|--|--|--|--|

| NAME    | NO. | TYPE | DESCRIPTION                       |  |  |  |  |

| OUTPUT1 | 1   | 0    | Output, Channel 1                 |  |  |  |  |

| INPUT1- | 2   | 1    | Inverting Input, Channel 1        |  |  |  |  |

| INPUT1+ | 3   | 1    | Noninverting Input, Channel 1     |  |  |  |  |

| V+      | 4   | Р    | Positive Supply Voltage           |  |  |  |  |

| INPUT2+ | 5   | 1    | Nonnverting Input, Channel 2      |  |  |  |  |

| INPUT2- | 6   | I    | verting Input, Channel 2          |  |  |  |  |

| OUTPUT2 | 7   | 0    | Output, Channel 2                 |  |  |  |  |

| OUTPUT3 | 8   | 0    | Output, Channel 3                 |  |  |  |  |

| INPUT3- | 9   | 1    | Inverting Input, Channel 3        |  |  |  |  |

| INPUT3+ | 10  | 1    | Noninverting Input, Channel 3     |  |  |  |  |

| GND     | 11  | Р    | Ground or Negative Supply Voltage |  |  |  |  |

| INPUT4+ | 12  | I    | Noninverting Input, Channel 4     |  |  |  |  |

| INPUT4- | 13  | I    | Inverting Input, Channel 4        |  |  |  |  |

| OUTPUT4 | 14  | 0    | Output, Channel 4                 |  |  |  |  |

# TEXAS INSTRUMENTS

## 6 Specifications

### 6.1 Absolute Maximum Ratings

See (1).

|                                                         |                         |                                                 | MIN    | MAX  | UNIT |

|---------------------------------------------------------|-------------------------|-------------------------------------------------|--------|------|------|

| Supply Voltage, V <sup>+</sup>                          |                         |                                                 |        | 32   | V    |

| Differential Input Voltage                              |                         | 32                                              | V      |      |      |

| Input Voltage                                           | -0.3                    | 32                                              | V      |      |      |

| Input Current (V <sub>IN</sub> < -0.3 V) <sup>(2)</sup> |                         |                                                 |        | 50   | mA   |

| Power Dissipation <sup>(3)</sup>                        | PDIP                    |                                                 |        | 1130 | mW   |

|                                                         | CDIP                    |                                                 |        | 1260 | mW   |

| SOIC Package                                            |                         |                                                 |        | 800  | mW   |

| Output Short-Circuit to GND (One Amplifier) (4)         |                         | V <sup>+</sup> ≤ 15 V and T <sub>A</sub> = 25°C | Contin | uous |      |

| Soldering Information                                   | Dual-In-Line<br>Package |                                                 |        | 260  | °C   |

| Coldoning innormation                                   | Small Outline           | Vapor Phase (60 seconds)                        |        | 215  | °C   |

|                                                         | Package                 | Infrared (15 seconds)                           |        | 220  | °C   |

| Storage temperature, T <sub>stg</sub>                   |                         |                                                 | -65    | 150  | °C   |

- (1) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/ Distributors for availability and specifications.

- (2) This input current will only exist when the voltage at any of the input leads is driven negative. It is due to the collector-base junction of the input PNP transistors becoming forward biased and thereby acting as input diode clamps. In addition to this diode action, there is also lateral NPN parasitic transistor action on the IC chip. This transistor action can cause the output voltages of the op amps to go to the V⁺voltage level (or to ground for a large overdrive) for the time duration that an input is driven negative. This is not destructive and normal output states will re-establish when the input voltage, which was negative, again returns to a value greater than −0.3 V (at 25°C).

- (3) For operating at high temperatures, the LM324-N-MIL must be derated based on a 125°C maximum junction temperature and a thermal resistance of 88°C/W which applies for the device soldered in a printed circuit board, operating in a still air ambient. The dissipation is the total of all four amplifiers—use external resistors, where possible, to allow the amplifier to saturate of to reduce the power which is dissipated in the integrated circuit.

- (4) Short circuits from the output to V<sup>+</sup> can cause excessive heating and eventual destruction. When considering short circuits to ground, the maximum output current is approximately 40 mA independent of the magnitude of V<sup>+</sup>. At values of supply voltage in excess of 15 V, continuous short-circuits can exceed the power dissipation ratings and cause eventual destruction. Destructive dissipation can result from simultaneous shorts on all amplifiers.

## 6.2 ESD Ratings

|                    |                         |                                                                   | VALUE | UNIT |

|--------------------|-------------------------|-------------------------------------------------------------------|-------|------|

| V <sub>(ESD)</sub> | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup> | ±250  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

## 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                                                   | MIN | MAX | UNIT |

|---------------------------------------------------|-----|-----|------|

| Supply Voltage (V <sup>+</sup> - V <sup>-</sup> ) | 3   | 32  | ٧    |

| Operating Input Voltage on Input pins             | 0   | +٧  | ٧    |

| Operating junction temperature, T <sub>J</sub>    | 0   | 70  | °C   |

## 6.4 Thermal Information

|                 |                                        | LM324-N-MIL |      |

|-----------------|----------------------------------------|-------------|------|

|                 | THERMAL METRIC <sup>(1)</sup>          | D/SOIC      | UNIT |

|                 |                                        | 14 PINS     |      |

| $R_{\theta JA}$ | Junction-to-ambient thermal resistance | 88          | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

JAJSDC6-JUNE 2017 www.ti.com

## 6.5 Electrical Characteristics

$V^+ = +5.0V$ , (1), unless otherwise stated

| PAI                                            | RAMETER                         | TEST CO                                                                                                                          | NDITIONS                                                                             | MIN | TYP | MAX                 | UNIT  |  |  |

|------------------------------------------------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-----|-----|---------------------|-------|--|--|

| Input Offset Voltage                           | je                              | T <sub>A</sub> = 25°C <sup>(2)</sup>                                                                                             |                                                                                      |     | 2   | 7                   | mV    |  |  |

| Input Bias Current                             | (3)                             | $I_{IN(+)}$ or $I_{IN(-)}$ , $V_{CM} = 0$ V, $T_A = 25^{\circ}$ C                                                                |                                                                                      | 45  | 250 | nA                  |       |  |  |

| Input Offset Curre                             | nt                              | $I_{IN(+)}$ or $I_{IN(-)}$ , $V_{CM} = 0$ V, $T_A = 25^{\circ}$ C                                                                |                                                                                      |     | 5   | 50                  | nA    |  |  |

| Input Common-Mo                                | de Voltage Range <sup>(4)</sup> | V <sup>+</sup> = 30 V,<br>T <sub>A</sub> = 25°C                                                                                  |                                                                                      | 0   |     | V <sup>+</sup> -1.5 | V     |  |  |

| Supply Current                                 |                                 | Over Full Temperature Range $R_L = \infty$ On All Op Amps, $V^+ = 30 \text{ V}$                                                  |                                                                                      |     | 1.5 | 3                   | mA    |  |  |

|                                                |                                 | V <sup>+</sup> = 5 V                                                                                                             |                                                                                      |     | 0.7 | 1.2                 |       |  |  |

| Large Signal Volta                             | ge Gain                         | $V^+$ = 15V, R <sub>L</sub> ≥ 2 kΩ,<br>(V <sub>O</sub> = 1 V to 11 V), T <sub>A</sub> = 25°C                                     |                                                                                      | 25  | 100 |                     | V/mV  |  |  |

| Common-Mode Re                                 | ejection Ratio                  | DC, $V_{CM} = 0 \text{ V to V}^+ - 1.5 \text{ V}$ , $T_A =$                                                                      | 25°C                                                                                 | 65  | 85  |                     | dB    |  |  |

| Power Supply Rej                               | ection Ratio                    | V <sup>+</sup> = 5 V to 30 V, T <sub>A</sub> = 25°C                                                                              |                                                                                      | 65  | 100 |                     | dB    |  |  |

| Amplifier-to-Amplif<br>Coupling <sup>(5)</sup> | ier                             | f = 1 kHz to 20 kHz, T <sub>A</sub> = 25°C (Input Referred)                                                                      |                                                                                      |     |     |                     | dB    |  |  |

| Source                                         |                                 | $V_{IN}^{+} = 1 \text{ V}, V_{IN}^{-} = 0 \text{ V},$<br>$V^{+} = 15 \text{ V}, V_{O} = 2 \text{ V}, T_{A} = 25^{\circ}\text{C}$ | 20                                                                                   | 40  |     | mA                  |       |  |  |

| Output Current                                 | Circle                          | $V_{IN}^- = 1 \text{ V}, V_{IN}^+ = 0 \text{ V},$<br>$V^+ = 15 \text{ V}, V_O = 2 \text{ V}, T_A = 25^{\circ}\text{C}$           | 10                                                                                   | 20  |     | mA                  |       |  |  |

|                                                | Sink                            | $V_{IN}^- = 1 \text{ V}, V_{IN}^+ = 0 \text{ V},$<br>$V^+ = 15 \text{ V}, V_O = 200 \text{ mV}, T_A = 25^\circ$                  | 12                                                                                   | 50  |     | μА                  |       |  |  |

| Short Circuit to Gr                            | ound                            | V <sup>+</sup> = 15 V, T <sub>A</sub> = 25°C <sup>(6)</sup>                                                                      |                                                                                      | 40  | 60  | mA                  |       |  |  |

| Input Offset Voltage                           | je                              | See (2)                                                                                                                          |                                                                                      |     |     | 9                   | mV    |  |  |

| V <sub>OS</sub> Drift                          |                                 | $R_S = 0 \Omega$                                                                                                                 |                                                                                      |     | 7   |                     | μV/°C |  |  |

| Input Offset Curre                             | nt                              | $I_{IN(+)} - I_{IN(-)}, V_{CM} = 0 \text{ V}$                                                                                    |                                                                                      |     | 150 | nA                  |       |  |  |

| I <sub>OS</sub> Drift                          |                                 | $R_S = 0 \Omega$                                                                                                                 |                                                                                      |     | 10  |                     | pA/°C |  |  |

| Input Bias Current                             |                                 | I <sub>IN(+)</sub> or I <sub>IN(-)</sub>                                                                                         |                                                                                      |     | 40  | 500                 | nA    |  |  |

| Input Common-Mo                                | de Voltage Range <sup>(4)</sup> | V <sup>+</sup> = 30 V                                                                                                            |                                                                                      | 0   |     | V+-2                | V     |  |  |

| Large Signal Volta                             | ge Gain                         | $V^+ = 15 \text{ V } (V_O \text{Swing} = 1 \text{ V to } 11 \text{ V}),$ $R_L \ge 2 \text{ k}\Omega$                             | 15                                                                                   |     |     | V/mV                |       |  |  |

|                                                | V                               | \/t 00\/                                                                                                                         | $R_L = 2 k\Omega$                                                                    | 26  |     |                     | \/    |  |  |

| Output Voltage<br>Swing                        | V <sub>OH</sub>                 | V <sup>+</sup> = 30 V                                                                                                            | $R_L = 10 \text{ k}\Omega$                                                           | 27  | 28  |                     | V     |  |  |

| O.VIIIg                                        | V <sub>OL</sub>                 | $V^{+} = 5 \text{ V}, R_{L} = 10 \text{ k}\Omega$                                                                                |                                                                                      | 5   | 20  | mV                  |       |  |  |

| Output Current                                 | Source                          | V <sub>O</sub> = 2 V                                                                                                             | $V_{IN}^{+} = 1 \text{ V},$<br>$V_{IN}^{-} = 0 \text{ V},$<br>$V^{+} = 15 \text{ V}$ | 10  | 20  |                     | mA    |  |  |

|                                                | Sink                            |                                                                                                                                  | $V_{IN}^{-} = 1 \text{ V},$<br>$V_{IN}^{+} = 0 \text{ V},$<br>$V^{+} = 15 \text{ V}$ | 5   | 8   |                     | mA    |  |  |

- (1) The LM324-N-MIL temperature specifications are limited to  $0^{\circ}\text{C} \le T_{A} \le +70^{\circ}\text{C}$ .

- $V_O \approx 1.4V$ ,  $R_S = 0 \Omega$  with  $V^+$  from 5 V to 30 V.

- The direction of the input current is out of the IC due to the PNP input stage. This current is essentially constant, independent of the state of the output so no loading change exists on the input lines.

- (4) The input common-mode voltage of either input signal voltage should not be allowed to go negative by more than 0.3 V (at 25°C). The upper end of the common-mode voltage range is V<sup>+</sup> 1.5 V (at 25°C), but either or both inputs can go to 32 V without damage, independent of the magnitude of V+.

- (5) Due to proximity of external components, insure that coupling is not originating via stray capacitance between these external parts. This

- typically can be detected as this type of capacitance increases at higher frequencies. Short circuits from the output to  $V^+$  can cause excessive heating and eventual destruction. When considering short circuits to ground, the maximum output current is approximately 40 mA independent of the magnitude of V<sup>+</sup>. At values of supply voltage in excess of 15 V, continuous short-circuits can exceed the power dissipation ratings and cause eventual destruction. Destructive dissipation can result from simultaneous shorts on all amplifiers.

# TEXAS INSTRUMENTS

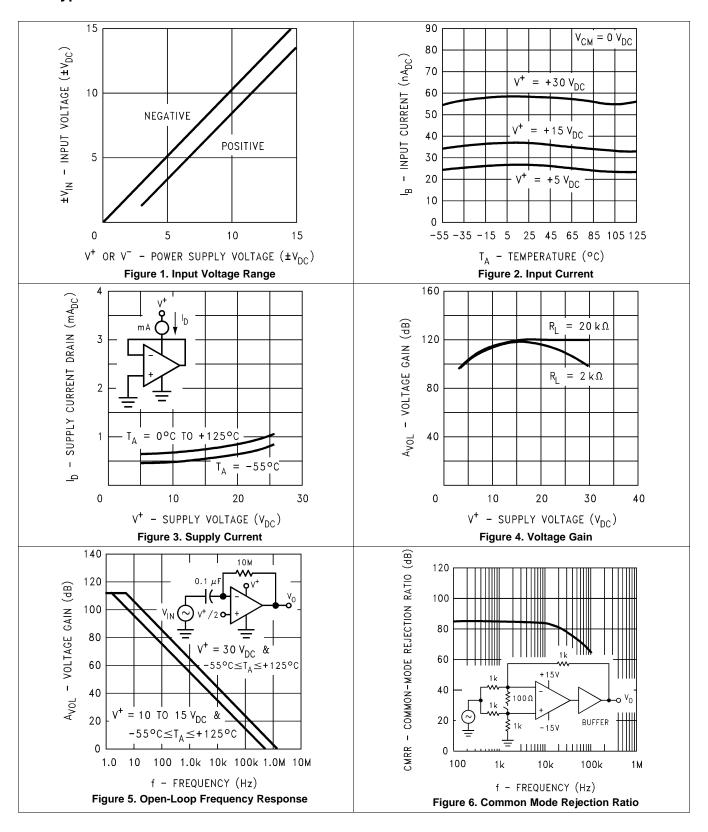

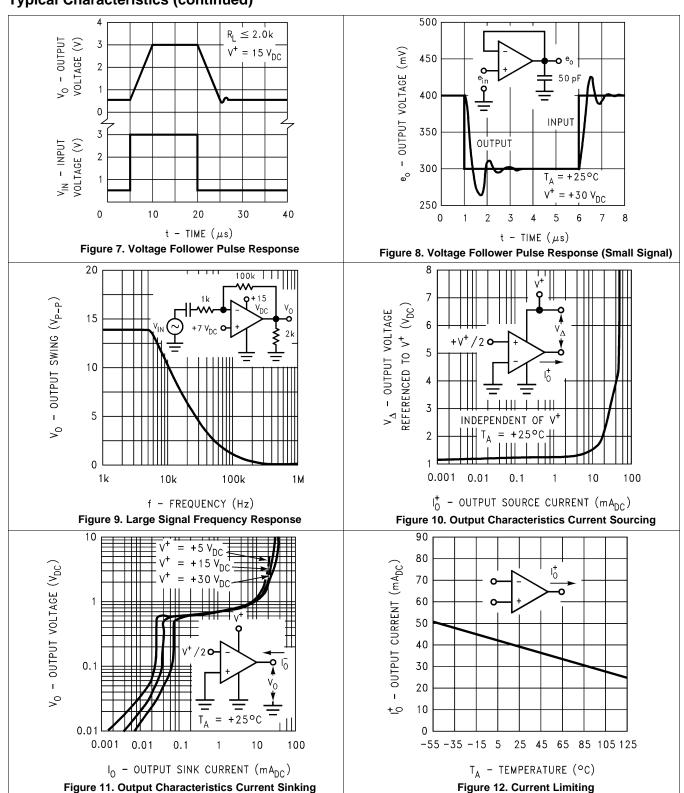

## 6.6 Typical Characteristics

**Typical Characteristics (continued)**

JAJSDC6 – JUNE 2017 www.ti.com

# TEXAS INSTRUMENTS

## 7 Detailed Description

#### 7.1 Overview

The LM324-N-MIL device is an op amp which operates with only a single power supply voltage, has true-differential inputs, and remains in the linear mode with an input common-mode voltage of 0 V<sub>DC</sub>. This amplifier operates over a wide range of power supply voltage with little change in performance characteristics. At 25°C amplifier operation is possible down to a minimum supply voltage of 2.3 V<sub>DC</sub>.

## 7.2 Functional Block Diagram

## 7.3 Feature Description

The LM324-N-MIL provides a compelling balance of performance versus current consumption. The 700  $\mu$ A of supply current draw over the wide operating conditions with a 1-MHz gain-bandwidth and temperature compensated bias currents makes the LM324-N-MIL an effective solution for large variety of applications. The input offset voltage of 2 mV and offset current of 5 nA, along with the 45n-A bias current across a wide supply voltage means a single design can be used in a large number of different implementations.

## 7.4 Device Functional Modes

Large differential input voltages can be easily accommodated and, as input differential voltage protection diodes are not needed, no large input currents result from large differential input voltages. The differential input voltage may be larger than  $V^+$  without damaging the device. Protection should be provided to prevent the input voltages from going negative more than  $-0.3~V_{DC}$  (at  $25^{\circ}C$ ). An input clamp diode with a resistor to the IC input terminal can be used.

To reduce the power supply drain, the amplifiers have a class A output stage for small signal levels which converts to class B in a large signal mode. This allows the amplifiers to both source and sink large output currents. Therefore both NPN and PNP external current boost transistors can be used to extend the power capability of the basic amplifiers. The output voltage needs to raise approximately 1 diode drop above ground to bias the on-chip vertical PNP transistor for output current sinking applications.

For ac applications, where the load is capacitively coupled to the output of the amplifier, a resistor should be used, from the output of the amplifier to ground to increase the class A bias current and prevent crossover distortion.

Where the load is directly coupled, as in dc applications, there is no crossover distortion.

Capacitive loads which are applied directly to the output of the amplifier reduce the loop stability margin. Values of 50 pF can be accommodated using the worst-case non-inverting unity gain connection. Large closed loop gains or resistive isolation should be used if larger load capacitance must be driven by the amplifier.

www.ti.com

**Device Functional Modes (continued)**

## Device Functional Modes (Continued)

The bias network of the LM324-N-MIL establishes a drain current which is independent of the magnitude of the power supply voltage over the range of from 3  $V_{DC}$  to 30  $V_{DC}$ .

Output short circuits either to ground or to the positive power supply should be of short time duration. Units can be destroyed, not as a result of the short circuit current causing metal fusing, but rather due to the large increase in IC chip dissipation which will cause eventual failure due to excessive junction temperatures. Putting direct short-circuits on more than one amplifier at a time will increase the total IC power dissipation to destructive levels, if not properly protected with external dissipation limiting resistors in series with the output leads of the amplifiers. The larger value of output source current which is available at 25°C provides a larger output current capability at elevated temperatures (see *Typical Characteristics*) than a standard IC op amp.

JAJSDC6 – JUNE 2017 www.ti.com

# TEXAS INSTRUMENTS

## 8 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

## 8.1 Application Information

The LM324-N-MIL amplifier is specified for operation from 3 V to 32 V (±1.5 V to ±16 V). Many of the specifications apply from -40°C to 125°C. Parameters that can exhibit significant variance with regards to operating voltage or temperature are presented in *Typical Characteristics*.

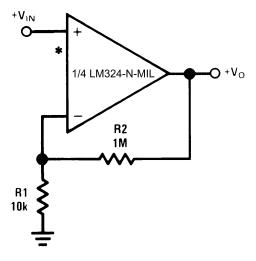

## 8.2 Typical Applications

Figure 13 emphasizes operation on only a single power supply voltage. If complementary power supplies are available, all of the standard op amp circuits can be used. In general, introducing a pseudo-ground (a bias voltage reference of V<sup>+</sup>/2) will allow operation above and below this value in single power supply systems. Many application circuits are shown which take advantage of the wide input common-mode voltage range which includes ground. In most cases, input biasing is not required and input voltages which range to ground can easily be accommodated.

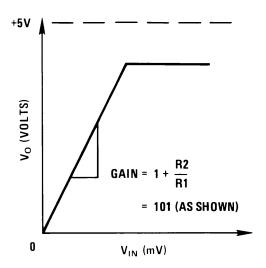

## 8.2.1 Non-Inverting DC Gain (0 V Input = 0 V Output)

<sup>\*</sup>R not needed due to temperature independent I<sub>IN</sub>

Figure 13. Non-Inverting Amplifier with G = 100

#### 8.2.1.1 Design Requirements

For this example application, the required signal gain is a non-inverting 100x±5% with a supply voltage of 5 V.

## 8.2.1.2 Detailed Design Procedure

Using the equation for a non-inverting gain configuration, Av = 1+R2/R1. Setting the R1 to 10 k $\Omega$ , R2 is 99 times larger than R1, which is 990 k $\Omega$ . A 1M $\Omega$  is more readily available, and provides a gain of 101, which is within the desired specification.

www.ti.com JAJSDC6 – JUNE 2017

## **Typical Applications (continued)**

The gain-frequency characteristic of the amplifier and its feedback network must be such that oscillation does not occur. To meet this condition, the phase shift through amplifier and feedback network must never exceed 180° for any frequency where the gain of the amplifier and its feedback network is greater than unity. In practical applications, the phase shift should not approach 180° since this is the situation of conditional stability. Obviously the most critical case occurs when the attenuation of the feedback network is zero.

## 8.2.1.3 Application Curve

Figure 14. Non-Inverting Amplified Response Curve

JAJSDC6 – JUNE 2017 www.ti.com

# TEXAS INSTRUMENTS

## **Typical Applications (continued)**

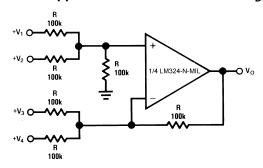

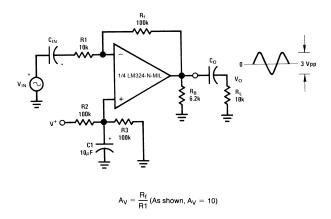

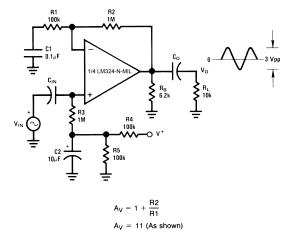

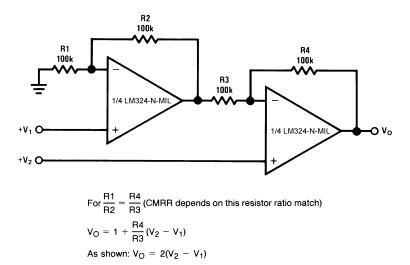

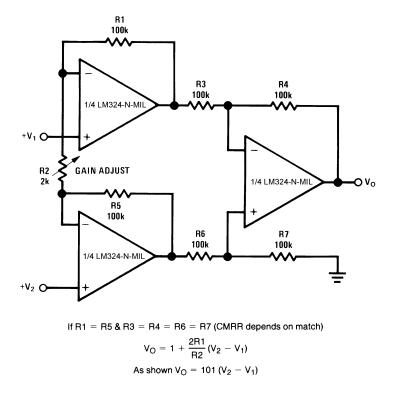

## 8.2.2 Other Application Circuits at $V^+ = 5.0 V_{DC}$

Where:

$$V_0 = V_1 + V_2 - V_3 - V_4$$

$(V_1 + V_2) \ge (V_3 + V_4)$  to keep  $V_0 > 0$   $V_{DC}$

Figure 15. DC Summing Amplifier  $(V_{IN'S} \ge 0 \ V_{DC} \ And \ V_O \ge V_{DC})$

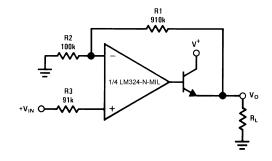

Where:

$$V_0 = 0 V_{DC}$$

for  $V_{IN} = 0 V_{DC}$

$A_V = 10$

Figure 16. Power Amplifier

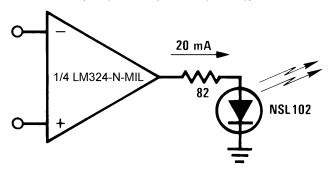

Figure 17. LED Driver

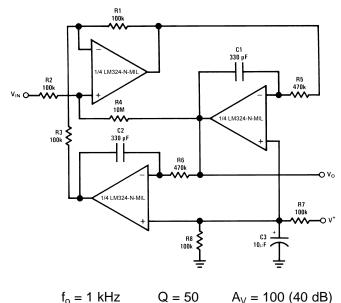

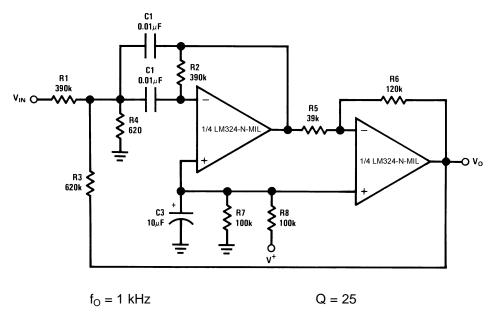

Figure 18. "BI-QUAD" RC Active Bandpass Filter

www.ti.com

# **Typical Applications (continued)**

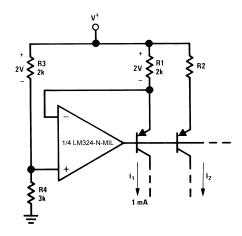

$$I_2 = \left(\frac{R1}{R2}\right)I_1$$

**Figure 19. Fixed Current Sources**

\*(Increase R1 for I<sub>L</sub> small)

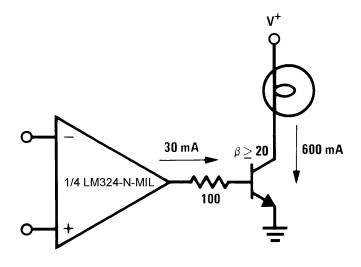

Figure 20. Lamp Driver

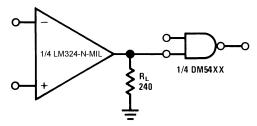

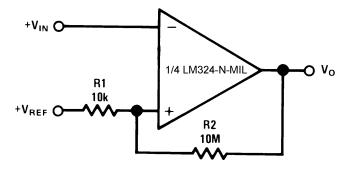

Figure 22. Driving TTL

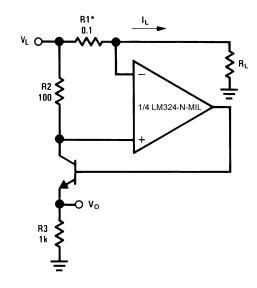

Figure 21. Current Monitor

Figure 23. Voltage Follower

## **Typical Applications (continued)**

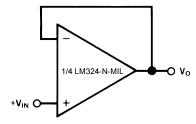

Figure 24. Pulse Generator

Figure 25. Squarewave Oscillator

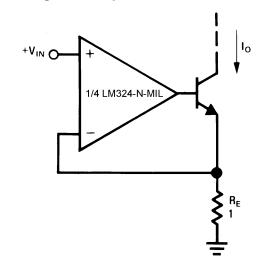

$I_O = 1$  amp/volt  $V_{IN}$  (Increase  $R_E$  for  $I_o$  small)

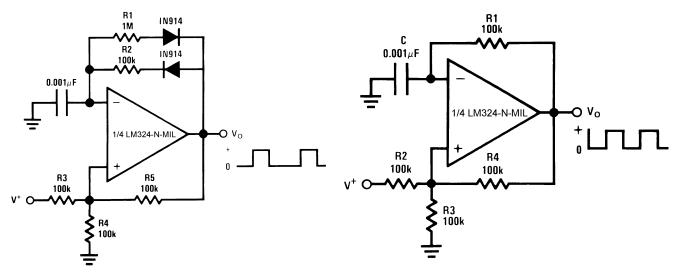

Figure 26. Pulse Generator

Figure 27. High Compliance Current Sink

www.ti.com

Typical Applications (continued)

# POLYCARBONATE OR TO THE POLYCA

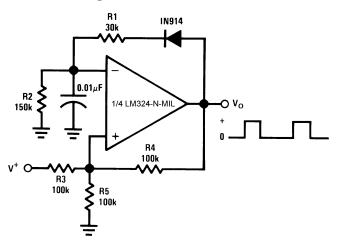

Figure 28. Low Drift Peak Detector

$V_{R} = V_{R}$   $V_{R} = V_{R}$   $V_{O} = V_{R}$

Figure 29. Comparator With Hysteresis

Figure 30. Ground Referencing a Differential Input Signal

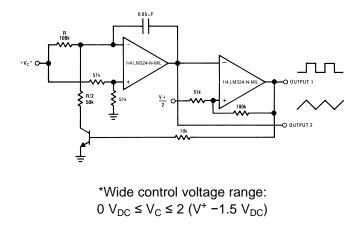

Figure 31. Voltage Controlled Oscillator Circuit

JAJSDC6 – JUNE 2017 www.ti.com

# TEXAS INSTRUMENTS

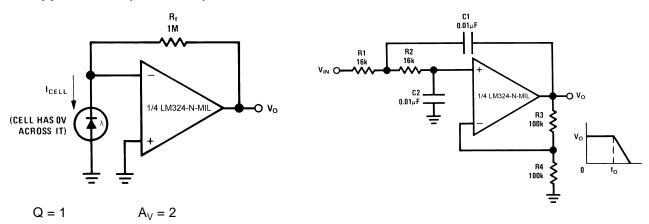

Figure 32. Photo Voltaic-Cell Amplifier

Figure 33. DC Coupled Low-Pass RC Active Filter

Figure 34. AC Coupled Inverting Amplifier

Figure 35. AC Coupled Non-Inverting Amplifier

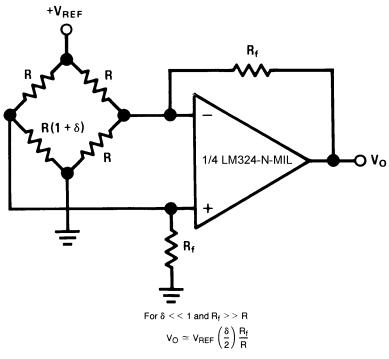

Figure 36. High Input Z, DC Differential Amplifier

Figure 37. High Input Z Adjustable-Gain DC Instrumentation Amplifier

# TEXAS INSTRUMENTS

Figure 38. Bridge Current Amplifier

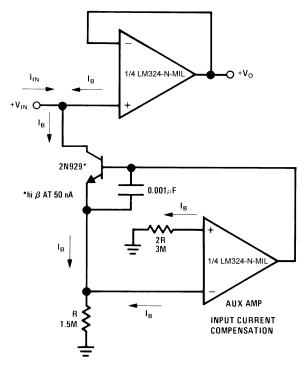

Figure 39. Using Symmetrical Amplifiers to Reduce Input Current (General Concept)

www.ti.com JAJSDC6-JUNE 2017

Figure 40. Bandpass Active Filter

JAJSDC6 – JUNE 2017 www.tij.co.jp

# TEXAS INSTRUMENTS

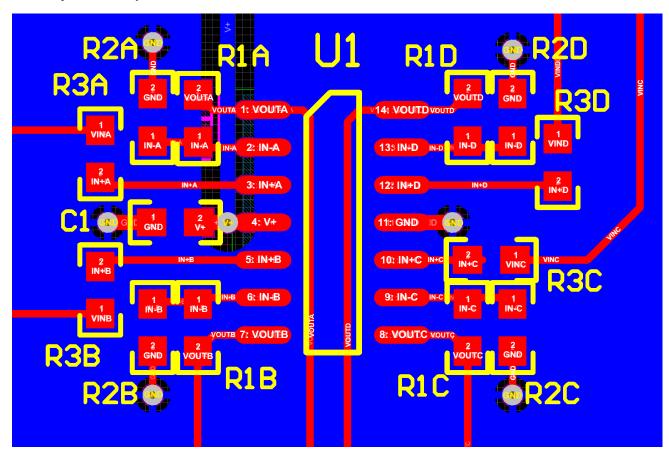

## 9 Power Supply Recommendations

The pinouts of the package have been designed to simplify PC board layouts. Inverting inputs are adjacent to outputs for all of the amplifiers and the outputs have also been placed at the corners of the package (pins 1, 7, 8, and 14).

Precautions should be taken to insure that the power supply for the integrated circuit never becomes reversed in polarity or that the unit is not inadvertently installed backwards in a test socket as an unlimited current surge through the resulting forward diode within the IC could cause fusing of the internal conductors and result in a destroyed unit.

## 10 Layout

## 10.1 Layout Guidelines

The V + pin should be bypassed to ground with a low-ESR capacitor. The optimum placement is closest to the V + and ground pins.

Take care to minimize the loop area formed by the bypass capacitor connection between V + and ground.

The ground pin should be connected to the PCB ground plane at the pin of the device.

The feedback components should be placed as close to the device as possible minimizing strays.

## 10.2 Layout Example

Figure 41. Layout Example

www.tij.co.jp JAJSDC6 – JUNE 2017

## 11 デバイスおよびドキュメントのサポート

## 11.1 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、ti.comのデバイス製品フォルダを開いてください。右上の隅にある「通知を受け取る」をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取れます。変更の詳細については、修正されたドキュメントに含まれている改訂履歴をご覧ください。

## 11.2 コミュニティ・リソース

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

TI E2E™オンライン・コミュニティ *TIのE2E(Engineer-to-Engineer)コミュニティ。*エンジニア間の共同作業を促進するために開設されたものです。e2e.ti.comでは、他のエンジニアに質問し、知識を共有し、アイディアを検討して、問題解決に役立てることができます。

設計サポート *TIの設計サポート* 役に立つE2Eフォーラムや、設計サポート・ツールをすばやく見つけることができます。技術サポート用の連絡先情報も参照できます。

#### 11.3 商標

E2E is a trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

## 11.4 静電気放電に関する注意事項

すべての集積回路は、適切なESD保護方法を用いて、取扱いと保存を行うようにして下さい。

静電気放電はわずかな性能の低下から完全なデバイスの故障に至るまで、様々な損傷を与えます。高精度の集積回路は、損傷に対して敏感であり、極めてわずかなパラメータの変化により、デバイスに規定された仕様に適合しなくなる場合があります。

## 11.5 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

## 12 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、そのデバイスについて利用可能な最新のデータです。このデータは予告なく変更されることがあり、ドキュメントが改訂される場合もあります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

www.ti.com 28-Jun-2024

#### PACKAGING INFORMATION

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan            | Lead finish/<br>Ball material | MSL Peak Temp    | Op Temp (°C) | Device Marking (4/5) | Samples |

|------------------|--------|--------------|--------------------|------|----------------|---------------------|-------------------------------|------------------|--------------|----------------------|---------|

| LM324J           | ACTIVE | CDIP         | J                  | 14   | 25             | Non-RoHS<br>& Green | Call TI                       | Level-1-NA-UNLIM | 0 to 70      | LM324J               | Samples |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

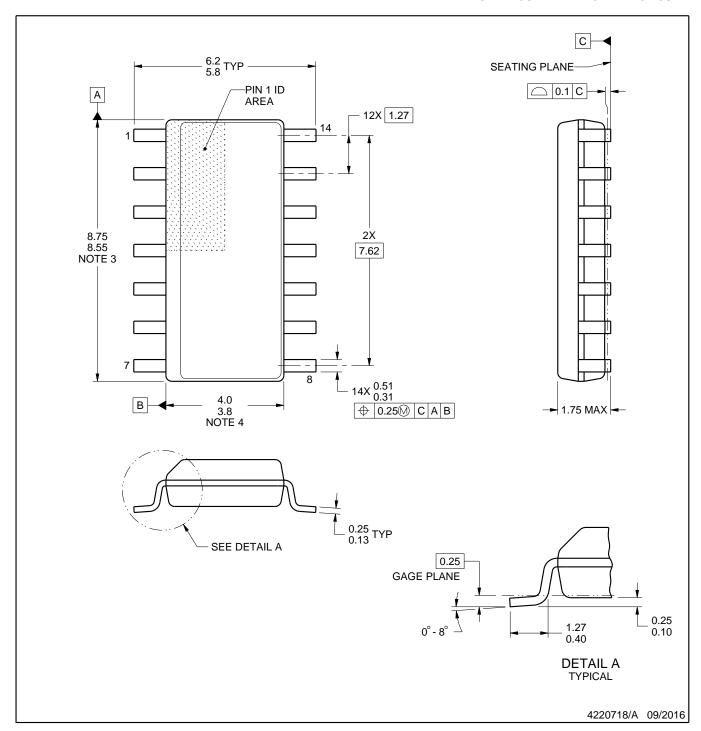

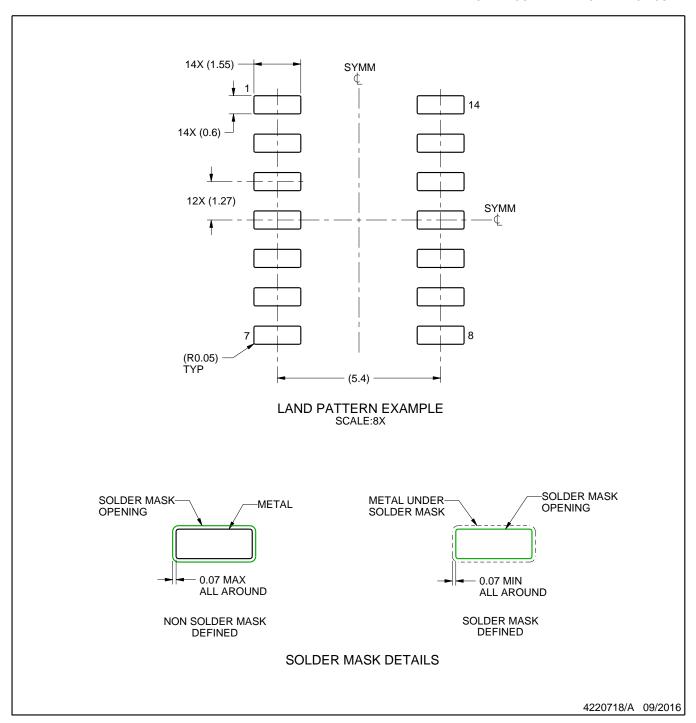

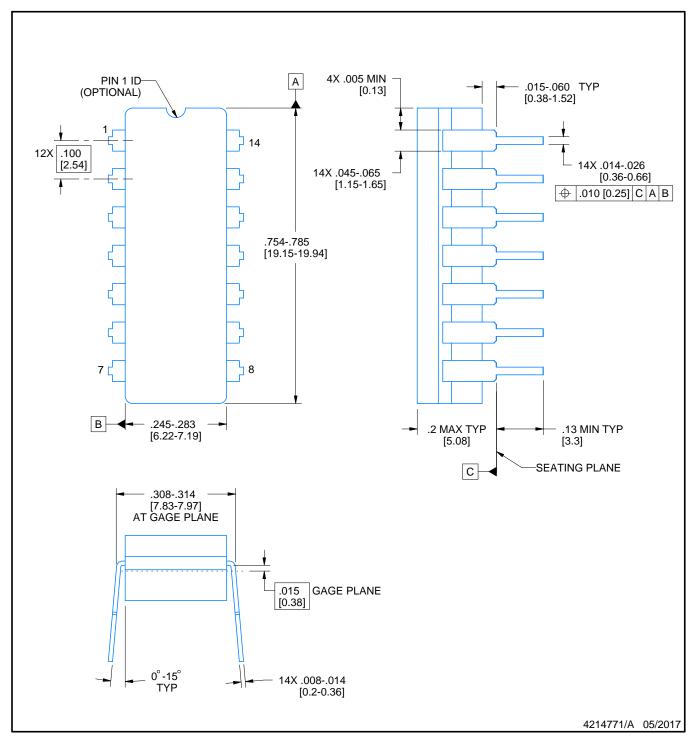

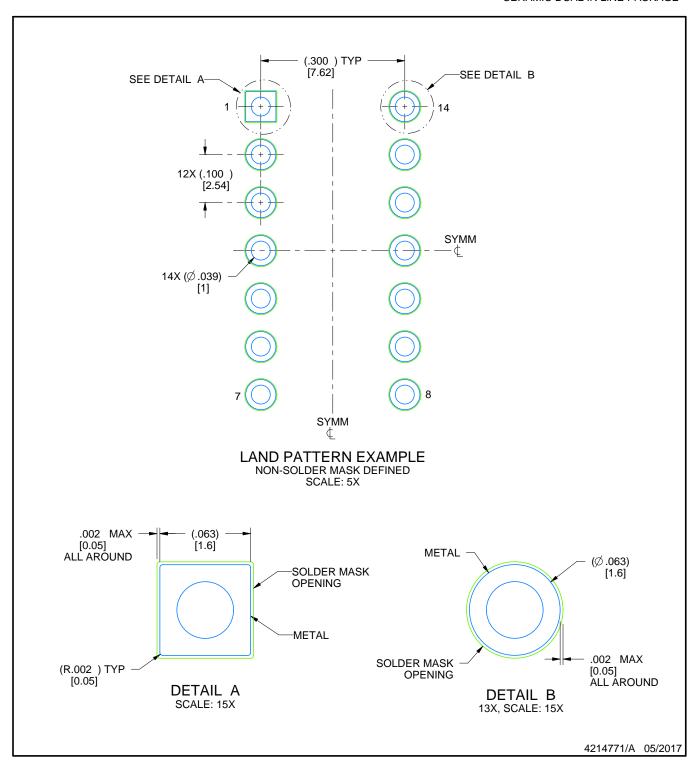

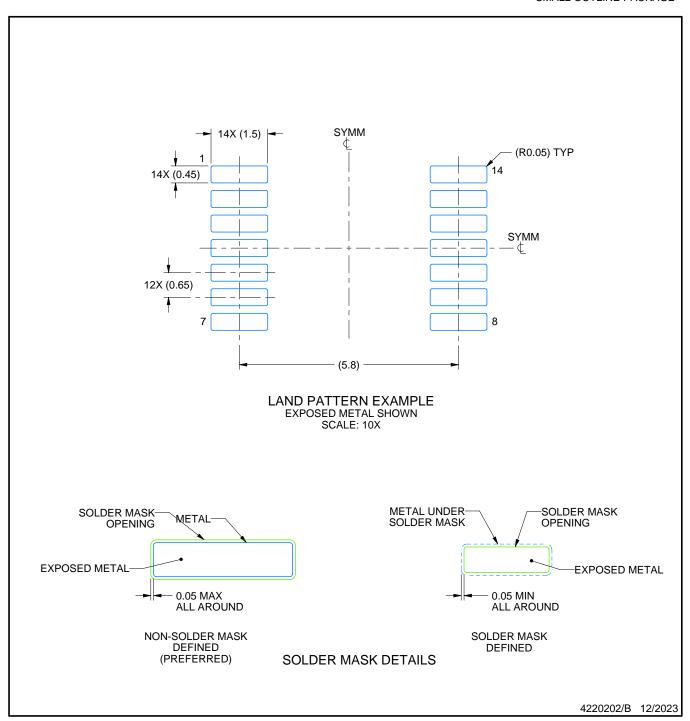

SMALL OUTLINE INTEGRATED CIRCUIT

## NOTES:

- 1. All linear dimensions are in millimeters. Dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm, per side.

- 4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.43 mm, per side.

- 5. Reference JEDEC registration MS-012, variation AB.

SMALL OUTLINE INTEGRATED CIRCUIT

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

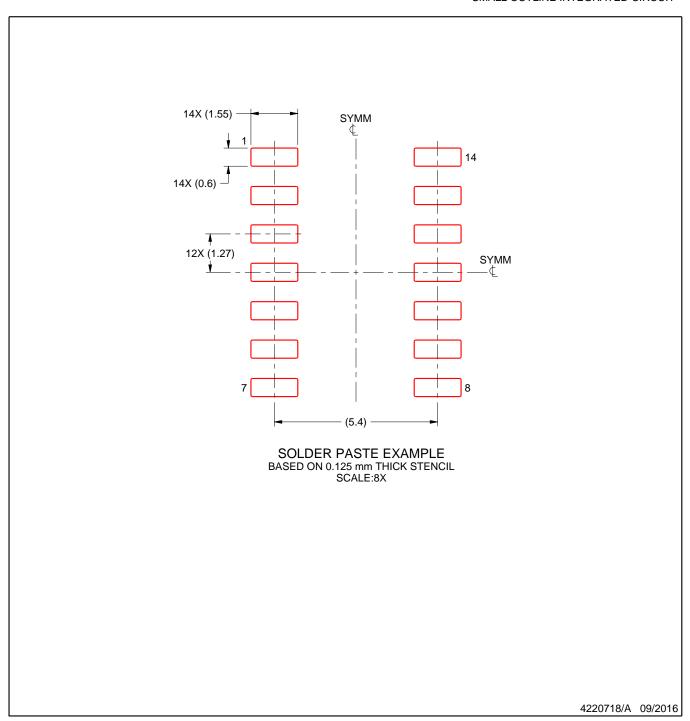

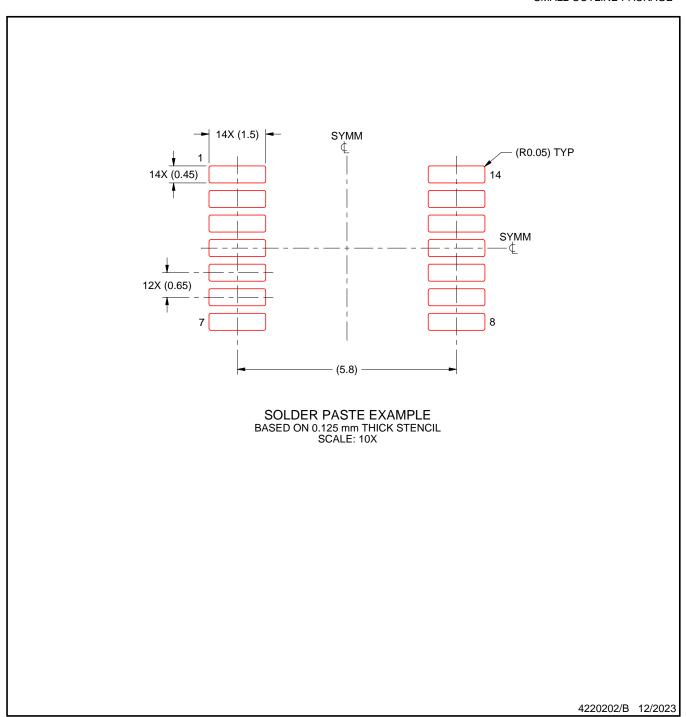

SMALL OUTLINE INTEGRATED CIRCUIT

NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

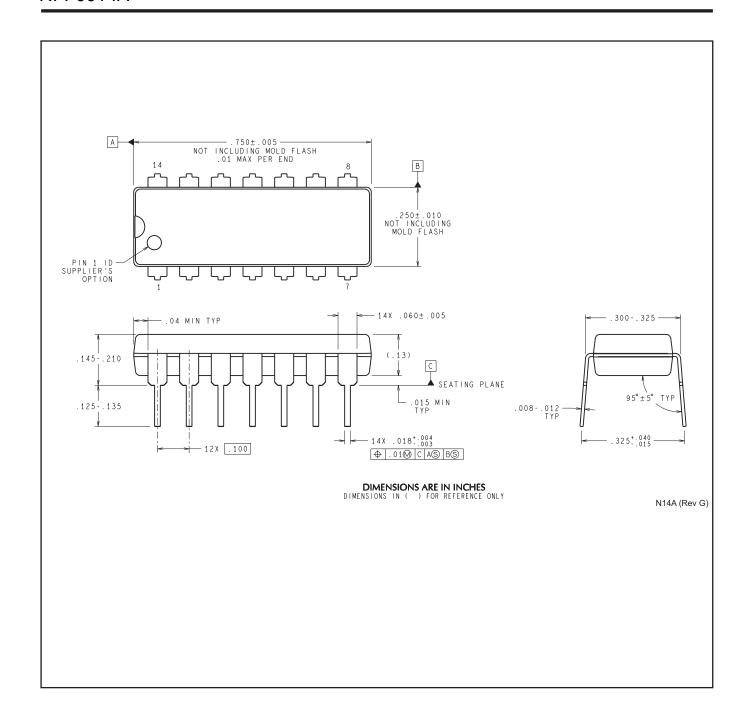

CERAMIC DUAL IN LINE PACKAGE

Images above are just a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

4040083-5/G

CERAMIC DUAL IN LINE PACKAGE

#### NOTES:

- 1. All controlling linear dimensions are in inches. Dimensions in brackets are in millimeters. Any dimension in brackets or parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

- 3. This package is hermitically sealed with a ceramic lid using glass frit.

- His package is remitted by sealed with a ceramic its using glass mit.

Index point is provided on cap for terminal identification only and on press ceramic glass frit seal only.

Falls within MIL-STD-1835 and GDIP1-T14.

CERAMIC DUAL IN LINE PACKAGE

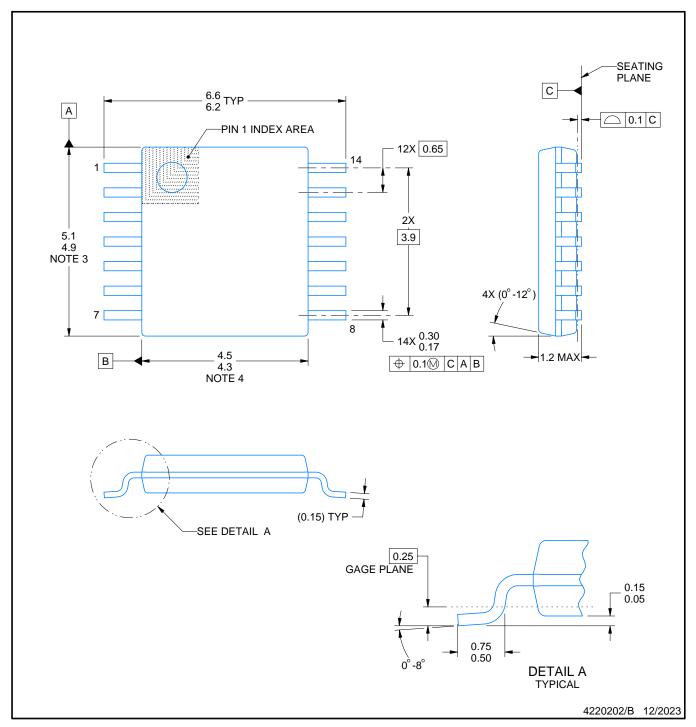

SMALL OUTLINE PACKAGE

## NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm per side.

- 4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side.

- 5. Reference JEDEC registration MO-153.

SMALL OUTLINE PACKAGE

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

SMALL OUTLINE PACKAGE

NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス・デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあら ゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TIの製品は、TIの販売条件、または ti.com やかかる TI 製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、TIはそれらに異議を唱え、拒否します。

郵送先住所:Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2024, Texas Instruments Incorporated