🕳 Order

Now

LM3478

JAJS711X -JULY 2000-REVISED JUNE 2017

参考資料

# LM3478 スイッチング・レギュレータ用高効率、ローサイドNチャネル・ コントローラ

Technical

Documents

# 1 特長

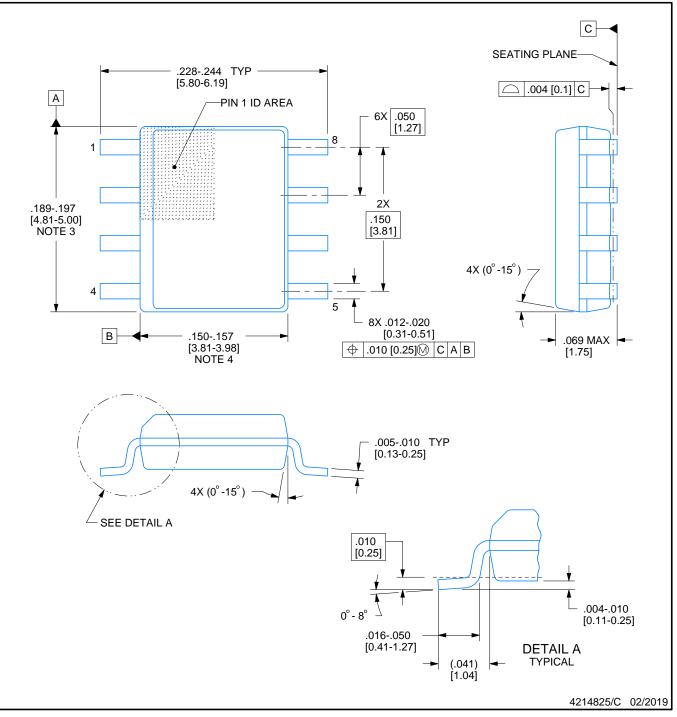

- 8リードのVSSOP-8およびSOIC-8パッケージ

- 1Aのピーク電流能力を持つ内部的なプッシュプ ル・ドライバ

- 電流制限およびサーマル・シャットダウン保護機

能

- コンデンサと抵抗による周波数補償の最適化

- 内部的なソフトスタート

- 電流モード動作

- ヒステリシス付きの低電圧誤動作防止

- WEBENCH Power Designerにより、LM3478を使 用するカスタム設計を作成

- 2 アプリケーション

- 分散電源システム

- バッテリ充電器

- オフライン電源

- テレコム電源

- 車載用電力システム

- 広い電源電圧範囲: 2.97V~40V

- クロック周波数を100kHz~1MHzの範囲で変更可

能

- ±2.5% (全温度範囲)の内部基準電圧

- シャットダウン時の消費電流10µA (全温度範囲)

# 3 説明

🥭 Tools &

Software

LM3478は、スイッチング・レギュレータ用の多用途ローサ イドNチャネルMOFFETコントローラです。昇圧、フライ バック、SEPICなど、ローサイドMOSFETを必要とするトポ ロジでの使用に適しています。さらに、LM3478は非常に 高いスイッチング周波数で動作可能なため、ソリューション 全体を小型化できます。LM3478のスイッチング周波数 は、単一の外付け抵抗を使用して、100kHz~1MHzの任 意の値に設定できます。電流モード制御により、帯域幅と 過渡応答が優れており、サイクル単位の電流制限機能も あります。出力電流は、単一の外付け抵抗によりプログラ ム可能です。

Support &

Community

22

LM3478にはサーマル・シャットダウン、短絡保護、過電圧 保護などの機能が組み込まれています。省電力シャットダ ウン・モードにより、合計消費電流が5µAに低減され、電源 シーケンシングを実行できます。内部的なソフトスタートに より、スタートアップ時の突入電流が制限されます。

製品情報(1)

| 型番       | パッケージ     | 本体サイズ(公称)     |

|----------|-----------|---------------|

| LM3478   | SOIC (8)  | 4.90mmx3.91mm |

| LIVI3410 | VSSOP (8) | 3.00mm×3.00mm |

(1) 利用可能なすべてのパッケージについては、このデータシートの末 尾にある注文情報を参照してください。

英語版のTI製品についての情報を翻訳したこの資料は、製品の概要を確認する目的で便宜的に提供しているものです。該当する正式な英語版の最新情報は、www.ti.comで閲覧でき、その内 容が常に優先されます。TIでは翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、必ず最新版の英語版をご参照くださいますようお願いいたします。 English Data Sheet: SNVS085

2

LM3478 JAJS711X-JULY 2000-REVISED JUNE 2017

# 目次

| 1 | 特長   |                                    |

|---|------|------------------------------------|

| 2 | アプ   | リケーション 1                           |

| 3 | 説明   | l1                                 |

| 4 | 改訂   | '履歴2                               |

| 5 | Pin  | Configuration and Functions 3      |

| 6 | Spe  | cifications4                       |

|   | 6.1  | Absolute Maximum Ratings 4         |

|   | 6.2  | ESD Ratings - LM3478 4             |

|   | 6.3  | Recommended Operating Conditions 4 |

|   | 6.4  | Thermal Information 5              |

|   | 6.5  | Electrical Characteristics5        |

|   | 6.6  | Typical Characteristics7           |

| 7 | Deta | ailed Description 11               |

|   | 7.1  | Overview 11                        |

|   | 7.2  | Functional Block Diagram 12        |

|   | 7.3  | Feature Description 12             |

|   | 7.4  | Device Functional Modes 15         |

| 8  | Appl | lication and Implementation | 16              |

|----|------|-----------------------------|-----------------|

|    | 8.1  | Application Information     | 16              |

|    |      | Typical Applications        |                 |

| 9  | Pow  | er Supply Recommendations   | <mark>28</mark> |

| 10 | Layo | out                         | 28              |

|    | 10.1 | Layout Guidelines           | 28              |

|    | 10.2 | Layout Example              | 29              |

| 11 | デバ   | イスおよびドキュメントのサポート            | 30              |

|    | 11.1 | WEBENCHツールによるカスタム設計         | 30              |

|    | 11.2 | ドキュメントの更新通知を受け取る方法          | 30              |

|    | 11.3 | ドキュメントのサポート                 | 30              |

|    | 11.4 | 関連リンク                       | 30              |

|    | 11.5 | 商標                          | 30              |

|    | 11.6 | 静電気放電に関する注意事項               | 30              |

|    | 11.7 | Glossary                    | 30              |

| 12 | メカニ  | ニカル、パッケージ、および注文情報           |                 |

|    |      |                             |                 |

# 4 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

#### Revision W (December 2014) から Revision X に変更

| • | LM3478Q-Q1データシートを参照し、LM3478Q-Q1デバイスを削除                                                                                                                                           | 1 |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| • | Changed package from "DCK" to "DGK" for LM3478 and LM3478-Q1 devices in the <i>Thermal Information</i> table; changed pin complement from "3" to "8" for the D, and DGK packages | 5 |

| • | Changed R <sub>0JA</sub> for the D package from "157.2" to "105.3" °C/W                                                                                                          | 5 |

| • | Changed R <sub>0JC(top)</sub> for the D package from "49.9" to "50.3" °C/W                                                                                                       | 5 |

| • | Changed R <sub>0JB</sub> for the D package from "77.1" to "55.8" °C/W                                                                                                            | 5 |

| • | Changed $\psi_{JT}$ for the D package from "4.7" to "6.8" °C/W                                                                                                                   | 5 |

| • | Changed will for the D package from "75.8" to "54.7" °C/W                                                                                                                        | 5 |

#### Revision V (February 2013) から Revision W に変更

| 4 |

|---|

| 6 |

|   |

### Revision U (February 2013) から Revision V に変更

www.ti.com

Page

# Page

# Page

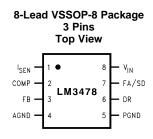

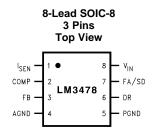

# 5 Pin Configuration and Functions

#### **Pin Functions**

| PIN<br>NAME NO.  |   | 1/0 | DESCRIPTION                                                                                                                                                                                                                                      |  |  |

|------------------|---|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                  |   | I/O | DESCRIPTION                                                                                                                                                                                                                                      |  |  |

| I <sub>SEN</sub> | 1 | I   | Current sense input pin. Voltage generated across an external sense resistor is fed into this pin.                                                                                                                                               |  |  |

| COMP             | 2 | I   | ompensation pin. A resistor, capacitor combination connected to this pin provides compensation for the ontrol loop.                                                                                                                              |  |  |

| FB               | 3 | I   | Feedback pin. The output voltage should be adjusted using a resistor divider to provide 1.26 V at this pin.                                                                                                                                      |  |  |

| AGND             | 4 | G   | Analog ground pin.                                                                                                                                                                                                                               |  |  |

| PGND             | 5 | G   | Power ground pin.                                                                                                                                                                                                                                |  |  |

| DR               | 6 | 0   | Drive pin. The gate of the external MOSFET should be connected to this pin.                                                                                                                                                                      |  |  |

| FA/SD            | 7 | I   | Frequency adjust and Shutdown pin. A resistor connected to this pin sets the oscillator frequency. A high level on this pin for longer than 30 $\mu$ s will turn the device off. The device will then draw less than 10 $\mu$ A from the supply. |  |  |

| V <sub>IN</sub>  | 8 | Р   | Power Supply Input pin.                                                                                                                                                                                                                          |  |  |

# 6 Specifications

### 6.1 Absolute Maximum Ratings

over operating free-air temperature (unless otherwise noted) <sup>(1)</sup>

|                                     |                     | MIN                | MAX                    | UNIT |

|-------------------------------------|---------------------|--------------------|------------------------|------|

| Input Voltage                       |                     |                    | 45                     | V    |

| FB Pin Voltage                      |                     | –0.4< V            | V <sub>FB</sub> < 7    | V    |

| FA/SD Pin Voltage                   |                     | $-0.4 < V_{FA/SD}$ | V <sub>FA/SD</sub> < 7 | V    |

| Peak Driver Output Curre<br>(<10µs) | nt                  |                    | 1                      | A    |

| Power Dissipation                   |                     | Internally         | Limited                |      |

| Junction Temperature                |                     |                    | +150                   | °C   |

| Lead Temperature                    | Vapor Phase (60 s)  |                    | 215                    | °C   |

|                                     | Infrared (15 s)     |                    | 260                    | °C   |

| DR Pin Voltage                      |                     | –0.4 ≤ VDR         | VDR ≤ 8                | V    |

| I <sub>SEN</sub> Pin Voltage        |                     |                    | 500                    | mV   |

| T <sub>stg</sub>                    | Storage temperature | -65                | 150                    | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 6.2 ESD Ratings - LM3478

|                    |                         |                                                                                   | VALUE | UNIT |

|--------------------|-------------------------|-----------------------------------------------------------------------------------|-------|------|

|                    |                         | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>       | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101, all $pins^{(2)}$ | ±750  | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                            | MIN                    | NOM MAX               | UNIT |

|----------------------------|------------------------|-----------------------|------|

| Supply Voltage             | 2.97 ≤ V <sub>IN</sub> | V <sub>IN</sub> ≤ 40  | V    |

| Junction Temperature Range | $-40 \le T_J$          | T <sub>J</sub> ≤ +125 | °C   |

| Switching Frequency        | $100 \le F_{SW}$       | F <sub>SW</sub> ≤ 1   | MHz  |

### 6.4 Thermal Information

|                       |                                              | LM     | 3478   |      |

|-----------------------|----------------------------------------------|--------|--------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | D      | DGK    | UNIT |

|                       |                                              | 8 PINS | 8 PINS |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 105.3  | 157.2  | °C/W |

| $R_{\theta JC(top)}$  | Junction-to-case (top) thermal resistance    | 50.3   | 49.9   | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 55.8   | 77.1   | °C/W |

| ΨJT                   | Junction-to-top characterization parameter   | 6.8    | 4.7    | °C/W |

| ΨЈВ                   | Junction-to-board characterization parameter | 54.7   | 75.8   | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | N/A    | N/A    | °C/W |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

# 6.5 Electrical Characteristics

Unless otherwise specified,  $V_{IN}$  = 12V,  $R_{FA}$  = 40k\Omega,  $T_{J}$  = 25°C

|                                                                | PARAMETER                                            | TEST CONDITIONS                                                                             | MIN    | ТҮР             | MAX    | UNIT   |

|----------------------------------------------------------------|------------------------------------------------------|---------------------------------------------------------------------------------------------|--------|-----------------|--------|--------|

|                                                                |                                                      | $V_{COMP} = 1.4V, 2.97 \le V_{IN} \le 40V$                                                  | 1.2416 | 1.26            | 1.2843 |        |

| $V_{FB}$                                                       | Feedback Voltage                                     | $V_{COMP} = 1.4V, 2.97 \le V_{IN} \le 40V, -40^{\circ}C$ $\le T_J \le 125^{\circ}C$         | 1.228  |                 | 1.292  | V      |

| $\Delta V_{\text{LINE}}$                                       | Feedback Voltage Line<br>Regulation                  | $2.97 \le V_{IN} \le 40V$                                                                   |        | 0.001           |        | %/V    |

| $\Delta V_{LOAD}$                                              | Output Voltage Load<br>Regulation                    | I <sub>EAO</sub> Source/Sink                                                                |        |                 | ±0.5   | %/A    |

| V                                                              | Input Undervoltage                                   |                                                                                             |        | 2.85            |        | V      |

| V <sub>UVLO</sub>                                              | UVLO Lock-out                                        | $-40^{\circ}C \le T_{J} \le 125^{\circ}C$                                                   |        |                 | 2.97   | v      |

| V <sub>UV(HYS)</sub> Input Undervoltage<br>Lock-out Hysteresis |                                                      |                                                                                             | 170    |                 | mV     |        |

|                                                                | $-40^{\circ}C \le T_{J} \le 125^{\circ}C$            | 130                                                                                         |        | 210             | mv     |        |

| -                                                              | Nominal Switching<br>Frequency                       | $R_{FA} = 40K\Omega$                                                                        |        | 400             |        |        |

| Fnom                                                           |                                                      | $R_{FA} = 40K\Omega$ , $-40^{\circ}C \le T_{J} \le 125^{\circ}C$                            | 350    |                 | 440    | kHz    |

| R <sub>DS1 (ON)</sub>                                          | Driver Switch On<br>Resistance (top)                 | I <sub>DR</sub> = 0.2A, V <sub>IN</sub> = 5V                                                |        | 16              |        | Ω      |

| R <sub>DS2 (ON)</sub>                                          | Driver Switch On<br>Resistance (bottom)              | I <sub>DR</sub> = 0.2A                                                                      |        | 4.5             |        | 52     |

| 17                                                             | Maximum Drive Voltage                                | V <sub>IN</sub> < 7.2V                                                                      |        | V <sub>IN</sub> |        | V      |

| V <sub>DR (max)</sub>                                          | Swing <sup>(1)</sup>                                 | V <sub>IN</sub> ≥ 7.2V                                                                      |        | 7.2             |        | v      |

| D <sub>max</sub>                                               | Maximum Duty Cycle <sup>(2)</sup>                    |                                                                                             |        | 100%            |        |        |

|                                                                | Minimum On Time                                      |                                                                                             |        | 325             |        |        |

| T <sub>min</sub> (on)                                          | Minimum On Time                                      | $-40^{\circ}C \le T_{J} \le 125^{\circ}C$                                                   | 210    |                 | 600    | ns     |

|                                                                | Supply Current (non-                                 | See <sup>(3)</sup>                                                                          |        | 2.7             |        |        |

| ISUPPLY                                                        | switching)                                           | See $^{(3)}$ , -40°C $\leq$ T <sub>J</sub> $\leq$ 125°C                                     |        |                 | 3.3    | mA     |

|                                                                | Ouissesst Oursest in                                 | $V_{FA/SD} = 5V$ <sup>(4)</sup> , $V_{IN} = 5V$                                             |        | 5               |        |        |

| lQ                                                             | I <sub>Q</sub> Quiescent Current in<br>Shutdown Mode | $V_{FA/SD} = 5V$ <sup>(4)</sup> , $V_{IN} = 5V$ , $-40^{\circ}C \le T_{J} \le 125^{\circ}C$ |        |                 | 10     | μA     |

| \ <i>\</i>                                                     | Current Sense                                        | V <sub>IN</sub> = 5V                                                                        | 135    | 156             | 180    |        |

| V <sub>SENSE</sub>                                             | Threshold Voltage                                    | $V_{IN} = 5V, -40^{\circ}C \le T_J \le 125^{\circ}C$                                        | 125    |                 | 190    | mV     |

| \ <i>\</i>                                                     | Short-Circuit Current                                | V <sub>IN</sub> = 5V                                                                        |        | 343             |        |        |

| V <sub>SC</sub>                                                | Limit Sense Voltage                                  | $V_{IN} = 5V, -40^{\circ}C \le T_J \le 125^{\circ}C$                                        | 250    |                 | 415    | 415 mV |

(1) The voltage on the drive pin, V<sub>DR</sub> is equal to the input voltage when input voltage is less than 7.2 V. V<sub>DR</sub> is equal to 7.2 V when the input voltage is greater than or equal to 7.2 V.

- (3) For this test, the FA/SD pin is pulled to ground using a 40-K resistor.

- (4) For this test, the FA/SD pin is pulled to 5 V using a 40-K resistor.

<sup>(2)</sup> The limits for the maximum duty cycle can not be specified since the part does not permit less than 100% maximum duty cycle operation.

### **Electrical Characteristics (continued)**

Unless otherwise specified,  $V_{IN}$  = 12V,  $R_{FA}$  = 40k $\Omega$ ,  $T_J$  = 25°C

|                       | PARAMETER                                                                            | TEST CONDITIONS                                                                                | MIN  | TYP  | MAX  | UNIT |

|-----------------------|--------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|------|------|------|------|

| V                     | Internal Compensation                                                                | V <sub>IN</sub> = 5V                                                                           |      | 92   |      |      |

| V <sub>SL</sub>       | Ramp Voltage                                                                         | $V_{IN} = 5V, -40^{\circ}C \le T_J \le 125^{\circ}C$                                           | 52   |      | 132  | mV   |

| √ <sub>SL</sub> ratio | V <sub>SL</sub> /V <sub>SENSE</sub>                                                  |                                                                                                | 0.30 | 0.49 | 0.70 |      |

|                       |                                                                                      | $V_{COMP} = 1.4V$                                                                              | 32   | 50   |      |      |

|                       |                                                                                      | $V_{COMP} = 1.4V, -40^{\circ}C \le T_{J} \le 125^{\circ}C$                                     | 25   |      |      |      |

|                       | Output Over-voltage                                                                  | VSSOP Package                                                                                  |      |      | 78   |      |

| V <sub>OVP</sub>      | Protection (with respect to feedback voltage) <sup>(5)</sup>                         | VSSOP Package, −40°C ≤ T <sub>J</sub> ≤ 125°C                                                  |      |      | 85   | mV   |

|                       | <b>G</b> <i>'</i>                                                                    | SOIC Package                                                                                   |      |      | 78   |      |

|                       |                                                                                      | SOIC Package, −40°C ≤ T <sub>J</sub> ≤ 125°C                                                   |      |      | 100  |      |

| V <sub>OVP(HYS)</sub> | Output Over-Voltage                                                                  | $V_{COMP} = 1.4V$                                                                              |      | 60   |      |      |

|                       | Protection Hysteresis <sup>(5)</sup>                                                 | $V_{COMP} = 1.4V, -40^{\circ}C \le T_{J} \le 125^{\circ}C$                                     | 20   |      | 110  | mV   |

| Cm                    | Error Amplifier                                                                      | $V_{COMP} = 1.4V, I_{EAO} = 100\mu A$<br>(Source/Sink)                                         | 600  | 800  | 1000 |      |

| Gm Transconductance   | $V_{COMP} = 1.4V, I_{EAO} = 100\mu A$<br>(Source/Sink), -40°C $\leq T_J \leq 125$ °C | 365                                                                                            |      | 1265 | μS   |      |

| ٨                     | Error Amplifier Voltage                                                              | V <sub>COMP</sub> = 1.4V, I <sub>EAO</sub> = 100µA<br>(Source/Sink)                            |      | 38   |      |      |

| A <sub>VOL</sub> Gain | $V_{COMP} = 1.4V, I_{EAO} = 100\mu A$<br>(Source/Sink), -40°C $\leq T_J \leq 125$ °C | 26                                                                                             |      | 44   | V/V  |      |

|                       | Error Amplifier Output<br>Current (Source/ Sink)                                     | Source, $V_{COMP} = 1.4V$ , $V_{FB} = 0V$                                                      | 80   | 110  | 140  | μΑ   |

|                       |                                                                                      | Source, $V_{COMP} = 1.4V$ , $V_{FB} = 0V$ , $-40^{\circ}C \le T_J \le 125^{\circ}C$            | 50   |      | 180  |      |

| EAO                   |                                                                                      | Sink, $V_{COMP} = 1.4V$ , $V_{FB} = 1.4V$                                                      | -100 | -140 | -180 |      |

|                       |                                                                                      | Sink, $V_{COMP} = 1.4V$ , $V_{FB} = 1.4V$ , $\neg 40^{\circ}C \le T_{J} \le 125^{\circ}C$      | -85  |      | -185 | μA   |

| V <sub>EAO</sub>      | Error Amplifier Output<br>Voltage Swing                                              | Upper Limit, $V_{FB} = 0V$ , COMP Pin = Floating                                               |      | 2.2  |      | V    |

|                       |                                                                                      | Upper Limit, $V_{FB} = 0V$ , COMP Pin =<br>Floating, $-40^{\circ}C \le T_{J} \le 125^{\circ}C$ | 1.8  |      | 2.4  | V    |

|                       |                                                                                      | Lower Limit, $V_{FB} = 1.4V$                                                                   |      | 0.56 |      |      |

|                       |                                                                                      | Lower Limit, $V_{FB} = 1.4V$ , $-40^{\circ}C \le T_{J} \le 125^{\circ}C$                       | 0.2  |      | 1.0  | V    |

| Г <sub>SS</sub>       | Internal Soft-Start Delay                                                            | $V_{FB}$ = 1.2V, $V_{COMP}$ = Floating                                                         |      | 4    |      | ms   |

| Г <sub>г</sub>        | Drive Pin Rise Time                                                                  | Cgs = 3000pf, $V_{DR} = 0$ to 3V                                                               |      | 25   |      | ns   |

| Г <sub>f</sub>        | Drive Pin Fall Time                                                                  | Cgs = 3000pf, $V_{DR} = 0$ to 3V                                                               |      | 25   |      | ns   |

|                       | Shutdown threshold (6)                                                               | Output = High                                                                                  |      | 1.27 |      | V    |

| ,                     |                                                                                      | Output = High, $-40^{\circ}C \le T_{J} \le 125^{\circ}C$                                       |      |      | 1.4  | V    |

| / <sub>SD</sub>       |                                                                                      | Output = Low                                                                                   |      | 0.65 |      |      |

|                       |                                                                                      | Output = Low, $-40^{\circ}C \le T_{J} \le 125^{\circ}C$                                        |      |      | 0.3  | V    |

|                       | Chutdown Die Ownerst                                                                 | V <sub>SD</sub> = 5V                                                                           |      | -1   |      | ^    |

| SD                    | Shutdown Pin Current                                                                 | V <sub>SD</sub> = 0V                                                                           |      | +1   |      | μA   |

| FB                    | Feedback Pin Current                                                                 |                                                                                                |      | 15   |      | nA   |

| Г <sub>SD</sub>       | Thermal Shutdown                                                                     |                                                                                                |      | 165  |      | °C   |

| T <sub>sh</sub>       | Thermal Shutdown<br>Hysteresis                                                       |                                                                                                |      | 10   |      | °C   |

(5) The over-voltage protection is specified with respect to the feedback voltage. This is because the over-voltage protection tracks the feedback voltage. The over-voltage protection threshold is given by adding the feedback voltage, V<sub>FB</sub> to the over-voltage protection specification.

(6) The FA/SD pin should be pulled to V<sub>IN</sub> through a resistor to turn the regulator off. The voltage on the FA/SD pin must be above the maximum limit for Output = High to keep the regulator off and must be below the limit for Output = Low to keep the regulator on.

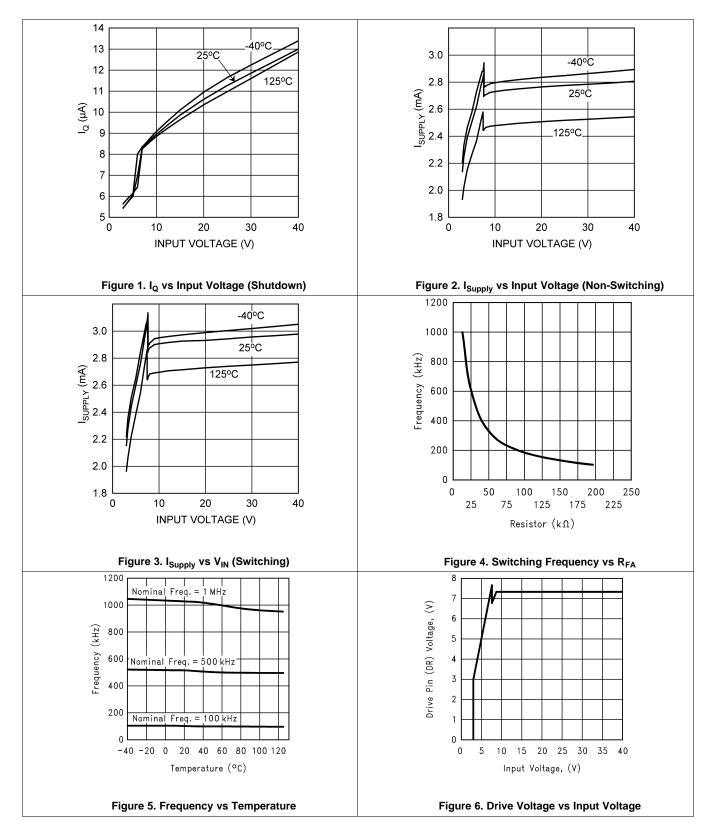

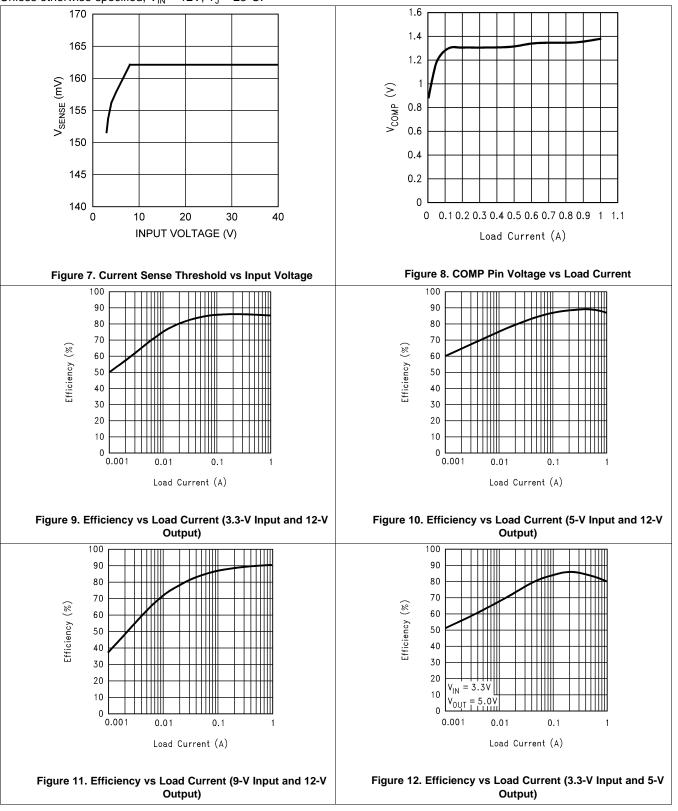

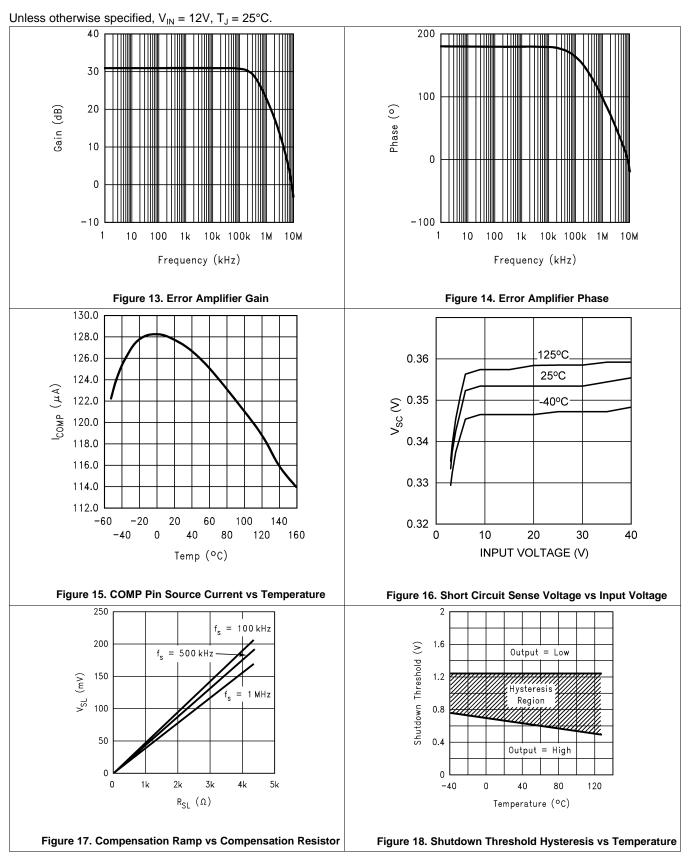

#### 6.6 Typical Characteristics

Unless otherwise specified,  $V_{IN} = 12V$ ,  $T_J = 25^{\circ}C$ .

# **Typical Characteristics (continued)**

Unless otherwise specified,  $V_{IN} = 12V$ ,  $T_J = 25^{\circ}C$ .

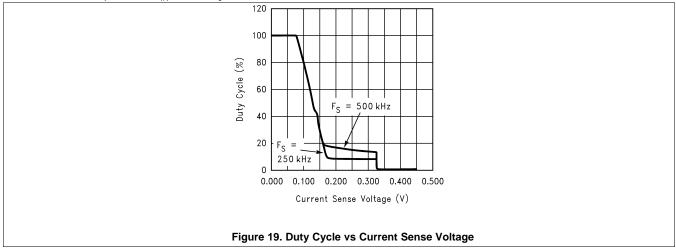

### **Typical Characteristics (continued)**

TEXAS INSTRUMENTS

www.ti.com

# **Typical Characteristics (continued)**

# LM3478 JAJS711X – JULY 2000 – REVISED JUNE 2017

# 7 Detailed Description

# 7.1 Overview

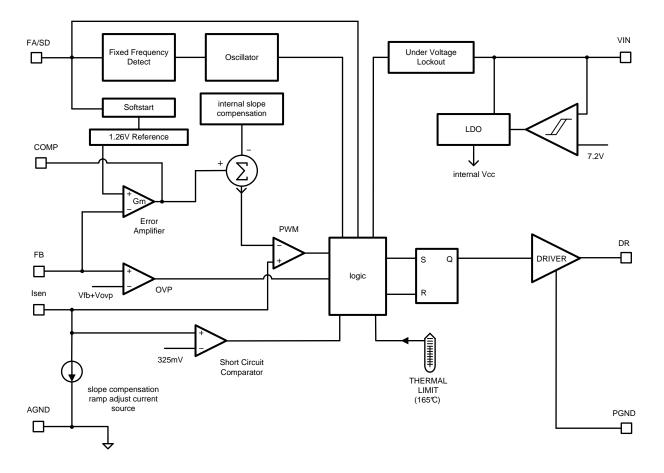

The LM3478 device uses a fixed frequency, Pulse Width Modulated (PWM) current mode control architecture. The *Functional Block Diagram* shows the basic functionality. In a typical application circuit, the peak current through the external MOSFET is sensed through an external sense resistor. The voltage across this resistor is fed into the I<sub>SEN</sub> pin. This voltage is fed into the positive input of the PWM comparator. The output voltage is also sensed through an external feedback resistor divider network and fed into the slope compensation ramp and fed into the negative input of the PWM comparator. At the start of any switching cycle, the oscillator sets the RS latch using the switch logic block. This forces a high signal on the DR pin (gate of the external MOSFET) and the external MOSFET turns on. When the voltage on the positive input of the PWM comparator exceeds the negative input, the RS latch is reset and the external MOSFET turns off.

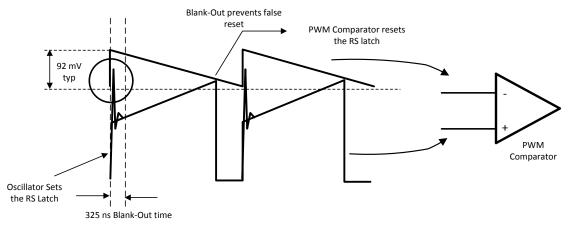

The voltage sensed across the sense resistor generally contains spurious noise spikes, as shown in Figure 20. These spikes can force the PWM comparator to reset the RS latch prematurely. To prevent these spikes from resetting the latch, a blank-out circuit inside the IC prevents the PWM comparator from resetting the latch for a short duration after the latch is set. This duration is about 325 ns and is called the blanking interval and is specified as minimum on-time in the Electrical Characteristics section. Under extremely light-load or no-load conditions, the energy delivered to the output capacitor when the external MOSFET in on during the blanking interval is more than what is delivered to the load. An over-voltage comparator inside the LM3478 prevents the output voltage from rising under these conditions. The over-voltage comparator senses the feedback (FB pin) voltage and resets the RS latch. The latch remains in reset state until the output decays to the nominal value.

Figure 20. Basic Operation of the PWM Comparator

# 7.2 Functional Block Diagram

# 7.3 Feature Description

### 7.3.1 Overvoltage Protection

The LM3478 has over voltage protection (OVP) for the output voltage. OVP is sensed at the feedback pin (pin 3). If at anytime the voltage at the feedback pin rises to  $V_{FB}$ +  $V_{OVP}$ , OVP is triggered. See *Electrical Characteristics* section for limits on  $V_{FB}$  and  $V_{OVP}$ .

OVP will cause the drive pin to go low, forcing the power MOSFET off. With the MOSFET off, the output voltage will drop. The LM3478 will begin switching again when the feedback voltage reaches  $V_{FB}$  + ( $V_{OVP}$  -  $V_{OVP(HYS)}$ ). See *Electrical Characteristics* for limits on  $V_{OVP(HYS)}$ .

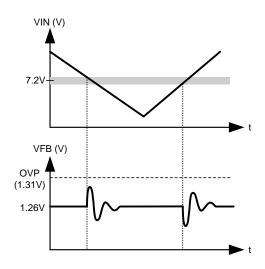

OVP can be triggered if the unregulated input voltage crosses 7.2 V, the output voltage will react as shown in Figure 21. The internal bias of the LM3478 comes from either the internal LDO as shown in the block diagram or the voltage at the Vin pin is used directly. At Vin voltages lower than 7.2 V the internal IC bias is the Vin voltage and at voltages above 7.2V the internal LDO of the LM3478 provides the bias. At the switch over threshold at 7.2 V a sudden small change in bias voltage is seen by all the internal blocks of the LM3478. The control voltage shifts because of the bias change, the PWM comparator tries to keep regulation. To the PWM comparator, the scenario is identical to a step change in the load current, so the response at the output voltage is the same as would be observed in a step load change. Hence, the output voltage overshoot here can also trigger OVP. The LM3478 will regulate in hysteretic mode for several cycles, or may not recover and simply stay in hysteretic mode until the load current drops or Vin is not crossing the 7.2 V threshold anymore. Note that the output is still regulated in hysteretic mode.

#### Feature Description (continued)

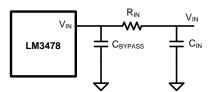

Depending on the requirements of the application, there is some influence one has over this effect. The threshold of 7.2 V can be shifted to higher voltages by adding a resistor in series with  $V_{IN}$ . In case  $V_{IN}$  is right at the threshold of 7.2 V, the threshold could cross over and over due to some slight ripple on  $V_{IN}$ . To minimize the effect on the output voltage one can filter the  $V_{IN}$  pin with an RC filter.

#### Figure 21. The Feedback Voltage Experiences an Oscillation if the Input Voltage crosses the 7.2-V Internal Bias Threshold

#### 7.3.2 Slope Compensation Ramp

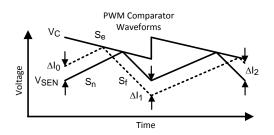

The LM3478 uses a current mode control scheme. The main advantages of current mode control are inherent cycle-by-cycle current limit for the switch and simpler control loop characteristics. It is also easy to parallel power stages using current mode control since current sharing is automatic. However, current mode control has an inherent instability for duty cycles greater than 50%, as shown in Figure 22.

A small increase in the load current causes the switch current to increase by  $\Delta I_0$ . The effect of this load change is  $\Delta I_1$ .

The two solid waveforms shown are the waveforms compared at the internal pulse width modulator, used to generate the MOSFET drive signal. The top waveform with the slope  $S_e$  is the internally generated control waveform V<sub>C</sub>. The bottom waveform with slopes  $S_n$  and  $S_f$  is the sensed inductor current waveform V<sub>SEN</sub>.

# Figure 22. Sub-Harmonic Oscillation for D>0.5 and Compensation Ramp to Avoid Sub-Harmonic Oscillation

Sub-harmonic Oscillation can be easily understood as a geometric problem. If the control signal does not have slope, the slope representing the inductor current ramps up until the control signal is reached and then slopes down again. If the duty cycle is above 50%, any perturbation will not converge but diverge from cycle to cycle and causes sub-harmonic oscillation.

It is apparent that the difference in the inductor current from one cycle to the next is a function of  $S_n$ ,  $S_f$  and  $S_e$  as shown in Equation 1.

Copyright © 2000-2017, Texas Instruments Incorporated

14

#### Feature Description (continued)

$$\Delta I_n = \frac{S_f - S_e}{S_p + S_p} \Delta I_{n-1}$$

Hence, if the quantity

$$(S_f - S_e)/(S_n + S_e)$$

is greater than 1, the inductor current diverges and sub-harmonic oscillation results. This counts for all current mode topologies. The LM3478 has some internal slope compensation  $V_{SL}$  which is enough for many applications above 50% duty cycle to avoid sub-harmonic oscillation.

For boost applications, the slopes S<sub>e</sub>, S<sub>f</sub> and S<sub>n</sub> can be calculated with Equation 2, Equation 3, and Equation 4.

$$S_{e} = V_{SL} \times f_{s}$$

$$S_{f} = R_{sen} \times (V_{OUT} - V_{IN})/L$$

$$S_{n} = V_{IN} \times R_{sen}/L$$

(2)

(3)

(3)

(4)

When  $S_e$  increases, then the factor that determines if sub-harmonic oscillation will occur decreases. When the duty cycle is greater than 50%, and the inductance becomes less, the factor increases.

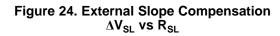

For more flexibility, slope compensation can be increased by adding one external resistor,  $R_{SL}$ , in the  $I_{SEN}$ 's path. Figure 23 shows the setup. The externally generated slope compensation is then added to the internal slope compensation of the LM3478. When using external slope compensation, the formula for  $S_e$  becomes:

$$S_{e} = (V_{SL} + (K \times R_{SL})) \times f_{s}$$

(5)

A typical value for factor K is 40 µA.

DR

₩

$\mathsf{R}_{\mathsf{SL}}$

LM3478

ISEN

$K = \Delta V_{SL} / R_{SL}$

The factor changes with switching frequency. Figure 24 is used to determine the factor K for individual applications and Equation 6 gives the factor K.

It is a good design practice to only add as much slope compensation as needed to avoid sub-harmonic oscillation. Additional slope compensation minimizes the influence of the sensed current in the control loop. With very large slope compensation the control loop characteristics are similar to a voltage mode regulator which compares the error voltage to a saw tooth waveform rather than the inductor current.

Figure 23. Adding External Slope Compensation

$\mathsf{R}_{\mathsf{SEN}}$

Copyright © 2000-2017, Texas Instruments Incorporated

www.ti.com

(1)

(6)

$R_{FA} =$

(7)

#### Feature Description (continued)

#### 7.3.3 Frequency Adjust/Shutdown

The switching frequency of the LM3478 can be adjusted between 100 kHz and 1 MHz using a single external resistor. This resistor must be connected between FA/SD pin and ground, as shown in Figure 25. To determine the value of the resistor required for a desired switching frequency, refer to *Typical Characteristics* or use Equation 7:

4.503 x 10<sup>11</sup> x

$$f_{S}^{-1.26}$$

FA/SD  $R_{FA}$

Figure 25. Frequency Adjust

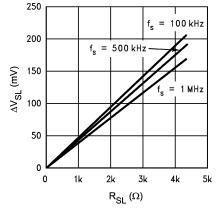

The FA/SD pin also functions as a shutdown pin. If a high signal (>1.35 V) appears on the FA/SD pin, the LM3478 stops switching and goes into a low current mode. The total supply current of the IC reduces to less than 10  $\mu$ A under these conditions. Figure 26 shows implementation of the shutdown function when operating in frequency adjust mode. In this mode a high signal for more than 30 us shuts down the IC. However, the voltage on the FA/SD pin should be always less than the absolute maximum of 7 V to avoid any damage to the device.

Figure 26. Shutdown Operation in Frequency Adjust Mode

#### 7.3.4 Short-Circuit Protection

When the voltage across the sense resistor measured on the I<sub>SEN</sub> pin exceeds 343 mV, short circuit current limit protection gets activated. A comparator inside the LM3478 reduces the switching frequency by a factor of 5 and maintains this condition until the short is removed. In normal operation the sensed current will trigger the power MOSFET to turn off. During the blanking interval the PWM comparator will not react to an over current so that this additional 343 mV current limit threshold is implemented to protect the device in a short circuit or severe overload condition.

### 7.4 Device Functional Modes

The device is set to run as soon as the input voltage crosses above the UVLO set point and at a frequency set according to the FA/SD pin pulldown resistor. If the FA/SD pin is pulled high, the LM3481 enters shut-down mode.

(8)

(9)

#### Application and Implementation 8

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

#### 8.1 Application Information

The LM3478 may be operated in either the continuous conduction mode (CCM) or the discontinuous current conduction mode (DCM). The following applications are designed for the CCM operation. This mode of operation has higher efficiency and usually lower EMI characteristics than the DCM.

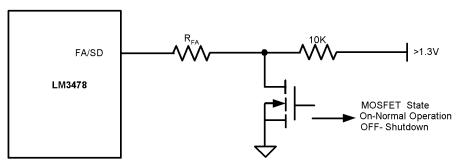

#### 8.2 Typical Applications

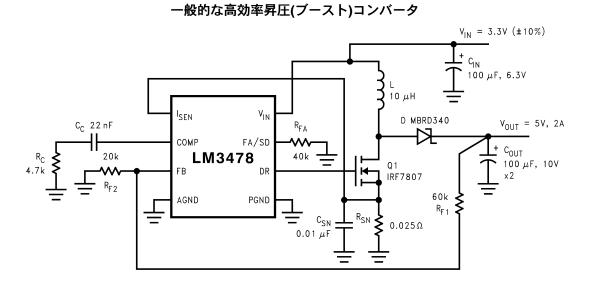

#### 8.2.1 Typical High Efficiency Step-Up (Boost) Converter

C<sub>C</sub> 22 nF

204

ISEN

COME

R<sub>FA</sub>

40k

$V_{\rm IN}$

FA/SD

Figure 27. Typical High Efficiency Step-Up (Boost) Converter Schematic

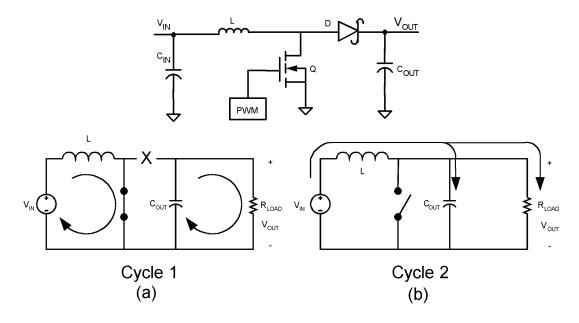

The boost converter converts a low input voltage into a higher output voltage. The basic configuration for a boost converter is shown in Figure 28. In the CCM (when the inductor current never reaches zero at steady state), the boost regulator operates in two states. In the first state of operation, MOSFET Q is turned on and energy is stored in the inductor. During this state, diode D is reverse biased and load current is supplied by the output capacitor, COUT.

In the second state, MOSFET Q is off and the diode is forward biased. The energy stored in the inductor is transferred to the load and the output capacitor. The ratio of the switch on time to the total period is the duty cycle D as shown in Equation 8.

$$D = 1 - (V_{in} / V_{out})$$

Including the voltage drop across the MOSFET and the diode the definition for the duty cycle is shown in Equation 9.

$$D = 1 - ((V_{in} - V_q)/(V_{out} + V_d))$$

$V_d$  is the forward voltage drop of the diode and  $V_d$  is the voltage drop across the MOSFET when it is on.

$V_{IN} = 3.3V (\pm 10\%)$

$V_{OUT} = 5V, 2A$

C<sub>OUT</sub>

CIN 100 µF, 6.3V

10 µH

D MBRD340

# **Typical Applications (continued)**

- A. First Cycle Operation

- B. Second Cycle of Operation

#### Figure 28. Simplified Boost Converter

#### 8.2.1.1 Design Requirements

To properly size the components for the application, the designer needs the following parameters: input voltage range, output voltage, output current range, and required switching frequency. These four main parameters affect the choices of component available to achieve a proper system behavior.

For the power supply, the input impedance of the supply rail should be low enough that the input current transient does not drop below the UVLO value. The factors determining the choice of inductor used should be the average inductor current, and the inductor current ripple. If the switching frequency is set high, the converter can be operated with very small inductor values. The maximum current that can be delivered to the load is set by the sense resistor, RSEN. Current limit occurs when the voltage generated across the sense resistor equals the current sense threshold voltage, VSENSE. Also, a resistor RSL adds additional slope compensation, if required.

The following sections describe the design requirements for a typical LM3478 boost application.

#### 8.2.1.2 Detailed Design Procedure

#### 8.2.1.2.1 Custom Design with WEBENCH Tools

Click here to create a custom design using the LM3478 device with the WEBENCH® Power Designer.

- 1. Start by entering your  $V_{IN}$ ,  $V_{OUT}$  and  $I_{OUT}$  requirements.

- 2. Optimize your design for key parameters like efficiency, footprint and cost using the optimizer dial and compare this design with other possible solutions from Texas Instruments.

- 3. WEBENCH Power Designer provides you with a customized schematic along with a list of materials with real time pricing and component availability.

- 4. In most cases, you will also be able to:

- Run electrical simulations to see important waveforms and circuit performance,

- Run thermal simulations to understand the thermal performance of your board,

- Export your customized schematic and layout into popular CAD formats,

- Print PDF reports for the design, and share your design with colleagues.

# **Typical Applications (continued)**

5. Get more information about WEBENCH tools at www.ti.com/webench.

#### 8.2.1.2.2 Power Inductor Selection

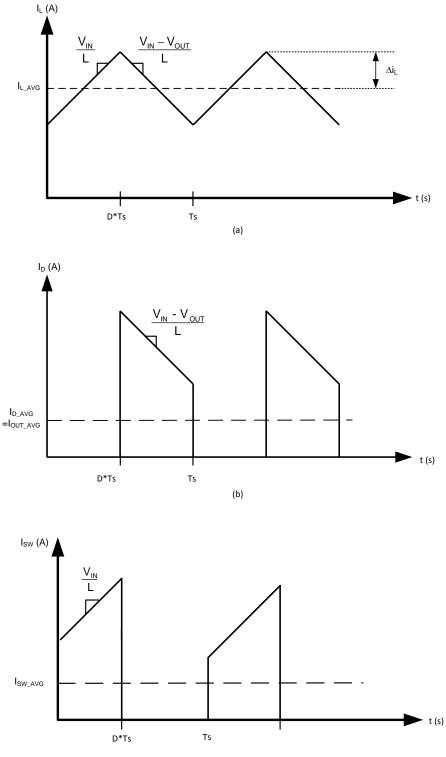

The inductor is one of the two energy storage elements in a boost converter. Figure 29 shows how the inductor current varies during a switching cycle. The current through an inductor is quantified using Equation 10, which shows the relationship of L,  $I_L$  and  $V_L$ .

$$V_{L}(t) = L \frac{di_{L}(t)}{dt}$$

(10)

The important quantities in determining a proper inductance value are  $I_L$  (the average inductor current) and  $\Delta I_L$  (the inductor current ripple). If  $\Delta I_L$  is larger than  $I_L$ , the inductor current will drop to zero for a portion of the cycle and the converter will operate in the DCM. All the analysis in this datasheet assumes operation in the CCM. To operate in the CCM, the following condition must be met by using Equation 11.

$$L > \frac{D(1-D)V_{\text{IN}}}{2I_{\text{OUT}}f_{\text{S}}}$$

(11)

Choose the minimum  $I_{OUT}$  to determine the minimum inductance value. A common choice is to set  $\Delta I_L$  to 30% of  $I_L$ . Choosing an appropriate core size for the inductor involves calculating the average and peak currents expected through the inductor. Use Equation 12, Equation 13, and Equation 14 to the peak inductor current in a boost converter.

| $I_{LPEAK}$ = Average $I_{L(max)}$ + $\Delta I_{L(max)}$        | (12) |

|-----------------------------------------------------------------|------|

| Average $I_{L(max)} = I_{out} / (1-D)$                          | (13) |

| $\Delta I_{L(max)} = D \times V_{in} / (2 \times f_s \times L)$ | (14) |

An inductor size with ratings higher than these values has to be selected. If the inductor is not properly rated, saturation will occur and may cause the circuit to malfunction.

The LM3478 can be set to switch at very high frequencies. When the switching frequency is high, the converter can be operated with very small inductor values. The LM3478 senses the peak current through the switch which is the same as the peak inductor current as calculated in the previous equation.

Copyright © 2000-2017, Texas Instruments Incorporated

**ISTRUMENTS**

# **Typical Applications (continued)**

(C)

Figure 29. Inductor Current and Diode Current

# Typical Applications (continued)

### 8.2.1.2.3 Programming the Output Voltage

The output voltage can be programmed using a resistor divider between the output and the FB pin. The resistors are selected such that the voltage at the FB pin is 1.26 V. Pick  $R_{F1}$  (the resistor between the output voltage and the feedback pin) and  $R_{F2}$  (the resistor between the feedback pin and ground) can be selected using the following equation,

$$R_{F2} = (1.26 \text{ V x } R_{F1}) / (V_{out} - 1.26 \text{ V})$$

A 100-pF capacitor may be connected between the feedback and ground pins to reduce noise.

### 8.2.1.2.4 Setting the Current Limit

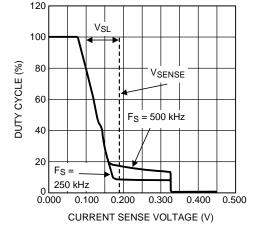

The maximum amount of current that can be delivered to the load is set by the sense resistor,  $R_{SEN}$ . Current limit occurs when the voltage that is generated across the sense resistor equals the current sense threshold voltage,  $V_{SENSE}$ . When this threshold is reached, the switch will be turned off until the next cycle. Limits for  $V_{SENSE}$  are specified in the electrical characteristics section.  $V_{SENSE}$  represents the maximum value of the internal control signal  $V_{CS}$  as shown in Figure 30. This control signal, however, is not a constant value and changes over the course of a period as a result of the internal compensation ramp ( $V_{SL}$ ). Therefore the current limit threshold will also change. The actual current limit threshold is a function of the sense voltage ( $V_{SENSE}$ ) and the internal compensation ramp:

$$R_{SEN} \times ISW_{LIMIT} = VCS_{MAX} = V_{SENSE} - (D \times V_{SL})$$

Where ISW<sub>LIMIT</sub> is the peak switch current limit, defined by Equation 17.

Figure 30. Current Sense Voltage vs Duty Cycle

Figure 30 shows how V<sub>CS</sub> (and current limit threshold voltage) change with duty cycle. The curve is equivalent to the internal compensation ramp slope (S<sub>e</sub>) and is bounded at low duty cycle by V<sub>SENSE</sub>, shown as a dotted line. As duty cycle increases, the control voltage is reduced as V<sub>SL</sub> ramps up. The graph also shows the short circuit current limit threshold of 343 mV (typical) during the 325 ns (typical) blanking time. For higher frequencies this fixed blanking time obviously occupies more duty cycle, percentage wise. Since current limit threshold varies with duty cycle, the use Equation 17 to select R<sub>SEN</sub> and set the desired current limit threshold:

$$R_{SEN} = \frac{V_{SENSE} - (D \times V_{SL})}{ISW_{LIMIT}}$$

(17)

The numerator of Equation 17 is  $V_{CS}$ , and  $ISW_{LIMIT}$  using Equation 18.

$$ISW_{LIMIT} = \left[\frac{I_{OUT}}{(1-D)} + \frac{(D \times V_{IN})}{(2 \times f_S \times L)}\right]$$

(18)

(15)

(16)

#### **Typical Applications (continued)**

To avoid false triggering, the current limit value should have some margin above the maximum operating value, typically 120%. Values for both  $V_{SENSE}$  and  $V_{SL}$  are specified in *Electrical Characteristics*. However, calculating with the limits of these two specs could result in an unrealistically wide current limit or  $R_{SEN}$  range. Therefore, Equation 19 is recommended, using the  $V_{SL}$  ratio value given in *Electrical Characteristics*.

$$R_{SEN} = \frac{V_{SENSE} - (D \times V_{SENSE} \times V_{SL} ratio)}{ISW_{LIMIT}}$$

(19)

R<sub>SEN</sub> is part of the current mode control loop and has some influence on control loop stability. Therefore, once the current limit threshold is set, loop stability must be verified. As described in the slope compensation section, Equation 20 must hold true for a current mode converter to be stable.

$$S_{f} - S_{e} < S_{n} + S_{e}$$

<sup>(20)</sup>

To verify that this equation holds true, use Equation 21.

$$R_{SEN} < \frac{2 x V_{SL} x f_{S} x L}{V_{0} - (2 x V_{IN})}$$

(21)

If the selected RSEN is greater than this value, additional slope compensation must be added to ensure stability, as described in the section below.

#### 8.2.1.2.5 Current Limit with External Slope Compensation

$R_{SL}$  is used to add additional slope compensation when required. It is not necessary in most designs and  $R_{SL}$  should be no larger than necessary. Select RSL according to Equation 22.

$$R_{SL} > \frac{\frac{R_{SEN} \times (Vo - 2V_{IN})}{2 \times f_S \times L} - V_{SL}}{40 \ \mu A}$$

(22)

Where R<sub>SEN</sub> is the selected value based on current limit. With RSL installed, the control signal includes additional external slope to stabilize the loop, which will also have an effect on the current limit threshold. Therefore, the current limit threshold must be re-verified, as illustrated in Equation 23, Equation 24, and Equation 25 below.

$$V_{CS} = V_{SENSE} - (D \times (V_{SL} + \Delta V_{SL}))$$

(23)

Where  $\Delta V_{SL}$  is the additional slope compensation generated as discussed in the slope compensation ramp section and calculated using Equation 24.

$$\Delta V_{SL} = 40 \ \mu A \ x \ R_{SL}$$

(24)

This changes the equation for current limit (or R<sub>SEN</sub>) as shown in Equation 25.

$$ISW_{LIMIT} = \frac{V_{SENSE} - (D x(V_{SL} + \Delta V_{SL}))}{R_{SEN}}$$

(25)

The  $R_{SEN}$  and  $R_{SL}$  values may have to be calculated iteratively in order to achieve both the desired current limit and stable operation. In some designs  $R_{SL}$  can also help to filter noise on the  $I_{SEN}$  pin.

If the inductor is selected such that ripple current is the recommended 30% value, and the current limit threshold is 120% of the maximum peak, a simpler method can be used to determine  $R_{SEN}$ . Equation 26 below will provide optimum stability without RSL, provided that the above 2 conditions are met.

$$R_{SEN} = \frac{V_{SENSE}}{ISW_{LIMIT} + \left(\frac{Vo - Vi}{L \times f_{S}}\right) \times D}$$

(26)

#### 8.2.1.2.6 Power Diode Selection

Observation of the boost converter circuit shows that the average current through the diode is the average load current, and the peak current through the diode is the peak current through the inductor. The diode should be rated to handle more than its peak current. The peak diode current can be calculated using Equation 27.

$$I_{D(Peak)} = I_{OUT} / (1-D) + \Delta I_{L}$$

(27)

### **Typical Applications (continued)**

Thermally the diode must be able to handle the maximum average current delivered to the output. The peak reverse voltage for boost converters is equal to the regulated output voltage. The diode must be capable of handling this voltage. To improve efficiency, a low forward drop schottky diode is recommended.

#### 8.2.1.2.7 Power MOSFET Selection

The drive pin of the LM3478 must be connected to the gate of an external MOSFET. The drive pin (DR) voltage depends on the input voltage (see *Typical Characteristics*). In most applications, a logic level MOSFET can be used. For very low input voltages, a sub logic level MOSFET should be used. The selected MOSFET has a great influence on the system efficiency. The critical parameters for selecting a MOSFET are:

- 1. Minimum threshold voltage, V<sub>TH</sub>(MIN)

- 2. On-resistance, R<sub>DS(ON)</sub>

- 3. Total gate charge, Q<sub>g</sub>

- 4. Reverse transfer capacitance, C<sub>RSS</sub>

- 5. Maximum drain to source voltage, V<sub>DS(MAX)</sub>

The off-state voltage of the MOSFET is approximately equal to the output voltage. Vds(max) must be greater than the output voltage. The power losses in the MOSFET can be categorized into conduction losses and switching losses.  $R_{DS(ON)}$  is needed to estimate the conduction losses, Pcond:

$Pcond = I^2 \times R_{DS(ON)} \times D$

(28)

The temperature effect on the R<sub>DS(ON)</sub> usually is quite significant. Assume 30% increase at hot.

For the current I in Equation 28 the average inductor current may be used.

Especially at high switching frequencies the switching losses may be the largest portion of the total losses.

The switching losses are very difficult to calculate due to changing parasitics of a given MOSFET in operation. Often the individual MOSFET's data sheet does not give enough information to yield a useful result. Equation 29 and Equation 30 give a rough idea how the switching losses are calculated:

$$P_{SW} = \frac{I_{Lmax} \times V_{out}}{2} \times f_{SW} \times (t_{LH} + t_{HL})$$

$$t_{LH} = \left(Qgd + \frac{Qgs}{2}\right) \times \frac{Rdr_{On}}{Vdr - Vgs_{th}}$$

(29)

(30)

#### 8.2.1.2.8 Input Capacitor Selection

.

Due to the presence of an inductor at the input of a boost converter, the input current waveform is continuous and triangular as shown in Figure 29. The inductor ensures that the input capacitor sees fairly low ripple currents. However, as the input capacitor gets smaller, the input ripple goes up. The RMS current in the input capacitor is given using Equation 31.

$$I_{CIN(RMS)} = \Delta i_L / \sqrt{3} = \frac{1}{2\sqrt{3}} \left( \frac{V_{OUT} - V_{IN}}{V_{OUT} L f_S} \right) X V_{in}$$

(31)

The input capacitor should be capable of handling the RMS current. Although the input capacitor is not as critical in a boost application, low values can cause impedance interactions. Therefore a good quality capacitor should be chosen in the range of 10  $\mu$ F to 20  $\mu$ F. If a value lower than 10  $\mu$ F is used, then problems with impedance interactions or switching noise can affect the LM3478. To improve performance, especially with Vin below 8 volts, it is recommended to use a 20 Ohm resistor at the input to provide an RC filter. The resistor is placed in series with the VIN pin with only a bypass capacitor attached to the VIN pin directly (see Figure 31). A 0.1- $\mu$ F or 1- $\mu$ F ceramic capacitor is necessary in this configuration. The bulk input capacitor and inductor will connect on the other side of the resistor at the input power supply.

#### **Typical Applications (continued)**

Figure 31. Reducing IC Input Noise

#### 8.2.1.2.9 Output Capacitor Selection

The output capacitor in a boost converter provides all the output current when the inductor is charging. As a result it sees very large ripple currents. The output capacitor should be capable of handling the maximum RMS current. Equation 32 shows the RMS current in the output capacitor.

$$I_{\text{COUT(RMS)}} = \sqrt{(1-D) \left[ I_{\text{OUT}}^2 \frac{D}{(1-D)^2} + \frac{\Delta i_L^2}{3} \right]}$$

(32)

Where

$\Delta i_1$

$$=\frac{DV_{\rm IN}}{2Lf_{\rm S}}$$

(33)

The ESR and ESL of the capacitor directly control the output ripple. Use capacitors with low ESR and ESL at the output for high efficiency and low ripple voltage. Surface mount tantalums, surface mount polymer electrolytic, polymer tantalum, or multi-layer ceramic capacitors are recommended at the output.

For applications that require very low output voltage ripple, a second stage LC filter often is a good solution. Most of the time it is lower cost to use a small second Inductor in the power path and an additional final output capacitor than to reduce the output voltage ripple by purely increasing the output capacitor without an additional LC filter.

#### 8.2.1.2.10 Compensation

For detailed explanation on how to select the right compensation components to attach to the compensation pin for a boost topology, please see AN-1286 Compensation For The LM3748 Boost Controller SNVA067.

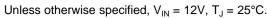

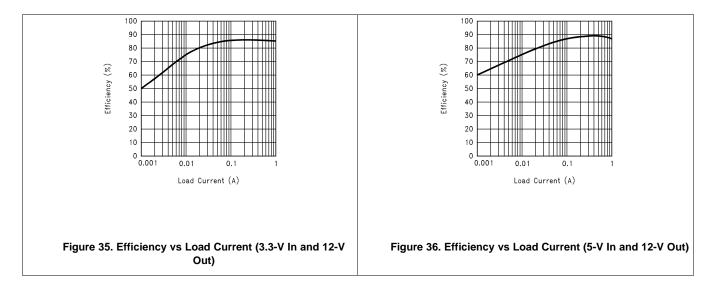

#### 100 100 90 90 80 80 70 70 (%) (%) 60 60 Efficiency Efficiency 50 50 40 40 30 30 20 20 10 10 V<sub>OUT</sub> = 5.0V 0 0 0.001 0.01 0. 0.001 0.01 0.1 Load Current (A) Load Current (A) Figure 32. Efficiency vs Load Current (9-V In and 12-V Out) Figure 33. Efficiency vs Load Current (3.3-V In and 5-V Out)

#### 8.2.1.3 Application Curves

### **Typical Applications (continued)**

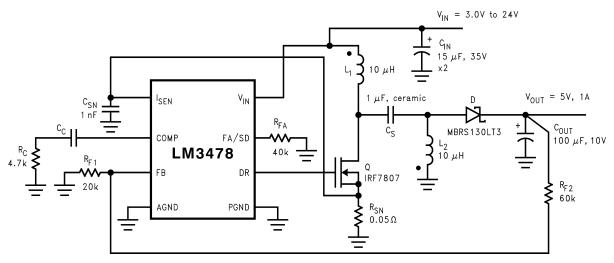

### 8.2.2 Typical SEPIC Converter

Figure 34. Typical SEPIC Converter

Since the LM3478 controls a low-side N-Channel MOSFET, it can also be used in SEPIC (Single Ended Primary Inductance Converter) applications. An example of a SEPIC using the LM3478 is shown in Figure 34. Note that the output voltage can be higher or lower than the input voltage. The SEPIC uses two inductors to step-up or step-down the input voltage. The inductors L1 and L2 can be two discrete inductors or two windings of a coupled inductor since equal voltages are applied across the inductor throughout the switching cycle. Using two discrete inductors allows use of catalog magnetics, as opposed to a custom inductor. The input ripple can be reduced along with size by using the coupled windings for L1 and L2.

Due to the presence of the inductor L1 at the input, the SEPIC inherits all the benefits of a boost converter. One main advantage of a SEPIC over a boost converter is the inherent input to output isolation. The capacitor CS isolates the input from the output and provides protection against a shorted or malfunctioning load. Hence, the SEPIC is useful for replacing boost circuits when true shutdown is required. This means that the output voltage falls to 0V when the switch is turned off. In a boost converter, the output can only fall to the input voltage minus a diode drop.

The duty cycle of a SEPIC is given using Equation 34.

$$D = \frac{V_{\text{out}} + V_{\text{DIODE}}}{V_{\text{out}} + V_{\text{IN}} - V_{\text{Q}} + V_{\text{DIODE}}}$$

(34)

In Equation 34,  $V_Q$  is the on-state voltage of the MOSFET, Q, and  $V_{DIODE}$  is the forward voltage drop of the diode.

### 8.2.2.1 Design Requirements

To properly size the components for the application, the designer needs the following parameters: input voltage range, output voltage, output current range, and required switching frequency. These four main parameters affect the choices of component available to achieve a proper system behavior.

For the power supply, the input impedance of the supply rail should be low enough that the input current transient does not drop below the UVLO value. The factors determining the choice of inductor used should be the average inductor current, and the inductor current ripple. If the switching frequency is set high, the converter can be operated with very small inductor values. The maximum current that can be delivered to the load is set by the sense resistor, RSEN. Current limit occurs when the voltage generated across the sense resistor equals the current sense threshold voltage, VSENSE. Also, a resistor RSL adds additional slope compensation, if required.

The following sections describe the design requirements for a typical LM3478 boost application.

(36)

#### **Typical Applications (continued)**

#### 8.2.2.2 Detailed Design Procedure

#### 8.2.2.2.1 Power MOSFET Selection

As in a boost converter, parameters governing the selection of the MOSFET are the minimum threshold voltage,  $V_{TH(MIN)}$ , the on-resistance,  $R_{DS(ON)}$ , the total gate charge,  $Q_g$ , the reverse transfer capacitance,  $C_{RSS}$ , and the maximum drain to source voltage,  $V_{DS(MAX)}$ . The peak switch voltage in a SEPIC is given using Equation 35.

$$V_{\rm SW(PEAK)} = V_{\rm IN} + V_{\rm OUT} + V_{\rm DIODE}$$

(35)

The selected MOSFET should satisfy the condition:

$V_{DS(MAX)} > V_{SW(PEAK)}$

The peak switch current is given using Equation 37.

$$I_{SW(PEAK)} = I_{L1(AVG)} + I_{OUT} + \frac{\Delta I_{L1} + \Delta I_{L2}}{2}$$

(37)

The RMS current through the switch is given using Equation 38.

$$I_{SWRMS} = \sqrt{\left[I_{SWPEAK}^{2} - I_{SWPEAK} \left(\Delta I_{L1} + \Delta I_{L2}\right) + \frac{\left(\Delta I_{L1} + \Delta I_{L2}\right)^{2}}{3}\right]} D$$

(38)

#### 8.2.2.2.2 Power Diode Selection

The Power diode must be selected to handle the peak current and the peak reverse voltage. In a SEPIC, the diode peak current is the same as the switch peak current. The off-state voltage or peak reverse voltage of the diode is  $V_{IN} + V_{OUT}$ . Similar to the boost converter, the average diode current is equal to the output current. Schottky diodes are recommended.

#### 8.2.2.3 Selection of Inductors L1 and L2

Proper selection of inductors L1 and L2 to maintain continuous current conduction mode requires calculations of the following parameters.

Average current in the inductors can be calculated using Equation 39.

$$I_{L1AVE} = \frac{DI_{OUT}}{1-D}$$

(39)

$$I_{L2AVE} = I_{OUT}$$

(40)

Peak to peak ripple current, to calculate core loss if necessary using Equation 41 and Equation 42.

$$\Delta I_{L1} = \frac{(V_{IN} - V_Q) D}{(L1) f_S}$$

(41)

$$\Delta I_{L2} = \frac{(V_{IN} - V_Q) D}{(L2) f_S}$$

(42)

Maintaining the condition  $I_L > \Delta i_L/2$  to ensure continuous current conduction yields Equation 43 and Equation 44.

$$L1 > \frac{(V_{IN} - V_Q)(1 - D)}{2I_{OUT}f_S}$$

$$L2 > \frac{(V_{IN} - V_Q)D}{2I_{OUT}f_S}$$

(43)

Peak current in the inductor, use Equation 45 and Equation 46 to ensure the inductor does not saturate.

$$I_{L1PK} = \frac{DI_{OUT}}{1-D} + \frac{\Delta I_{L1}}{2}$$

(45)

(44)

ISTRUMENTS

FXAS

#### **Typical Applications (continued)**

$$I_{L2PK} = I_{OUT} + \frac{\Delta I_{L2}}{2}$$

(46)

IL1PK must be lower than the maximum current rating set by the current sense resistor.

The value of L1 can be increased above the minimum recommended to reduce input ripple and output ripple. However, once  $D_{IL1}$  is less than 20% of  $I_{L1AVE}$ , the benefit to output ripple is minimal.

By increasing the value of L2 above the minimum recommended,  $\Delta_{IL2}$  can be reduced, which in turn will reduce the output ripple voltage:

$$\Delta V_{OUT} = \left(\frac{I_{OUT}}{1-D} + \frac{\Delta I_{L2}}{2}\right) \quad \text{ESR}$$

(47)

where ESR is the effective series resistance of the output capacitor.

If L1 and L2 are wound on the same core, then L1 = L2 = L. All of the previous equations will hold true if the inductance is replaced by 2L.

#### 8.2.2.2.4 Sense Resistor Selection

The peak current through the switch,  $I_{SW(PEAK)}$  can be adjusted using the current sense resistor,  $R_{SEN}$ , to provide a certain output current. Resistor  $R_{SEN}$  can be selected using Equation 48

$$R_{SEN} = \frac{V_{SENSE} - D(V_{SL} + \Delta V_{SL})}{I_{SWPEAK}}$$

(48)

#### 8.2.2.2.5 Sepic Capacitor Selection

The selection of the SEPIC capacitor, CS, depends on the RMS current. The RMS current of the SEPIC capacitor is given by Equation 49.

$$I_{\text{CSRMS}} = \sqrt{I_{\text{SWRMS}}^2 + (I_{\text{L1PK}}^2 - I_{\text{L1PK}} \Delta I_{\text{L1}} + \Delta I_{\text{L1}}^2) (1-D)}$$

(49)

The SEPIC capacitor must be rated for a large ACrms current relative to the output power. This property makes the SEPIC much better suited to lower power applications where the RMS current through the capacitor is relatively small (relative to capacitor technology). The voltage rating of the SEPIC capacitor must be greater than the maximum input voltage. There is an energy balance between CS and L1, which can be used to determine the value of the capacitor. Equation 50 shows the basic energy balance.

$\frac{1}{2}C_{S}\Delta V_{S}^{2} = \frac{1}{2}L_{1}\Delta I_{L1}^{2}$ (50)

where

$$\Delta V_{s} = \left(\frac{V_{OUT}}{V_{OUT} + V_{IN} - V_{Q} + V_{DIODE}}\right) \frac{I_{OUT}}{f_{s}C_{s}}$$

(51)

is the ripple voltage across the SEPIC capacitor, and

$$\Delta I_{L1} = \frac{(V_{IN} - V_Q) D}{L_1 f_S}$$

(52)

is the ripple current through the inductor L1. The energy balance equation can be solved using Equation 53 to provide a minimum value for  $C_s$ .

$$C_{S} \ge L_{1} \frac{I_{OUT}^{2}}{(V_{IN} - V_{Q})^{2}}$$

(53)

### **Typical Applications (continued)**

#### 8.2.2.2.6 Input Capacitor Selection

Similar to a boost converter, the SEPIC has an inductor at the input. Hence, the input current waveform is continuous and triangular. The inductor ensures that the input capacitor sees fairly low ripple currents. However, as the input capacitor gets smaller, the input ripple goes up. The RMS current in the input capacitor is given using Equation 54.

$$I_{CIN(RMS)} = \Delta I_{L1} / \sqrt{12} = \frac{D}{2\sqrt{3}} \left( \frac{V_{IN} - V_Q}{L_1 f_S} \right)$$

(54)

The input capacitor should be capable of handling the RMS current. Although the input capacitor is not as critical in a boost application, low values can cause impedance interactions. Therefore a good quality capacitor should be chosen in the range of 10µF to 20µF. If a value lower than 10 µF is used, then problems with impedance interactions or switching noise can affect the LM3478. To improve performance, especially with  $V_{IN}$  below 8 volts, TI recommends that the user uses a 20 $\Omega$  resistor at the input to provide a RC filter. The resistor is placed in series with the  $V_{IN}$  pin with only a bypass capacitor attached to the  $V_{IN}$  pin directly (see Figure 31). A 0.1-µF or 1-µF ceramic capacitor is necessary in this configuration. The bulk input capacitor and inductor will connect on the other side of the resistor with the input power supply.

#### 8.2.2.2.7 Output Capacitor Selection

The output capacitor of the SEPIC sees very large ripple currents (similar to the output capacitor of a boost converter). The RMS current through the output capacitor is given using Equation 55.

$$I_{RMS} = \sqrt{\left[I_{SWPK}^{2} - I_{SWPK} \left(\Delta I_{L1} + \Delta I_{L2}\right) + \frac{\left(\Delta I_{L1} + \Delta I_{L2}\right)^{2}}{3}\right] (1-D) - I_{OUT}^{2}}$$

(55)

The ESR and ESL of the output capacitor directly control the output ripple. Use low capacitors with low ESR and ESL at the output for high efficiency and low ripple voltage. Surface mount tantalums, surface mount polymer electrolytic and polymer tantalum, Sanyo-OSCON, or multi-layer ceramic capacitors are recommended at the output for low ripple.

#### 8.2.2.3 Application Curves

### 9 Power Supply Recommendations

The LM3478 is designed to operate from various DC power supply including a car battery. If so, VIN input should be protected from reversal voltage and voltage dump over 40 volts. The impedance of the input supply rail should be low enough that the input current transient does not cause drop below VIN UVLO level. If the input supply is connected by using long wires, additional bulk capacitance may be required in addition to normal input capacitor.

# 10 Layout

### 10.1 Layout Guidelines

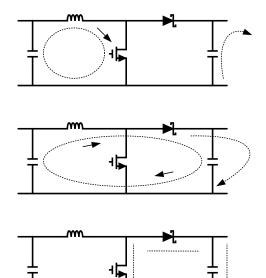

Good board layout is critical for switching controllers. First the ground plane area must be sufficient for thermal dissipation purposes and second, appropriate guidelines must be followed to reduce the effects of switching noise. Switching converters are very fast switching devices. In such devices, the rapid increase of input current combined with the parasitic trace inductance generates unwanted Ldi/dt noise spikes. The magnitude of this noise tends to increase as the output current increases. This parasitic spike noise may turn into electromagnetic interference (EMI), and can also cause problems in device performance. Therefore, care must be taken in layout to minimize the effect of this switching noise. The current sensing circuit in current mode devices can be easily affected by switching noise. This noise can cause duty cycle jittering which leads to increased spectral noise. Although the LM3478 has 325 ns blanking time at the beginning of every cycle to ignore this noise, some noise may remain after the blanking time.

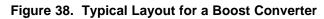

The most important layout rule is to keep the AC current loops as small as possible. Figure 37 shows the current flow of a boost converter. The top schematic shows a dotted line which represents the current flow during onstate and the middle schematic shows the current flow during off-state. The bottom schematic shows the currents we refer to as AC currents. They are the most critical ones since current is changing in very short time periods. The dotted lined traces of the bottom schematic are the once to make as short as possible.

The PGND and AGND pins have to be connected to the same ground very close to the IC. To avoid ground loop currents, attach all the grounds of the system only at one point.

A ceramic input capacitor should be connected as close as possible to the Vin pin and grounded close to the GND pin.

For more information about layout in switch mode power supplies please refer to AN-1229 Simple Switcher PCB Layout Guidelines, SNVA054.

Figure 37. Current Flow in a Boost Application

www.tij.co.jp

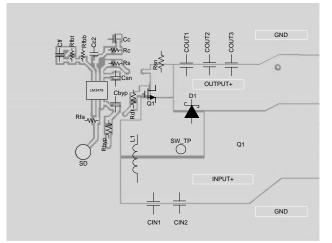

# 10.2 Layout Example

See evaluation modules for more detailed examples.

www.tij.co.jp

# 11 デバイスおよびドキュメントのサポート

# 11.1 WEBENCHツールによるカスタム設計

ここをクリックすると、WEBENCH<sup>®</sup>Power Designerにより、LM3478デバイスを使用するカスタム設計を作成できます。

- 1. 最初に、V<sub>IN</sub>、V<sub>OUT</sub>、I<sub>OUT</sub>の要件を入力します。

- 2. オプティマイザのダイヤルを使用して、効率、占有面積、コストなどの主要なパラメータについて設計を最適化し、この 設計と、テキサス・インスツルメンツによる他の可能なソリューションとを比較します。

- 3. WEBENCH Power Designerでは、カスタマイズされた回路図と部品リストを、リアルタイムの価格や部品の在庫情報 と併せて参照できます。

- 4. ほとんどの場合、次の操作も実行できます。

- 電気的なシミュレーションを実行し、重要な波形と回路の性能を確認する。

- 熱シミュレーションを実行し、基板の熱特性を把握する。

- カスタマイズされた回路図やレイアウトを、一般的なCADフォーマットでエクスポートする。

- 設計のレポートをPDFで印刷し、同僚と設計を共有する。

- 5. WEBENCHツールの詳細は、www.ti.com/webenchでご覧になれます。

# 11.2 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、ti.comのデバイス製品フォルダを開いてください。右上の隅にある「通 知を受け取る」をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取れます。変更の 詳細については、修正されたドキュメントに含まれている改訂履歴をご覧ください。

# 11.3 ドキュメントのサポート

WEBENCH Power Designerにより、LM3478を使用するカスタム設計を作成できます。

#### 11.3.1 関連資料

関連資料については、以下を参照してください:

- 『AN-1286 LM3748昇圧コントローラの補償』SNVA067

- 『AN-1229 Simple Switcher PCBレイアウト・ガイドライン』SNVA054

# 11.4 関連リンク

次の表に、クイック・アクセス・リンクを示します。カテゴリには、技術資料、サポートおよびコミュニティ・リソース、ツールとソフトウェア、およびサンプル注文またはご購入へのクイック・アクセスが含まれます。

#### 表 1. 関連リンク

| 製品     | プロダクト・フォルダ | サンプルとご購入 | 技術資料    | ツールとソフトウェア | サポートとコミュニティ |  |

|--------|------------|----------|---------|------------|-------------|--|

| LM3478 | ここをクリック    | ここをクリック  | ここをクリック | ここをクリック    | ここをクリック     |  |

### 11.5 商標

WEBENCH is a registered trademark of Texas Instruments. All other trademarks are the property of their respective owners.

### 11.6 静電気放電に関する注意事項

これらのデバイスは、限定的なESD(静電破壊)保護機能を内蔵しています。保存時または取り扱い時は、MOSゲートに対する静電破壊を防止するために、リード線同士をショートさせておくか、デバイスを導電フォームに入れる必要があります。

### 11.7 Glossary

#### SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

#### www.tij.co.jp

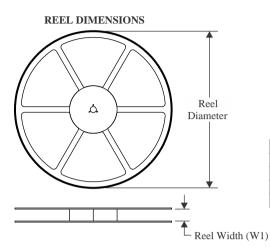

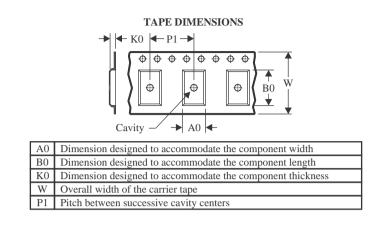

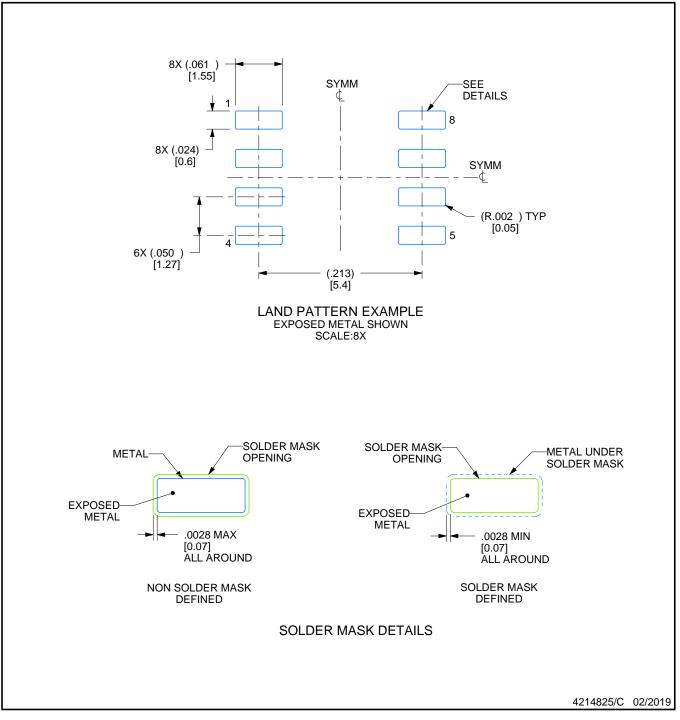

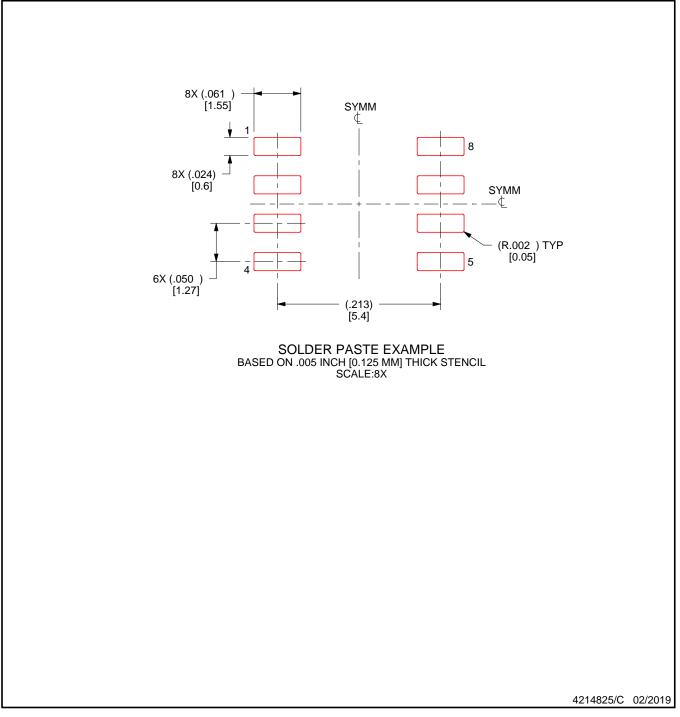

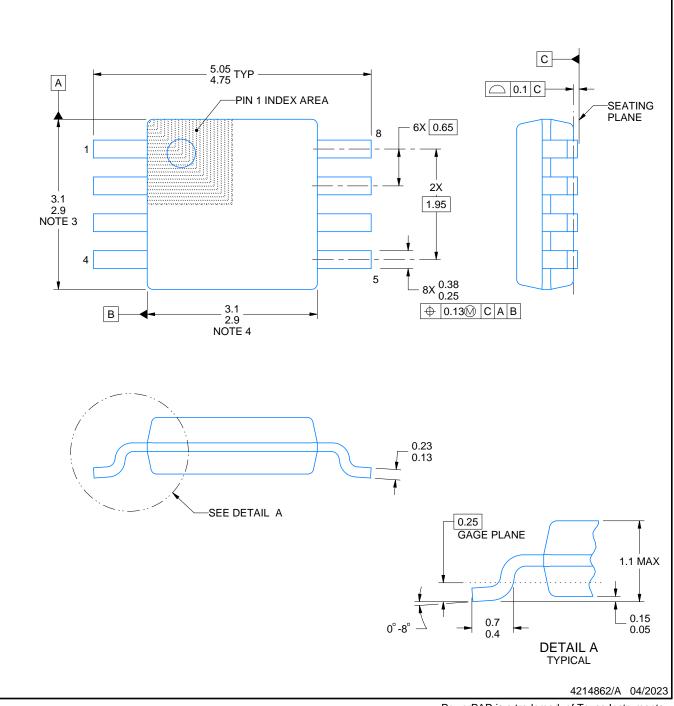

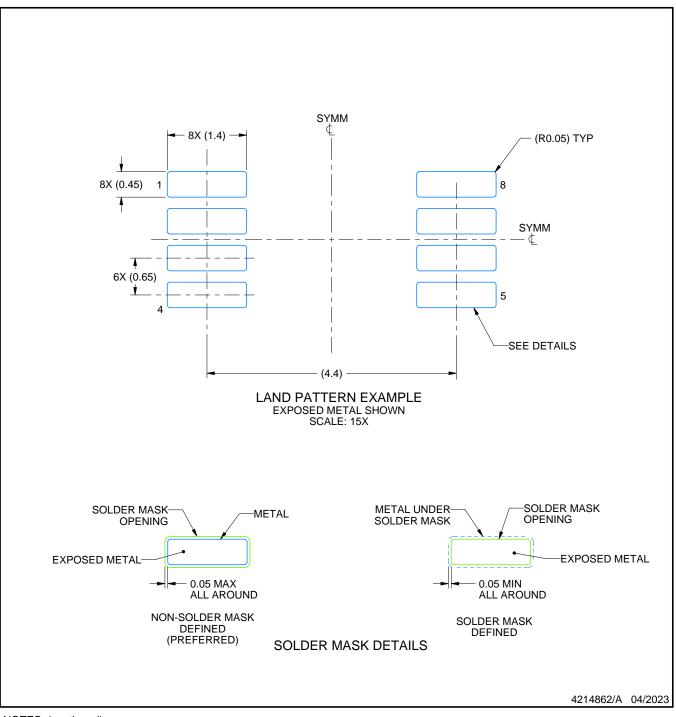

# 12 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、そのデバイスに ついて利用可能な最新のデータです。このデータは予告なく変更されることがあり、ドキュメントが改訂される場合もありま す。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

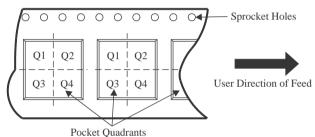

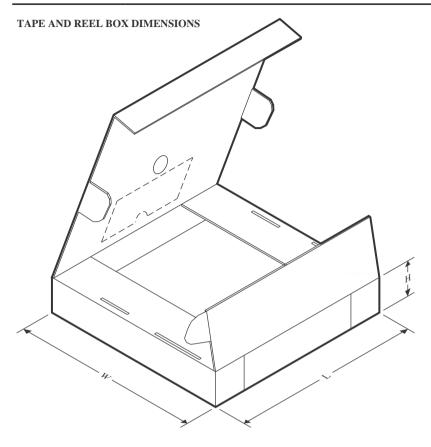

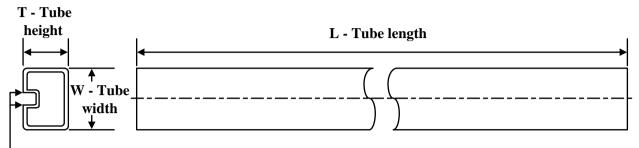

# PACKAGING INFORMATION

| Orderable Device | Status | Package Type | •       | Pins | Package | Eco Plan     | Lead finish/  | MSL Peak Temp      | Op Temp (°C) | Device Marking | Samples |

|------------------|--------|--------------|---------|------|---------|--------------|---------------|--------------------|--------------|----------------|---------|

|                  | (1)    |              | Drawing |      | Qty     | (2)          | Ball material | (3)                |              | (4/5)          |         |

|                  |        |              |         |      |         |              | (6)           |                    |              |                |         |

| LM3478MA/NOPB    | ACTIVE | SOIC         | D       | 8    | 95      | RoHS & Green | SN            | Level-1-260C-UNLIM |              | L3478          | Samples |

|                  |        |              |         |      |         |              |               |                    |              | MA             | Samples |

| LM3478MAX/NOPB   | ACTIVE | SOIC         | D       | 8    | 2500    | RoHS & Green | SN            | Level-1-260C-UNLIM |              | L3478          | Samples |

|                  |        |              |         |      |         |              |               |                    |              | MA             | Samples |

| LM3478MM/NOPB    | ACTIVE | VSSOP        | DGK     | 8    | 1000    | RoHS & Green | NIPDAUAG   SN | Level-1-260C-UNLIM | -40 to 125   | S14B           | Samples |

|                  |        |              |         |      |         |              |               |                    |              |                | Samples |

| LM3478MMX/NOPB   | ACTIVE | VSSOP        | DGK     | 8    | 3500    | RoHS & Green | NIPDAUAG   SN | Level-1-260C-UNLIM | -40 to 125   | S14B           | Samplas |

|                  |        |              |         |      |         |              | •             |                    |              |                | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

**LIFEBUY:** TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.