オーディオ・パワー・アンプ・シリーズ

## I<sup>2</sup>C ボリューム制御機能内蔵クラス G ヘッドフォン・アンプ

#### 概要

TEXAS

INSTRUMENTS

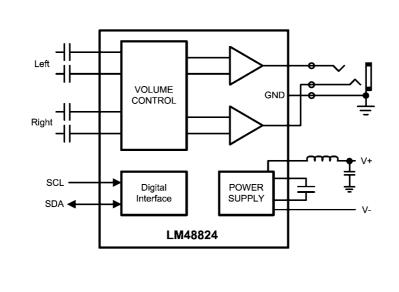

LM48824 は、ポータブル機器用に設計されたクラス G グラウン ドリファレンス・ステレオ・ヘッドフォン・アンプです。LM48824 はテキサス・インスツルメンツのグラウンドリファレンス・アーキテ クチャーにより、従来のヘッドフォン・アンプで必要とされた大 きな DC コンデンサを不要にし、ボードスペースの削減とシステ ムコストの最小化を実現します。

LM48824 はテキサス・インスツルメンツの特許出願中のクラス G アーキテクチャーを採用し、従来のクラス AB ヘッドフォン・ア ンプに比べて消費電力を削減しています。さらに、アンプのグ ラウンドとヘッドフォンのリターン・ターミナル間の相違を補正す るコモンモード検出機能により、グラウンド電位のミスマッチに よって発生するノイズを最小限に抑え、出力ノイズを改善してい ます。

高出力インピーダンス・モードにより、信号の劣化を招かずに 外部ソースによる LM48824 の出力駆動が可能です。その他の 機能として、柔軟な電源条件、差動入力によるノイズ・リダク ションの向上、省電力 (2.5 µ A) シャットダウン・モード、ミュー ト機能付きの32ステップ1<sup>2</sup>Cボリューム制御機能などがあります。

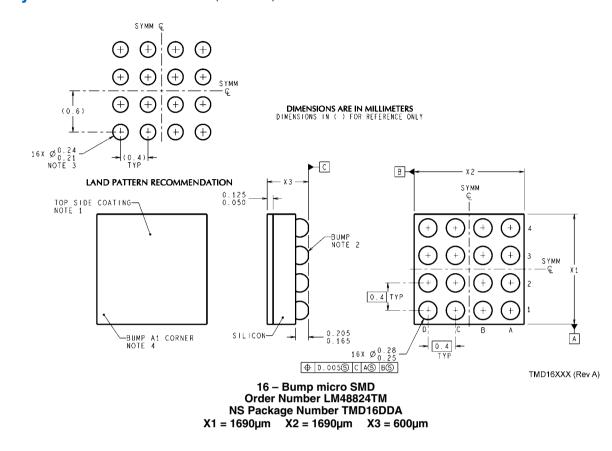

LM48824の優れたクリック/ポップ抑圧回路は、パワーアップ/ ダウン時やシャットダウン時の可聴トランジェントを除去します。 LM48824は、16ピン、ピッチ幅 0.4mmの超小型 micro SMD パッケージ (1.69mm × 1.69mm) で提供されます。

#### 主な仕様

| 特長                                                                      |               |

|-------------------------------------------------------------------------|---------------|

| ■ シャットダウン電流                                                             | 2.5 µ A (typ) |

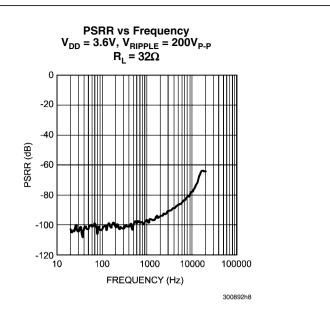

| ■ PSRR                                                                  | 100dB (typ)   |

| ■ 出力電力 / チャネル @ $V_{DD} = 3.6V$<br>$R_L = 32 \Omega$ 、THD + N ≤ 1%      | 29mW (typ)    |

| ■ 出力電力 / チャネル @ $V_{DD} = 3.6V$<br>$R_L = 16\Omega$ 、THD + N $\leq 1\%$ | 37mW (typ)    |

| ■ 静止時消費電流 @3.6V                                                         | 0.9mA (typ)   |

- クラスGの電力効率

- グラウンドリファレンス・ヘッドフォン出力 出力カップリング・コンデンサが不要

- コモンモード検出機能

- I<sup>2</sup>C ボリューム / モード制御

- シャットダウン時の高出力インピーダンス

- 差動入力

- 高度なクリック / ポップ・ノイズ低減回路

- 低消費電力

- 低 THD モード・オプション

## アプリケーション

- 携帯電話、PDA、MP3 プレーヤ

- 携帯電子機器、ノートブック PC

## 簡略ブロック図

#### 2009年8月

JAJSBI7

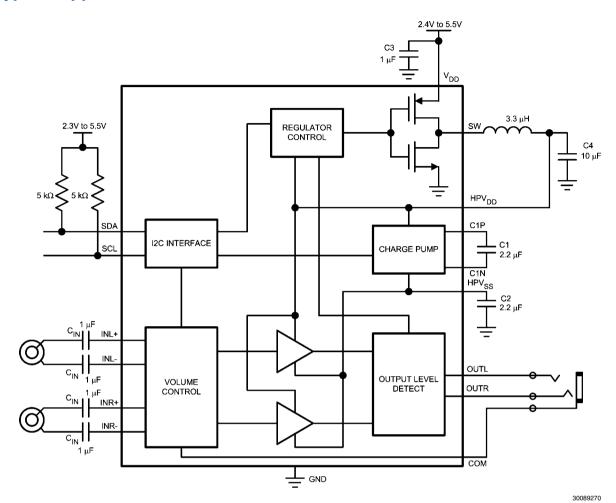

## **Typical Application**

FIGURE 1. Typical Audio Amplifier Application Circuit

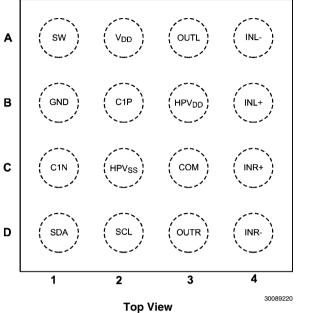

## Connection Diagrams TM Package 1.7mm x 1.7mm x 0.6mm

Order Number LM48824TM See NS Package Number TMD16DDA

## **Ordering Information**

| Order Number | Package           | Package DWG # | Transport Media             | MSL Level | Green Status |

|--------------|-------------------|---------------|-----------------------------|-----------|--------------|

| LM48824TM    | 16 Bump micro SMD | TMD16DDA      | 250 units on tape and reel  | 1         | NOPB         |

| LM48824TMX   | 16 Bump micro SMD | TMD16DDA      | 3000 units on tape and reel | 1         | NOPB         |

30089217

16–Bump micro SMD Marking

XYTT

Top View XY = Date code TT = Die traceability G = Boomer Family L6 = LM48824TM

Pin 1

GL6

## **Bump Descriptions**

| Bump | Name              | Pin Descriptions                                          |  |

|------|-------------------|-----------------------------------------------------------|--|

| A1   | SW                | Regulator Switching Node                                  |  |

| A2   | V <sub>DD</sub>   | Power Supply                                              |  |

| A3   | OUTL              | Left Channel Output                                       |  |

| A4   | INL-              | Left Channel Inverting Input                              |  |

| B1   | GND               | Ground                                                    |  |

| B2   | C1P               | Charge Pump Flying Capacitor Positive Terminal            |  |

| B3   | HPV <sub>DD</sub> | Amplifier Power Supply/Regulator Output                   |  |

| B4   | INL+              | Left Channel Non-Inverting Input                          |  |

| C1   | C1N               | Charge Pump Flying Capacitor Negative Terminal            |  |

| C2   | HPV <sub>SS</sub> | Charge Pump Output                                        |  |

| C3   | COM               | Common-mode Sense Input. Connect to headphone jack return |  |

| C4   | INR+              | Right Channel Non-Inverting Input                         |  |

| D1   | SDA               | I2C Serial Data Input                                     |  |

| D2   | SCL               | I2C Serial Clock Input                                    |  |

| D3   | OUTR              | Right Channel Output                                      |  |

| D4   | INR-              | Right Channel Inverting Input                             |  |

## Absolute Maximum Ratings (Note 1, Note

#### 2)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| Supply Voltage (Note 1)             | 6V                              |

|-------------------------------------|---------------------------------|

| Storage Temperature                 | –65°C to +150°C                 |

| Input Voltage                       | -0.3V to V <sub>DD</sub> + 0.3V |

| Power Dissipation ( <i>Note 3</i> ) | Internally Limited              |

| ESD Rating (Note 4)                 | 2000V                           |

| ESD Rating ( <i>Note 5</i> )        | 200V                            |

| ESD Rating ( <i>Note 6</i> )        | 500V                            |

| Junction Temperature                | 150°C                           |

| Soldering Information<br>Vapor Phase (60 sec.) | 215°C  |

|------------------------------------------------|--------|

| Infrared (15 sec.)                             | 220°C  |

| Thermal Resistance                             |        |

| θ <sub>JA</sub> (TMA16DDA)                     | 60°C/W |

| Soldering Information                          |        |

See AN-1112 "Micro SMD Wafer Level Chip Scale package"

## **Operating Ratings**

| Temperature Range                 |                                         |

|-----------------------------------|-----------------------------------------|

| $T_{MIN} \leq T_{A} \leq T_{MAX}$ | $-40^{\circ}C \le T_A \le +85^{\circ}C$ |

| Supply Voltage (V <sub>DD</sub> ) | $2.4V \le V_{DD} \le 5.5V$              |

**Electrical Characteristics**  $V_{DD}$  = 3.6V (*Note 1, Note 2*) The following specifications apply for A<sub>V</sub> = 0dB, R<sub>L</sub> = 32 $\Omega$ , f = 1kHz, unless otherwise specified. Limits apply to T<sub>A</sub> = 25°C.

|                                                    |                                                                                                                        |                                                                                          | LM48                         | Units                      |                   |

|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|------------------------------|----------------------------|-------------------|

| Symbol                                             | Parameter                                                                                                              | Conditions                                                                               | Typical<br>( <i>Note 7</i> ) | Limit<br>( <i>Note 8</i> ) | (Limits)          |

| I <sub>DD</sub>                                    | Quiescent Power Supply Current                                                                                         | $V_{IN} = 0V$ , both channels active $R_L = \infty$                                      | 0.9                          | 1.3                        | mA (ma:           |

|                                                    |                                                                                                                        | $R_L = \infty$ , Low THD mode                                                            | 1.55                         |                            | mA                |

|                                                    |                                                                                                                        | $P_O = 100\mu$ W, two channels in phase,<br>3dB Crest Factor, R <sub>L</sub> = 32Ω + 15Ω | 1.8                          | 2.5                        | mA (ma            |

| I <sub>DD(OP)</sub> Operating Power Supply Current | $P_O = 100\mu$ W, two channels in phase,<br>3dB Crest Factor, $R_L = 32\Omega + 15\Omega$ ,<br>Low THD mode            | 2.2                                                                                      |                              | rr                         |                   |

|                                                    | 3.1                                                                                                                    | 3.8                                                                                      | mA (ma                       |                            |                   |

|                                                    | $P_O = 500 \mu$ W, two channels in phase,<br>3dB Crest Factor R <sub>L</sub> = $32\Omega + 15\Omega$ ,<br>Low THD mode | 3.4                                                                                      |                              | n                          |                   |

|                                                    |                                                                                                                        | $P_0 = 1$ mW, two channels in phase, 3dB<br>Crest Factor, $R_L = 32\Omega + 15\Omega$    | 4.1                          | 4.9                        | mA (ma            |

|                                                    | $P_{O}$ = 1mW, two channels in phase, 3dB<br>Crest Factor, $R_{L}$ = 32 $\Omega$ + 15 $\Omega$ ,<br>Low THD mode       |                                                                                          | 4.4                          |                            | mA                |

| $I_{SD}$                                           | Shutdown Current                                                                                                       | Shutdown Enabled<br>V <sub>SCL</sub> = V <sub>SDA</sub> = 1.8V                           | 2.5                          | 3.9                        | µA (ma            |

| V <sub>os</sub>                                    | Output Offset Voltage                                                                                                  | V <sub>IN</sub> = 0V                                                                     | 0.15                         | 0.65                       | mV (ma            |

| Τ <sub>WU</sub>                                    | Wake Up Time                                                                                                           | From Shutdown                                                                            | 2                            |                            | ms                |

| A <sub>V</sub>                                     | Gain                                                                                                                   | Minimum Gain Setting                                                                     | -59                          | 58<br>60                   | dB (ma<br>dB (mi  |

|                                                    |                                                                                                                        | Maximum Gain Setting                                                                     | 4                            | 4.5<br>3.5                 | dB (ma<br>dB (mi  |

| A <sub>V(MUTE)</sub>                               | Mute Attenuation                                                                                                       |                                                                                          | -110                         |                            | dB                |

| R <sub>IN</sub>                                    | Input Resistance                                                                                                       | $A_V = 4dB$<br>$A_V = -59dB$                                                             | 24<br>64                     | 20<br>80                   | kΩ (mir<br>kΩ (ma |

|                   |                                   |                                                                                           | LM4                          | 3824                       | Units                     |

|-------------------|-----------------------------------|-------------------------------------------------------------------------------------------|------------------------------|----------------------------|---------------------------|

| Symbol            | Parameter                         | Conditions                                                                                | Typical<br>( <i>Note 7</i> ) | Limit<br>( <i>Note 8</i> ) | (Limits)                  |

|                   |                                   | f = 1kHz, THD+N = 1%<br>Two channels in phase                                             | 37                           | 30                         | mW (mii                   |

| Po                | Output Power                      | $R_{L} = 16\Omega$<br>f = 1kHz, THD+N = 1%                                                |                              |                            |                           |

|                   |                                   | Two channels in phase $R_L = 32\Omega$ ,                                                  | 29                           | 23                         | mW (mi                    |

|                   |                                   | THD+N = 1%, Two Channels in Phase                                                         | r                            | 1                          | 1                         |

|                   |                                   | R <sub>L</sub> = 16Ω                                                                      | 0.77                         | 0.7                        | V <sub>RMS</sub><br>(min) |

| Vo                | Output Swing                      | R <sub>L</sub> = 32Ω                                                                      | 0.96                         | 0.86                       | V <sub>RMS</sub><br>(min) |

|                   |                                   | $R_L = 32\Omega + 15\Omega$                                                               | 1.05                         |                            | V <sub>RMS</sub>          |

|                   |                                   | $R_L = 10k\Omega$                                                                         | 1.3                          | 1.1                        | V <sub>RMS</sub><br>(min) |

|                   |                                   | f = 1kHz, Single Channel                                                                  |                              |                            |                           |

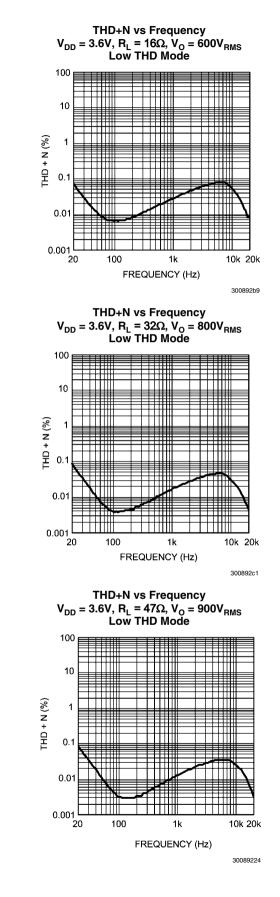

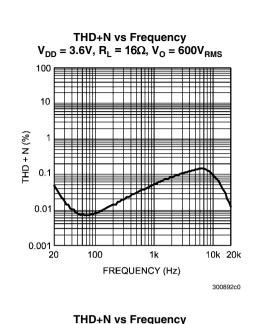

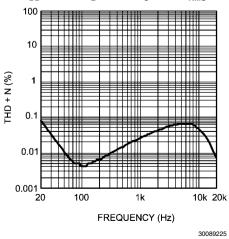

|                   |                                   | $V_{O} = 600 \text{mV}_{\text{RMS}}, \text{ R}_{\text{L}} = 16 \Omega$                    | 0.05                         |                            | %                         |

|                   | Total Harmonic Distortion + Noise | $V_{O} = 600 m V_{RMS}, R_{L} = 16\Omega,$<br>Low THD Mode                                | 0.03                         |                            | %                         |

|                   |                                   | $V_0 = 800 \text{mV}_{\text{RMS}}, \text{R}_{\text{L}} = 32\Omega,$                       | 0.035                        |                            | %                         |

| THD+N             |                                   | $V_{O} = 800 \text{mV}_{\text{RMS}}, \text{R}_{\text{L}} = 32\Omega,$<br>Low THD Mode     | 0.02                         |                            | %                         |

|                   |                                   | $V_0 = 900 \text{mV}_{\text{BMS}}, \text{R}_{\text{L}} = 32\Omega + 15\Omega$             | 0.027                        | 0.04                       | %(max                     |

|                   |                                   | $V_{O} = 900 \text{mV}_{\text{RMS}}, \text{R}_{L} = 32\Omega + 15\Omega,$<br>Low THD Mode | 0.015                        |                            | %                         |

|                   |                                   | $V_{RIPPLE} = 200 mV_{P-P}$ , Inputs AC GND                                               |                              |                            | •                         |

| PSRR              | Power Supply Dejection Datio      | $C_{IN}$ = 1µF, input referred,                                                           |                              |                            |                           |

| ronn              | Power Supply Rejection Ratio      | f <sub>RIPPLE</sub> = 217Hz                                                               | 100                          | 94                         | dB (mir                   |

|                   |                                   | f <sub>RIPPLE</sub> = 1kHz                                                                | 100                          |                            | dB                        |

| CMRR              | Common Mode Rejection Ratio       | $V_{RIPPLE} = 1V_{P-P}$ , $f_{RIPPLE} = 217Hz$                                            | 60                           |                            | dB                        |

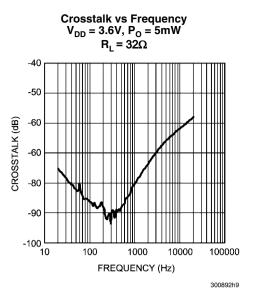

| V                 |                                   | $R_L \ge 16\Omega$ , $P_O = 5mW$ , $f = 1kHz$                                             | 80                           | 70                         | dB (mir                   |

| X <sub>TALK</sub> | Crosstalk                         | $R_L \ge 10k\Omega$ , $V_{OUT} = 1V_{RMS}$ , $f = 1kHz$                                   | 110                          | 95                         | dB (mi                    |

|                   |                                   | $V_{OUT} = 1V_{RMS}, f = 1kHz$                                                            | 102                          | 98                         | dB (mi                    |

| SNR               | Signal-to-Noise Ratio             | V <sub>OUT</sub> = 1V <sub>RMS</sub> , f = 1kHz,<br>Low THD Mode                          | 105                          |                            | dB                        |

|                   |                                   | $A_V = 4$ dB, A-Weighted Filter                                                           | 8                            | 12                         | μV(max                    |

| ∈os               | Output Noise                      | $A_V = 4$ dB, A-weighted Filter,<br>Low THD Mode                                          | 7                            |                            | μV                        |

|                   |                                   | Charge pump-only mode enabled                                                             |                              |                            |                           |

| в                 | Output Impedance                  | f < 40kHz                                                                                 | 43                           | 30                         | kΩ (mii                   |

| R <sub>OUT</sub>  |                                   | f = 6MHz                                                                                  |                              | 500                        | Ω (min                    |

|                   |                                   | f = 36MHz                                                                                 |                              | 75                         | Ω (min                    |

|                   |                                   | No Sustained Oscillations                                                                 |                              |                            |                           |

| CL                | Maximum Capacitive Load           | with $5\Omega$ series resistance                                                          | 100                          |                            | nF                        |

|                   |                                   | with no series resistance                                                                 | 100                          |                            | pF                        |

| V <sub>OUT</sub>  | Maximum Voltage Swing             | Voltage applied to amplifier outputs in charge pump-only mode                             | 1.1                          | 1.0                        | V <sub>RMS</sub><br>(min) |

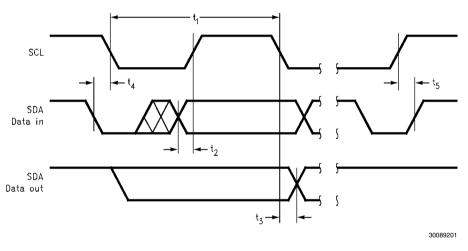

## I<sup>2</sup>C Interface Characteristics $V_{DD} = 3.6V$ (Note 1, Note 2)

The following specifications apply for  $A_V = 0$ dB,  $R_L = 16\Omega$ , f = 1kHz, unless otherwise specified. Limits apply to  $T_A = 25^{\circ}$ C.

|                  |                      |                              | LM4                        | 48824    | Units    |

|------------------|----------------------|------------------------------|----------------------------|----------|----------|

| Symbol Parameter | Conditions           | Typical<br>( <i>Note 7</i> ) | Limit<br>( <i>Note 8</i> ) | (Limits) |          |

| t <sub>1</sub>   | SCL Period           |                              |                            | 2.5      | µs (min) |

| t <sub>2</sub>   | SDA Setup Time       |                              |                            | 250      | ns (min) |

| t <sub>3</sub>   | SDA Stable Time      |                              |                            | 250      | ns (min) |

| t <sub>4</sub>   | Start Condition Time |                              |                            | 250      | ns (min) |

| t <sub>5</sub>   | Stop Condition Time  |                              |                            | 250      | ns (min) |

| V <sub>IH</sub>  | Input High Voltage   |                              |                            | 1.2      | V (min)  |

| V <sub>IL</sub>  | Input Low Voltage    |                              |                            | 0.6      | V (max)  |

**Note 1:** "Absolute Maximum Ratings" indicate limits beyond which damage to the device may occur, including inoperability and degradation of device reliability and/or performance. Functional operation of the device and/or non-degradation at the Absolute Maximum Ratings or other conditions beyond those indicated in the Recommended Operating Conditions is not implied. The Recommended Operating Conditions indicate conditions at which the device is functional and the device should not be operated beyond such conditions. All voltages are measured with respect to the ground pin, unless otherwise specified

Note 2: The *Electrical Characteristics* tables list guaranteed specifications under the listed *Recommended Operating Conditions* except as otherwise modified or specified by the *Electrical Characteristics Conditions* and/or Notes. Typical specifications are estimations only and are not guaranteed.

**Note 3:** The maximum power dissipation must be derated at elevated temperatures and is dictated by  $T_{JMAX}$ ,  $\theta_{JA}$ , and the ambient temperature,  $T_A$ . The maximum allowable power dissipation is  $P_{DMAX} = (T_{JMAX} - T_A) / \theta_{JA}$  or the number given in *Absolute Maximum Ratings*, whichever is lower.

Note 4: Human body model, applicable std. JESD22-A114C.

Note 5: Machine model, applicable std. JESD22-A115-A.

Note 6: Charged Device Model, applicable std. JESD22-C101-C.

**Note 7:** Typical values represent most likely parametric norms at  $T_A = +25^{\circ}$ C, and at the *Recommended Operation Conditions* at the time of product characterization and are not guaranteed.

Note 8: Datasheet min/max specification limits are guaranteed by test or statistical analysis.

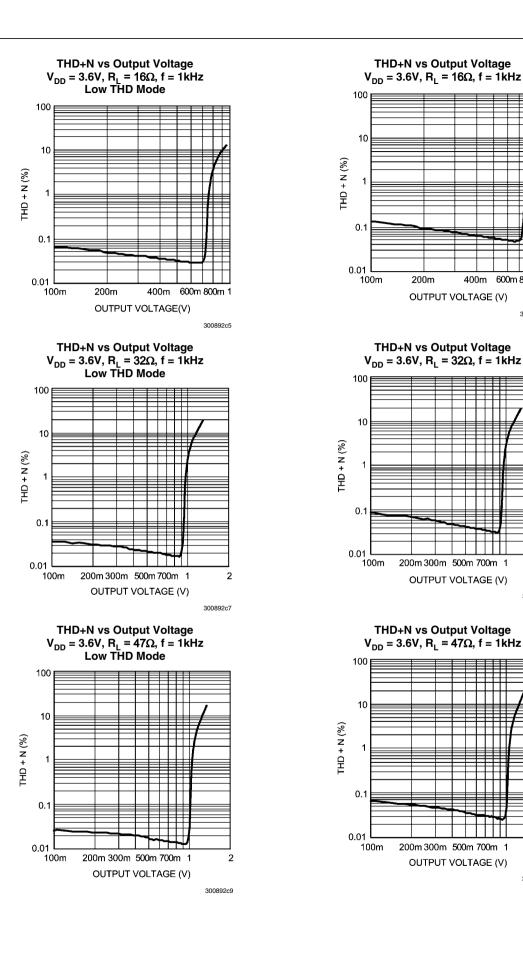

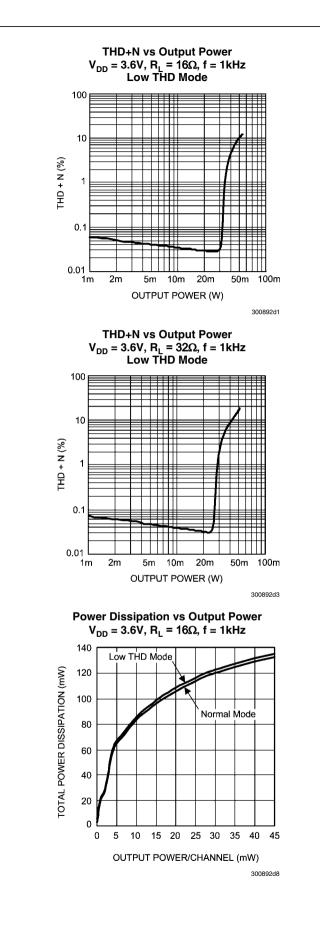

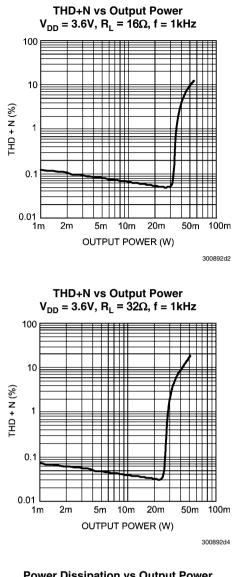

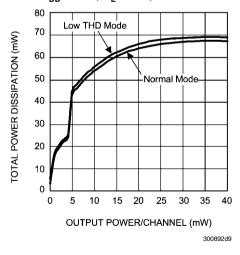

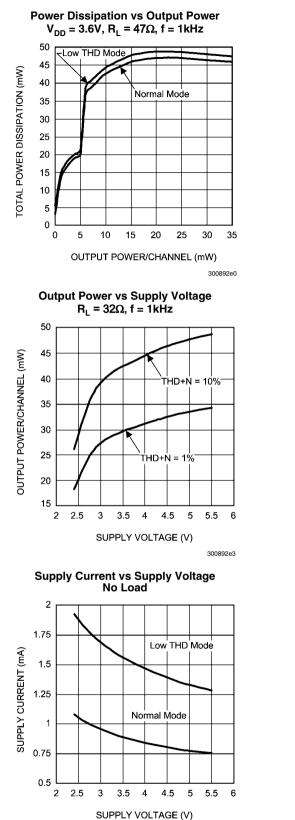

## **Typical Performance Characteristics**

$V_{DD} = 3.6V, R_{L} = 32\Omega, V_{O} = 800V_{RMS}$ 100 10 THD + N (%) 1 0.1 ∰ 11 0.01 0.001 100 10k 20k 20 1k FREQUENCY (Hz) 300892c2

THD+N vs Frequency  $V_{\text{DD}} = 3.6 \text{V}, \text{ R}_{\text{L}} = 47 \Omega, \text{ V}_{\text{O}} = 900 \text{V}_{\text{RMS}}$

LM48824

600m 800m 1

300892c6

2

2

300892d0

300892c8

Power Dissipation vs Output Power  $V_{DD} = 3.6V, R_L = 32\Omega, f = 1kHz$

300892e6

www.national.com

## **Application Information**

#### I<sup>2</sup>C COMPATIBLE INTERFACE

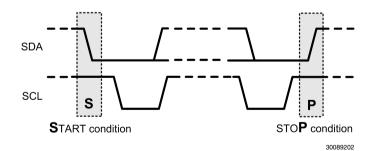

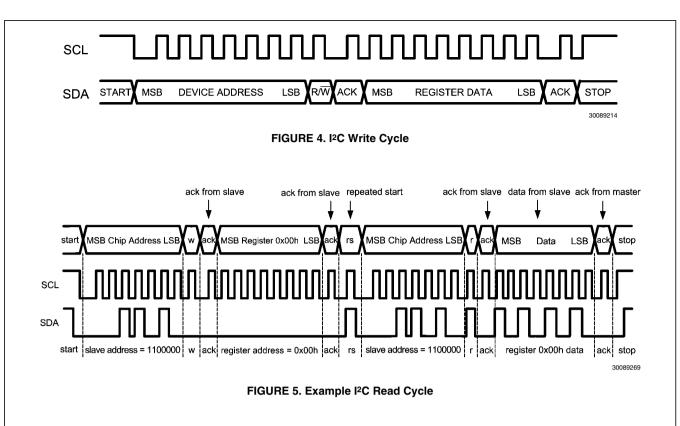

The LM48824 is controlled through an I<sup>2</sup>C compatible serial interface that consists of a serial data line (SDA) and a serial clock (SCL). The clock line is uni-directional. The data line is bi-directional (open drain). The LM48824 and the master can communicate at clock rates up to 400kHz. Figure 2 shows the I2C interface timing diagram. Data on the SDA line must be stable during the HIGH period of SCL. The LM48824 is a transmit/receive slave-only device, reliant upon the master to generate the SCL signal. Each transmission sequence is framed by a START condition and a STOP condition (Figure 3). Each data word, device address and data, transmitted over the bus is 8 bits long and is always followed by an acknowledge pulse (Figure 4). The LM48824 device address is 1100000.

#### I<sup>2</sup>C BUS FORMAT

The I<sup>2</sup>C bus format is shown in Figure 4. The START signal, the transition of SDA from HIGH to LOW while SCL is HIGH, is generated, alerting all devices on the bus that a device address is being written to the bus.

The 7-bit device address is written to the bus, most significant bit (MSB) first, followed by the  $R/\overline{W}$  bit ( $R/\overline{W} = 0$  indicates the master is writing to the LM48824,  $R/\overline{W} = 1$  indicates the master wants to read data from the LM48824). Data is latched into the device on the rising clock edge. Each address bit must be stable while SCL is HIGH. After the last address bit is transmitted, the master device releases SDA, during which time, an acknowledge clock pulse is generated by the slave device. If the LM48824 receives the correct address, the device pulls the SDA line low, generating an acknowledge bit (ACK).

Once the master device registers the ACK bit, the 8-bit register address word is sent. Each data bit should be stable while SCL is HIGH. After the 8-bit register address is sent, the LM48824 sends another ACK bit. Following the acknowledgment of the register address, the 8-bit register data word is sent. Each data bit should be stable while SCL is HIGH. After the 8-bit register data is sent, the LM48824 sends another ACK bit. Following the acknowledgement of the register data word, the master issues a STOP bit, allowing SDA to go high while SCL is high.

FIGURE 2. I<sup>2</sup>C Timing Diagram

FIGURE 3. Start and Stop Diagram

#### TABLE 1. Device Address

|                   | B7 | B6 | B5 | B4 | B3 | B2 | B1 | B0 (R/W) |

|-------------------|----|----|----|----|----|----|----|----------|

| Device<br>Address | 1  | 1  | 0  | 0  | 0  | 0  | 0  | х        |

#### TABLE 2. I<sup>2</sup>C Control Registers (Note 9)

| Register<br>Address | Register<br>Name                          | B7      | B6      | B5   | В4   | В3      | B2   | B1    | В0    |

|---------------------|-------------------------------------------|---------|---------|------|------|---------|------|-------|-------|

| 0x01h               | MODE<br>CONTROL                           | HPL_EN  | HPR_EN  | 0    | 0    | 0       | 0    | THRM  | SHDN  |

| 0x02h               | VOLUME<br>CONTROL                         | MUTE_L* | MUTE_R* | VOL4 | VOL3 | VOL2    | VOL1 | VOL0  | 0     |

| 0x03h               | OUTPUT<br>CONTROL                         | 0       | 0       | 0    | 0    | LOW_THD | 0    | HiZ_L | HiZ_R |

| 0x04h               | DEVICE<br>INFORMATI<br>ON (Read-<br>Only) | 0       | 1       | 0    | 0    | 0       | 0    | 0     | 0     |

Note 9: \* All registers default to 0 on initial power-up except SHDN, MUTE\_L, MUTE\_R bits default to 1 at power-up.

#### TABLE 3. Mode Control Register

| Bit | Name        | Value | Description                      |

|-----|-------------|-------|----------------------------------|

| B0  | SHDN        | 0     | Device enabled                   |

| DU  | 3000        | 1     | Device disabled                  |

| B1  | THRM        | 0     | Thermal-protection inactive      |

| Ы   | (Read Only) | 1     | Thermal-protection active        |

| B6  |             | 0     | Right channel amplifier disabled |

| DO  | HPR_EN      | 1     | Right channel amplifier enabled  |

| B7  |             | 0     | Left channel amplifier disabled  |

| 87  | HPL_EN      | 1     | Left channel amplifier enabled   |

#### TABLE 4. Volume Control Register

| Bit   | Name      | Value | Description                                                    |

|-------|-----------|-------|----------------------------------------------------------------|

| B5:B1 | VOL4:VOL0 |       | These bits set the volume level. See Table 5 (Volume Control). |

| B6    | MUTE_R    | 0     | Right Channel Mute Disabled                                    |

|       |           | 1     | Right Channel Mute Enabled                                     |

| В7    | MUTE_L    | 0     | Left Channel Mute Disabled                                     |

|       |           | 1     | Left Channel Mute Enabled                                      |

| TABLE 5. Volume Control |      |      |      |      |      |              |

|-------------------------|------|------|------|------|------|--------------|

| Volume Step             | VOL4 | VOL3 | VOL2 | VOL1 | VOL0 | HP Gain (dB) |

| 0                       | 0    | 0    | 0    | 0    | 0    | -59          |

| 1                       | 0    | 0    | 0    | 0    | 1    | -55          |

| 2                       | 0    | 0    | 0    | 1    | 0    | -51          |

| 3                       | 0    | 0    | 0    | 1    | 1    | -47          |

| 4                       | 0    | 0    | 1    | 0    | 0    | -43          |

| 5                       | 0    | 0    | 1    | 0    | 1    | -39          |

| 6                       | 0    | 0    | 1    | 1    | 0    | -35          |

| 7                       | 0    | 0    | 1    | 1    | 1    | -31          |

| 8                       | 0    | 1    | 0    | 0    | 0    | -27          |

| 9                       | 0    | 1    | 0    | 0    | 1    | -25          |

| 10                      | 0    | 1    | 0    | 1    | 0    | -23          |

| 11                      | 0    | 1    | 0    | 1    | 1    | -21          |

| 12                      | 0    | 1    | 1    | 0    | 0    | -19          |

| 13                      | 0    | 1    | 1    | 0    | 1    | -17          |

| 14                      | 0    | 1    | 1    | 1    | 0    | -15          |

| 15                      | 0    | 1    | 1    | 1    | 1    | -13          |

| 16                      | 1    | 0    | 0    | 0    | 0    | -11          |

| 17                      | 1    | 0    | 0    | 0    | 1    | -10          |

| 18                      | 1    | 0    | 0    | 1    | 0    | -9           |

| 19                      | 1    | 0    | 0    | 1    | 1    | -8           |

| 20                      | 1    | 0    | 1    | 0    | 0    | -7           |

| 21                      | 1    | 0    | 1    | 0    | 1    | -6           |

| 22                      | 1    | 0    | 1    | 1    | 0    | -5           |

| 23                      | 1    | 0    | 1    | 1    | 1    | -4           |

| 24                      | 1    | 1    | 0    | 0    | 0    | -3           |

| 25                      | 1    | 1    | 0    | 0    | 1    | -2           |

| 26                      | 1    | 1    | 0    | 1    | 0    | -1           |

| 27                      | 1    | 1    | 0    | 1    | 1    | 0            |

| 28                      | 1    | 1    | 1    | 0    | 0    | 1            |

| 29                      | 1    | 1    | 1    | 0    | 1    | 2            |

| 30                      | 1    | 1    | 1    | 1    | 0    | 3            |

| 31                      | 1    | 1    | 1    | 1    | 1    | 4            |

#### TABLE 5. Volume Control

#### **TABLE 6. Output Control Register**

| Bit      | Name     | Value | Description                                |

|----------|----------|-------|--------------------------------------------|

| PO       | B0 HiZ_R | 0     | Right channel high impedance mode disabled |

| BU       |          | 1     | Right channel high impedance mode enabled  |

| B1 HiZ_L |          | 0     | Left channel high impedance mode disabled  |

|          |          | 1     | Left channel high impedance mode enabled   |

| В3       | LOW_THD  | 0     | LOW_THD mode disabled                      |

|          |          | 1     | LOW_THD mode enabled, improves overall THD |

#### **GENERAL DEVICE FUNCTION**

The LM48824 integrates a high efficiency step down (buck) DC-DC switching regulator with a ground reference headphone amplifier. The switching regulator delivers a constant voltage from an input voltage ranging from 2.4V to 5.5V. The switching regulator uses a voltage-mode architecture with synchronous rectification, improving efficiency and reducing component count.

The LM48824 headphone amplifier features National's ground referenced architecture that eliminates the large DCblocking capacitors required at the outputs of traditional single-ended headphone amplifiers. A low-noise inverting charge pump creates a negative supply (HPV<sub>SS</sub>) from the positive supply voltage (V<sub>DD</sub>). The headphone amplifiers operate from these bipolar supplies, with the amplifier outputs biased about GND. Because there is no DC component on the output signals, the large DC-blocking, AC coupling capacitors (typically 220µF) are not necessary, conserving board space, reducing system cost, and improving frequency response.

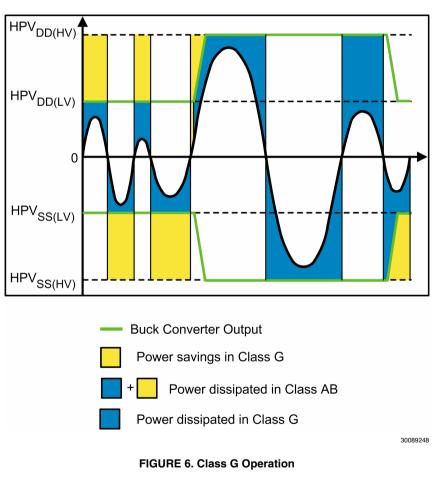

#### **CLASS G OPERATION**

Class G is a modification of some other class of amplifier (normally Class B or Class AB) to increase efficiency and reduce power dissipation. Class G works off the fact that musical and voice signals have a high peak to mean ratio with most of the signal content at low levels. To decrease power dissipation, Class G has multiple voltage supplies. The LM48824 has two discrete voltage supplies at the output of the buck, 1.1V and 1.8V. When the output reached the threshold to switch to the higher voltage rails, the rails will switch from 1.1V to 1.8V. When the output falls below the required voltage rails for a set period of time, it will switch back to the lower rail until the next time the threshold is reached. Power dissipation is greatly reduced for typical musical or voice sources. The drawing below shows how a musical output may look. The green lines are the supply voltages at the output of the buck converter.

#### DIFFERENTIAL AMPLIFIER EXPLANATION

The LM48824 features a differential input stage, which offers improved noise rejection compared to a single-ended input amplifier. Because a differential input amplifier amplifies the difference between the two input signals, any component common to both signals is cancelled.

#### SYNCHRONOUS RECTIFIER

The buck converter in the LM48824 uses an internal NFET synchronous rectifier to reduce rectifier forward voltage drop and associated power loss. Synchronous rectification provides a significant improvement in efficiency whenever the output voltage is relative low compared to the voltage drop across an ordinary rectifier diode and eliminating the need for the diode.

#### **CURRENT LIMITING**

A current limit of the buck converter in the LM48824 allows the device to protect itself and external components during overload conditions.

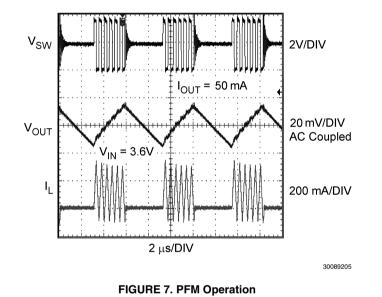

#### **PFM OPERATION**

During PFM(Pulse-Frequency Modulation) operation, if the output voltage of the buck converter is below the 'high' PFM comparator threshold, the PMOS power switch is turned on. It remains on until the output voltage reaches the 'high' PFM threshold or the peak current exceeds the I<sub>PFM</sub> level set for PFM mode. The typical peak current in PFM mode is I<sub>PFM</sub> = 112mA + V<sub>DD</sub>/27\Omega.

Once the PMOS power switch is turned off, the NMOS power switch is turned on until the inductor current ramps to zero. When the NMOS zero-current condition is detected, the NMOS power switch is turned off. If the output voltage is below the 'high' PFM comparator threshold, the PMOS switch is again turned on and the cycle is repeated until the output reaches the desired level. Once the output reaches the 'high' PFM threshold, the NMOS switch is turned on briefly to ramp the inductor current to zero and then both output switches are turned off and the part enters an extremely low power mode.

#### SOFT START

The buck converter has a soft-start circuit that limits in-rush current during start-up. During start-up the switch current limit is increased in steps. Soft start is activated only if global SHDN goes from 1 to 0 after  $V_{\text{DD}}$  reaches 2.7V. Soft start is implemented by increasing switch current limit in steps of 70-mA, 140mA, 280mA, and 750mA (typical switch current limit). The start-up time thereby depends on the output capacitor and load current of the buck converter. Typical start-up times with a 10uF output capacitor and 150mA load is 280us and with 5mA load is 240us.

#### **COMMON-MODE SENSE**

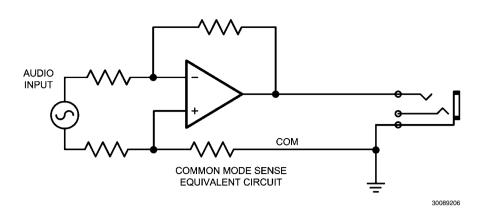

The LM48824 features a ground (common mode) sensing feature. In noisy applications, or where the headphone jack is

used as a line out to other devices, noise pick up and ground imbalance can degrade audio quality. The LM48824 COM input senses and corrects any noise at the headphone return, or any ground imbalance between the headphone return and device ground, improving audio reproduction. Connect COM directly to the headphone return terminal of the headphone jack (*Figure 8*). No additional external components are required. Connect COM to GND if the common-mode sense feature is not in use.

FIGURE 8. COM Connection

#### SHUTDOWN FUNCTION

The LM48824 features individual amplifier shutdown control and a global device shutdown control.

Bit B0 (SHDN) of the MODE CONTROL register controls the global shutdown for the entire device. Set SHDN = 1 to put the device into current-saving shutdown mode, and set SHDN = 0 for normal operation. SHDN defaults to 1 at power-up.

Bit B7 (HPL\_EN) and Bit B6 (HPR\_EN) of the MODE CON-TROL register (register address 0x01h) controls the left and right headphone amplifier shutdown respectively. Set HPL\_EN = 0 to set the left channel headphone amplifier to shutdown and set HPL\_EN = 1 to enable left channel operation. Set HPR\_EN = 0 to set the right channel headphone amplifier to shutdown and set HPR\_EN = 1 to enable right channel operation. The left and right channel amplifier shutdowns operate individually.

The LM48824 has a shutdown time of 3ms to complete the internal shutdown sequence. After SHDN is set to 1, any new I<sup>2</sup>C commands should only be sent after the 3ms shutdown time to ensure proper operation of the device.

#### **MUTE FUNCTION**

The LM48824 features independent left and right channel mute functions.

Bit B7 (MUTE\_L) and Bit B6 (MUTE\_R) of the VOLUME CONTROL register (register address 0x02h) controls the mute function of the left and right channels respectively. Set  $MUTE_L = 1$  to mute the left channel and set the  $MUTE_R =$ 1 to mute the right channel. Set  $MUTE_L = 0$  and  $MUTE_R =$ 0 to disable mute on the respective channels.  $MUTE_L$  and  $MUTE_R$  defaults to 1 at power-up.

#### LOW THD+N MODE

The LM48824 features a Low THD mode that reduces THD +N to improve audio qaulity. Set B3 (Low\_THD) of the OUT-PUT CONTROL register (register address 0x03h) to 1 to enable the Low THD mode. There is a quiescent and operating current increase in Low THD mode. See Electrical Characteristics table and Typical Performance Characteristics for reference.

#### **PROPER SELECTION OF EXTERNAL COMPONENTS**

#### **INDUCTOR SELECTION**

There are two main considerations when choosing an inductor; the inductor saturation current and the inductor current ripple should be small enough to achieve the desired output voltage ripple. Different saturation current rating specifications are followed by different manufacturers so attention must be given to details. Saturation current ratings are typically specified at 25°C, ratings at the maximum ambient temperature of application should be requested from the manufacturer. Shielded capacitors are preferred since these capacitors radiate less noise. Inductors with low DCR should also be considered to minimize the efficiency.

Inductor value involves trade-offs in performance. Larger inductors reduce inductor triple current, which typically means less output voltage ripple (for a given size of output capacitor).

#### **REGULATOR INPUT CAPACITOR SELECTION (C3)**

A ceramic input capacitor of  $1\mu$ F, 6.3V is sufficient for most applications. Place the input capacitor as close as possible to the V<sub>DD</sub> pin of the device. A larger value may be used for improved input voltage filtering. Use X7R or X5R types; do not use Y5V. DC bias characteristics of ceramic capacitors must be considered when selecting case sizes like 0805 and 0603.

#### **REGULATOR OUTPUT CAPACITOR SELECTION (C4)**

A low ESR ceramic output capacitor of  $10\mu$ F, 6.3V is sufficient for most applications. Use X7R or X5R types; do not use Y5V. DC bias characteristics of ceramic capacitors must be considered when selecting case sizes like 0805 and 0603. DC bias characteristics vary from manufacturer to manufacturer and dc bias curves should be requested from them as part of the capacitor selection process.

#### **CHARGE PUMP CAPACITOR SELECTION**

Use low ESR ceramic capacitors (less than 100m  $\!\Omega\!)$  for optimum performance.

#### **CHARGE PUMP FLYING CAPACITOR (C1)**

The flying capacitor (C1) affects the load regulation and output impedance of the charge pump. A C1 value that is too low results in a loss of current drive, leading to a loss of amplifier headroom. A higher valued C1 improves load regulation and lowers charge pump output impedance to an extent. Above  $2.2\mu$ F, the R<sub>DS(ON)</sub> of the charge pump switches and the ESR of C1 and C2 dominate the output impedance. A lower value capacitor can be used in systems with low maximum output power requirements.

#### **CHARGE PUMP HOLD CAPACITOR (C2)**

The value and ESR of the hold capacitor (C2) directly affects the ripple on  $\text{CPV}_{SS}$ . Increasing the value of C2 reduces output ripple. Decreasing the ESR of C2 reduces both output ripple and charge pump output impedance. A lower value capacitor can be used in systems with low maximum output power requirements.

#### **Amplifier Input Capacitor Selection**

Input capacitors may be required for some applications, or when the audio source is single-ended. Input capacitors block the DC component of the audio signal, eliminating any conflict between the DC component of the audio source and the bias voltage of the LM48824. The input capacitors create a highpass filter with the input resistors RIN. The -3dB point of the high-pass filter is found using Equation (1) below.

$$f = 1 / 2\pi R_{IN}C_{IN} \quad (Hz) \tag{1}$$

Where the value of  $\mathsf{R}_{\mathsf{IN}}$  is given in the Electrical Characteristics Table.

High-pass filtering the audio signal can be beneficial for some applications. When the LM48824 is using a single-ended source, power supply noise on the ground is seen as an input signal. Setting the high-pass filter point above the power supply noise frequencies, 217Hz in a GSM phone, for example, filters out the noise such that it is not amplified and heard on the output. Capacitors with a tolerance of 10% or better are recommended for impedance matching and improved CMRR and PSRR.

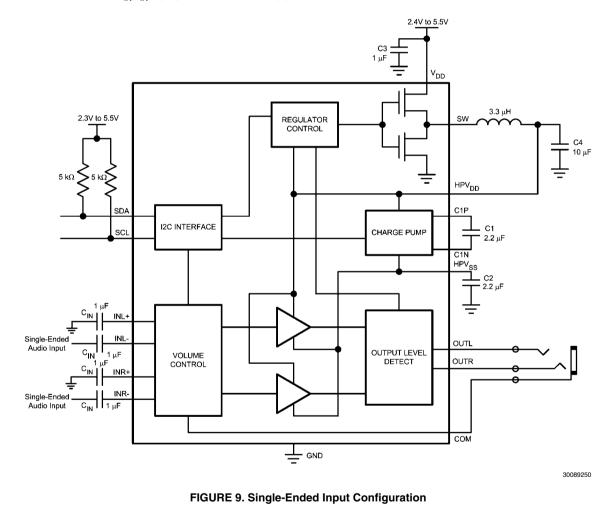

#### SINGLE-ENDED AUDIO AMPLIFIER CONFIGURATION

The LM48824 is compatible with single-ended sources. Figure 9 shows the typical single-ended applications circuit. Input coupling capacitors are required for single-ended configuration.

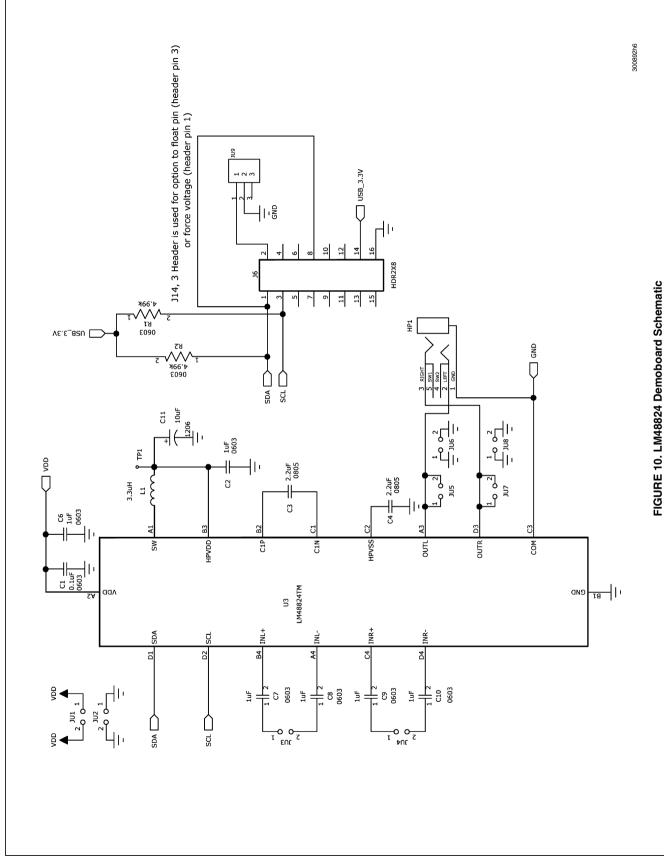

#### PCB LAYOUT CONFIGURATION

| Designator | Quantity | Description                                                         |

|------------|----------|---------------------------------------------------------------------|

| C1         | 1        | 10µF ±10% 16V 500Ω Tantalum Capacitor (B Case) AVX TPSB106K016R0500 |

| C2         | 1        | 1µF ±10% 16V X5R Ceramic Capacitor (603) Panasonic ECJ-1VB1C105K    |

| C3, C8, C9 | 3        | 2.2µF ±10% 10V X5R Ceramic Capacitor (603) Panasonic ECJ-1VB1A225K  |

| C4 – C7    | 4        | 1µF ±10% 16V X7R Ceramic Capacitor (1206) Panasonic ECJ-3YB1C105K   |

| R1, R2     | 2        | 5kΩ ±5% 1/10W Thick Film Resistor (603) Vishay CRCW06035R1KJNEA     |

| L1         | 1        | 3.3µH ± 30% 1.2A Inductor Murata LQM2MPN3R3NG0L                     |

| J1         | 1        | Stereo Headphone Jack                                               |

| J2         | 1        | 16-Pin Boardmount Socket 3M 8516-4500JL                             |

| JU1        | 1        | 3 Pin Header                                                        |

| JU2        | 1        | 2 Pin Header                                                        |

| LM4822TM   | 1        | LM48824TM (16-Bump microSMD)                                        |

## **Demoboard Schematic**

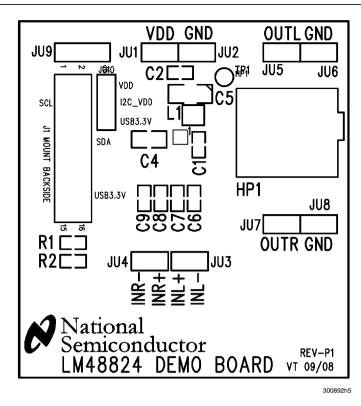

FIGURE 11. Top Silkscreen

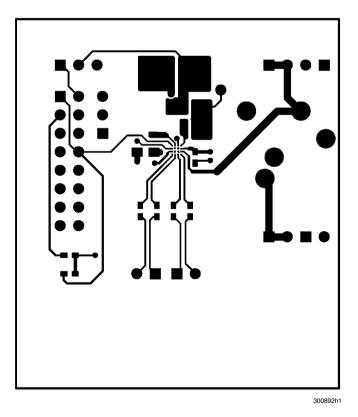

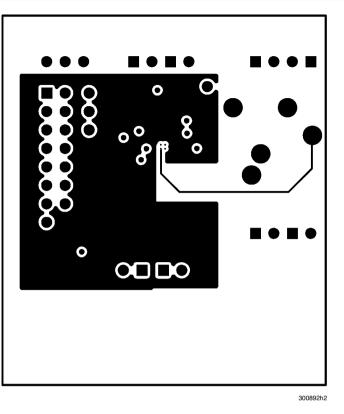

FIGURE 12. Top Layer

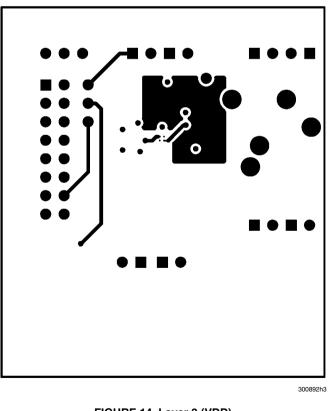

FIGURE 13. Layer 2 (GND)

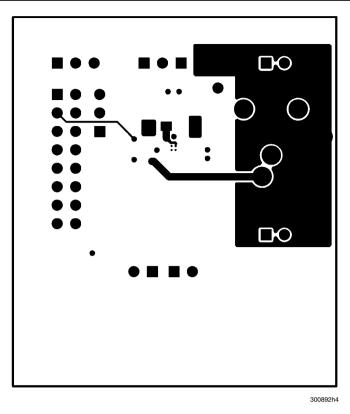

FIGURE 15. Bottom Layer

## **Revision History**

| Rev  | Date     | Description                             |

|------|----------|-----------------------------------------|

| 1.0  | 08/06/09 | Initial released of the full datasheet. |

| 1.01 | 08/31/09 | Text edits.                             |

## Physical Dimensions inches (millimeters) unless otherwise noted

すべて商標および登録商標は、それぞれの所有者に帰属します。

この資料は、Texas Instruments Incorporated (TI) が英文で記述した資料 を、皆様のご理解の一動として頂くために日本テキサス・インスツルメンツ (日本TI) が英文から和文勾翻訳して作成したものです。 資料によっては正規英語版資料の更新に対応していないものがあります。 日本TIによる和文資料は、あくまでもTI正規英語版をご理解頂くための補 助的参考資料としてご使用下さい。 製品のご検討およびご採用にあたりましては必ず正規英語版の最新資料を ご確認下さい。 マロのした目およびこ休用にのたりましては少す正況失語版の取新員科でご確認下さい。

Tiおよび日本Tiは、正規英語版にて更新の情報を提供しているにもかかわ

らず、更新以前の情報に基づいて発生した問題や障害等につきましては如

何なる責任も負いません。

TEXAS INSTRUMENTS

## ご注意

日本テキサス・インスツルメンツ株式会社(以下TIJといいます)及びTexas Instruments Incorporated (TIJの親会社、以下TIJないしTexas Instruments Incorporatedを総称してTIといいます)は、その製品及びサービスを任意に修正し、 改善、改良、その他の変更をし、もしくは製品の製造中止またはサービスの提供を 中止する権利を留保します。従いまして、お客様は、発注される前に、関連する最 新の情報を取得して頂き、その情報が現在有効かつ完全なものであるかどうかご 確認下さい。全ての製品は、お客様とTIJとの間に取引契約が締結されている場 合は、当該契約条件に基づき、また当該取引契約が締結されていない場合は、ご 注文の受諾の際に提示されるTIJの標準販売契約約款に従って販売されます。

TIは、そのハードウェア製品が、TIの標準保証条件に従い販売時の仕様に対応 した性能を有していること、またはお客様とTIIとの間で合意された保証条件に従 い合意された仕様に対応した性能を有していることを保証します。検査およびそ の他の品質管理技法は、TIが当該保証を支援するのに必要とみなす範囲で行 なわれております。各デバイスの全てのパラメーターに関する固有の検査は、政府 がそれ等の実行を義務づけている場合を除き、必ずしも行なわれておりません。

TIは、製品のアプリケーションに関する支援もしくはお客様の製品の設計につい て責任を負うことはありません。TI製部品を使用しているお客様の製品及びその アプリケーションについての責任はお客様にあります。TI製部品を使用したお客様 の製品及びアプリケーションについて想定されうる危険を最小のものとするため、 適切な設計上および操作上の安全対策は、必ずお客様にてお取り下さい。

TIは、TIの製品もしくはサービスが使用されている組み合せ、機械装置、もしくは 方法に関連しているTIの特許権、著作権、回路配置利用権、その他のTIの知的 財産権に基づいて何らかのライセンスを許諾するということは明示的にも黙示的に も保証も表明もしておりません。TIが第三者の製品もしくはサービスについて情報 を提供することは、TIが当該製品もしくはサービスを使用することについてライセン スを与えるとか、保証もしくは是認するということを意味しません。そのような情報を 使用するには第三者の特許その他の知的財産権に基づき当該第三者からライセ ンスを得なければならない場合もあり、またTIの特許その他の知的財産権に基づ きTIからライセンスを得て頂かなければならない場合もあります。

TIのデータ・ブックもしくはデータ・シートの中にある情報を複製することは、その情報 に一切の変更を加えること無く、かつその情報と結び付られた全ての保証、条件、 制限及び通知と共に複製がなされる限りにおいて許されるものとします。当該情 報に変更を加えて複製することは不公正で誤認を生じさせる行為です。TIは、そ のような変更された情報や複製については何の義務も責任も負いません。

TIの製品もしくはサービスについてTIにより示された数値、特性、条件その他のパ ラメーターと異なる、あるいは、それを超えてなされた説明で当該TI製品もしくは サービスを再販売することは、当該TI製品もしくはサービスに対する全ての明示的 保証、及び何らかの黙示的保証を無効にし、かつ不公正で誤認を生じさせる行為 です。TIは、そのような説明については何の義務も責任もありません。

TIは、TIの製品が、安全でないことが致命的となる用途ないしアプリケーション(例 えば、生命維持装置のように、TI製品に不良があった場合に、その不良により相当 な確率で死傷等の重篤な事故が発生するようなもの)に使用されることを認めて おりません。但し、お客様とTIの双方の権限有る役員が書面でそのような使用に ついて明確に合意した場合は除きます。たとえTIがアプリケーションに関連した情 報やサポートを提供したとしても、お客様は、そのようなアプリケーションの安全面及 び規制面から見た諸問題を解決するために必要とされる専門的知識及び技術を 持ち、かつ、お客様の製品について、またTI製品をそのような安全でないことが致 命的となる用途に使用することについて、お客様が全ての法的責任、規制を遵守 する責任、及び安全に関する要求事項を満足させる責任を負っていることを認め、 かつそのことに同意します。さらに、もし万一、TIの製品がそのような安全でないこ とが致命的となる用途に使用されたことによって損害が発生し、TIないしその代表 者がその損害を賠償した場合は、お客様がTIないしその代表者にその全額の補 償をするものとします。

TI製品は、軍事的用途もしくは宇宙航空アプリケーションないし軍事的環境、航空 宇宙環境にて使用されるようには設計もされていませんし、使用されることを意図 されておりません。但し、当該TI製品が、軍需対応グレード品、若しくは「強化プラス ティック 製品としてTIが特別に指定した製品である場合は除きます。TIが軍需対 応グレード品として指定した製品のみが軍需品の仕様書に合致いたします。お客 様は、TIが軍需対応グレード品として指定していない製品を、軍事的用途もしくは 軍事的環境下で使用することは、もっぱらお客様の危険負担においてなされると いうこと、及び、お客様がもっぱら責任をもって、そのような使用に関して必要とされ る全ての法的要求事項及び規制上の要求事項を満足させなければならないこと を認め、かつ同意します。

TI製品は、自動車用アプリケーションないし自動車の環境において使用されるよう には設計されていませんし、また使用されることを意図されておりません。但し、TI がISO/TS 16949の要求事項を満たしていると特別に指定したTI製品は除きます。 お客様は、お客様が当該TI指定品以外のTI製品を自動車用アプリケーションに使 用しても、TIは当該要求事項を満たしていなかったことについて、いかなる責任も 負わないことを認め、かつ同意します。

Copyright © 2012, Texas Instruments Incorporated 日本語版 日本テキサス・インスツルメンツ株式会社

以上

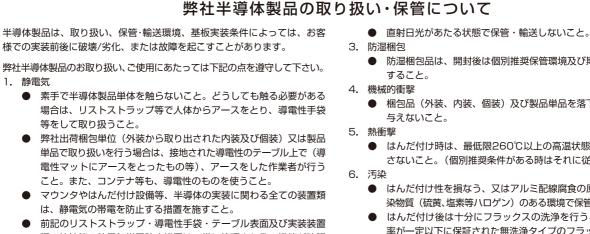

- 等をして取り扱うこと。 弊社出荷梱包単位(外装から取り出された内装及び個装)又は製品 単品で取り扱いを行う場合は、接地された導電性のテーブル上で(導 電性マットにアースをとったもの等)、アースをした作業者が行う こと。また、コンテナ等も、導電性のものを使うこと。

- マウンタやはんだ付け設備等、半導体の実装に関わる全ての装置類 は、静電気の帯電を防止する措置を施すこと。

- 前記のリストストラップ・導電性手袋・テーブル表面及び実装装置 類の接地等の静電気帯電防止措置は、常に管理されその機能が確認 されていること。

- 2. 温·湿度環境

1. 静電気

温度:0~40℃、相対湿度:40~85%で保管・輸送及び取り扱 いを行うこと。(但し、結露しないこと。)

- 防湿梱包品は、開封後は個別推奨保管環境及び期間に従い基板実装

- 梱包品(外装、内装、個装)及び製品単品を落下させたり、衝撃を

- はんだ付け時は、最低限260℃以上の高温状態に、10秒以上さら さないこと。(個別推奨条件がある時はそれに従うこと。)

- はんだ付け性を損なう、又はアルミ配線腐食の原因となるような汚 染物質(硫黄、塩素等ハロゲン)のある環境で保管・輸送しないこと。

- はんだ付け後は十分にフラックスの洗浄を行うこと。(不純物含有 率が一定以下に保証された無洗浄タイプのフラックスは除く。)