I M5009

JAJSLR9I - FEBRUARY 2006 - REVISED MAY 2021

#### ワイド入力、100V、150mA、降圧スイッチング・レギュレー LM5009

# 1 特長

- 新製品:LM5163 100V、0.5A の同期降圧 DC/DC コ ンバータ

- N チャネル MOSFET を内蔵

- 出力電流能力:150mA

- 超高速の過渡応答

- ループ補償が不要

- V<sub>IN</sub>のフィードフォワードにより一定の動作周波数を供 給します

- スイッチング周波数は600kHzを超えることがあります

- 高効率動作

- -40℃~+125℃の範囲で 2% 精度の 2.5V フィード バック

- スタートアップ用レギュレータを内蔵

- インテリジェントな電流制限保護

- 外部でのシャットダウン制御

- サーマル・シャットダウン

- 8ピン VSSOP および放熱特性の優れた 8ピン WSON パッケージ

# 2 アプリケーション

- 従来型リニア・レギュレータ・アプリケーション用ヒートシ ンク・エリミネータ

- 12V、24V、36V、48V の整流 AC システム

- 非絶縁型の充電結合型 AC メイン電源

- LED 用電流源

# 3 概要

LM5009 降圧スイッチング・レギュレータには、低コストで 高効率の降圧レギュレータを実装するために必要な、す べての機能が搭載されています。このデバイスは、9.5V~ 95V の入力ソースから 150mA の負荷電流を駆動できま す。入力電圧と出力電圧に応じて、スイッチング周波数が 600kHz を超えることがあります。出力電圧は 2.5~85V に設定できます。この高電圧レギュレータは、N チャネル 降圧スイッチと内部スタートアップ・レギュレータを搭載して います。8 ピン VSSOP パッケージおよび放熱特性の優 れた8ピン WSON パッケージで供給され、容易に実装 できます。レギュレータの動作は、VIN に反比例するオン 時間を使用する制御方式を基礎とします。この機能によ り、負荷および入力電圧が変化しても、動作周波数は比 較的一定に維持されます。ループ補償を必要としない制 御方式により、超高速の過渡応答が得られます。 Vout に 反比例する強制的オフ時間を持たせるインテリジェントな 電流制限機能が実装されています。この方式により、短絡 保護が確保され、最小限のフォールドバックを提供しま す。他の機能として、サーマルシャットダウン、Vcc・アンダ ーボルテージ・ロックアウト、ゲートドライブ・アンダーボル テージ・ロックアウト、最大デューティ・サイクル制限などが あります。

新しい製品 LM5163 は、部品点数を削減し、ソリューショ ン・サイズを縮小し、動作時の静止電流を低減し、他の多 くの機能を実現します。LM5163 を使用して WEBENCH® 設計を開始します。

### 製品情報

|          | A-CHH 113 114 |                 |  |  |

|----------|---------------|-----------------|--|--|

| 部品番号     | パッケージ         | 本体サイズ (公称)      |  |  |

| LM5009   | VSSOP (8)     | 3.00mm × 3.00mm |  |  |

| LIVISOUS | WSON (8)      | 4.00mm×4.00mm   |  |  |

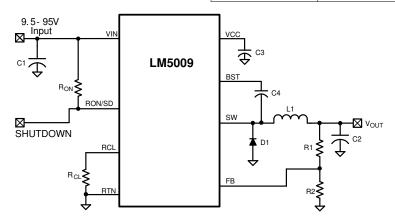

代表的なアプリケーション回路

# **Table of Contents**

| 1 特長                                 | 1  | 8 Application and Implementation                    | 11 |

|--------------------------------------|----|-----------------------------------------------------|----|

| 2 アプリケーション                           |    | 8.1 Application Information                         | 11 |

| 3 概要                                 |    | 8.2 Typical Application                             |    |

| 4 Revision History                   |    | 8.3 Do's and Don'ts                                 |    |

| 5 Pin Configuration and Functions    |    | 9 Power Supply Recommendations                      | 16 |

| 6 Specifications                     |    | 10 Layout                                           |    |

| 6.1 Absolute Maximum Ratings         |    | 10.1 Layout Guidelines                              | 17 |

| 6.2 ESD Ratings                      |    | 10.2 Layout Example                                 |    |

| 6.3 Recommended Operating Conditions |    | 11 Device and Documentation Support                 |    |

| 6.4 Thermal Information              |    | 11.1 Documentation Support                          |    |

| 6.5 Electrical Characteristics       |    | 11.2 Receiving Notification of Documentation Update |    |

| 6.6 Typical Characteristics          |    | <b>11.3</b> サポート・リソース                               | 18 |

| 7 Detailed Description               |    | 11.4 Trademarks                                     |    |

| 7.1 Overview                         |    | 11.5 Electrostatic Discharge Caution                | 18 |

| 7.2 Functional Block Diagram         |    | 11.6 Glossary                                       |    |

| 7.3 Feature Description              |    | 12 Mechanical, Packaging, and Orderable             |    |

| 7.4 Device Functional Modes          |    | Information                                         | 18 |

| 4 Revision History                   | 10 |                                                     |    |

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に進じています。

| 賃料番号木尾の央子は収割を衣していまり。その収割限歴は央部版に準していまり。                                                                                                                                                              |              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| Changes from Revision H (October 2015) to Revision I (May 2021)                                                                                                                                     | Page         |

| • LM5163 プロモーションの情報を追加                                                                                                                                                                              | 1            |

| • 文書全体にわたって表、図、相互参照の採番方法を更新                                                                                                                                                                         | 1            |

| • <i>セクション</i> <b>2</b> の箇条書きを変更                                                                                                                                                                    | 1            |

| • <i>セクション</i> <b>3</b> 、編集を変更                                                                                                                                                                      | 1            |

| Changes from Revision G (February 2013) to Revision H (October 2015)  • 「ESD 定格」表、「機能説明」セクション、「デバイスの機能モード」セクション、「アプリケーションと源に関する推奨事項」セクション、「レイアウト」セクション、「デバイスおよびドキュメントのサポートル、パッケージ、および注文情報」セクションを追加。 | 」セクション、「メカニカ |

| Changes from Revision F (February 2013) to Revision G (February 2013)                                                                                                                               | Page         |

| Changed layout of National Data Sheet to TI format                                                                                                                                                  | 16           |

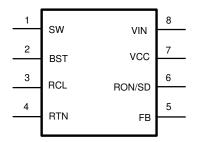

# **5 Pin Configuration and Functions**

図 5-1. DGK, NGU Packages 8-Pin VSSOP, WSON Top View

表 5-1. Pin Functions

| Р      | PIN I/O |     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|--------|---------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME   | NO.     | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| BST    | 2       | I   | Boost pin. An external capacitor is required between the BST and SW pins. A $0.022$ - $\mu$ F ceramic capacitor is recommended. An internal diode charges the capacitor from $V_{CC}$ .                                                                                                                                                                                                                                                                                                  |  |  |  |

| EP     | _       | _   | Exposed pad (WSON package only). Exposed metal pad on the underside of the device. Connecting this pad to the PC board ground plane is recommended to aid in heat dissipation.                                                                                                                                                                                                                                                                                                           |  |  |  |

| FB     | 5       | I   | Feedback input from regulated output. This pin is connected to the inverting input of the internal regulation comparator. The regulation threshold is 2.5 V.                                                                                                                                                                                                                                                                                                                             |  |  |  |

| RCL    | 3       | I   | Current limit off-time set pin. A resistor between this pin and RTN sets the off-time when current limit is detected. The off-time is preset to 35 $\mu s$ if FB = 0 V.                                                                                                                                                                                                                                                                                                                  |  |  |  |

| RON/SD | 6       | I   | On-time set pin. A resistor between this pin and VIN sets the switch on-time as a function of $V_{\text{IN}}$ . The minimum recommended on-time is 250 ns at the maximum input voltage. This pin can be used for remote shutdown.                                                                                                                                                                                                                                                        |  |  |  |

| RTN    | 4       | _   | Ground pin. Ground for the entire circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| sw     | 1       | 0   | Switching output. Power switching output. Connect to the inductor, recirculating diode, and bootstrap capacitor.                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| vcc    | 7       | 0   | Output from the internal high-voltage startup regulator. Regulated at 7.0 V. If an auxiliary voltage is available to raise the voltage on this pin above the regulation set point (7 V), the internal series pass regulator shuts down, reducing the device power dissipation. Do not exceed 14 V. This voltage provides gate drive power for the internal buck switch. An internal diode is provided between this pin and the BST pin. A local 0.1-µF decoupling capacitor is required. |  |  |  |

| VIN    | 8       | I   | Input voltage. Recommended operating range: 9.5 V to 95 V.                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

# **6 Specifications**

# **6.1 Absolute Maximum Ratings**

over operating free-air temperature range (unless otherwise noted)(1)

|                                       | MIN  | MAX       | UNIT |

|---------------------------------------|------|-----------|------|

| V <sub>IN</sub> to RTN                | -0.3 | 100       | V    |

| BST to RTN                            | -0.3 | 114       | V    |

| SW to RTN (steady-state)              |      | <b>–1</b> | V    |

| BST to VCC                            |      | 100       | V    |

| BST to SW                             |      | 14        | V    |

| VCC to RTN                            |      | 14        | V    |

| All other inputs to RTN               | -0.3 | 7         | V    |

| Storage temperature, T <sub>stg</sub> | -65  | 150       | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 6.2 ESD Ratings

|    |       |                         |                                                                                | VALUE | UNIT |

|----|-------|-------------------------|--------------------------------------------------------------------------------|-------|------|

|    | 1     | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup> (3)          | ±2000 | \/   |

| Ι, | (ESD) | Liectiostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±750  | , v  |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

- (3) The human body model is a 100-pF capacitor discharged through a 1.5-k $\Omega$  resistor into each pin.

# **6.3 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)(1)

|                 |                                | MIN | MAX | UNIT |

|-----------------|--------------------------------|-----|-----|------|

| V <sub>IN</sub> | Line voltage                   | 9.5 | 95  | V    |

|                 | Operating junction temperature | -40 | 125 | °C   |

<sup>(1)</sup> Operating ratings are conditions under which operation of the device is intended to be functional. For specifications and test conditions, see the セクション 6.5.

# **6.4 Thermal Information**

|                       |                                              | LM5009      |            |      |  |

|-----------------------|----------------------------------------------|-------------|------------|------|--|

|                       | THERMAL METRIC(1)                            | DGK (VSSOP) | NGU (WSON) | UNIT |  |

|                       |                                              | 8 PINS      | 8 PINS     |      |  |

| R <sub>θJA</sub>      | Junction-to-ambient thermal resistance       | 157.7       | 42.8       | °C/W |  |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 50.2        | 41.5       | °C/W |  |

| R <sub>0JB</sub>      | Junction-to-board thermal resistance         | 77.9        | 20.1       | °C/W |  |

| ΨЈТ                   | Junction-to-top characterization parameter   | 4.5         | 0.4        | °C/W |  |

| ΨЈВ                   | Junction-to-board characterization parameter | 76.5        | 20.2       | °C/W |  |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | n/a         | 4.5        | °C/W |  |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

## 6.5 Electrical Characteristics

Typical limits are for  $T_J$  = 25°C only, and all maximum and minimum limits apply over the junction temperature ( $T_J$ ) range of – 40°C to +125°C. Minimum and maximum limits are specified through test, design, or statistical correlation. Typical values represent the most likely parametric norm at  $T_J$  = 25°C, and are provided for reference purposes only. Unless otherwise stated, the following conditions apply:  $V_{IN}$  = 48 V and  $R_{ON}$  = 200 k $\Omega$ . (1).

|                     | PARAMETER                                                                 | TEST CONDITIONS                                          | MIN   | TYP   | MAX   | UNIT |

|---------------------|---------------------------------------------------------------------------|----------------------------------------------------------|-------|-------|-------|------|

| V <sub>CC</sub> SUP | PLY                                                                       |                                                          |       |       |       |      |

| V <sub>CC</sub> reg | V <sub>CC</sub> regulator output                                          |                                                          | 6.6   | 7     | 7.4   | V    |

|                     | V <sub>CC</sub> current limit <sup>(2)</sup>                              |                                                          |       | 9.5   |       | mA   |

|                     | V <sub>CC</sub> undervoltage lockout voltage (V <sub>CC</sub> increasing) |                                                          |       | 6.3   |       | V    |

|                     | V <sub>CC</sub> undervoltage hysteresis                                   |                                                          |       | 200   |       | mV   |

|                     | V <sub>CC</sub> UVLO delay (filter)                                       | 100-mV overdrive                                         |       | 10    |       | μs   |

|                     | I <sub>IN</sub> operating current                                         | Non-switching, FB = 3 V                                  |       | 485   | 675   | μA   |

|                     | I <sub>IN</sub> shutdown current                                          | RON/SD = 0 V                                             |       | 76    | 150   | μA   |

| SWITCH              | CHARACTERISTICS                                                           |                                                          |       |       | -     |      |

|                     | Buck switch Rds(on)                                                       | I <sub>TEST</sub> = 200 mA <sup>(3)</sup>                |       | 2.0   | 4.4   | Ω    |

|                     | Gate drive UVLO                                                           | V <sub>BST</sub> - V <sub>SW</sub> rising                | 3.4   | 4.5   | 5.5   | V    |

|                     | Gate drive UVLO hysteresis                                                |                                                          |       | 430   |       | mV   |

| CURREN              | IT LIMIT                                                                  |                                                          |       |       |       |      |

|                     | Current limit threshold                                                   |                                                          | 0.25  | 0.31  | 0.37  | Α    |

|                     | Current limit response time                                               | I <sub>switch</sub> overdrive = 0.1-A time to switch off |       | 400   |       | ns   |

|                     | OFF time generator (test 1)                                               | FB = 0 V, R <sub>CL</sub> = 100 kΩ                       |       | 35    |       | μs   |

|                     | OFF time generator (test 2)                                               | FB = 2.3 V, R <sub>CL</sub> = 100 kΩ                     |       | 2.56  |       | μs   |

| ON TIME             | GENERATOR                                                                 |                                                          |       |       |       |      |

|                     | T <sub>ON</sub> - 1                                                       | $V_{IN} = 10 \text{ V}, R_{ON} = 200 \text{ k}\Omega$    | 2.15  | 2.77  | 3.5   | μs   |

|                     | T <sub>ON</sub> - 2                                                       | V <sub>IN</sub> = 95 V, R <sub>ON</sub> = 200 kΩ         | 200   | 300   | 420   | ns   |

|                     | Remote shutdown threshold                                                 | Rising                                                   | 0.4   | 0.7   | 1.05  | V    |

|                     | Remote shutdown hysteresis                                                |                                                          |       | 35    |       | mV   |

| MINIMUN             | OFF TIME                                                                  |                                                          |       |       |       |      |

|                     | Minimum off timer                                                         | FB = 0 V                                                 |       | 300   |       | ns   |

| REGULA              | TION AND OV COMPARATORS                                                   | ,                                                        |       |       | 1     |      |

|                     | FB reference threshold                                                    | Internal reference, trip point for switch on             | 2.445 | 2.5   | 2.550 | V    |

|                     | FB overvoltage threshold                                                  | Trip point for switch off                                |       | 2.875 |       | V    |

|                     | FB bias current                                                           |                                                          |       | 1     |       | nA   |

| THERMA              | L SHUTDOWN                                                                | ,                                                        |       |       |       |      |

| T <sub>sd</sub>     | Thermal shutdown temperature                                              |                                                          |       | 165   |       | °C   |

|                     | Thermal shutdown hysteresis                                               |                                                          |       | 25    |       | °C   |

<sup>(1)</sup> All electrical characteristics having room temperature limits are tested during production with T<sub>A</sub> = T<sub>J</sub> = 25°C. All hot and cold limits are specified by correlating the electrical characteristics to process and temperature variations and applying statistical process control.

<sup>(2)</sup> The V<sub>CC</sub> output is intended as a self bias for the internal gate drive power and control circuits. Device thermal limitations limit external loading.

<sup>(3)</sup> For devices procured in the WSON-8 package, the Rds(on) limits are specified by design characterization data only.

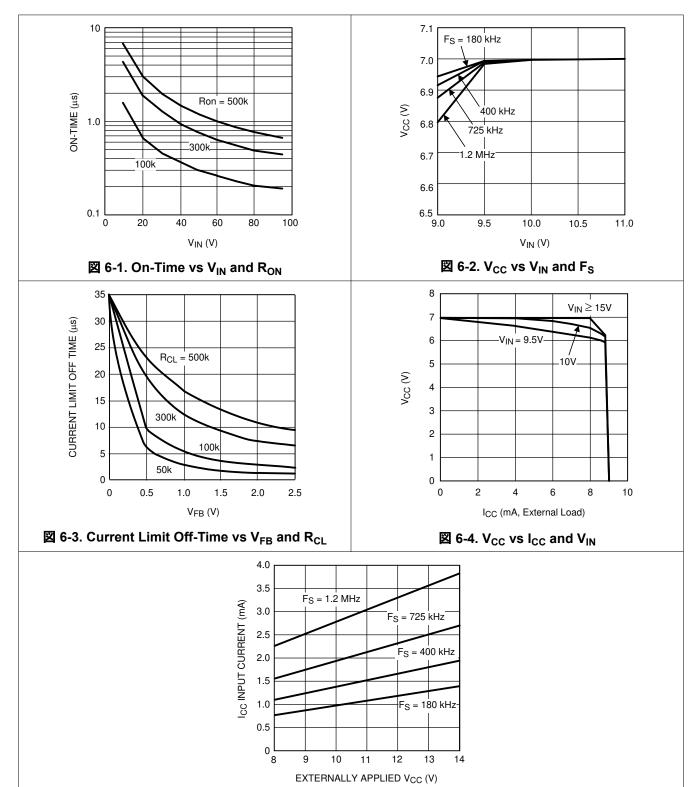

# **6.6 Typical Characteristics**

図 6-5. I<sub>CC</sub> Current vs Applied V<sub>CC</sub> Voltage

# 7 Detailed Description

## 7.1 Overview

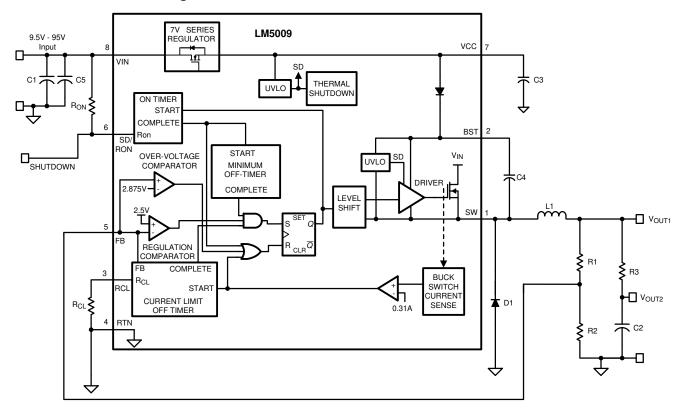

The LM5009 step-down switching regulator features all the functions needed to implement a low-cost, efficient, buck bias power converter. This high-voltage regulator contains a 100-V N-channel buck switch, is easy to implement, and is provided in VSSOP-8 and thermally-enhanced, WSON-8 packages. The regulator is based on a control scheme using an on-time inversely proportional to  $V_{IN}$ . The control scheme requires no loop compensation. Current limit is implemented with forced off-time that is inversely proportional to  $V_{OUT}$ . This scheme ensures short-circuit protection and provides minimum foldback. The functional block diagram of the LM5009 is shown in the  $\frac{1}{2}$ 7.2 section.

The LM5009 can be applied in numerous applications to efficiently regulate down higher voltages. This regulator is well-suited for 48-V telecom and 42-V automotive power bus ranges. Additional features include: thermal shutdown,  $V_{CC}$  undervoltage lockout, gate drive undervoltage lockout, maximum duty cycle limit timer, and the intelligent current limit off timer.

# 7.2 Functional Block Diagram

# 7.3 Feature Description

### 7.3.1 Control Circuit Overview

The LM5009 is a buck dc-dc regulator that uses a control scheme where the on-time varies inversely with line voltage ( $V_{IN}$ ). Control is based on a comparator and the on-time one-shot, with the output voltage feedback (FB) compared to an internal reference (2.5 V). If the FB level is below the reference, then the buck switch is turned on for a fixed time determined by the line voltage and a programming resistor ( $R_{ON}$ ). Following the on period, the switch remains off for at least the minimum off-timer period of 300 ns. If FB is still below the reference at that time, then the switch turns on again for another on-time period. This cycle continues until regulation is achieved, at which time the off-time increases based on the required duty cycle.

The LM5009 operates in discontinuous conduction mode at light load currents, and continuous conduction mode at heavy load current. In discontinuous conduction mode, current through the output inductor starts at zero and

ramps up to a peak during the on-time, then ramps back to zero before the end of the off-time. The next on-time period starts when the voltage at FB falls below the internal reference—until then, the inductor current remains zero. In this mode the operating frequency is lower than in continuous conduction mode, and varies with load current. Therefore, at light loads the conversion efficiency is maintained because the switching losses reduce with the reduction in load and frequency. The discontinuous operating frequency can be calculated as by  $\sharp$  1:

$$F = \frac{V_{OUT}^2 \times L \times 1.28 \times 10^{20}}{R_L \times (R_{ON})^2}$$

(1)

#### where

#### R<sub>I</sub> = the load resistance

In continuous conduction mode, current flows continuously through the inductor and never ramps down to zero. In this mode, the operating frequency is greater than the discontinuous mode frequency and remains relatively constant with load and line variations. The approximate continuous mode operating frequency can be calculated by  $\sharp$  2:

$$F = \frac{V_{OUT}}{1.25 \times 10^{-10} \times R_{ON}}$$

(2)

The output voltage (V<sub>OUT</sub>) is programmed by two external resistors; see the セクション 7.2 section. The regulation point is calculated by 式 3:

$$V_{OUT} = 2.5 \times (R1 + R2) / R2$$

(3)

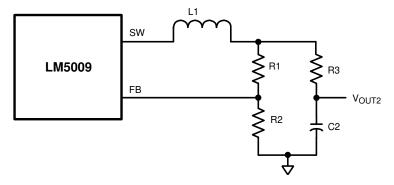

This regulator regulates the output voltage based on ripple voltage at the feedback input, requiring a minimum amount of equivalent series resistance (ESR) for the output capacitor C2. A minimum of 25 mV of ripple voltage at the feedback pin (FB) is required for the LM5009. In cases where the capacitor ESR is too small, additional series resistance may be required (see R3 in the \*\frac{table 2}{2} \text{2.2} \text{2.2} \text{section}).

For applications where lower output voltage ripple is required, the output can be taken directly from a low-ESR output capacitor, as shown in  $\boxtimes$  7-1. However, R3 slightly degrades the load regulation.

図 7-1. Low Ripple Output Configuration

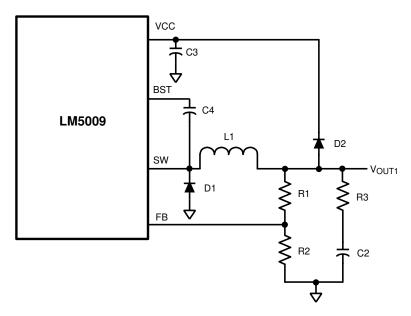

### 7.3.2 High Voltage Startup Regulator

The LM5009 contains an internal high voltage startup regulator. The input pin (VIN) can be connected directly to line voltages up to 95 V, with transient capability to 100 V. The regulator is internally current limited at 9.5 mA. Upon power-up, the regulator sources current into the external capacitor at VCC (C3). When the voltage on the VCC pin reaches the undervoltage lockout threshold of 6.3 V, the buck switch is enabled.

In applications involving a high value for  $V_{IN}$ , where power dissipation in the  $V_{CC}$  regulator is a concern, an auxiliary voltage can be diode connected to the VCC pin. Setting the voltage between 8 V and 14 V shuts off the internal regulator, reducing internal power dissipation, as shown in  $\boxtimes$  7-2. The current required into the VCC pin is illustrated in the  $2/2 \times 2/6.6$  section.

図 7-2. Self-Biased Configuration

### 7.3.3 Regulation Comparator

The feedback voltage at FB is compared to an internal 2.5-V reference. In normal operation (the output voltage is regulated), an on-time period is initiated when the voltage at FB falls below 2.5 V. The buck switch stays on for the programmed on-time, causing the FB voltage to rise above 2.5 V. After the on-time period, the buck switch stays off until the FB voltage again falls below 2.5 V. During start-up, the FB voltage is below 2.5 V at the end of each on-time, resulting in the minimum off-time. Bias current at the FB pin is less than 5 nA over temperature.

#### 7.3.4 Overvoltage Comparator

The feedback voltage at FB is compared to an internal 2.875-V reference. If the voltage at FB rises above 2.875 V, then the on-time pulse is immediately terminated. This condition can occur if the input voltage, or the output load, changes suddenly. The buck switch does not turn on again until the voltage at FB falls below 2.5 V.

#### 7.3.5 On-Time Generator

The on-time for the LM5009 is determined by the  $R_{ON}$  resistor, and is inversely proportional to the input voltage ( $V_{IN}$ ), resulting in a nearly constant frequency because  $V_{IN}$  is varied over its range. The on-time equation is shown in  $\pm 4$ :

$$T_{ON} = 1.25 \times 10^{-10} \times R_{ON} / V_{IN}$$

(4)

Select  $R_{ON}$  for a minimum on-time (at maximum  $V_{IN}$ ) greater than 250 ns, for proper current limit operation. This requirement limits the maximum frequency for each application, depending on  $V_{IN}$  and  $V_{OUT}$ .

### 7.3.6 Current Limit

The LM5009 contains an intelligent current limit off timer. If the current in the buck switch exceeds 0.31 A, then the present cycle is immediately terminated and a non-resettable off timer is initiated. The length of off-time is controlled by an external resistor ( $R_{CL}$ ) and the FB voltage. When FB = 0 V, a maximum off-time is required and the time is preset to 35  $\mu$ s. This condition occurs when the output is shorted and during the initial part of start-up. This amount of time ensures safe short-circuit operation up to the maximum input voltage of 95 V. In cases of

Copyright © 2021 Texas Instruments Incorporated

Submit Document Feedback

overload where the FB voltage is above 0 V (not a short-circuit) the current limit off-time is less than 35 μs. Reducing the off-time during less severe overloads reduces the amount of foldback, recovery time, and start-up time. The off-time is calculated from  $\pm$  5:

$$T_{OFF} = \frac{10^{-5}}{0.285 + \frac{V_{FB}}{(6.35 \times 10^{-6} \times R_{CL})}}$$

(5)

The current limit sensing circuit is blanked for the first 50 ns to 70 ns of each on-time so it is not falsely tripped by the current surge that occurs at turn-on. The current surge is required by the recirculating diode (D1) for its turn-off recovery.

### 7.3.7 N-Channel Buck Switch and Driver

The LM5009 integrates an N-channel buck switch and associated floating high-voltage gate driver. The gate driver circuit works in conjunction with an external bootstrap capacitor and an internal high-voltage diode. A 0.022-µF ceramic capacitor (C4) connected between the BST pin and SW pin provides the voltage to the driver during the on-time.

During each off-time, the SW pin is at approximately -1 V, and the bootstrap capacitor charges from  $V_{CC}$  through the internal diode. The minimum off timer ensures a minimum time for each cycle to recharge the bootstrap capacitor.

An external re-circulating diode (D1) carries the inductor current after the internal buck switch turns off. This diode must be of the ultra-fast or Schottky type to minimize turn-on losses and current overshoot.

### 7.3.8 Thermal Protection

Operate the LM5009 so that the junction temperature does not exceed 125°C during normal operation. An internal thermal shutdown circuit is provided to protect the LM5009 in the event of a higher than normal junction temperature. When activated, typically at 165°C, the controller is forced into a low-power reset state, disabling the buck switch. This feature prevents catastrophic failures from accidental device overheating. When the junction temperature reduces below 140°C (typical hysteresis = 25°C), the buck switch is enabled and normal operation is resumed.

### 7.4 Device Functional Modes

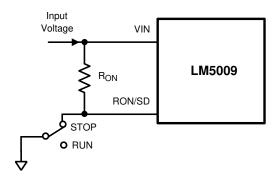

The LM5009 can be remotely disabled by taking the RON/SD pin to ground, as shown in  $\boxtimes$  7-3. The voltage at the RON/SD pin is between 1.7 V and 5 V, depending on  $V_{IN}$  and the value of the  $R_{ON}$  resistor.

図 7-3. Shutdown Implementation

# 8 Application and Implementation

### Note

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes, as well as validating and testing their design implementation to confirm system functionality.

# **8.1 Application Information**

The LM5009 is a non-synchronous buck regulator designed to operate over a wide input voltage range and output current. Spreadsheet-based quick-start calculation tools and the on-line WEBENCH® software can be used to create a buck design along with the bill of materials, estimated efficiency, and the complete solution cost.

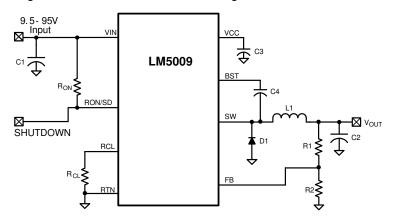

# 8.2 Typical Application

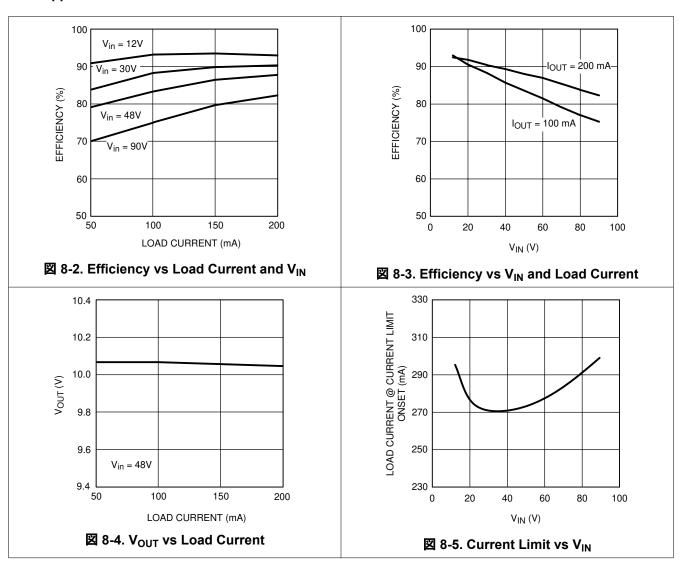

A typical buck application circuit with the LM5009 is shown in  $\boxtimes$  8-1. The circuit can operate over a wide input voltage range of 9.5 V to 95 V and provides a stable output of 10 V over the load current being varied from 50 mA to 200 mA. The resulting curves are shown in  $\boxtimes$  8-2 through  $\boxtimes$  8-5.

図 8-1. Typical Buck Application Circuit

# 8.2.1 Design Requirements

A typical buck application circuit with the LM5009 can be summarized by the operating conditions listed in  $\frac{1}{8}$ 8-1.

| 2,                          |                 |

|-----------------------------|-----------------|

| DESIGN PARAMETER            | EXAMPLE VALUE   |

| Input voltage range         | 9.5 V to 95 V   |

| Output voltage              | 10 V            |

| Load current range          | 50 mA to 200 mA |

| Nominal switching frequency | 330 kHz         |

表 8-1. Design Parameters

### 8.2.2 Detailed Design Procedure

# 8.2.2.1 Output Resistor Divider Selection

**R1 and R2:** From the  $trac{1}{2}$  7.2 section,  $V_{OUT1}$  can be determined to be equal to  $V_{FB} \times (R1 + R2) / R2$ , and because  $V_{FB} = 2.5$  V, the ratio of R1 to R2 calculates as 3:1. Standard values of 3.01 k $\Omega$  (R1) and 1.00 k $\Omega$  (R2) are chosen. Other values can be used as long as the 3:1 ratio is maintained. The selected values, however, provide a small amount of output loading (2.5 mA) in the event that the main load is disconnected and allows the circuit to maintain regulation until the main load is reconnected.

# 8.2.2.2 Frequency Selection

**F<sub>s</sub> and R<sub>ON</sub>:** Unless the application requires a specific frequency, the choice of frequency is generally a compromise because the size of L1 and C2, and the switching losses are affected. The maximum-allowed frequency, based on a minimum on-time of 250 ns, is calculated by  $\stackrel{>}{\atop}$  6:

$$F_{MAX} = V_{OUT} / (V_{INMAX} \times 250 \text{ ns})$$

(6)

For this exercise,  $F_{MAX}$  = 444 kHz. From  $\gtrsim 2$ ,  $R_{ON}$  calculates to 180 kΩ. A standard-value, 237-kΩ resistor is used to allow for tolerances in  $\gtrsim 2$ , resulting in a nominal frequency of 337 kHz.

#### 8.2.2.3 Inductor Selection

**L1:** The main parameter affected by the inductor is the output current ripple amplitude. The choice of inductor value therefore depends on both the minimum and maximum load currents, keeping in mind that the maximum ripple current occurs at maximum  $V_{IN}$ .

Minimum load current: To maintain continuous conduction at minimum I<sub>O</sub> (100 mA), the ripple amplitude (I<sub>OR</sub>) must be less than 200 mA peak-to-peak so the lower peak of the waveform does not reach zero. L1 is calculated using 式 7:

$$L1 = \frac{V_{OUT1} \times (V_{IN} - V_{OUT1})}{I_{OR} \times F_s \times V_{IN}}$$

(7)

At  $V_{IN}$  = 90 V, L1 (min) calculates to 132  $\mu$ H. The next larger standard value (150  $\mu$ H) is chosen and, with this value,  $I_{OR}$  calculates to 176 mA peak-to-peak at  $V_{IN}$  = 90 V and 33 mA peak-to-peak at  $V_{IN}$  = 12 V.

2. **Maximum load current:** At a load current of 150 mA, the peak of the ripple waveform must not reach the minimum value of the LM5009 current limit threshold (250 mA). Therefore, the ripple amplitude must be less than 200 mA peak-to-peak, which is already satisfied in 式 7. With L1 = 150 μH, at maximum V<sub>IN</sub> and I<sub>O</sub>, the peak of the ripple is 238 mA. Although L1 must carry this peak current without saturating or exceeding its temperature rating, L1 must also be capable of carrying the maximum value of the LM5009 current limit threshold (370 mA) without saturating because the current limit is reached during startup.

#### 8.2.2.4 VCC and Bootstrap Capacitor

C3: The capacitor on the  $V_{CC}$  output provides not only noise filtering and stability, but also prevents false triggering of the  $V_{CC}$  UVLO at the buck switch on and off transitions. For this reason, C3 must be no smaller than 0.1  $\mu$ F.

**C4:** The recommended value is 0.022  $\mu$ F for C4 because this value is appropriate in the majority of applications. A high-quality ceramic capacitor, with low ESR is recommended because C4 supplies the surge current to charge the buck switch gate at turn-on. A low ESR also ensures a quick recharge during each off-time. At minimum VIN when the on-time is at maximum, C4 can possibly not fully recharge at start-up during each 300-ns off-time. This failure to recharge results from the circuit being unable to complete the start-up and achieve output regulation. This condition can occur when the frequency is intended to be low (for example,  $R_{ON} = 500 \text{ k}\Omega$ ). In this case, increase C4 to maintain sufficient voltage across the buck switch driver during each on-time.

### 8.2.2.5 Output Capacitor Selection

**C2 and R3:** When selecting the output filter capacitor C2, the items to consider are ripple voltage resulting from the C2 ESR, ripple voltage resulting from the C2 capacitance, and the nature of the load.

- 1. **ESR and R3:** A low ESR for C2 is generally desirable to minimize power losses and heating within the capacitor. However, this regulator requires a minimum amount of ripple voltage at the feedback input for proper loop operation. For the LM5009, the minimum ripple required at pin 5 is 25 mV peak-to-peak, requiring a minimum ripple at  $V_{OUT1}$  of 100 mV. The minimum ESR required at  $V_{OUT1}$  is 3  $\Omega$  because the minimum ripple current (at minimum  $V_{IN}$ ) is 33 mA peak-to-peak. R3 is inserted as illustrated in the  $V_{OUT1}$  7.2 section because quality capacitors for SMPS applications have considerably less ESR. The value of R3, along with the ESR of C2, must result in at least a 25-mV peak-to-peak ripple at pin 5. Generally, R3 is 0.5  $\Omega$  to 5.0  $\Omega$ .

- 2. **Nature of the load:** The load can be connected to  $V_{OUT1}$  or  $V_{OUT2}$ .  $V_{OUT1}$  provides good regulation, but with a ripple voltage that ranges from 100 mV (at  $V_{IN}$  = 12 V) to 580 mV (at  $V_{IN}$  = 90 V). Alternatively,  $V_{OUT2}$  provides low ripple (3 mV to 13 mV) but lower regulation resulting from R3.

- C2 generally must be no smaller than 3.3  $\mu$ F. Typically, the value of C2 is 10  $\mu$ F to 20  $\mu$ F, with the optimum value determined by the load. If the load current is fairly constant, a small value suffices for C2. If the load current includes significant transients, a larger value is necessary. For each application, experimentation is needed to determine the optimum values for R3 and C2.

- 3. **Ripple reduction:** The ripple amplitude at  $V_{OUT1}$  can be reduced by reducing R3 and by adding a capacitor across R1 to transfer the ripple at  $V_{OUT1}$  directly to the FB pin without attenuation. The new value of R3 is calculated by  $\stackrel{\star}{\to}$  8:

$$R3 = 25 \text{ mV} / I_{OR(min)}$$

(8)

where

I<sub>OR(min)</sub> is the minimum ripple current amplitude—33 mAp-p in this example

The added capacitor value is calculated by  $\pm 9$ :

$$C = T_{ON(max)} / (R1 // R2)$$

(9)

where

•  $T_{ON(max)}$  is the maximum on-time (at minimum  $V_{IN}$ )

The selected capacitor must be larger than the value calculated in  $\pm 9$ .

#### 8.2.2.6 Current Limit Off-Timer Setting

**R<sub>CL</sub>:** When a current limit condition is detected, the minimum off-time set by this resistor must be greater than the maximum normal off-time that occurs at maximum  $V_{IN}$ . Using  $\pm$  4, the minimum on-time is 0.329  $\mu$ s, yielding a maximum off-time of 2.63  $\mu$ s. This value is further increased by 82 ns (to 2.72  $\mu$ s), resulting from a ±25% tolerance of the on-time. This value is then increased to allow for the response time of the current limit detection loop (400 ns).

The off-time determined by  $\pm 5$  has a  $\pm 25\%$  tolerance, as given by  $\pm 10$ :

$$t_{OFFCL(MIN)} = (2.72 \,\mu\text{s} \times 1.25) + 0.4 \,\mu\text{s} = 3.8 \,\mu\text{s}$$

(10)

Using  $\pm$  5, R<sub>CL</sub> calculates to 167 kΩ (at V<sub>FB</sub> = 2.5 V). The closest standard value is 169 kΩ.

#### 8.2.2.7 Rectifier Diode Selection

**D1:** The important parameters are reverse recovery time and forward voltage. Reverse recovery time determines how long the reverse current surge lasts each time that the buck switch is turned on. The forward voltage drop is significant in the event that the output is short-circuited because only this diode voltage forces the inductor current to reduce during the forced off-time. For this reason, a higher voltage is better, although higher voltages affect efficiency. A good choice is an ultrafast or Schottky diode with a reverse recovery time of approximately 30 ns and a forward voltage drop of approximately 0.7 V. Other types of diodes can have a lower forward voltage drop, but can also have longer recovery times or greater reverse leakage. The D1 reverse voltage rating must be at least as great as the maximum  $V_{IN}$ , and the D1 current rating must be greater than the maximum current limit threshold (370 mA).

### 8.2.2.8 Input Capacitor Selection

C1: The purpose of this capacitor is to supply most of the switch current during the on-time and to limit the voltage ripple at VIN, on the assumption that the voltage source feeding VIN has an output impedance greater than zero. At maximum load current, when the buck switch turns on, the current into pin 8 suddenly increases to the lower peak of the output current waveform, ramps up to the peak value, and then drops to zero at turn-off. The average input current during this on-time is the load current (150 mA). For a worst-case calculation, C1 must supply this average load current during the maximum on-time. To keep the input voltage ripple to less than 2 V (for this exercise), C1 calculates to 3 11:

$$C1 = \frac{I \times t_{ON}}{\Delta V} = \frac{0.15A \times 2.47 \ \mu s}{2.0V} = 0.185 \ \mu F \tag{11}$$

Quality ceramic capacitors in this value have a low ESR that adds only a few millivolts to the ripple. The capacitance is dominant in this case. To allow for the capacitor tolerance, temperature effects, and voltage effects, a  $1.0-\mu F$ , 100-V, X7R capacitor is used.

**C5:** This capacitor helps avoid supply voltage transients and ringing resulting from long lead inductance at VIN. A low-ESR, 0.1-μF ceramic chip capacitor is recommended, located close to the LM5009.

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

### 8.2.2.9 Ripple Configuration

The LM5009 uses a constant-on-time (COT) control scheme where the on-time is terminated by a one-shot and the off-time is terminated by the feedback voltage ( $V_{FB}$ ) falling below the reference voltage. Therefore, for stable operation, the feedback voltage must decrease monotonically in phase with the inductor current during the off-time. Furthermore, this change in feedback voltage ( $V_{FB}$ ) during off-time must be large enough to dominate any noise present at the feedback node.

表 8-2 presents three different methods for generating appropriate voltage ripple at the feedback node. Type 1 and type 2 ripple circuits couple the ripple from the output of the converter to the feedback node (FB). The output voltage ripple has two components:

- 1. Capacitive ripple caused by the inductor current ripple charging or discharging the output capacitor.

- 2. Resistive ripple caused by the inductor current ripple flowing through the ESR of the output capacitor and R3.

表 8-2. Ripple Configuration TYPE 1 TYPE 2 TYPE 3 Lowest cost Reduced ripple Minimum ripple  $V_{OLIT}$  $V_{OUT}$ m Ø **GND**  $C_{ff} \ge \frac{1}{F_{SW} \times (R_{FB2} IIR_{FB1})}$  $R_3 \geq \frac{25 \text{ mV} \times V_O}{V_{REF} \times \Delta I_{L1, \, min}}$  $R_A C_A \ge \frac{(V_{IN, min} - V_O) \times T_{ON(@V_{IN, min})}}{25mV}$ (14)(12)(13)

The capacitive ripple is out of phase with the inductor current. As a result, the capacitive ripple does not decrease monotonically during the off-time. The resistive ripple is in phase with the inductor current and decreases monotonically during the off-time. The resistive ripple must exceed the capacitive ripple at output  $(V_{OUT})$  for stable operation. If this condition is not satisfied, then unstable switching behavior is observed in COT converters with multiple on-time bursts in close succession followed by a long off-time.

The type 3 ripple method uses a ripple injection circuit with  $R_A$ ,  $C_A$ , and the switch node (SW) voltage to generate a triangular ramp. This triangular ramp is then ac-coupled into the feedback node (FB) using the capacitor  $C_B$ . This circuit is suited for applications where low output voltage ripple is imperative because this circuit does not use the output voltage ripple. See application note *AN-1481 Controlling Output Ripple and Achieving ESR Independence in Constant On-Time (COT) Regulator Designs*, SNVA166 for more details on each ripple generation method.

### 8.2.3 Application Curves

### 8.3 Do's and Don'ts

A minimum load current of 1 mA is required to maintain proper operation. If the load current falls below that level, the bootstrap capacitor can discharge during the long off-time and the circuit either shuts down or cycles on and off at a low frequency. If the load current is expected to drop below 1 mA in the application, choose the feedback resistors to be low enough in value to provide the minimum required current at nominal  $V_{OUT}$ .

# 9 Power Supply Recommendations

The LM5009 is designed to operate with an input power supply capable of supplying a voltage range between 9 V and 95 V. The input power supply must be well-regulated and capable of supplying sufficient current to the regulator during peak load operation. Also, like in all applications, the power-supply source impedance must be small compared to the module input impedance to maintain the stability of the converter.

# 10 Layout

# 10.1 Layout Guidelines

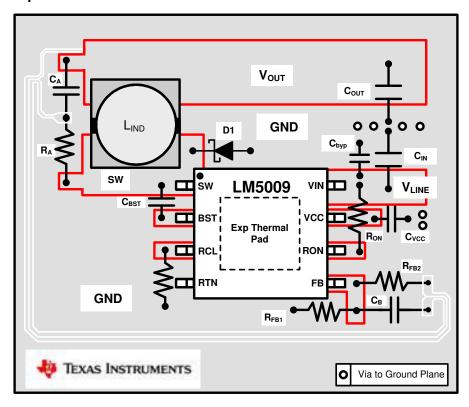

The LM5009 regulation and overvoltage comparators are very fast, and as such respond to short-duration noise pulses. Layout considerations are therefore critical for optimum performance. The components at pins 1, 2, 3, 5, and 6 must be as physically close as possible to the device, thereby minimizing noise pickup in the PC tracks. The two major current loops conduct currents that switch very fast and, therefore, those loops must be as small as possible to minimize conducted and radiated electromagnetic interference (EMI). The first loop is formed by  $C_{IN}$ , through the VIN to SW pins,  $L_{IND}$ ,  $C_{OUT}$ , and back to  $C_{IN}$ . The second current loop is formed by D1,  $L_{IND}$ , and  $C_{OUT}$ .

If the internal dissipation of the LM5009 produces excessive junction temperatures during normal operation, good use of the PC board ground plane can help considerably to dissipate heat. The exposed pad on the bottom of the WSON-8 package can be soldered to a ground plane on the PC board, and that plane must extend out from beneath the device to help dissipate heat. Additionally, the use of wide PC board traces, where possible, can also help conduct heat away from the device. Judicious positioning of the PC board within the end product, along with the use of any available air flow (forced or natural convection) can help reduce the junction temperatures.

### 10.2 Layout Example

図 10-1. LM5009 Buck Layout Example with the WSON Package

# 11 Device and Documentation Support

# 11.1 Documentation Support

#### 11.1.1 Related Documentation

Application note AN-1481 Controlling Output Ripple and Achieving ESR Independence in Constant On-Time (COT) Regulator Designs, SNVA166

# 11.2 Receiving Notification of Documentation Updates

To receive notification of documentation updates, navigate to the device product folder on ti.com. Click on *Subscribe to updates* to register and receive a weekly digest of any product information that has changed. For change details, review the revision history included in any revised document.

## 11.3 サポート・リソース

TI E2E<sup>™</sup> サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、該当する貢献者により、現状のまま提供されるものです。これらは TI の仕様を構成するものではなく、必ずしも TI の見解を反映したものではありません。TI の使用条件を参照してください。

### 11.4 Trademarks

TI E2E™ is a trademark of Texas Instruments.

is a registered trademark of TI.

すべての商標は、それぞれの所有者に帰属します。

### 11.5 Electrostatic Discharge Caution

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

### 11.6 Glossary

TI Glossary

This glossary lists and explains terms, acronyms, and definitions.

# 12 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

www.ti.com 13-Sep-2024

### PACKAGING INFORMATION

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp      | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|--------|--------------|--------------------|------|----------------|--------------|-------------------------------|--------------------|--------------|-------------------------|---------|

|                  |        |              |                    |      |                |              | (6)                           |                    |              |                         |         |

| LM5009MM/NOPB    | ACTIVE | VSSOP        | DGK                | 8    | 1000           | RoHS & Green | SN                            | Level-1-260C-UNLIM | -40 to 125   | SLLB                    | Samples |

| LM5009MMX/NOPB   | ACTIVE | VSSOP        | DGK                | 8    | 3500           | RoHS & Green | SN                            | Level-1-260C-UNLIM | -40 to 125   | SLLB                    | Samples |

| LM5009SDC/NOPB   | ACTIVE | WSON         | NGU                | 8    | 1000           | RoHS & Green | SN                            | Level-1-260C-UNLIM | -40 to 125   | 5009SD                  | Samples |

| LM5009SDCX/NOPB  | ACTIVE | WSON         | NGU                | 8    | 4500           | RoHS & Green | SN                            | Level-1-260C-UNLIM | -40 to 125   | 5009SD                  | Samples |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

**Green:** TI defines "Green" to mean the content of Chlorine (Cl) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and

# PACKAGE OPTION ADDENDUM

www.ti.com 13-Sep-2024

continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 25-Sep-2024

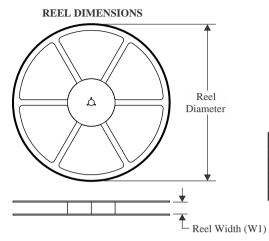

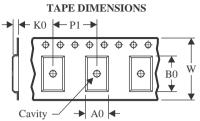

# TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

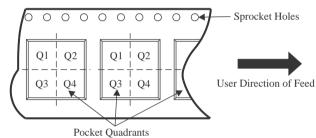

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device          | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-----------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| LM5009MM/NOPB   | VSSOP           | DGK                | 8 | 1000 | 178.0                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

| LM5009MMX/NOPB  | VSSOP           | DGK                | 8 | 3500 | 330.0                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

| LM5009SDC/NOPB  | WSON            | NGU                | 8 | 1000 | 178.0                    | 12.4                     | 4.3        | 4.3        | 1.3        | 8.0        | 12.0      | Q1               |

| LM5009SDCX/NOPB | WSON            | NGU                | 8 | 4500 | 330.0                    | 12.4                     | 4.3        | 4.3        | 1.3        | 8.0        | 12.0      | Q1               |

www.ti.com 25-Sep-2024

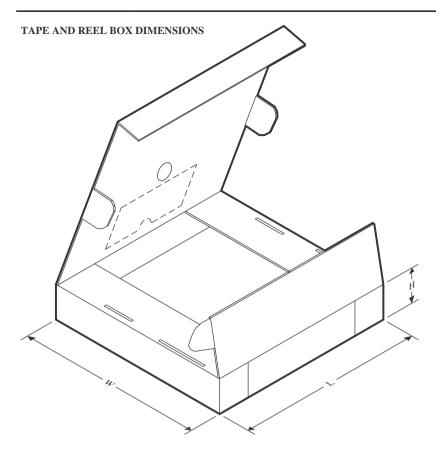

## \*All dimensions are nominal

| Device          | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-----------------|--------------|-----------------|------|------|-------------|------------|-------------|

| LM5009MM/NOPB   | VSSOP        | DGK             | 8    | 1000 | 208.0       | 191.0      | 35.0        |

| LM5009MMX/NOPB  | VSSOP        | DGK             | 8    | 3500 | 367.0       | 367.0      | 35.0        |

| LM5009SDC/NOPB  | WSON         | NGU             | 8    | 1000 | 208.0       | 191.0      | 35.0        |

| LM5009SDCX/NOPB | WSON         | NGU             | 8    | 4500 | 367.0       | 367.0      | 35.0        |

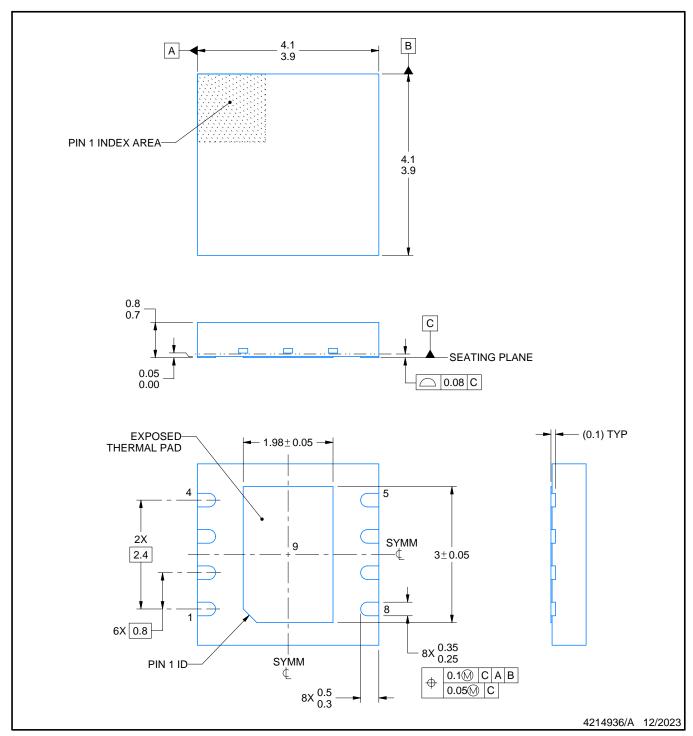

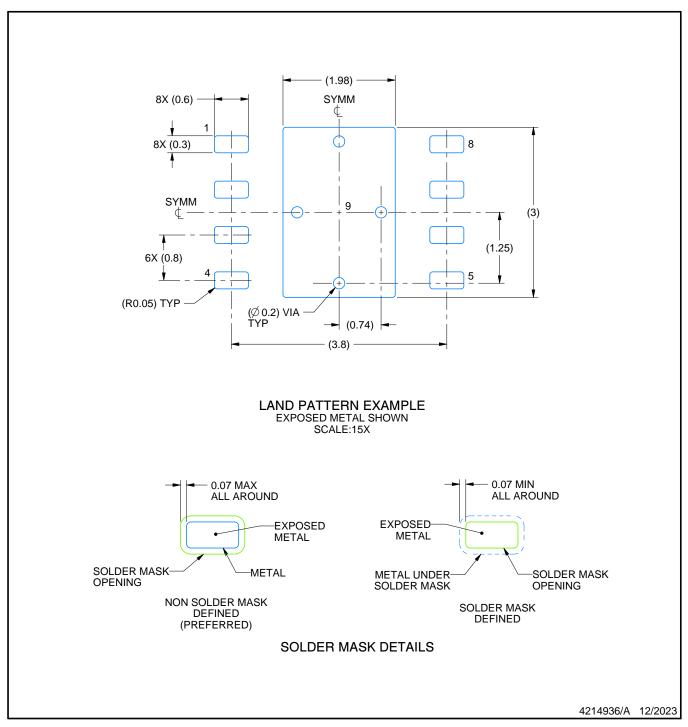

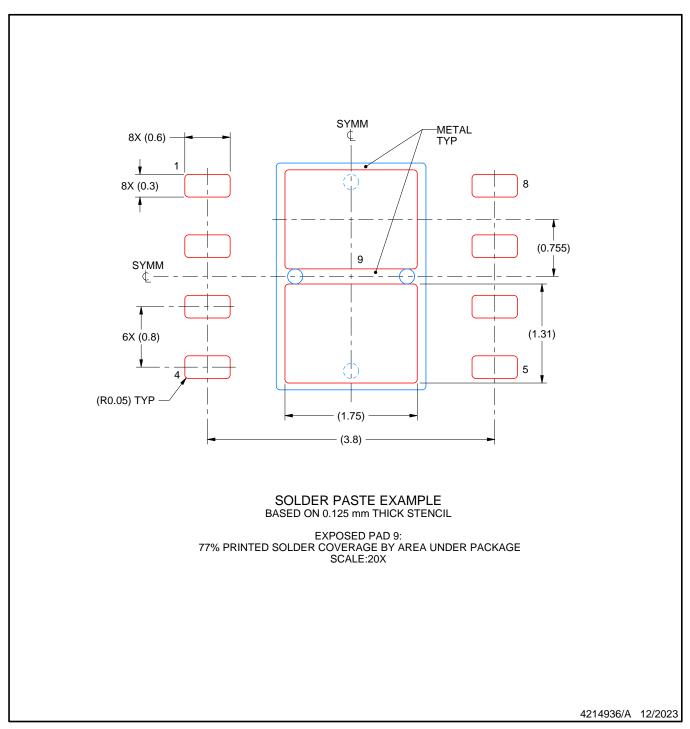

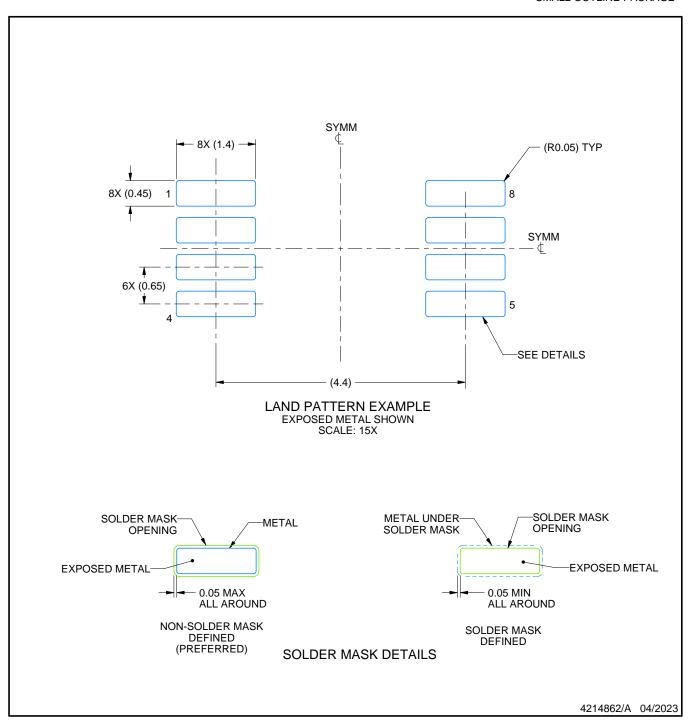

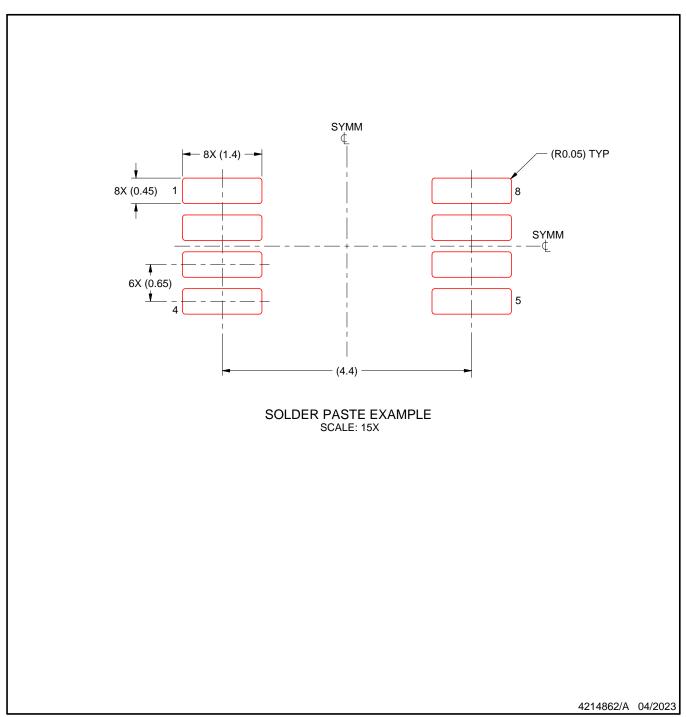

PLASTIC SMALL OUTLINE - NO LEAD

### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

- 3. The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

PLASTIC SMALL OUTLINE - NO LEAD

NOTES: (continued)

- 4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

- 5. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

PLASTIC SMALL OUTLINE - NO LEAD

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

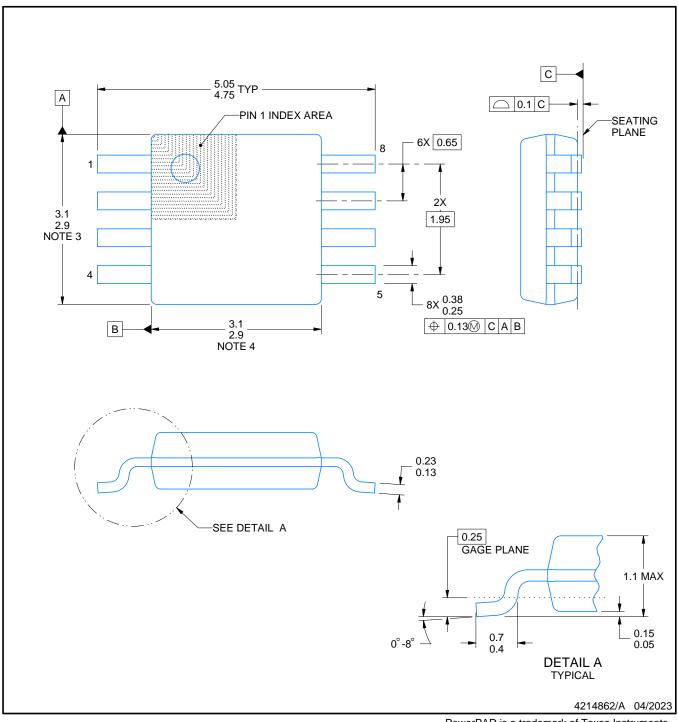

SMALL OUTLINE PACKAGE

### NOTES:

PowerPAD is a trademark of Texas Instruments.

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm per side.

- 4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side.

- 5. Reference JEDEC registration MO-187.

SMALL OUTLINE PACKAGE

NOTES: (continued)

- 6. Publication IPC-7351 may have alternate designs.

- 7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

- 8. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

- 9. Size of metal pad may vary due to creepage requirement.

SMALL OUTLINE PACKAGE

NOTES: (continued)

- 11. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 12. Board assembly site may have different recommendations for stencil design.

# 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス・デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあら ゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TIの製品は、TIの販売条件、または ti.com やかかる TI 製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、TIはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2024, Texas Instruments Incorporated