LM7480

JAJSLG4 - DECEMBER 2022

# LM7480 3V~65V、バック・ツー・バック NFET 駆動、理想ダイオード・コン トローラ

# 1 特長

- 拡張温度アプリケーション向けに認定済み

- デバイス温度:

- -55°C~+125°Cの動作時周用温度範囲

- 3V~65V の入力範囲

- 最低 -65V までの逆入力保護

- 共通ドレインと共通ソースの構成で外付けのバック・ツ ー・バック N チャネル MOSFET を駆動

- アノードからカソードへ 10.5mV の順方向電圧降下レ ギュレーションを行う理想ダイオード動作 (LM74800)

- 低いスレッショルド (-4.5mV) と高速応答 (0.5µs) の逆 電流検出

- 20mA のピーク・ゲート (DGATE) ターンオン電流

- 2.6A のピーク DGATE ターンオフ電流

- 調整可能な過電圧保護機能

- 低シャットダウン電流 (EN/UVLO = Low):2.87µA

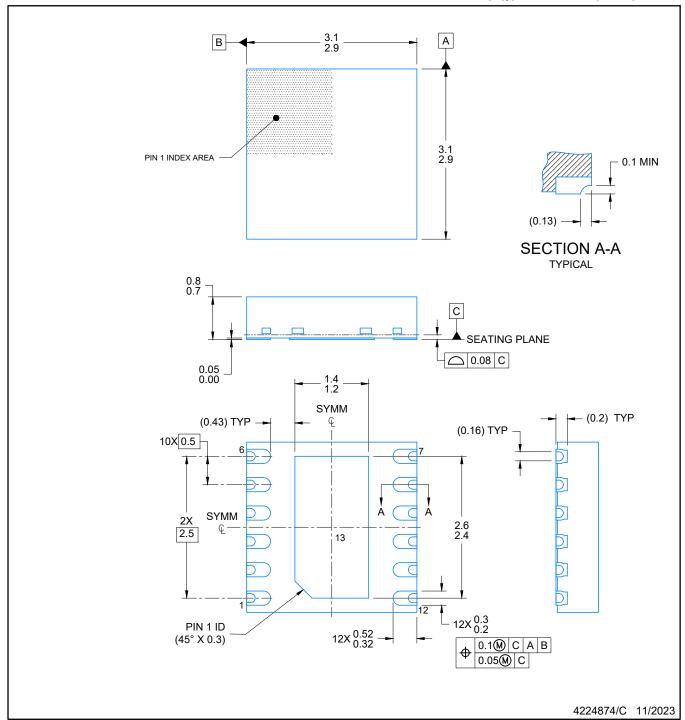

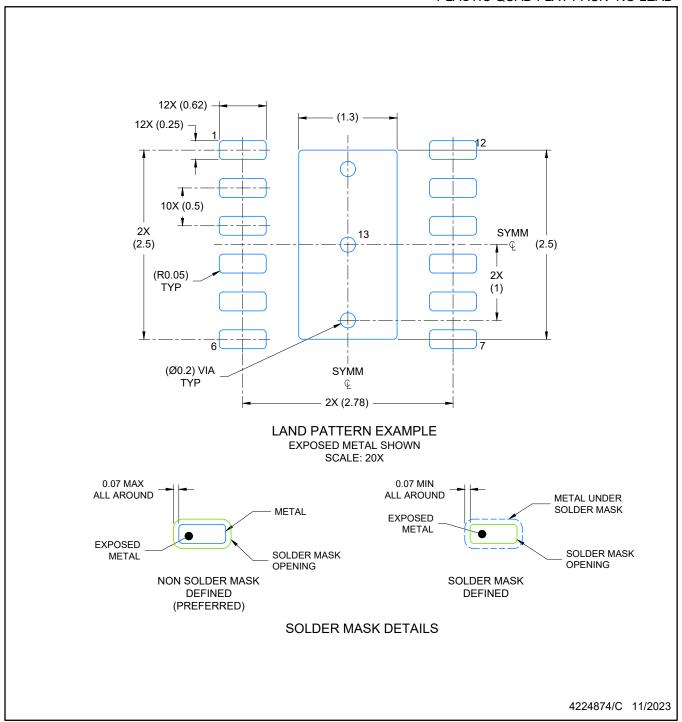

- 省スペースの 12 ピン WSON パッケージで供給

# 2 アプリケーション

- アビオニクス入力の逆極性保護

- センサ

- 画像処理

- レーダー

- 冗長化電源用のアクティブ OR

#### VOUT2 (Always ON) VOUT1 (VBATT Switched) DGATE CAP VS C HGATE OUT /SNS SW LM7480x BATT MON EN/UVLO - ONOFF GNE

スイッチ出力を備えた理想ダイオード

## 3 概要

LM7480 理想ダイオード・コントローラは外付けのバック・ ツー・バック N チャネル MOSFET を駆動および制御し て、電力パスの ON/OFF 制御と過電圧保護を備えた理想 ダイオード整流器をエミュレートします。入力電源電圧範 囲が 3V~65V と広いため、12V および 24V 入力電源シ ステムを保護および制御できます。このデバイスは最低 -65V の負の電源電圧に耐え、この電圧から負荷を保護で きます。内蔵の理想ダイオード・コントローラ (DGATE) は 第1の MOSFET を駆動し、逆電流保護および出力電圧 保持用のショットキー・ダイオードを置き換えます。電力パ スの第2の MOSFET により、HGATE 制御を使用した負 荷の切断 (ON/OFF 制御) と過電圧保護が可能です。こ のデバイスには可変の過電圧カットオフ保護機能がありま す。LM7480 には、LM74800 とLM74801 の 2 つのバリ エーションがあります。LM74800 は、リニア・レギュレーシ ョンおよびコンパレータ方式を使用した逆電流ブロックを 採用しています。一方、LM74801 はコンパレータに基づ く方式をサポートしています。共通ドレイン構成のパワー MOSFET の場合、もう 1 つの理想ダイオードを使用した OR 接続設計のために中間点を利用できます。LM7480 は 65V の最大電圧定格を持っています。本デバイスと外 付け MOSFET を共通ソース・トポロジに構成することで、 24V バッテリ・システムの 200V 非抑制負荷ダンプのよう な大きな過電圧過渡からも負荷を保護できます。

## パッケージ情報

|         | / Y / / / IFITA      |                        |

|---------|----------------------|------------------------|

| 部品番号    | パッケージ <sup>(1)</sup> | 本体サイズ (公称)             |

| LM74800 | WSON (12)            | 3.00mm × 3.00mm        |

| LM74801 | VV30IV (12)          | 3.0011111 ~ 3.00111111 |

利用可能なパッケージについては、このデータシートの末尾にあ る注文情報を参照してください。

200V 負荷ダンプ保護機能を備えた理想ダイオード

# **Table of Contents**

| 1 特長                                 | 1    | 9.4 Device Functional Modes                  | 16               |

|--------------------------------------|------|----------------------------------------------|------------------|

| 2 アプリケーション                           |      | 9.5 Application Examples                     | 16               |

| 3 概要                                 |      | 10 Applications and Implementation           | 18               |

| 4 Revision History                   |      | 10.1 Application Information                 | 18               |

| 5 Device Comparison Table            |      | 10.2 Typical 12-V Reverse Battery Protection |                  |

| 6 Pin Configuration and Functions    |      | Application                                  | 18               |

| 7 Specifications                     |      | 10.3 200-V Unsuppressed Load Dump Protection |                  |

| 7.1 Absolute Maximum Ratings         |      | Application                                  | 26               |

| 7.2 ESD Ratings                      |      | 10.4 Do's and Don'ts                         | 29               |

| 7.3 Recommended Operating Conditions |      | 10.5 Power Supply Recommendations            | 29               |

| 7.4 Thermal Information              |      | 10.6 Layout                                  | <mark>3</mark> 1 |

| 7.5 Electrical Characteristics       |      | 11 Device and Documentation Support          | 33               |

| 7.6 Switching Characteristics        |      | 11.1ドキュメントの更新通知を受け取る方法                       | 33               |

| 7.7 Typical Characteristics          |      | 11.2 サポート・リソース                               | 33               |

| 8 Parameter Measurement Information  |      | 11.3 Trademarks                              | 33               |

| 9 Detailed Description               | . 11 | 11.4 静電気放電に関する注意事項                           | 33               |

| 9.1 Overview                         |      | 11.5 用語集                                     | 33               |

| 9.2 Functional Block Diagram         | .12  | 12 Mechanical, Packaging, and Orderable      |                  |

| 9.3 Feature Description              |      | Information                                  | 33               |

| •                                    |      |                                              |                  |

# **4 Revision History**

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| DATE          | REVISION | NOTES           |

|---------------|----------|-----------------|

| December 2022 | *        | Initial Release |

# **5 Device Comparison Table**

|                          | LM74800                                      | LM74801                            |

|--------------------------|----------------------------------------------|------------------------------------|

| Reverse Current Blocking | $V_{(A-C)}$ linear regulation and comparator | V <sub>(A-C)</sub> comparator only |

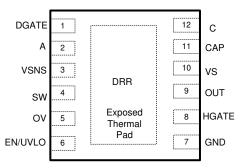

# **6 Pin Configuration and Functions**

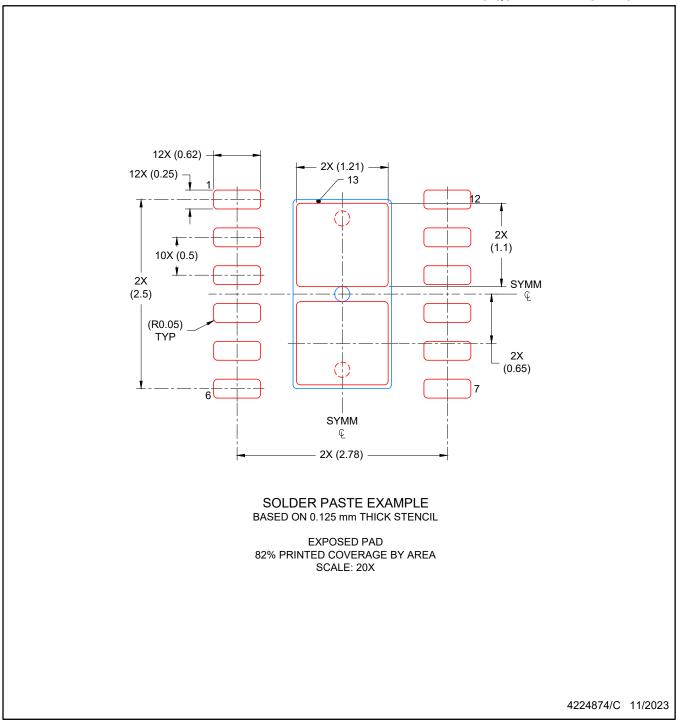

図 6-1. DRR Package, 12-Pin WSON (Top View)

表 6-1. Pin Functions

|         | PIN           |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|---------|---------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME    | LM7480        | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| NAME    | DRR-12 (WSON) |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| DGATE   | 1             | 0    | Diode Controller Gate Drive Output. Connect to the GATE of the external MOSFET.                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| Α       | 2             | I    | Anode of the ideal diode. Connect to the source of the external MOSFET.                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| VSNS    | 3             | Į.   | Voltage sensing input.                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| SW      | 4             | ı    | Voltage sensing disconnect switch terminal. VSNS and SW are internally connected through a switch. Use SW as the top connection of the battery sensing or OV resistor ladder network. When EN/UVLO is pulled low, the switch is OFF disconnecting the resistor ladder from the battery line thereby cutting off the leakage current. If the internal disconnect switch between VSNS and SW is not used then short them together and connect to VS pin. |  |  |

| ov      | 5             | I    | Adjustable overvoltage threshold input. Connect a resistor ladder across SW to OV terminal. When the voltage at OVP exceeds the overvoltage cut-off threshold then the HGATE is pulled low turning OFF the HSFET. HGATE turns ON when the sense voltage goes below the OVP falling threshold.                                                                                                                                                          |  |  |

| EN/UVLO | 6             | I    | EN/UVLO Input. Connect to VS pin for always ON operation. Can be driven externally from a micro controller I/O. Pulling it low below $V_{(ENF)}$ makes the device enter into low Iq shutdown mode. For UVLO, connect an external resistor ladder to EN/UVLO to GND.                                                                                                                                                                                    |  |  |

| GND     | 7             | G    | Connect to the system ground plane.                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| HGATE   | 8             | 0    | GATE driver output for the HSFET. Connect to the GATE of the external FET.                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| OUT     | 9             | I    | Connect to the output rail (external MOSFET source).                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| VS      | 10            | I    | Input power supply to the IC. Connect VS to middle point of the common drain back to back MOSFET configuration. Connect a 100-nF capacitor across VS and GND pins.                                                                                                                                                                                                                                                                                     |  |  |

| CAP     | 11            | 0    | Charge pump output. Connect a 100-nF capacitor across CAP and VS pins.                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| С       | 12            | I    | Cathode of the ideal diode. Connect to the drain of the external MOSFET.                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| RTN     | Thermal Pad   | _    | Leave exposed pad floating. Do Not connect to GND plane.                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

# 7 Specifications

# 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                                       |                                                                 | MIN              | MAX              | UNIT |  |

|---------------------------------------|-----------------------------------------------------------------|------------------|------------------|------|--|

|                                       | A to GND                                                        | -65              | 70               |      |  |

|                                       | VS to GND                                                       | -1               | 70               |      |  |

|                                       | VSNS, SW, EN/UVLO, C, OV, OUT to GND, V(A) > 0 V                | -0.3             | 70               | V    |  |

| Innut Dina                            | VSNS, SW, EN/UVLO, C, OV, OUT to GND, $V_{(A)} \le 0 \text{ V}$ | V <sub>(A)</sub> | $(70 + V_{(A)})$ |      |  |

| Input Pins                            | RTN to GND                                                      | -65              | 0.3              |      |  |

|                                       | I <sub>VSNS</sub> , I <sub>SW</sub>                             | -1               | 10               | mA   |  |

|                                       | I <sub>EN/UVLO</sub> , I <sub>OV,</sub> V <sub>(A)</sub> > 0 V  | -1               |                  | mA   |  |

|                                       | $I_{EN/UVLO}$ , $I_{OV}$ , $V_{(A)} \le 0 \text{ V}$            | Internally       | imited           |      |  |

| Output Pins                           | OUT to VS                                                       | -65              | 16.5             | V    |  |

|                                       | CAP to VS                                                       | -0.3             | 15               |      |  |

| Output Pins                           | CAP to A                                                        | -0.3             | 85               |      |  |

| Output Pilis                          | DGATE to A                                                      | -0.3             | 15               | V    |  |

|                                       | HGATE to OUT                                                    | -0.3             | 15               |      |  |

| Output to Input Pins                  | C to A                                                          | -5               | 85               |      |  |

| Operating junction tempera            | erating junction temperature, T <sub>j</sub> <sup>(2)</sup>     |                  | 150              | °C   |  |

| Storage temperature, T <sub>stg</sub> |                                                                 | -55              | 150              |      |  |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Rating may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Condition. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### 7.2 ESD Ratings

|                    |                         |                                  |                                | VALUE | UNIT |

|--------------------|-------------------------|----------------------------------|--------------------------------|-------|------|

|                    |                         | Human body model (HBM), per JEDI | EC JS-001 <sup>(1)</sup>       | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), V    | Corner pins (DGATE, OV, and C) | ±750  | V    |

|                    | JEDEO 10 000(2)         |                                  | Other pins                     | ±500  |      |

<sup>1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

# 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)(1)

|                                |                                               | MIN | NOM MAX | UNIT |

|--------------------------------|-----------------------------------------------|-----|---------|------|

|                                | A to GND                                      | -60 | 65      | V    |

| Input Pins                     | VS to GND                                     | 0   | 65      | V    |

|                                | EN/UVLO to GND                                | 0   | 65      | V    |

| External Capacitance           | CAP to A, VS to GND, A to GND                 | 0.1 |         | μF   |

| External MOSFET max VGS rating | DGATE to A and HGATE to OUT                   | 15  |         | V    |

| Tj                             | Operating Junction temperature <sup>(2)</sup> | -55 | 150     | °C   |

Recommended Operating Conditions are conditions under which the device is intended to be functional. For specifications and test conditions, see Electrical Characteristics.

<sup>(2)</sup> High junction temperatures degrade operating lifetimes. Operating lifetime is de-rated for junction temperatures greater than 125°C.

<sup>(2)</sup> JEDEC document JEP155 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

<sup>(2)</sup> High junction temperatures degrade operating lifetimes. Operating lifetime is de-rated for junction temperatures greater than 125°C.

# 7.4 Thermal Information

|                       |                                              | LM7480x    |      |

|-----------------------|----------------------------------------------|------------|------|

|                       | THERMAL METRIC(1)                            | DRR (WSON) | UNIT |

|                       |                                              | 12 PINS    |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 60.9       | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 48         | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 31.5       | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 1.2        | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 31.4       | °C/W |

| R <sub>θJC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 7.1        | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

# 7.5 Electrical Characteristics

$T_J$  = -55°C to +125°C; typical values at  $T_J$  = 25°C,  $V_{(A)}$  =  $V_{(OUT)}$  =  $V_{(VS)}$  =  $V_{(VSNS)}$  = 12 V,  $V_{(AC)}$  = 20 mV,  $V_{(VCAP)}$  = 0.1  $\mu$ F,  $V_{(EN/UVLO)}$  = 2 V, over operating free-air temperature range (unless otherwise noted)

|                        | PARAMETER                                                     | TEST CONDITIONS                                                               | MIN   | TYP   | MAX   | UNIT |

|------------------------|---------------------------------------------------------------|-------------------------------------------------------------------------------|-------|-------|-------|------|

| SUPPLY VOLTA           | AGE                                                           |                                                                               |       |       | '     |      |

| V <sub>(VS)</sub>      | Operating input voltage                                       |                                                                               | 3     |       | 65    | V    |

| V <sub>(VS_PORR)</sub> | VS POR threshold, rising                                      |                                                                               | 2.4   | 2.6   | 2.85  | V    |

| V <sub>(VS_PORF)</sub> | VS POR threshold, falling                                     |                                                                               | 1.9   | 2.1   | 2.3   | V    |

| I <sub>(SHDN)</sub>    | SHDN current, I <sub>(GND)</sub>                              | V <sub>(EN/UVLO)</sub> = 0 V                                                  |       | 2.87  | 5     | μA   |

| 1                      | Total System Outcosent surrent I                              | V <sub>(EN/UVLO)</sub> = 2 V                                                  |       | 397   |       | μA   |

| $I_{(Q)}$              | Total System Quiescent current, I <sub>(GND)</sub>            | V <sub>(A)</sub> = V <sub>(VS)</sub> = 24 V, V <sub>(EN/UVLO)</sub> = 2 V     |       | 413   | 530   | μA   |

| 1                      | I <sub>(A)</sub> leakage current during Reverse Polarity,     | 0.V.c.V. c. 65.V.                                                             |       | 10    | 112   | μΑ   |

|                        | I <sub>(OUT)</sub> leakage current during Reverse<br>Polarity | $-0 \text{ V} \leq \text{V}_{(A)} \leq -65 \text{ V}$                         |       |       | 1     | μA   |

| ENABLE AND             | UNDERVOLTAGE LOCKOUT (EN/UVLO) I                              | NPUT                                                                          |       |       | '     |      |

| V <sub>(UVLOR)</sub>   | EN/UVLO threshold voltage, rising                             |                                                                               | 1.195 | 1.231 | 1.267 | V    |

| V <sub>(UVLOF)</sub>   | EN/UVLO threshold voltage, falling                            |                                                                               | 1.091 | 1.132 | 1.159 | V    |

| V <sub>(ENF)</sub>     | Enable threshold voltage for low Iq shutdown, falling         |                                                                               | 0.3   | 0.67  | 0.93  | V    |

| V <sub>(EN_Hys)</sub>  | Enable Hysteresis                                             |                                                                               | 37    | 72    | 95    | mV   |

| I <sub>(EN/UVLO)</sub> |                                                               | 0 V ≤ V <sub>(EN/UVLO)</sub> ≤ 65 V                                           |       | 55    | 200   | nA   |

| OVERVOLTAG             | E PROTECTION AND BATTERY SENSING                              | (VSNS, SW, OV) INPUT                                                          |       |       |       |      |

| R <sub>(SW)</sub>      | Battery sensing disconnect switch resistance                  | 3 V ≤ V <sub>(SNS)</sub> ≤ 65 V                                               | 10    | 19.5  | 46    | Ω    |

| V <sub>(OVR)</sub>     | Overvoltage threshold input, rising                           |                                                                               | 1.195 | 1.231 | 1.267 | V    |

| V <sub>(OVF)</sub>     | Overvoltage threshold input, falling                          |                                                                               | 1.091 | 1.13  | 1.159 | V    |

| I <sub>(OV)</sub>      | OV Input leakage current                                      | 0 V ≤ V <sub>(OV)</sub> ≤ 65 V                                                |       | 53    | 200   | nA   |

| CHARGE PUM             | P (CAP)                                                       |                                                                               |       |       | '     |      |

| I <sub>(CAP)</sub>     | Charge Pump source current (Charge pump on)                   | $V_{(CAP)} - V_{(A)} = 7 \text{ V}, 6 \text{ V} \le V_{(S)} \le 65 \text{ V}$ | 1.3   | 2.7   |       | mA   |

| VCAP – VS              | Charge Pump Turn ON voltage                                   |                                                                               | 11    | 12.2  | 13.2  | V    |

| VUAP - V3              | Charge Pump Turnoff voltage                                   |                                                                               | 11.9  | 13.2  | 14.1  | V    |

# 7.5 Electrical Characteristics (continued)

$T_J$  = -55°C to +125°C; typical values at  $T_J$  = 25°C,  $V_{(A)}$  =  $V_{(OUT)}$  =  $V_{(VS)}$  =  $V_{(VSNS)}$  = 12 V,  $V_{(AC)}$  = 20 mV,  $V_{(VCAP)}$  = 0.1  $\mu$ F,  $V_{(EN/UVLO)}$  = 2 V, over operating free-air temperature range (unless otherwise noted)

| PARAMETER                                                                      | TEST CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | MIN  | TYP  | MAX  | UNIT |

|--------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| Charge Pump UVLO voltage threshold, rising                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5.4  | 6.6  | 7.9  | V    |

| Charge Pump UVLO voltage threshold, falling                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.4  | 5.5  | 6.6  | V    |

| C, DGATE)                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |      |      |      |

| V <sub>(A)</sub> POR threshold, rising                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2.2  | 2.35 | 2.6  | V    |

| V <sub>(A)</sub> POR threshold, falling                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2    | 2.2  | 2.4  | V    |

| Regulated Forward V <sub>(A)</sub> –V <sub>(C)</sub><br>Threshold              | For LM74800 Only                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 6.8  | 10   | 13.4 | mV   |

| V <sub>(A)</sub> –V <sub>(C)</sub> Threshold for Fast Reverse Current Blocking |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -6.5 | -5.5 | -1.3 | mV   |

| V <sub>(A)</sub> –V <sub>(C)</sub> Threshold for Reverse to Forward transition |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 150  | 177  | 220  | mV   |

| Gate Drive Voltage                                                             | 3 V < V <sub>(S)</sub> < 5 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 7    |      |      | V    |

| Gate Drive voltage                                                             | 5 V < V <sub>(S)</sub> < 65 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 10   | 11.5 | 13   | V    |

| Peak Gate Source current                                                       | V <sub>(A)</sub> – V <sub>(C)</sub> = 100 mV, V <sub>(DGATE)</sub> – V <sub>(A)</sub> =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      | 20   |      | mA   |

| Peak Gate Sink current                                                         | $V_{(A)} - V_{(C)} = -12 \text{ mV}, V_{(DGATE)} - V_{(A)} = 11 \text{ V}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      | 2670 |      | mA   |

| Regulation sink current                                                        | V <sub>(A)</sub> – V <sub>(C)</sub> = 0 V, V <sub>(DGATE)</sub> – V <sub>(A)</sub> = 11<br>V, LM74800 Only                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7.2  | 12.3 |      | μΑ   |

| Cathoda lagkaga Current                                                        | V <sub>(A)</sub> = -14 V, V <sub>(C)</sub> = 12 V, LM74801                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0.1  | 2.84 | 15   | μA   |

| Catriode leakage Current                                                       | V <sub>(A)</sub> = -14 V, V <sub>(C)</sub> = 12 V, LM74800                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4    | 8.77 | 32   | μΑ   |

| ROLLER (HGATE, OUT, SNS, SW, OV)                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |      |      |      |

| Cata Drive Voltage                                                             | 3 V < V <sub>(S)</sub> < 5 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 7    |      |      | V    |

| Gate Drive voltage                                                             | 5 V < V <sub>(S)</sub> < 65 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 10   | 11.1 | 14.5 | V    |

| Source Current                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 39   | 55   | 75   | μΑ   |

| Sink Current                                                                   | $V_{(OV)} > V_{(OVR)}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 168  | 260  |      | mA   |

|                                                                                | Charge Pump UVLO voltage threshold, rising Charge Pump UVLO voltage threshold, falling  C, DGATE)  V <sub>(A)</sub> POR threshold, rising V <sub>(A)</sub> POR threshold, falling Regulated Forward V <sub>(A)</sub> -V <sub>(C)</sub> Threshold  V <sub>(A)</sub> -V <sub>(C)</sub> Threshold for Fast Reverse Current Blocking  V <sub>(A)</sub> -V <sub>(C)</sub> Threshold for Reverse to Forward transition  Gate Drive Voltage  Peak Gate Source current  Peak Gate Sink current  Regulation sink current  Cathode leakage Current  ROLLER (HGATE, OUT, SNS, SW, OV)  Gate Drive Voltage  Source Current |      |      |      |      |

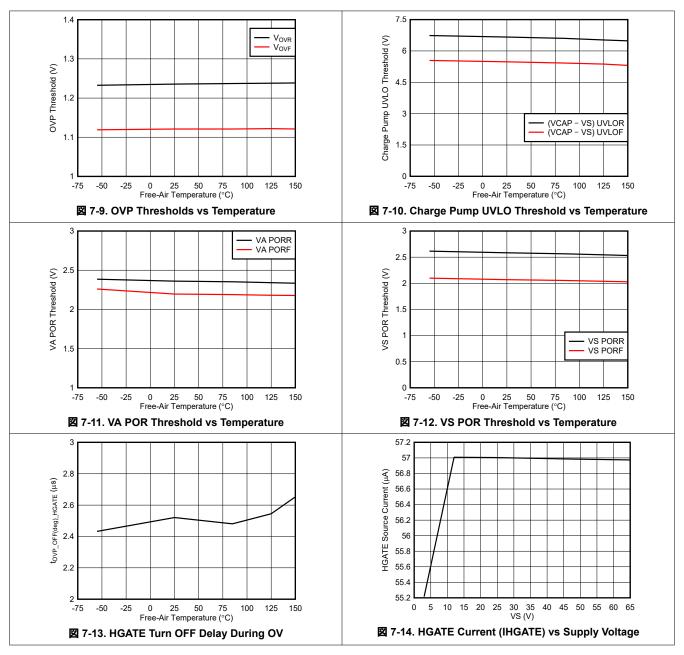

# 7.6 Switching Characteristics

$T_J$  = -55°C to +125°C; typical values at  $T_J$  = 25°C,  $V_{(A)}$  =  $V_{(C)}$  =  $V_{(OUT)}$  =  $V_{(VS)}$  = 12V,  $V_{(AC)}$  = 20 mV,  $C_{(VCAP)}$  = 0.1  $\mu$ F,  $V_{(EN/UVLO)}$  = 2 V, over operating free-air temperature range (unless otherwise noted)

|                                 | PARAMETER                                            | TEST CONDITIONS                                                                                                              | MIN | TYP  | MAX   | UNIT |

|---------------------------------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|-----|------|-------|------|

| t <sub>DGATE_OFF(dly)</sub>     | DGATE Turnoff Delay during reverse voltage detection | $V_{(A)} - V_{(C)} = +30 \text{ mV to } -100 \text{ mV}$<br>to $V_{(DGATE-A)} < 1 \text{ V, } C_{(DGATE-A)} = 10 \text{ nF}$ |     | 0.5  | 0.875 | μs   |

| t <sub>DGATE_ON(dly)</sub>      | DGATE Turnon Delay during forward voltage detection  | $V_{(A)} - V_{(C)} = -20$ mV to +700<br>mV to $V_{(DGATE-A)} > 5$ V, $C_{(DGATE-A)} = 10$<br>nF                              |     | 2.8  | 3.8   | μs   |

| t <sub>EN(dly)_DGATE</sub>      | DGATE Turnon Delay during EN/<br>UVLO                | EN/UVLO $\uparrow$ to V <sub>(DGATE-A)</sub> > 5V,<br>C <sub>(DGATE-A)</sub> = 10 nF                                         | 98  | 175  | 270   | μs   |

| t <sub>EN_OFF(deg)_DGATE</sub>  | DGATE Turnoff Deglitch during EN/<br>UVLO            | EN/UVLO ↓ to DGATE ↓                                                                                                         |     | 8.1  |       | μs   |

| t <sub>EN_OFF(deg)_HGATE</sub>  | HGATE Turnoff Deglitch during EN/<br>UVLO            | EN/UVLO ↓ to HGATE ↓                                                                                                         | 3   | 4.6  | 6     | μs   |

| t <sub>OVP_OFF(deg)_</sub> HGAT | HGATE Turnoff Deglitch during OV                     | OV ↑ to HGATE ↓, For LM74800 only                                                                                            |     | 3.98 | 5.4   | μs   |

| E                               | TIOATE Tarrior Degition during OV                    | OV ↑ to HGATE ↓, For LM74801 only                                                                                            |     | 3.2  | 4.7   | μs   |

# 7.6 Switching Characteristics (continued)

$T_J$  = -55°C to +125°C; typical values at  $T_J$  = 25°C,  $V_{(A)}$  =  $V_{(C)}$  =  $V_{(OUT)}$  =  $V_{(VS)}$  = 12V,  $V_{(AC)}$  = 20 mV,  $V_{(VCAP)}$  = 0.1  $\mu$ F,  $V_{(EN/UVLO)}$  = 2 V, over operating free-air temperature range (unless otherwise noted)

| PARAMETER                                                      | TEST CONDITIONS | MIN | TYP  | MAX | UNIT |

|----------------------------------------------------------------|-----------------|-----|------|-----|------|

| t <sub>OVP_ON(deg)_HGATE</sub> HGATE Turnon Deglitch during OV | OV ↓ to HGATE ↑ |     | 2.95 |     | μs   |

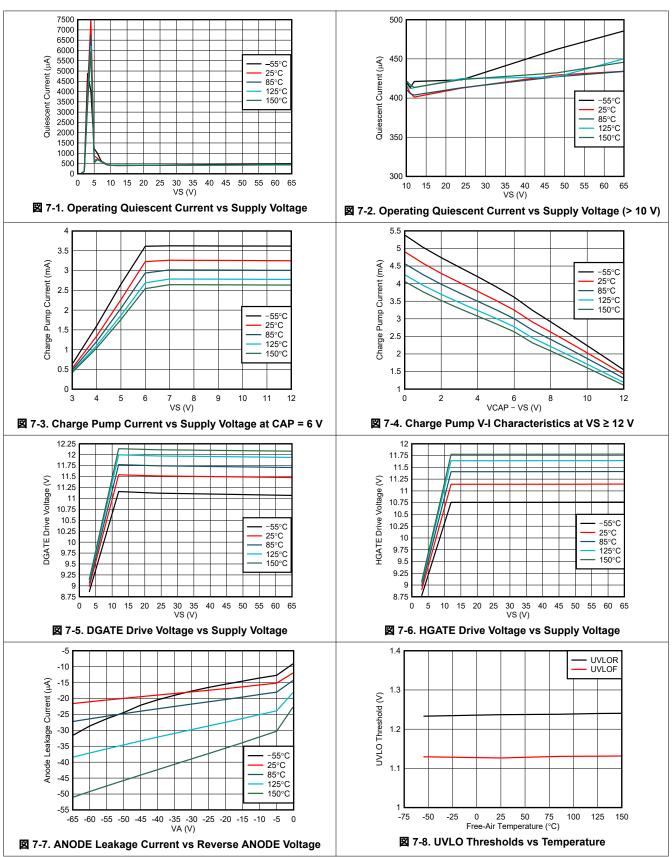

# 7.7 Typical Characteristics

# 7.7 Typical Characteristics (continued)

English Data Sheet: SNOSDD8

# **8 Parameter Measurement Information**

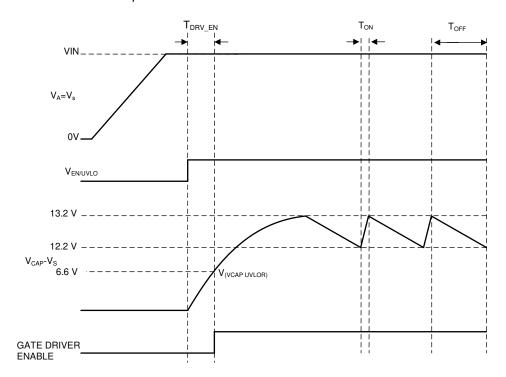

図 8-1. Timing Waveforms

# 9 Detailed Description

#### 9.1 Overview

The LM7480 ideal diode controller drives and controls external back to back N-Channel MOSFETs to emulate an ideal diode rectifier with power path ON/OFF control, inrush current limiting and overvoltage protection. The wide input supply of 3 V to 65 V allows protection and control of 12-V and 24-V automotive battery powered ECUs. The device can withstand and protect the loads from negative supply voltages down to –65 V. An integrated ideal diode controller (DGATE) drives the first MOSFET to replace a Schottky diode for reverse input protection and output voltage holdup. A strong charge pump with 20-mA peak GATE source current driver stage and short turn ON and turn OFF delay times ensures fast transient response ensuring robust performance during automotive testing such as ISO16750 or LV124 where an ECU is subjected to AC superimpose input signals. With a second MOSFET in the power path the device allows load disconnect (ON/OFF control) and overvoltage protection using HGATE control. The device features an adjustable overvoltage cut-off protection feature using a programming resistor across SW and OVP terminal.

The LM7480 controller can drive the external MOSFETs in common drain and common source configurations. With common drain configuration of the power MOSFETs, the mid-point can be utilized for OR-ing designs using an another ideal diode. The LM7480 has a maximum voltage rating of 65 V. The loads can be protected from extended overvoltage transients like 200-V unsuppressed load dumps in 24-V battery systems by configuring the device with external MOSFETs in common source topology.

The LM74800 controls the DGATE of the MOSFET to regulate the forward voltage drop at 10.5 mV. The linear regulation scheme in these devices enables graceful control of the GATE voltage and turns off of the MOSFET during a reverse current event and ensures zero DC reverse current flow. The LM74801 features a comparator based scheme to turn ON/OFF the MOSFET GATE.

The device features enable control. With the enable pin low during the standby mode, both the external MOSFETs and controller is off and draws a very low 2.87  $\mu$ A of current. The high voltage rating of LM7480 helps to simplify the system designs for automotive ISO7637 protection. The LM74800 is also suitable for ORing applications.

# 9.2 Functional Block Diagram

English Data Sheet: SNOSDD8

www.ti.com/ja-jp

## 9.3 Feature Description

# 9.3.1 Charge Pump

The charge pump supplies the voltage necessary to drive the external N-channel MOSFET. An external charge pump capacitor is placed between CAP and VS pins to provide energy to turn on the external MOSFET. In order for the charge pump to supply current to the external capacitor, the EN/UVLO pin voltage must be above the specified input high threshold, V<sub>(ENR)</sub>. When enabled the charge pump sources a charging current of 2.7-mA typical. If EN/UVLO pin is pulled low, then the charge pump remains disabled. To ensure that the external MOSFET can be driven above its specified threshold voltage, the CAP to VS voltage must be above the undervoltage lockout threshold, typically 6.6 V, before the internal gate driver is enabled. Use 式 1 to calculate the initial gate driver enable delay.

$$T_{\left(\mathsf{DRV\_EN}\right)} = 175 \mu s + C_{\left(\mathsf{CAP}\right)} x \frac{V_{\left(\mathsf{CAP\_UVLOR}\right)}}{2.7 m A} \tag{1}$$

where

- $C_{(CAP)}$  is the charge pump capacitance connected across VS and CAP pins

- $V_{(CAP\ UVLOR)} = 6.6\ V\ (typical)$

To remove any chatter on the gate drive approximately 1 V of hysteresis is added to the VCAP undervoltage lockout. The charge pump remains enabled until the CAP to VS voltage reaches 13.2 V, typically, at which point the charge pump is disabled decreasing the current draw on the VS pin. The charge pump remains disabled until the CAP to VS voltage is below to 12.2 V typically at which point the charge pump is enabled. The voltage between CAP and VS continue to charge and discharge between 12.2 V and 13.2 V as shown in 🗵 9-1. By enabling and disabling the charge pump, the operating quiescent current of the LM7480 is reduced. When the charge pump is disabled it sinks 15 µA.

図 9-1. Charge Pump Operation

#### 9.3.2 Dual Gate Control (DGATE, HGATE)

The LM7480x feature two separate gate control and driver outputs i.e DGATE and HGATE to drive back to back N-channel MOSFETs.

#### 9.3.2.1 Reverse Battery Protection (A, C, DGATE)

A, C, DGATE comprises of Ideal Diode stage. Connect the Source of the external MOSFET to A, Drain to C and Gate to DGATE. The LM7480x has integrated reverse input protection down to -65 V.

Before the DGATE driver is enabled, following conditions must be achieved:

- The EN/UVLO pin voltage must be greater than the specified input high voltage.

- The CAP to VS voltage must be greater than the undervoltage lockout voltage.

- Voltage at A pin must be greater than VA POR Rising threshold.

- Voltage at Vs pin must be greater than Vs POR Rising thershold.

If the above conditions are not achieved, then the DGATE pin is internally connected to the A pin, assuring that the external MOSFET is disabled.

In LM74800 the voltage drop across the MOSFET is continuously monitored between the A and C pins, and the DGATE to A voltage is adjusted as needed to regulate the forward voltage drop at 10.5 mV (typ). This closed loop regulation scheme enables graceful turn off of the MOSFET during a reverse current event and ensures zero DC reverse current flow. This scheme ensures robust performance during slow input voltage ramp down tests. Along with the linear regulation amplifier scheme, the LM74800 also integrates a fast reverse voltage comparator. When the voltage drop across A and C reaches V(AC REV) threshold then the DGATE goes low within 0.5-us (typ). This fast reverse voltage comparator scheme ensures robust performance during fast input voltage ramp down tests such as input micro-shorts. The external MOSFET is turned ON back when the voltage across A and C hits V(AC FWD) threshold within 2.8 µs (typ).

In LM74801, reverse current blocking is by fast reverse voltage comparator only. When the voltage drop across A and C reaches V(AC REV) threshold then the DGATE goes low within 0.5 µs (typ). This fast reverse voltage comparator scheme ensures robust performance during fast input voltage ramp down tests such as input LM7480 micro-shorts. The external MOSFET is turned ON back when the voltage across A and C hits V(AC FWD) threshold within 2.8 µs (typ).

For Ideal Diode only designs, connect LM7480x as shown in 29-2.

図 9-2. Configuring LM7480x-Q1 for Ideal Diode Only

## 9.3.2.2 Load Disconnect Switch Control (HGATE, OUT)

HGATE and OUT comprises of Load disconnect switch control stage. Connect the Source of the external MOSFET to OUT and Gate to HGATE.

Before the HGATE driver is enabled, following conditions must be achieved:

The EN/UVLO pin voltage must be greater than the specified input high voltage.

- The CAP to VS voltage must be greater than the undervoltage lockout voltage.

- Voltage at Vs pin must be greater than Vs POR Rising thershold.

If the above conditions are not achieved, then the HGATE pin is internally connected to the OUT pin, assuring that the external MOSFET is disabled.

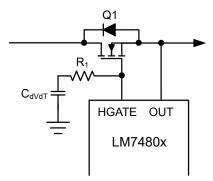

For Inrush Current limiting, connect  $C_{dVdT}$  capacitor and  $R_1$  as shown in  $\boxtimes$  9-3.

図 9-3. Inrush Current Limiting

The  $C_{dVdT}$  capacitor is required for slowing down the HGATE voltage ramp during power up for inrush current limiting. Use  $\not\equiv$  2 to calculate  $C_{dVdT}$  capacitance value.

$$C_{dVdT} = \frac{I_{HGATE\_DRV}}{I_{INRUSH}} x C_{OUT}$$

(2)

where  $I_{HATE\_DRV}$  is 55  $\mu A$  (typ),  $I_{INRUSH}$  is the inrush current and  $C_{OUT}$  is the output load capacitance. An extra resistor,  $R_1$ , in series with the  $C_{dVdT}$  capacitor improves the turn off time.

## 9.3.3 Overvoltage Protection and Battery Voltage Sensing (VSNS, SW, OV)

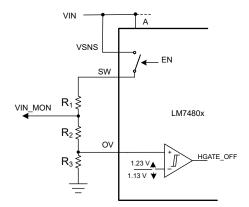

Connect a resistor ladder as shown in 29-4 for overvoltage threshold programming.

図 9-4. Programming Overvoltage Threshold and Battery Sensing

A disconnect switch is integrated between VSNS and SW pins. This switch is turned OFF when EN/UVLO pin is pulled low. This helps to reduce the leakage current through the resistor divider network during system shutdown state (IGN OFF state).

LM7480-Q1 OV pin can also be used as a control input to turn off HGATE drive to achieve load disconnect functionality. When OV pin is driven high  $(V_{OV} > V_{OVR})$ , device pulls down HGATE to OUT thus turning off the load disconnect MOSFET. When OV pin is pulled low  $(V_{OV} < V_{OVF})$  HGATE drive is again enabled to trun on the

load disconnect MOSFET. When OV pin is used as a control input to turn on/off load disconnect MOSFET, ensure device EN/UVLO pin is high ( $V_{EN/UVLO} > V_{ENR}$ ) and SW/VSNS pin voltage is higher than OV pin voltage.

## 9.3.4 Low Iq Shutdown and Under Voltage Lockout (EN/UVLO)

The enable pin allows for the gate driver to be either enabled or disabled by an external signal. If the EN/UVLO pin voltage is greater than the rising threshold, the gate driver and charge pump operates as described in Charge Pump section. If EN/UVLO pin voltage is less than the input low threshold,  $V_{(ENF)}$ , the charge pump and both the gate drivers (DGATE and HGATE) are disabled placing the LM7480 in shutdown mode. If  $V_{(ENF)} < V_{(EN/UVLO)} < V_{(UVLOF)}$  then only HGATE is disabled disconnecting the load from the supply, DGATE remains ON. The EN/UVLO pin can withstand a maximum voltage of 65 V. For always ON operation connect EN/UVLO pin to VS.

#### 9.4 Device Functional Modes

#### **Shutdown Mode**

The LM7480 enters shutdown mode when the EN/UVLO pin voltage is below the specified input low threshold  $V_{(ENF)}$ . Both the gate drivers and the charge pump are disabled in shutdown mode. During shutdown mode the LM7480 enters low IQ operation with a total input quiescent consumption of 2.87  $\mu$ A (typ). When the LM7480 is in shutdown mode, forward current flow to always ON loads connected to the common drain point of the back to back MOSFETs is not interrupted but is conducted through the MOSFET's body diode.

## 9.5 Application Examples

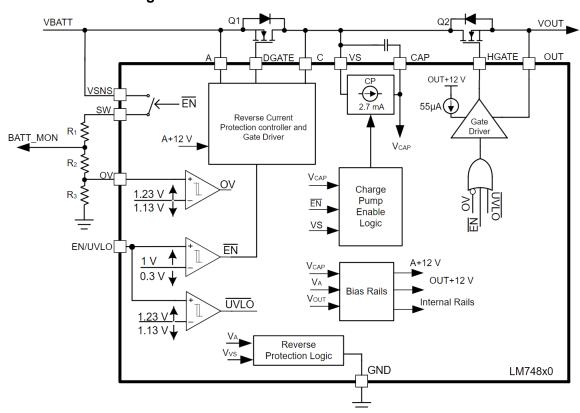

# 9.5.1 Redundant Supply OR-ing with Inrush Current Limiting, Overvoltage Protection and ON/OFF Control

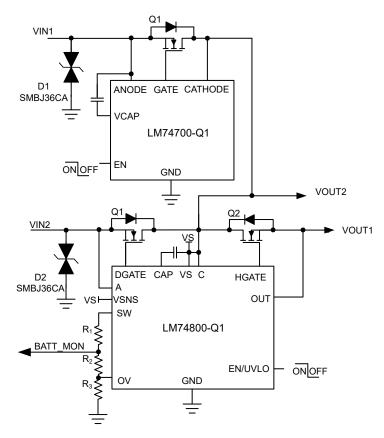

図 9-5. Redundant Supply OR-ing with Overvoltage Protection and ON/OFF Control

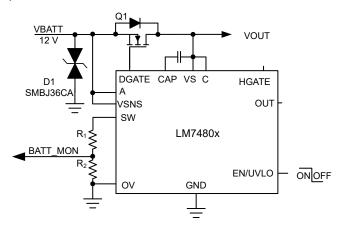

☑ 9-5 shows the implementation of Dual OR-ing with Inrush Current Limiting, overvoltage Protection and power path ON/OFF control. The input side SMBJ36CA TVS across the ideal diodes is required for ISO7637 Pulse 1 transient suppression to limit the input voltage within the device max voltage rating of –65V.

R1 and R2 are the programming resistors for over voltage protection (OVP) threshold. When the voltage at OV pin exceeds OV cut-off reference threshold then the HGATE driver turns OFF the FET Q3, disconnecting the power path and protecting the downstream load. HGATE goes high once the OVP pin voltage goes below the OVP falling hysteresis threshold. Use 0.1-µF to 1-µF capacitor across VS to CAP pins of the LM7480. This is the charge pump capacitor and acts as the supply for both the DGATE and HGATE driver stages. The DGATE driver of the LM7480 is equipped with 20-mA peak source current and 2.6-A peak sink current capability resulting in fast and efficient transient responses during the ISO16750 or LV124 short interruptions as well as AC superimpose testing.

Pull EN low during the sleep/standby mode. With EN low, both the DGATE and HGATE drivers are pulled low turning OFF both the power FETs. VOUT1 gets disconnected from the input supply rail reducing the system  $I_Q$ . VOUT2 is gets power through the body diode of the MOSFET Q2 and this supply can be utilized for always ON loads. The LM7480 draws a  $2.87-\mu A$  (typ) current during this mode.

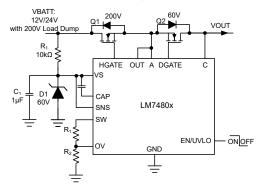

#### 9.5.2 Ideal Diode With Unsuppressed Load Dump Protection

An extended overvoltage protection support above 65 V can be achieved by configuring the device with external back to back MOSFETs in common source topology as shown in ot 9-6. Place a resistor R1 and a zener clamp across VS pin to GND to limit the voltage below 65 V. The load gets protected from overvoltages transients like unsuppressed load dumps with the help of overvoltage protection feature. Use R2 and R3 for setting the overvoltage protection threshold. When voltage at OV pin exceeds the set OV threshold then the HGATE turns OFF. This results in power path disconnection between input and output.

☑ 9-6. Ideal Diode With 200-V Unsupressed Load Dump Protection

# 10 Applications and Implementation

注

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes, as well as validating and testing their design implementation to confirm system functionality.

# **10.1 Application Information**

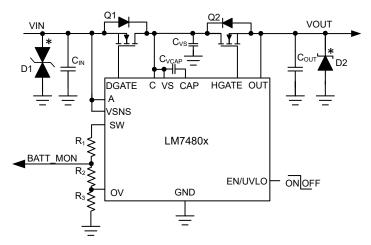

LM7480 controls two N-channel power MOSFETs with DGATE used to control diode MOSFET to emulate an ideal diode and HGATE controlling second MOSFET for power path cut-off when disabled or during an overvoltage protection. HGATE controlled MOSFET can be used to clamp the output during overvoltage or load dump conditions. LM7480 can be placed into low quiescent current mode using EN/UVLO, where both DGATE and HGATE are turned OFF.

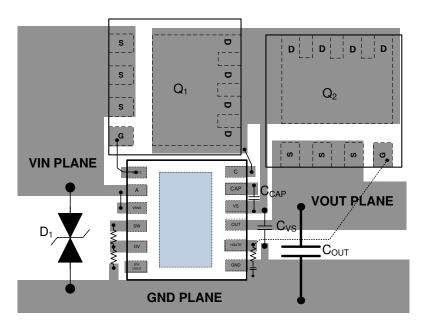

The device has a separate supply input pin (Vs). The charge pump is derived from this supply input. With the separate supply input provision and separate GATE control architecture, the LM7480 device offers flexibility in system design architectures and enables circuit design with various power path control topologies like common drain, common source, ORing and Power MUXing. With these various topologies, the system designers can design the front-end power system to meet various system design requirements. For more information, see the Six System Architectures With Robust Reverse Battery Protection Using an Ideal Diode Controller Application Report.

# 10.2 Typical 12-V Reverse Battery Protection Application

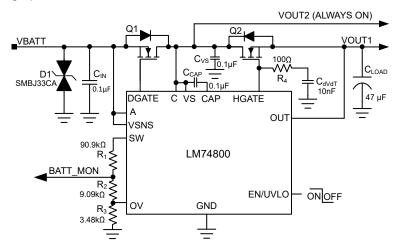

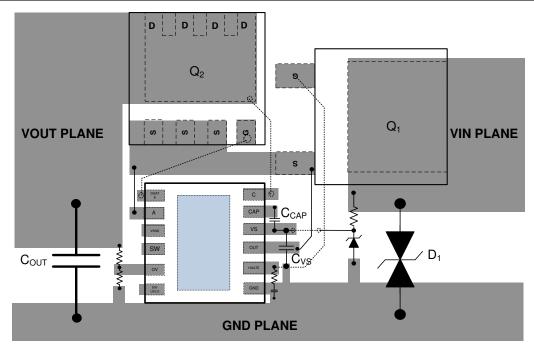

A typical application circuit of LM74800 configured in **common-drain topology** to provide reverse battery protection with overvoltage protection is shown in  $\boxtimes$  10-1.

図 10-1. Typical Application Circuit: 12-V Reverse Battery Protection and Overvoltage Protection

# 10.2.1 Design Requirements for 12-V Battery Protection

The system design requirements are listed in 表 10-1.

表 10-1. Design Parameters for 12-V Reverse Battery Protection and Overvoltage Protection

| DESIGN PARAMETER              | EXAMPLE VALUE                                                       |  |  |  |

|-------------------------------|---------------------------------------------------------------------|--|--|--|

| Operating Input Voltage Range | 12-V battery, 12-V nominal with 3.2-V cold crank and 35-V load dump |  |  |  |

| Output Power                  | 50 W                                                                |  |  |  |

| Output Current Range          | 4-A nominal, 5-A maximum                                            |  |  |  |

| Input Capacitance             | 0.1-μF minimum                                                      |  |  |  |

| Output Capacitance            | 0.1-μF minimum (optional hold-up capacitor of 47 μF )               |  |  |  |

| Overvoltage Cut-off           | 37 V, output cut-off > 37 V                                         |  |  |  |

| Battery Monitor Ratio         | 8:1                                                                 |  |  |  |

#### 10.2.2 Automotive Reverse Battery Protection

The LM7480 feature two separate gate control and driver outputs i.e DGATE and HGATE to drive back to back N-channel MOSFETs. This enables LM7480 to provide comprehensive immunity with robust system protection during various automotive transient tests as per ISO 7637-2 and ISO 16750-2 standard as well as other automotive OEM standards. For more information, see the *Automotive EMC-compliant reverse-battery protection with ideal-diode controllers* article.

LM7480 gate drive output DGATE controls MOSFET Q1 to provide reverse battery protection and true reverse current blocking functionality. HGATE controls MOSFET Q2 to turn off the power path during input overvoltage condition. Resistor network R1, R2 and R3 connected to OV and SW can be configured for overvoltage protection and also for battery monitoring under normal operating conditions as well as reverse battery conditions. Bi-directional TVS D1 clamps the automotive transient input voltages on the 12-V battery, both positive and negative transients, to voltage levels safe for MOSFET Q1 and LM7480.

Fast reverse current blocking response and quick reverse recovery enables LM7480 to turn ON/OFF MOSFET Q1 during AC super imposed input and provide active rectification of the AC input superimposed on DC battery voltage. Fast reverse current blocking response of LM7480 helps to turn off MOSFET Q1 during negative transients inputs and input micro short interruption conditions where input can fall to 0-V for short duration.

#### 10.2.3 Detailed Design Procedure

# 10.2.3.1 Design Considerations

表 10-1 summarizes the design parameters that must be known for designing an automotive reverse battery protection circuit with overvoltage cut-off. During power up, inrush current through MOSFET Q2 needs to be limited so that the MOSFET operates well within its SOA. Maximum load current, maximum ambient temperature and thermal properties of the PCB determine the R<sub>DSON</sub> of the MOSFET Q2 and maximum operating voltage determines the voltage rating of the MOSFET Q2. Selection of MOSFET Q2 is determined mainly by the maximum operating load current, maximum ambient temperature, maximum frequency of AC super imposed voltage ripple and ISO 7637-2 pulse 1 requirements. overvoltage threshold is decided based on the rating of downstream DC/DC converter or other components after the reverse battery protection circuit. A single bidirectional TVS or two back-back uni-directional TVS are required to clamp input transients to a safe operating level for the MOSFETs Q1, Q2 and LM7480.

#### 10.2.3.2 Charge Pump Capacitance VCAP

Minimum required capacitance for charge pump VCAP is based on input capacitance of the MOSFET Q1,  $C_{ISS(MOSFET\ Q1)}$  and input capacitance of Q2  $C_{ISS(MOSFET)}$ .

Charge Pump VCAP: Minimum 0.1  $\mu$ F is required; recommended value of VCAP ( $\mu$ F)  $\geq$  10 x (  $C_{ISS(MOSFET\_Q1)} + C_{ISS(MOSFET\_Q2)}$ ) ( $\mu$ F)

# 10.2.3.3 Input and Output Capacitance

A minimum input capacitance C<sub>IN</sub> of 0.1 µF and output capacitance C<sub>OUT</sub> of 0.1 µF is recommended.

# 10.2.3.4 Hold-Up Capacitance

Usually bulk capacitors are placed on the output due to various reasons such as uninterrupted operation during power interruption or micro-short at the input, hold-up requirements for doing a memory dump before turning of the module and filtering requirements as well. This design considers minimum bulk capacitors requirements for meeting functional status "A" during LV124 E10 test case 2 100-µs input interruption. To achieve functional pass status A, acceptable voltage droop in the output of LM7480 is based on the UVLO settings of downstream DC-DC converters. For this design, 2.5-V drop in output voltage for 100 µs is considered and the minimum hold-up capacitance required is calculated by

$$C_{HOLD\_UP\_MIN} = \frac{I_{LOAD\_MAX}}{dV_{OUT}} x 100 \,\mu s \tag{3}$$

Minimum hold-up capacitance required for 2.5-V drop in 100 μs is 200 μF. Note that the typical application circuit shows the hold-up capacitor as optional because not all designs require hold-up capacitance.

#### 10.2.3.5 Overvoltage Protection and Battery Monitor

Resistors  $R_1$ ,  $R_2$  and  $R_3$  connected in series are used to program the overvoltage threshold and battery monitor ratio. The resistor values required for setting the overvoltage threshold  $V_{OV}$  to 37.0 V and battery monitor ratio  $V_{BATT\ MON}$ :  $V_{BATT\ to}$  1:8 are calculated by solving Equation 3 and Equation 4.

$$V_{OVR} = \frac{R_3}{R_1 + R_2 + R_3} x V_{OV} \tag{4}$$

$$V_{BAT\_MON} = \frac{R_2 + R_3}{R_1 + R_2 + R_3} x V_{BATT}$$

(5)

For minimizing the input current drawn from the battery through resistors  $R_1$ ,  $R_2$  and  $R_3$ , it recommended to use higher value of resistance. Using high value resistors will add error in the calculations because the current

through the resistors at higher value will become comparable to the leakage current into the OV pin. Maximum leakage current into the OV pin is 1  $\mu$ A and choosing (R<sub>1</sub> + R<sub>2</sub> + R<sub>3</sub>) < 120 k $\Omega$  ensures current through resistors is 100 times greater than leakage through OV pin.

Based on the device electrical characteristics,  $V_{OVR}$  is 1.23 V and battery monitor ratio ( $V_{BATT\_MON}$  /  $V_{BATT}$ ) is designed for a ratio of 1/8. To limit ( $R_1 + R_2 + R_3$ ) < 120 k $\Omega$ , select ( $R_1 + R_2$ ) = 100 k $\Omega$ . Solving Equation 3 gives  $R_3$  = 3.45 k $\Omega$ . Solving Equation 4 for R2 using ( $R_1 + R_2$ ) = 100 k $\Omega$  and  $R_3$  = 3.45 k $\Omega$ , gives  $R_2$  = 9.48 k $\Omega$  and  $R_1$  = 90.52 k $\Omega$ .

Standard 1% resistor values closest to the calculated resistor values are R1 = 90.9 k $\Omega$ , R2 = 9.09 k $\Omega$  and R3 = 3.48 k $\Omega$ .

#### 10.2.4 MOSFET Selection: Blocking MOSFET Q1

For selecting the blocking MOSFET Q1, important electrical parameters are the maximum continuous drain current  $I_D$ , the maximum drain-to-source voltage  $V_{DS(MAX)}$ , the maximum drain-to-source voltage  $V_{GS(MAX)}$ , the maximum source current through body diode and the drain-to-source ON resistance  $R_{DSON}$ .

The maximum continuous drain current, ID, rating must exceed the maximum continuous load current.

The maximum drain-to-source voltage,  $V_{DS(MAX)}$ , must be high enough to withstand the highest differential voltage seen in the application. This would include all the automotive transient events and any anticipated fault conditions. It is recommended to use MOSFETs with  $V_{DS}$  voltage rating of 60 V along with a single bidirectional TVS or a  $V_{DS}$  rating 40-V maximum rating along with two unidirectional TVS connected back-back at the input.

The maximum  $V_{GS}$  LM7480 can drive is 14 V, so a MOSFET with 15-V minimum  $V_{GS}$  rating should be selected. If a MOSFET with < 15-V  $V_{GS}$  rating is selected, a zener diode can be used to clamp  $V_{GS}$  to safe level, but this would result in increased  $I_{Q}$  current.

To reduce the MOSFET conduction losses, lowest possible  $R_{DS(ON)}$  is preferred, but selecting a MOSFET based on low  $R_{DS(ON)}$  may not be beneficial always. Higher  $R_{DS(ON)}$  will provide increased voltage information to LM7480's reverse comparator at a lower reverse current. Reverse current detection is better with increased  $R_{DS(ON)}$ . Choosing a MOSFET with < 50-mV forward voltage drop at maximum current is a good starting point.

For active rectification of AC super imposed ripple on the battery supply voltage, gate-source charge  $Q_{GS}$  of Q1 must be selected to meet the required AC ripple frequency. Maximum gate-source charge  $Q_{GS}$  (at 4.5-V  $V_{GS}$ ) for active rectification every cycle is

$$Q_{GS\_MAX} = \frac{1.3mA}{F_{AC\_RIPPLE}}$$

(6)

Where 1.3 mA is minimum charge pump current at 7-V  $V_{DGATE}$ - $V_A$ ,  $F_{AC\_RIPPLE}$  is frequency of the AC ripple superimposed on the battery and  $Q_{GS\_MAX}$  is the  $Q_{GS}$  value specified in manufacturer datasheet at 6-V  $V_{GS}$ . For active rectification at  $F_{AC\_RIPPLE}$  = 30 KHz,  $Q_{GS\_MAX}$  = 43 nC.

Based on the design requirements, BUK7Y4R8-60E MOSFET is selected and its ratings are:

- 60-V V<sub>DS(MAX)</sub> and ±20-V V<sub>GS(MAX)</sub>

- $R_{DS(ON)}$  5.0-m $\Omega$  typical at 5-V  $V_{GS}$  and 2.9-m $\Omega$  rated at 10-V  $V_{GS}$

- MOSFET Q<sub>GS</sub> 17.4 nC

Thermal resistance of the MOSFET should be considered against the expected maximum power dissipation in the MOSFET to ensure that the junction temperature  $(T_J)$  is well controlled.

#### 10.2.5 MOSFET Selection: Hot-Swap MOSFET Q2

The  $V_{DS}$  rating of the MOSFET Q2 should be sufficient to handle the maximum system voltage along with the input transient voltage. For this 12-V design, transient overvoltage events are during suppressed load dump 35 V 400 ms and ISO 7637-2 pulse 2 A 50 V for 50  $\mu$ s. Further, ISO 7637-2 Pulse 3B is a very fast repetitive pulse of 100 V 100 ns that is usually absorbed by the input and output ceramic capacitors and the maximum voltage on the 12-V battery can be limited to < 40 V the minimum recommended input capacitance of 0.1  $\mu$ F. The 50-V

SO 7637-2 Pulse 2 A can also be absorbed by input and output capacitors and its amplitude could be reduced to 40-V peak by placing sufficient amount of capacitance at input and output. However for this 12-V design, maximum system voltage is 50 V and a 60-V  $V_{DS}$  rated MOSFET is selected.

The VGS rating of the MOSFET Q2 should be higher than that maximum HGATE-OUT voltage 15 V.

Inrush current through the MOSFET during input hot-plug into the 12-V battery is determined by output capacitance. External capacitor on HGATE,  $C_{DVDT}$  is used to limit the inrush current during input hot-plug or startup. The value of inrush current determined by  $\not \equiv 2$  need to be selected to ensure that the MOSFET Q2 is operating well within its safe operating area (SOA). To limit inrush current to 250 mA, value of  $C_{DVDT}$  is 10.43 nF, closest standard value of 10.0 nF is chosen.

Duration of inrush current is calculated by

$$dT_{INRUSH} = \frac{12}{I_{INRUSH}} x C_{OUT} \tag{7}$$

Calculated inrush current duration is 2.36 ms with 250-mA inrush current.

MOSFET BUK7Y4R8-60E having 60-V  $V_{DS}$  and  $\pm 20$ -V  $V_{GS}$  rating is selected for Q2. Power dissipation during inrush is well within the MOSFET's safe operating area (SOA).

#### 10.2.6 TVS Selection

A 600-W SMBJ TVS such as SMBJ33CA is recommended for input transient clamping and protection. For detailed explanation on TVS selection for 12-V battery systems, refer to TVS Selection for 12-V Battery Systems.

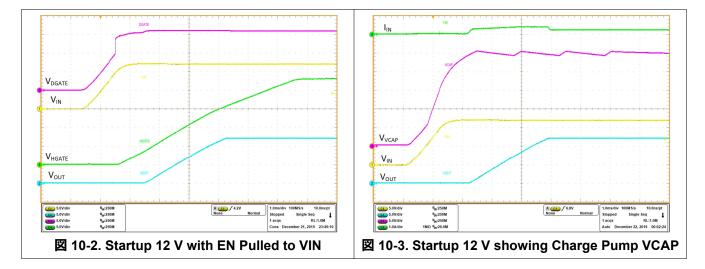

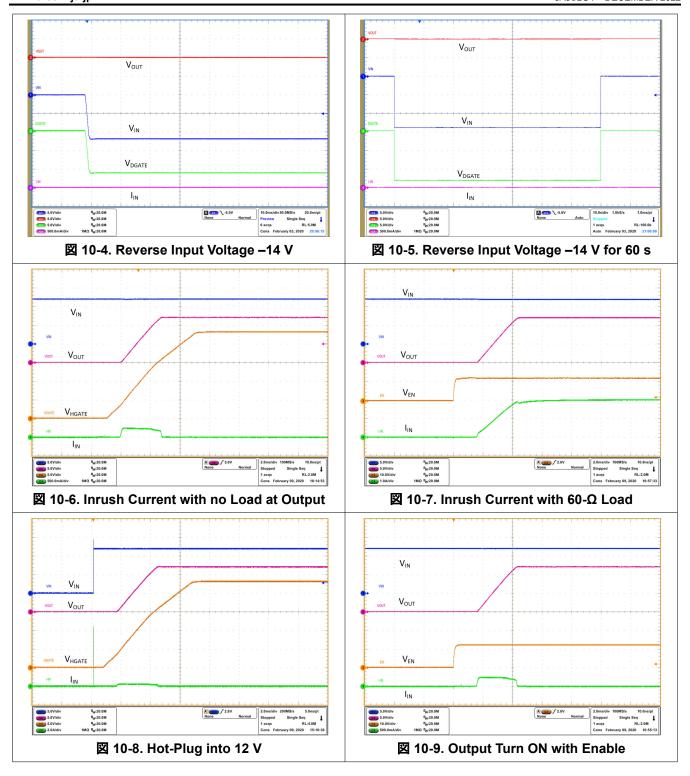

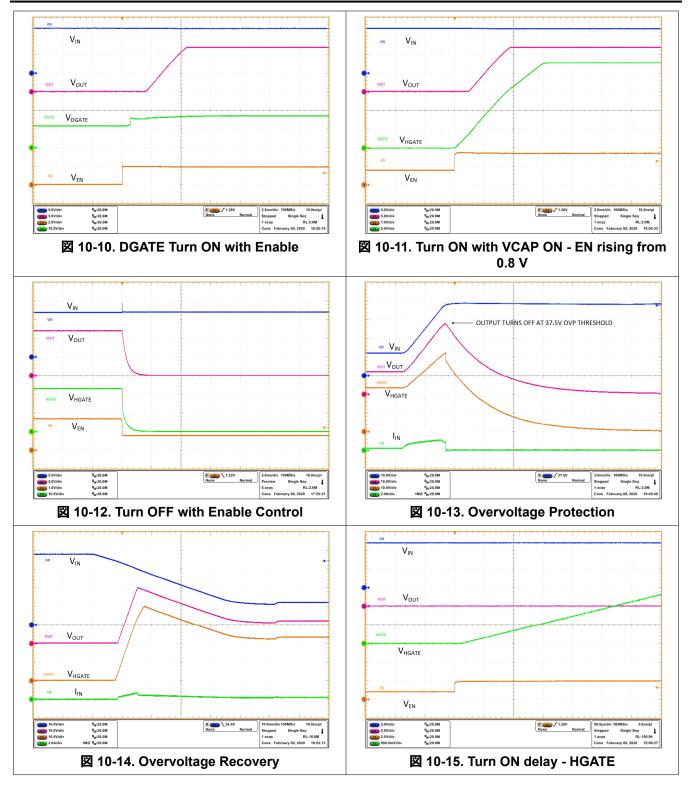

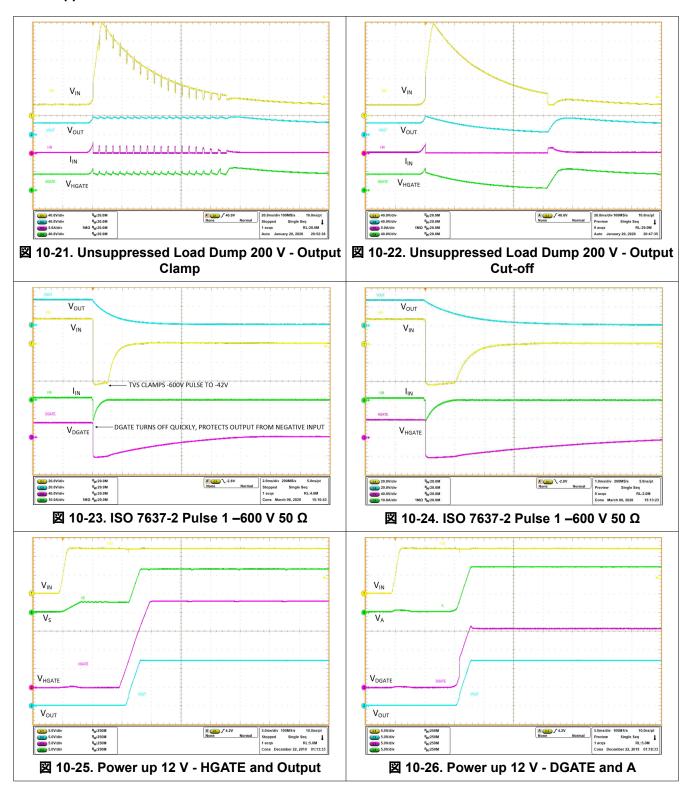

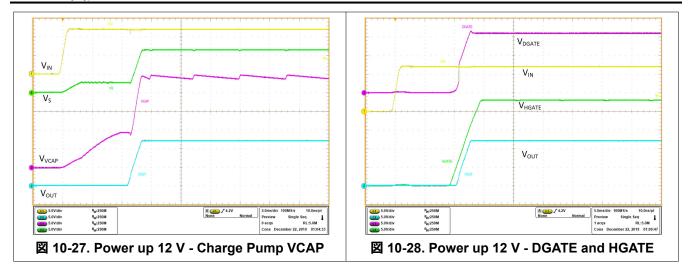

#### 10.2.7 Application Curves

# 10.3 200-V Unsuppressed Load Dump Protection Application

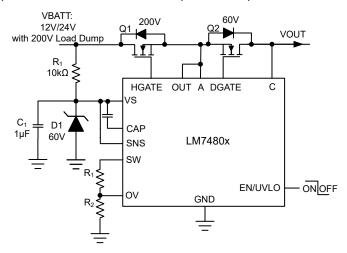

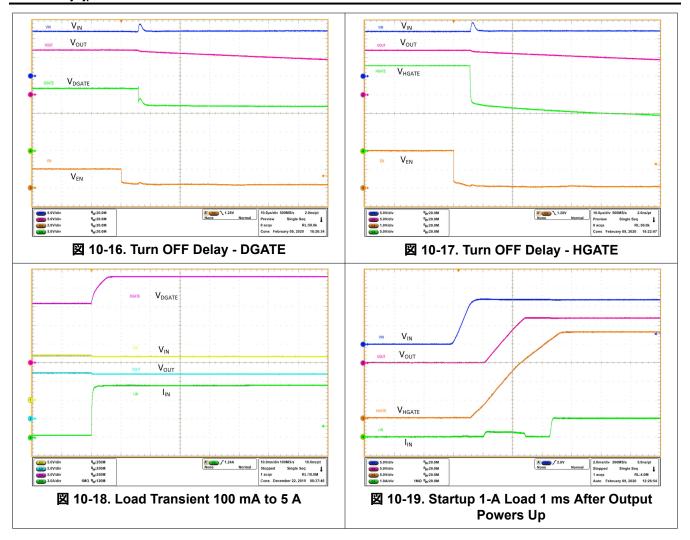

Independent gate drive topology of LM74800-Q1 enables to configure the LM74800-Q1 in to provide unsuppressed load dump or surge protection along with reverse battery protection. LM74800-Q1 configured in **common-source topology** to provide 200-V unsuppressed load dump protection with reverse battery protection is  $\boxtimes$  10-20.

図 10-20. Typical Application Circuit: 200-V Unsuppressed Load Dump Protection With Reverse Battery Protection

#### 10.3.1 Design Requirements for 200-V Unsuppressed Load Dump Protection

表 10-2. Design Parameters for 24-V Unsuppressed Load Dump Protection

| DESIGN PARAMETER                         | EXAMPLE VALUE                                                                                                |

|------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| Operating Input Voltage Range            | 24-V battery, 6 V during cold crank 200-V unsuppressed load lump                                             |

| Output Voltage                           | 6 V during cold crank and 37 V during load dump                                                              |

| Output Power                             | 25 W                                                                                                         |

| Output Current Range                     | 2-A nominal, 2.5-A peak                                                                                      |

| Input Capacitance                        | 0.1-μF minimum                                                                                               |

| Output Capacitance                       | 0.1-μF minimum, 220-μF typical hold-up capacitance                                                           |

| Overvoltage Cut-Off Threshold            | 37 V                                                                                                         |

| Overvoltage Clamp                        | Output clamped between 34.5 V and 37.5 V                                                                     |

| Automotive Transient Immunity Compliance | ISO 7637-2 and ISO 16750-2 including 200-V unsuppressed load dump Pulse 5 A and –600-V 50-Ω ISO-7637 Pulse 1 |

#### 10.3.2 Design Procedure

Load dump transients occurs on loads connected to the alternator when a discharged battery is disconnected from alternator while it is still generating charging current. Load dump amplitude and duration depends on alternator speed and field current into the rotor. The pulse shape and parameter are specified in ISO 7637-2 5A where a 200-V pulse lasts maximum 350 ms on 24-V battery system. Circuit topology and MOSFET ratings are important when designing a 200-V unsuppressed load dump protection circuit using LM74800-Q1. Dual gate drive enables LM74800-Q1 to be configured in common source topology in  $\boxtimes$  10-20 where MOSFET Q1 is used to turn off or clamp output voltage to acceptable safe level and protect the MOSFET Q2 and LM74800-Q1 from 200 V. Note that only the V<sub>S</sub> pin is exposed to 200 V through a 10-k $\Omega$  resistor. A 60-V rated zener diode is used to clamp and protect the V<sub>S</sub> pin. Rest of the circuit is not exposed to higher voltage as the MOSFET Q1 can either be turned off completely or output voltage clamped to safe level. MOSFET Q1 selection, input TVS selection and MOSFET Q2 selection for ISO 7637-2 and ISO 16750-2 compliance are discussed in this section.

#### 10.3.2.1 Boost Converter Components (C2, C3, L1)

Place a minimum of 1- $\mu$ F capacitor across drain of the FET to GND (C2) and across CAP pin of LM7472x-Q1 to drain of the FET (C3). Use a 100- $\mu$ H inductor (L1) with saturation current rating > 175 mA (for example, XPL2010-104ML from coil craft).

#### 10.3.2.2 Input and Output Capacitance

A minimum input capacitance  $C_{IN}$  of 0.1  $\mu F$  and output capacitance  $C_{OUT}$  of 0.1  $\mu F$  is recommended.

#### 10.3.2.3 V<sub>S</sub> Capacitance, Resistor, and Zener Clamp

Minimum of 1- $\mu$ F C<sub>VS</sub> capacitance is required. During 200-V load dump, resistor R<sub>1</sub> and Zener diode D<sub>1</sub> are used to protect VS pin from exceeding the maximum ratings by clamping V<sub>VS</sub> to 60 V. Choosing R<sub>1</sub> = 10 k $\Omega$ , the peak power dissipated in Zener diode D1 = 60 V × (200 V – 60 V) / 10 k $\Omega$  = 0.840 W of peak power dissipation. SMA package diode such as BZG03B62-M can handle 840-mW peak power dissipation. Peak power dissipated in R1 = (200 V – 60 V)² / 10 k $\Omega$  = 1.96 W. One 10-k $\Omega$  resistor in 1210 package with 0.5-W DC power rating and 200-V rating can withstand 200-V load dump for 350 ms.

#### 10.3.2.4 Overvoltage Protection and Output Clamp

Resistors  $R_2$  and  $R_3$  connected in series is used to program the overvoltage threshold. Connecting R2 to VBATT provides overvoltage cut-off and switching the connection to VOUT provides overvoltage clamp. The resistor values required for setting the overvoltage threshold  $V_{OV}$  to 37.0 V is calculated by solving Equation 7.

$$V_{OVR} = \frac{R_3}{R_2 + R_3} x V_{OV} \tag{8}$$

For minimizing the input current drawn from the battery through resistors  $R_2$  and  $R_3$ , it recommended to use higher value of resistance. Using high value resistors will add error in the calculations because the current through the resistors at higher value will become comparable to the leakage current into the OV pin. Maximum leakage current into the OV pin is 1  $\mu$ A and choosing ( $R_2 + R_3$ ) < 120 k $\Omega$  ensures current through resistors is 100 times greater than leakage through OV pin.

Based on the device electrical characteristics,  $V_{OVR}$  is 1.233V V. To limit  $(R_2 + R_3) < 120 \text{ k}\Omega$ , select  $(R_2) = 100 \text{ k}\Omega$ . Solving Equation 7 gives  $R_3 = 3.45 \text{ k}\Omega$ .