LMH6518 JAJSNR7E - MAY 2008 - REVISED JULY 2024

# LMH6518 900MHz、デジタル制御、可変ゲイン アンプ

# 1 特長

- ゲイン範囲:40dB

- ゲイン ステップ サイズ:2dB

- 総合ゲイン分解能 (GSPS ADC 使用時):8.5mdB

- 最小ゲイン:-1.16dB

- 最大ゲイン:38.8dB

- -3dB 帯域幅 (BW):900MHz

- 立ち上がりおよび立ち下がり時間: < 500ps

- 復帰時間:5ns 未満

- 伝搬遅延のばらつき:100ps

- HD2 (100MHz):-50dBc

- HD3 (100MHz): -53dBc

- 入力換算ノイズ (最大ゲイン):0.98nV/√Hz

- 過電圧クランプによる高速復帰

- 消費電力:1.1W (補助出力を無効化することで 0.75W に低減可能)

# 2 アプリケーション

- オシロスコープのプログラマブル ゲイン アンプ

- 差動 ADC ドライバ

- 高周波数のシングルエンド入力から差動への変換

- 高精度ゲイン制御アプリケーション

- 医療用アプリケーション

- RF/IF アプリケーション

### 3 概要

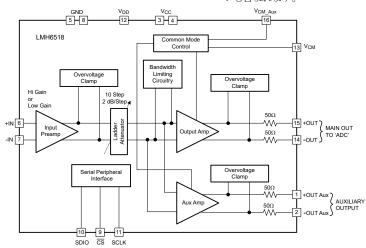

LMH6518 は、総合ゲインを -1.16dB から 38.8dB まで 40dB の範囲にわたって 2dB 刻みで変化させることがで きるデジタル制御可変ゲインアンプです。すべてのゲイン において、-3dB 帯域幅は 900MHz です。 各設定でのゲ イン精度は 0.1dB (標準値) です。 フルスケール レンジを 調整可能な、テキサス・インスツルメンツの GSPS (ギガサ ンプル毎秒) ADC と組み合わせて使用すると、LMH6518 はゲインを調整することで  $6.8 \text{mV}_{PP}$  から  $920 \text{mV}_{PP}$  のフ ルスケール入力信号に対応でき、 $700mV_{PP}$  (公称値) の ADC 入力を得ることができます。補助出力 (+OUT AUX、 -OUT AUX) はメイン出力に追従します。補助出力は、オ シロスコープのトリガ機能回路で使うことを想定しています が、その他の用途にも使用できます。

LMH6518 のゲインは、SPI 互換シリアル バスを介して設 定します。本デバイスのゲインと GSPS ADC FS 入力の 両方を操作した場合、8.5mdBの信号経路総合ゲイン分 解能を達成できます。入力と出力は DC 結合されていま す。出力は差動であり、個別の同相モード電圧制御機能 (メインおよび補助出力用)を備えています。また、選択可 能な (20MHz、100MHz、200MHz、350MHz、650MHz、 750MHz、全 BW) 帯域幅制限回路 (メイン出力と補助出 力の両方に共通)を備えています。

### パッケージ情報

|         | ALEII A A            |                          |

|---------|----------------------|--------------------------|

| 部品番号    | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |

| LMH6518 | RGH (WQFN, 16)       | 4mm × 4 mm               |

- 詳細については、セクション 10 を参照してください。

- パッケージ サイズ (長さ×幅) は公称値であり、該当する場合はピ ンも含まれます。

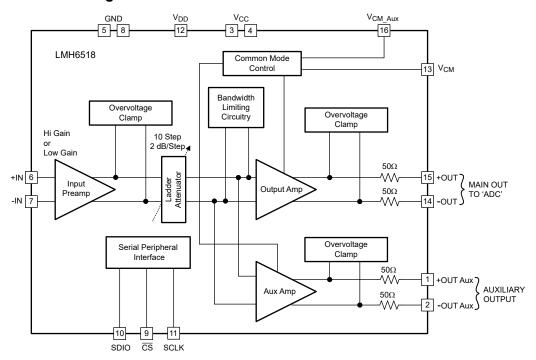

機能ブロック図

# **Table of Contents**

| 1 特長                                 | 1 6.5 Programming  | 19              |

|--------------------------------------|--------------------|-----------------|

| 2 アプリケーション                           |                    | <mark>23</mark> |

| 3 概要                                 | - 4 A 1: 1: 1 E 1: | <u>23</u>       |

| 4 Pin Configuration and Functions    |                    | <mark>23</mark> |

| 5 Specifications                     |                    | 36              |

| 5.1 Absolute Maximum Ratings         |                    | 37              |

| 5.2 ESD Ratings                      |                    | 38              |

| 5.3 Recommended Operating Conditions | 0.4.D              | 38              |

| 5.4 Thermal Information              |                    | 38              |

| 5.5 Electrical Characteristics       |                    | 38              |

| 5.6 Timing Requirements              |                    | 39              |

| 5.7 Typical Characteristics          |                    |                 |

| 6 Detailed Description1              |                    | 39              |

| 6.1 Overview1                        |                    |                 |

| 6.2 Functional Block Diagram1        |                    |                 |

| 6.3 Feature Description1             |                    |                 |

| 6.4 Device Functional Modes1         |                    | 39              |

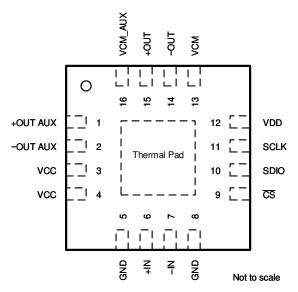

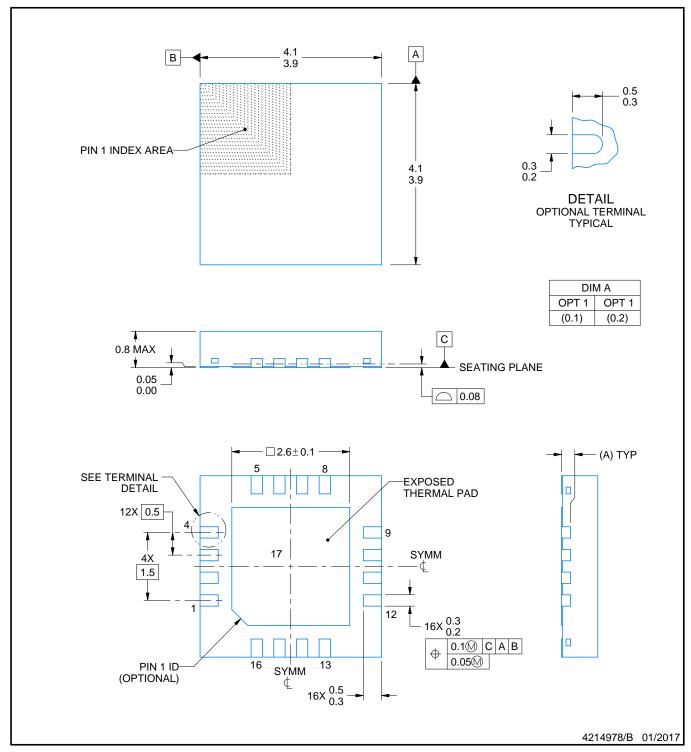

# 4 Pin Configuration and Functions

図 4-1. RGH Package, 16-Pin WQFN (Top View)

表 4-1. Pin Functions

| PIN |             | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----|-------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME        |                     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 1   | +OUT AUX    | 0                   | Auxiliary positive output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2   | -OUT AUX    | 0                   | Auxiliary negative output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 3   | VCC         | Р                   | Analog power supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 4   | VCC         | Р                   | Analog power supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5   | GND         | G                   | Ground, electrically connected to the WQFN heat sink                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 6   | +IN         | I                   | Positive input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 7   | -IN         | I                   | Negative input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 8   | GND         | G                   | Ground, electrically connected to the WQFN heat sink                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 9   | CS          | I                   | Serial chip select (SPI, active low): While this signal is asserted, SCLK is used to accept serial data present on SDIO and to source serial data on SDIO. When this signal is deasserted, SDIO is ignored and SDIO is in a high-impedance state.                                                                                                                                                                                                                                                                                                         |

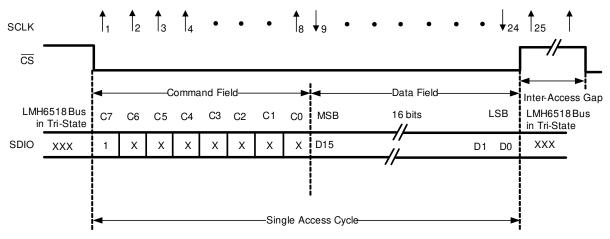

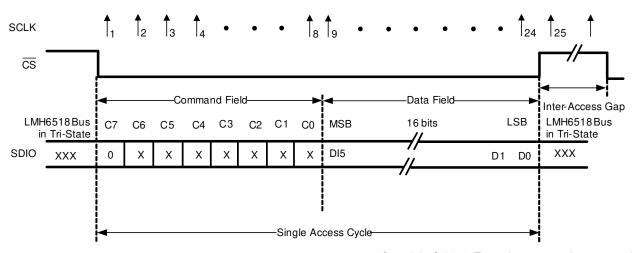

| 10  | SDIO        | I/O                 | Serial data-in or data-out (SPI). During a write operation, serial data are shifted into the device (8-bit command and 16-bit data) on this pin while $\overline{CS}$ signal is asserted. During a read operation, serial data are shifted out of the device on this pin while $\overline{CS}$ signal is asserted. At other times, and after one complete access cycle (24 bits; see $\boxtimes$ 6-1 and $\boxtimes$ 6-2), this input is ignored. This output is in a high-impedance state when $\overline{CS}$ is deasserted. This pin is bidirectional. |

| 11  | SCLK        | I                   | Serial clock (SPI): Serial data are shifted into and out of the device synchronous with this clock signal. SCLK transitions with $\overline{\text{CS}}$ deasserted are ignored. To minimize digital crosstalk, stop SCLK when not used.                                                                                                                                                                                                                                                                                                                   |

| 12  | VDD         | Р                   | Digital power supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 13  | VCM         | I                   | Input from ADC to control main output common mode (CM) voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 14  | -OUT        | 0                   | Main negative output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 15  | +OUT        | 0                   | Main positive output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 16  | VCM_AUX     | I                   | Input to control auxiliary output CM voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Pad | Thermal Pad | _                   | Thermal pad (WQFN heat sink), electrically connected to pins 5 and 8 (GND)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

(1) G = ground, I = input, O = output, P = power

### 5 Specifications

### 5.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                  |                                                    |                               | MIN | MAX  | UNIT    |

|------------------|----------------------------------------------------|-------------------------------|-----|------|---------|

| V <sub>CC</sub>  | Analog supply voltage (5 V nominal)                |                               |     | 5.5  | V       |

| $V_{DD}$         | Digital supply voltage (3.3 V nominal              | )                             |     | 3.6  | V       |

|                  | Differential input signal voltage                  |                               |     | ±1   | V       |

|                  | Maximum dc output value <sup>(2)</sup>             |                               |     | 1700 | $mV_PP$ |

|                  | Input common mode voltage                          |                               | 1   | 4    | V       |

|                  | V <sub>CM</sub> and V <sub>CM_Aux</sub>            |                               |     | 2    | V       |

|                  | V <sub>CM</sub> and V <sub>CM_Aux</sub> SPI inputs |                               |     | 3.6  | V       |

|                  | Soldering temperature                              | Infrared or convention (20 s) |     | 235  | °C      |

|                  | Soldering temperature                              | Wave (10 s)                   |     | 260  | C       |

| TJ               | Junction temperature                               |                               |     | 150  | °C      |

| T <sub>stg</sub> | Storage temperature                                |                               | -65 | 150  | °C      |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

### 5.2 ESD Ratings

|                    |  |                                                                                | VALUE | UNIT |

|--------------------|--|--------------------------------------------------------------------------------|-------|------|

|                    |  | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±2000 |      |

| V <sub>(ESD)</sub> |  | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> |       | V    |

|                    |  | Machine model (MM)                                                             | ±200  |      |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

# 5.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                 |                        | MIN | NOM MAX | UNIT |

|-----------------|------------------------|-----|---------|------|

| V <sub>CC</sub> | Analog supply voltage  |     | 5 ±5%   | V    |

| $V_{DD}$        | Digital supply voltage |     | 3.3 ±5% | V    |

| T <sub>A</sub>  | Ambient temperature    | -40 | 85      | °C   |

### 5.4 Thermal Information

|                       |                                              | LMH6518    |      |

|-----------------------|----------------------------------------------|------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | RGH (WQFN) | UNIT |

|                       |                                              | 16 PINS    |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 40         | °C/W |

| R <sub>θJC(top)</sub> | Junction-to-case (top) thermal resistance    | 31.7       | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 11.5       | °C/W |

| ΨЈТ                   | Junction-to-top characterization parameter   | 0.3        | °C/W |

| ΨЈВ                   | Junction-to-board characterization parameter | 11.5       | °C/W |

| R <sub>θJC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 3.4        | °C/W |

(1) For information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

Product Folder Links: LMH6518

*資料に関するフィードバック (ご意見やお問い合わせ) を送信* Copyright © 2024 Te:

English Data Sheet: SNOSB21

<sup>(2)</sup> When the LMH6518 output is held at saturation conditions for long time periods the part can develop a permanent output offset voltage. To manage this output offset condition the device attenuation must be set properly to avoid long periods of output saturation.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

#### 5.5 Electrical Characteristics

Unless otherwise noted, all limits are specified at  $T_A$  = 25°C, input CM = 2.5 V,  $V_{CM}$  = 1.2 V,  $V_{CM\_Aux}$  = 1.2 V, single-ended input drive,  $V_{CC}$  = 5 V,  $V_{DD}$  = 3.3 V,  $R_L$  = 100-Ω differential (both main and auxiliary outputs),  $V_{OUT}$  = 0.7  $V_{PP}$  differential (both main and auxiliary outputs), both main and auxiliary output specifications, full bandwidth setting, gain = 18.8 dB (preamp LG, 0-dB ladder attenuation), and full power setting (with auxiliary output turned on) (see  $\frac{1}{8}$  8-1 for abbreviations used). (1)

|                    | PARAMETER                                      | TEST CONDITIONS                                                            | MIN <sup>(2)</sup> TYP <sup>(3)</sup> MAX | (2) UNIT          |

|--------------------|------------------------------------------------|----------------------------------------------------------------------------|-------------------------------------------|-------------------|

| DYNAMIC PE         | RFORMANCE                                      |                                                                            |                                           |                   |

| LSBW               | -3-dB bandwidth                                | All gains                                                                  | 900                                       | MHz               |

|                    | Peaking                                        | All gains                                                                  | 1                                         | dB                |

| GF_0.1 dB          | ±0.1-dB gain flatness                          | All gains                                                                  | 150                                       | MHz               |

| GF_1 dB            | ±1-dB gain flatness                            | All gains                                                                  | 400                                       | MHz               |

| TRS                | Rise time                                      |                                                                            | 460                                       | ps                |

| TRL                | Fall time                                      |                                                                            | 450                                       |                   |

| OS                 | Overshoot                                      | Main output                                                                | 9%                                        |                   |

| t <sub>s_1</sub>   | Settling time                                  | Main output, ±0.5%                                                         | 10                                        | ns                |

| t <sub>s_2</sub>   | Settling time                                  | Main output, ±0.05%                                                        | 14                                        |                   |

| t_recover          | Recovery time <sup>(4)</sup>                   | All gains                                                                  | <5                                        | ns                |

| $P_D$              | Propagation delay                              | V <sub>OUT</sub> = 0.7 V <sub>PP</sub> , all gains                         | 1.2                                       | ns                |

| P <sub>D_VAR</sub> | Propagation delay variation                    | Gain varied                                                                | 100                                       | ps                |

|                    | ORTION, AND RF SPECIFICAT                      | ONS                                                                        |                                           |                   |

| e <sub>n_1</sub>   | Input noise spectral density                   | Max gain, 10 MHz                                                           | 0.98                                      | nV/√ Hz           |

| e <sub>n_2</sub>   | Input noise spectral density                   | Preamp LG and 0-dB ladder,<br>10 MHz                                       | 4.1                                       | nV/√ Hz           |

| e <sub>no_1</sub>  | RMS output noise                               | Max gain, 100 Hz to 400 MHz                                                | 1.7                                       | mV                |

| e <sub>no_2</sub>  | RMS output noise                               | Preamp LG, 0-dB ladder,<br>100 Hz to 400 MHz                               | 940                                       | μV                |

| NF_1               | Noise figure                                   | Max gain, $R_S$ = 50 $\Omega$ each input, 10 MHz                           | 3.8                                       | dB                |

| NF_2               | Noise figure                                   | Preamp LG, 0-dB ladder,<br>R <sub>S</sub> = 50 $\Omega$ each input, 10 MHz | 13.5                                      | dB                |

| HD2_1              | 2nd harmonic distortion <sup>(5)</sup>         | Main output, 100 MHz, all gains                                            | -50                                       | dBc               |

| HD3_1              | 3rd harmonic distortion <sup>(5)</sup>         | Main output, 100 MHz, all gains                                            | -53                                       | dBc               |

| HD2_2              | 2nd harmonic distortion <sup>(5)</sup>         | Auxiliary output, 100 MHz, all gains                                       | -48                                       | dBc               |

| HD3_2              | 3rd harmonic distortion <sup>(5)</sup>         | Auxiliary output, 100 MHz, all gains                                       | -50                                       | dBc               |

| HD2_3              | 2nd harmonic distortion <sup>(5)</sup>         | Main output, 250 MHz, all gains                                            | -44                                       | dBc               |

| HD3_3              | 3rd harmonic distortion <sup>(5)</sup>         | Main output, 250 MHz, all gains                                            | -50                                       | dBc               |

| HD2/HD3_4          | 2nd and 3rd harmonic distortion <sup>(5)</sup> | Auxiliary output, 250 MHz, all gains                                       | -42                                       | dBc               |

| IMD3               | Intermodulation distortion <sup>(5)</sup>      | f = 250 MHz, main output                                                   | -65                                       | dBc               |

| OIP3_1             | Intermodulation intercept <sup>(5)</sup>       | Main output, 250 MHz                                                       | 26                                        | dBm               |

|                    | 4 dD                                           | Main output, 250 MHz, 0-dB ladder                                          | 1.8                                       | .,                |

| P_1dB_main         | –1-dB compression                              | Main output, 250 MHz, 20-dB ladder                                         | 1                                         | → V <sub>PP</sub> |

| D 44D              | 4.40                                           | Auxiliary output, 250 MHz, 0-dB ladder                                     | 1.65                                      | .,                |

| P_1dB_aux          | -1-dB compression                              | Auxiliary output, 250 MHz,<br>20-dB ladder                                 | 1                                         | — V <sub>PP</sub> |

# 5.5 Electrical Characteristics (続き)

Unless otherwise noted, all limits are specified at  $T_A$  = 25°C, input CM = 2.5 V,  $V_{CM}$  = 1.2 V,  $V_{CM\_Aux}$  = 1.2 V, single-ended input drive,  $V_{CC}$  = 5 V,  $V_{DD}$  = 3.3 V,  $R_L$  = 100-Ω differential (both main and auxiliary outputs),  $V_{OUT}$  = 0.7  $V_{PP}$  differential (both main and auxiliary outputs), both main and auxiliary output specifications, full bandwidth setting, gain = 18.8 dB (preamp LG, 0-dB ladder attenuation), and full power setting (with auxiliary output turned on) (see  $\frac{1}{8}$  8-1 for abbreviations used). (1)

|                                           | PARAMETER                                       | TEST CONDITIONS                                         | MIN <sup>(2)</sup>     | TYP <sup>(3)</sup> | MAX <sup>(2)</sup> | UNIT      |

|-------------------------------------------|-------------------------------------------------|---------------------------------------------------------|------------------------|--------------------|--------------------|-----------|

| GAIN PARAM                                | ETERS                                           |                                                         |                        |                    |                    |           |

| A <sub>V_DIFF_MAX</sub>                   | Maximum gain                                    |                                                         | 38.1                   | 38.8               | 39.5               | dB        |

| A <sub>V_DIFF_MIN</sub>                   | Minimum gain                                    |                                                         | -1.91                  | -1.16              | -0.4               | dB        |

|                                           | Gain step size                                  | All gains including preamp step                         | 1.8                    | 2                  | 2.2                | dB        |

| Gain_Step                                 | Gain step size with ADC (see セクション 7)           | ADC FS adjusted                                         |                        | 8.5                |                    | mdB       |

| Gain_Range                                | Gain range                                      |                                                         | 39                     | 40                 | 41                 | dB        |

| TC_A <sub>V_DIFF</sub>                    | Gain temp coefficient <sup>(6)</sup>            | All gains                                               |                        | -0.8               |                    | mdB/°C    |

| Gain_A <sub>CC</sub>                      | Absolute gain accuracy                          | Compared to theoretical from max gain in 2-dB steps     | 0.75                   |                    | 0.75               | dB        |

| MATCHING                                  |                                                 |                                                         |                        |                    |                    |           |

| Gain_match                                | Gain matching,<br>main and auxiliary            | All gains                                               |                        | ±0.1               | ±0.2               | dB        |

| BW_match                                  | –3-dB bandwidth matching,<br>main and auxiliary | All gains                                               |                        | 5%                 |                    |           |

| RT_match                                  | Rise time matching, main and auxiliary          | All gains                                               |                        | 5%                 |                    |           |

| PD_match                                  | Propagation delay matching, main and auxiliary  | All gains                                               |                        | 100                |                    | ps        |

| ANALOG I/O                                |                                                 |                                                         |                        |                    |                    |           |

| CMRR_1                                    | CM rejection ratio (see 表 8-1)                  | Preamp HG, 0-dB ladder,<br>1.9 V < CMVR < 3.1 V         | 45                     | 86                 |                    | dB        |

| CMRR_2                                    | CM rejection ratio (see 表 8-1)                  | Preamp LG, 0-dB ladder,<br>1.9 V < CMVR < 3.1 V         | 40                     | 55                 |                    | dB        |

| CMVR_1                                    | Input common-mode voltage                       | Preamp HG, all ladder steps,<br>CMRR ≥ 45 dB            | 1.9                    |                    | 3.1                | V         |

| CMVR_2                                    | Input common-mode voltage                       | Preamp LG, all ladder steps,<br>CMRR ≥ 40 dB            | 1.9                    |                    | 3.1                | V         |

| ΔV <sub>O_CM</sub>  <br>Δ <sub>I_CM</sub> |                                                 | All gains, 2 V < CMVR < 3 V                             | -60                    | -100               |                    | dB        |

| CMRR_CM                                   | CM rejection ratio relative to VCM (see 表 8-1)  | Preamp LG, 0 dB                                         |                        | 101                |                    | dB        |

| $Z_{in\_diff}$                            | Differential input impedance                    | All gains                                               |                        | 150    1.5         |                    | kΩ    pF  |

| Z <sub>in_CM</sub>                        | CM input impedance                              | Preamp HG                                               |                        | 420    1.7         |                    | kΩ    pF  |

| ←in_CM                                    | OW Input Impedance                              | Preamp LG                                               |                        | 900    1.7         |                    | K32    Pi |

| FS <sub>OUT1</sub>                        | Full scale voltage swing                        | Main output, all gains,<br>THD at 100 MHz ≤ –40 dBc     | 770 <sup>(7)</sup>     | 800                |                    | $mV_{PP}$ |

| FS <sub>OUT2</sub>                        | Full scale voltage swing                        | Main output, clamped, 0-dB ladder                       |                        | 1800               | 1960               | $mV_PP$   |

| FS <sub>OUT3</sub>                        | Full scale voltage swing                        | Auxiliary output, all gains<br>THD at 100 MHz ≤ –40 dBc | 770 <sup>(7)</sup> 800 |                    |                    | $mV_{PP}$ |

| FS <sub>OUT4</sub>                        | Full scale voltage swing                        | Auxiliary output, clamped, 0-dB ladder                  |                        | 1600               | 1760               | $mV_{PP}$ |

| V <sub>OUT_MAX1</sub>                     | Voltage at each output pin (clamped)            | Main output, all gains, V <sub>CM</sub> = 1.2 V         | 0.5                    |                    | 1.8                | V         |

| V <sub>OUT_MAX2</sub>                     | Voltage at each output pin (clamped)            | Auxiliary output, all gains,<br>V <sub>CM</sub> = 1.2 V | 0.8                    |                    | 2.2                | V         |

Copyright © 2024 Texas Instruments Incorporated

# 5.5 Electrical Characteristics (続き)

Unless otherwise noted, all limits are specified at  $T_A$  = 25°C, input CM = 2.5 V,  $V_{CM}$  = 1.2 V,  $V_{CM\_Aux}$  = 1.2 V, single-ended input drive,  $V_{CC}$  = 5 V,  $V_{DD}$  = 3.3 V,  $R_L$  = 100-Ω differential (both main and auxiliary outputs),  $V_{OUT}$  = 0.7  $V_{PP}$  differential (both main and auxiliary outputs), both main and auxiliary output specifications, full bandwidth setting, gain = 18.8 dB (preamp LG, 0-dB ladder attenuation), and full power setting (with auxiliary output turned on) (see  $\frac{1}{8}$  8-1 for abbreviations used).<sup>(1)</sup>

|                         | PARAMETER                                             | TES                                           | T CONDITIONS                                        | MIN <sup>(2)</sup>    | TYP <sup>(3)</sup> | MAX <sup>(2)</sup> | UNIT  |

|-------------------------|-------------------------------------------------------|-----------------------------------------------|-----------------------------------------------------|-----------------------|--------------------|--------------------|-------|

| V <sub>OUT_MAX3</sub>   | Voltage at each output pin (clamped)                  | Main output, all                              | gains, V <sub>CM</sub> = 1.45 V                     |                       |                    | 2.05               | V     |

| V <sub>OUT_MAX4</sub>   | Voltage at each output pin (clamped)                  | Auxiliary output,<br>V <sub>CM</sub> = 1.45 V | , all gains,                                        |                       |                    | 2.45               | V     |

| Z <sub>OUT_DIFF</sub>   | Differential output impedance                         | All gains                                     |                                                     | 92                    | 100                | 108                | Ω     |

| V <sub>oos</sub>        | Output offset voltage                                 | All gains                                     |                                                     |                       | ±15                | ±40                | mV    |

| V <sub>OOS_shift1</sub> | Output offset voltage shift                           | Preamp LG to p                                | reamp HG                                            |                       | 13.7               |                    | mV    |

| V <sub>OOS_shift2</sub> | Output offset voltage shift                           | All gains, exclud                             | ding preamp step                                    |                       | 12.7               |                    | mV    |

| TCV <sub>OOS</sub>      | Output offset voltage drift <sup>(6)</sup>            | Preamp HG, 0-c                                | dB ladder                                           |                       | -24                |                    | μV/°C |

| 10v <sub>00S</sub>      | Output offset voltage drift(*)                        | Preamp LG, 0-d                                | Preamp LG, 0-dB ladder                              |                       | -7                 |                    | μν/ С |

| 1                       | Input bias current <sup>(8)</sup>                     | $T_A = -40^{\circ}C \text{ to } +$            | 85°C                                                |                       | 40                 | 100                |       |

| I <sub>B</sub>          | input bias current(9)                                 | $T_A = -65^{\circ}C \text{ to } +$            | 150°C                                               |                       |                    | 140                | μA    |

| V                       | Outrot CM valtage                                     | All mains                                     | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$       |                       | 1.2                |                    | V     |

| V <sub>OCM</sub>        | Output CM voltage                                     | All gains                                     | $T_A = -65^{\circ}C \text{ to } +150^{\circ}C$      | 0.95                  |                    | 1.45               | V     |

| V <sub>OS_CM</sub>      | Output CM offset                                      | All gains                                     | -                                                   |                       | ±15                | ±30                | mV    |

| TC_V <sub>OS_CM</sub>   | CM offset voltage temperature coefficient             | All gains                                     |                                                     |                       | +55                |                    | μV/°C |

| BAL_Error_DC            | Output gain balance error                             | DC, $\frac{\Delta V_{O\_CM}}{\Delta V_{OUT}}$ |                                                     |                       | -78                |                    | dB    |

| BAL_Error_AC            | Output gain balance error                             | 250 MHz, Vo_cm<br>Vout                        |                                                     |                       | -45                |                    | dB    |

| РВ                      | Phase balance error (see 表<br>8-1)                    | 250 MHz                                       | 250 MHz                                             |                       | ±0.8               |                    | deg   |

| DCDD                    | Differential power-supply                             | Preamp HG, 0-0                                | dB ladder                                           | -60                   | -87                |                    | 40    |

| PSRR                    | rejection (see 表 8-1)                                 | Preamp LG, 0-dB ladder                        |                                                     | -50                   | -70                |                    | dB    |

| PSRR_CM                 | CM power-supply rejection (see 表 8-1)                 | Preamp LG, 0-d                                | IB ladder                                           | -55                   | -71                |                    | dB    |

|                         |                                                       |                                               | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$       |                       | ±1                 | ±10                |       |

| $V_{CM\_I}$             | V <sub>CM</sub> input bias current <sup>(8)</sup>     | All gains                                     | $T_A = -65^{\circ}C \text{ to } +150^{\circ}C$      |                       |                    | ±20                | nA    |

|                         | 1/2                                                   | A.U                                           | $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$ |                       | ±1                 | ±10                | A     |

| $V_{CM\_AUX\_I}$        | V <sub>CM_AUX</sub> input bias current <sup>(8)</sup> | All gains                                     | $T_A = -65^{\circ}C \text{ to } +150^{\circ}C$      |                       |                    | ±20                | nA    |

| DIGITAL I/O             |                                                       | -1                                            |                                                     | ,                     | ,                  |                    |       |

| V <sub>IH</sub>         | Input logic high                                      | $T_A = -65^{\circ}C \text{ to +}$             | 150°C                                               | V <sub>DD</sub> - 0.6 |                    |                    | V     |

| V <sub>IL</sub>         | Input logic low                                       | T <sub>A</sub> = -65°C to +150°C              |                                                     |                       |                    | 0.5                | V     |

| V <sub>OH</sub>         | Output logic high                                     |                                               |                                                     |                       | $V_{DD}$           |                    | V     |

| V <sub>OL</sub>         | Output logic low                                      |                                               |                                                     |                       | 0                  |                    | V     |

| R <sub>Hi_Z</sub>       | Output resistance                                     | High-impedance mode                           |                                                     |                       | 5                  |                    | ΜΩ    |

| <br>I_in                | Input bias current                                    |                                               |                                                     |                       | <1                 |                    | μA    |

| F <sub>SCLK</sub>       | SCLK rate                                             |                                               |                                                     |                       |                    | 10                 | MHz   |

| F <sub>SCLK_DT</sub>    | SCLK duty cycle                                       |                                               |                                                     | 45%                   | 50%                | 55%                |       |

# 5.5 Electrical Characteristics (続き)

Unless otherwise noted, all limits are specified at  $T_A$  = 25°C, input CM = 2.5 V,  $V_{CM}$  = 1.2 V,  $V_{CM\_Aux}$  = 1.2 V, single-ended input drive,  $V_{CC}$  = 5 V,  $V_{DD}$  = 3.3 V,  $R_L$  = 100- $\Omega$  differential (both main and auxiliary outputs),  $V_{OUT}$  = 0.7  $V_{PP}$  differential (both main and auxiliary outputs), both main and auxiliary output specifications, full bandwidth setting, gain = 18.8 dB (preamp LG, 0-dB ladder attenuation), and full power setting (with auxiliary output turned on) (see  $\frac{1}{2}$  8-1 for abbreviations used).

|                     | PARAMETER                               | TES                                | T CONDITIONS | MIN <sup>(2)</sup> | TYP <sup>(3)</sup> | MAX <sup>(2)</sup> | UNIT |

|---------------------|-----------------------------------------|------------------------------------|--------------|--------------------|--------------------|--------------------|------|

| POWER R             | REQUIREMENTS                            | '                                  |              |                    |                    |                    |      |

|                     | Complex compant V                       | $T_A = -40$ °C to +                | +85°C        | 195                | 210                | 225                | Л    |

| I <sub>S1</sub>     | Supply current, V <sub>CC</sub>         | $T_A = -65^{\circ}C \text{ to } +$ | +150°C       |                    |                    | 230                | mA   |

| ı                   | Cupply ourrent \/ aux off               | $T_A = -40^{\circ}C \text{ to } +$ | +85°C        |                    | 150                | 165                | mA   |

| I <sub>S1_off</sub> | Supply current, V <sub>CC</sub> aux off | $T_A = -65^{\circ}C \text{ to } +$ | +150°C       |                    |                    | 170                | ША   |

|                     | Supply surrent V                        | $T_A = -40^{\circ}C \text{ to } +$ | +85°C        |                    | 180                | 350                |      |

| I <sub>DD</sub>     | Supply current, V <sub>DD</sub>         | T <sub>A</sub> = -65°C to 150°C    |              |                    |                    | 400                | μA   |

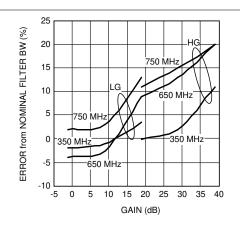

| BANDWID             | OTH LIMITING FILTER SPECIFICAT          | TONS                               |              | 1                  |                    | '                  |      |

|                     |                                         |                                    | 20 MHz       | 0%                 | 20%                |                    |      |

|                     |                                         |                                    | 100 MHz      | 0%                 | 20%                |                    |      |

|                     |                                         | All going                          | 200 MHz      | 0%                 | 20%                |                    |      |

|                     |                                         | All gains                          | 350 MHz      |                    | ±25%               |                    |      |

|                     | Pass band tolerance,  –3 dB bandwidth   |                                    | 650 MHz      |                    | ±25%               |                    |      |

|                     |                                         |                                    | 750 MHz      |                    | ±25%               |                    |      |

|                     |                                         | Preamp LG,<br>0-dB ladder          | 350 MHz      |                    | ±10%               |                    |      |

|                     |                                         |                                    | 650 MHz      |                    | ±10%               |                    |      |

|                     |                                         | a second                           | 750 MHz      |                    | ±10%               |                    |      |

- (1) Electrical Characteristics table values apply only for factory testing conditions at the temperature indicated. Factory testing conditions result in limited self-heating of the device such that T<sub>J</sub> = T<sub>A</sub>. No specification of parametric performance is indicated in the electrical tables under conditions of internal self-heating where T<sub>J</sub> > T<sub>A</sub>.

- (2) Limits are 100% production tested at 25°C unless otherwise specified. Limits over the operating temperature range are specified through correlation using Statistical Quality Control (SQC) methods.

- (3) Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values can vary over time and also depends on the application and configuration. The typical values are not tested and are not specified on shipped production material.

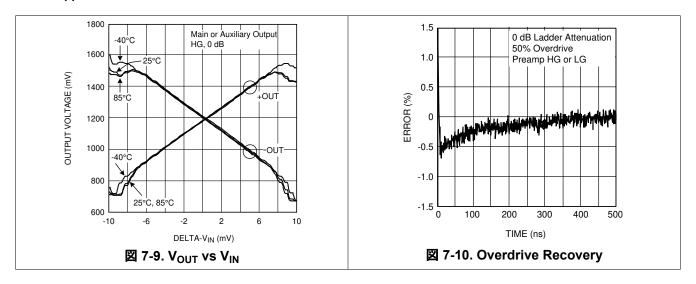

- (4) Recovery time is the slower of the main and auxiliary outputs. Output swing of 700 mV<sub>PP</sub> shifted up or down by 50% (0.35 V) by introducing an offset. Measured values correspond to the time required to return to within ±1% of 0.7 V<sub>PP</sub> (±7 mV).

- (5) Distortion data taken under single ended input condition.

- (6) Drift determined by dividing the change in parameter at temperature extremes by the total temperature change.

- (7) Specified by design.

- (8) Positive current is current flowing into the device.

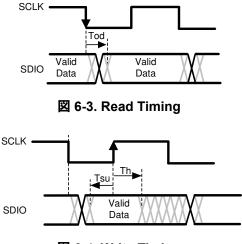

### 5.6 Timing Requirements

|                  |                                                                   | MIN | NOM | MAX | UNIT        |

|------------------|-------------------------------------------------------------------|-----|-----|-----|-------------|

| t <sub>S</sub>   | SDIO setup time                                                   | 25  |     |     | ns          |

| t <sub>H</sub>   | SDIO hold time                                                    | 25  |     |     | ns          |

| t <sub>CES</sub> | CS enable setup time (from CS asserted to rising edge of SCLK)    | 25  |     |     | ns          |

| t <sub>CDS</sub> | CS disable setup time (from CS deasserted to rising edge of SCLK) | 25  |     |     | ns          |

| t <sub>IAG</sub> | Inter-access gap                                                  | 3   |     |     | SCLK cycles |

Product Folder Links: LMH6518

資料に関するフィードバック(ご意見やお問い合わせ) を送信

Copyright © 2024 Texas Instruments Incorporated

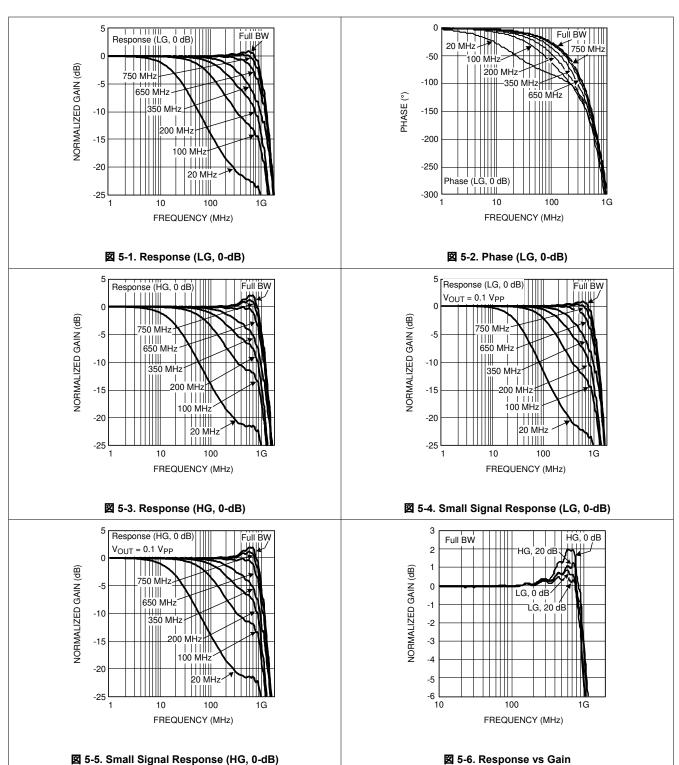

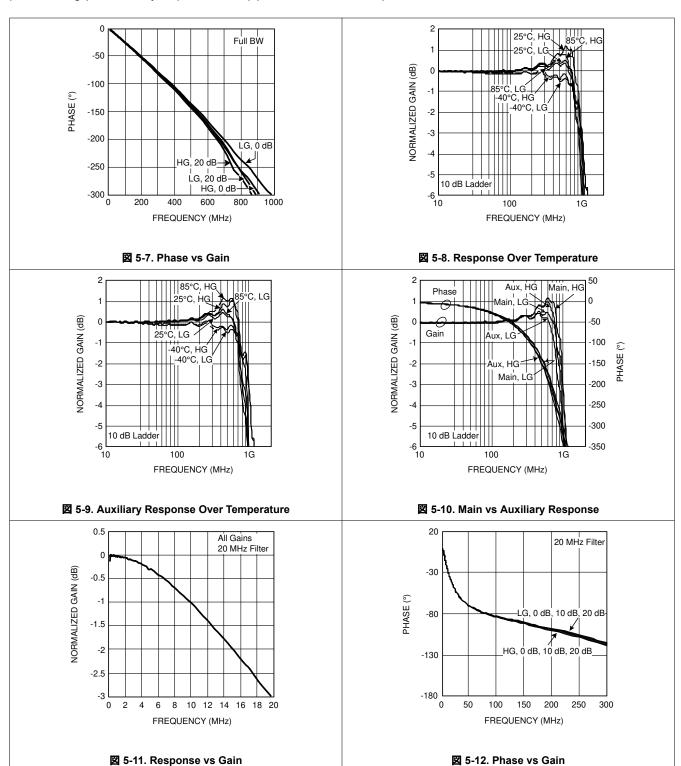

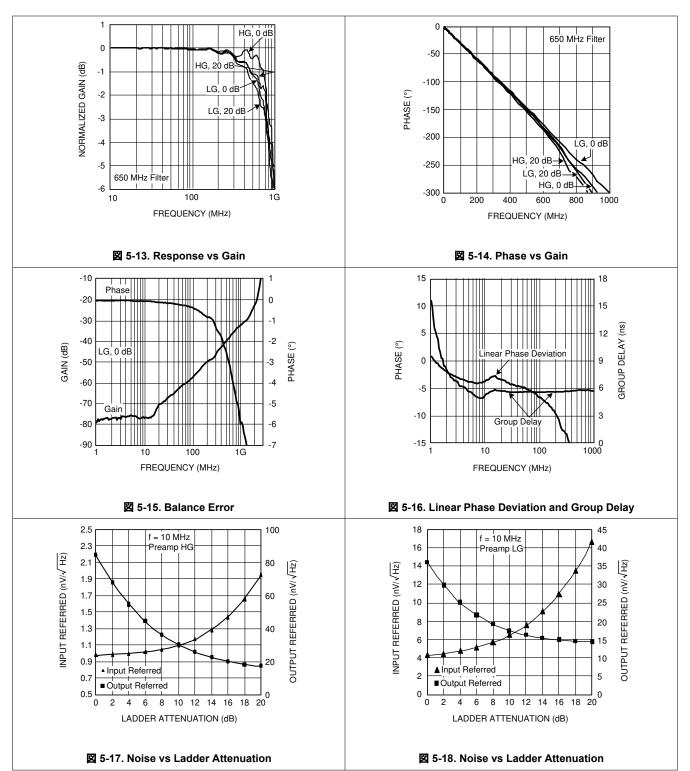

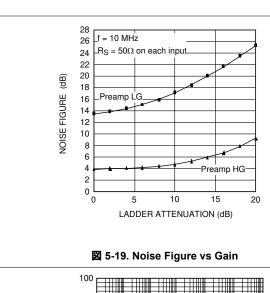

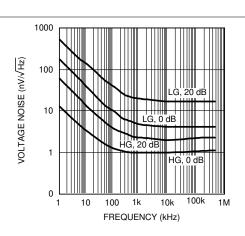

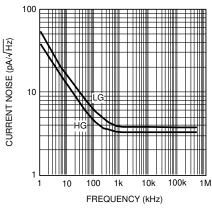

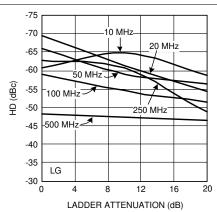

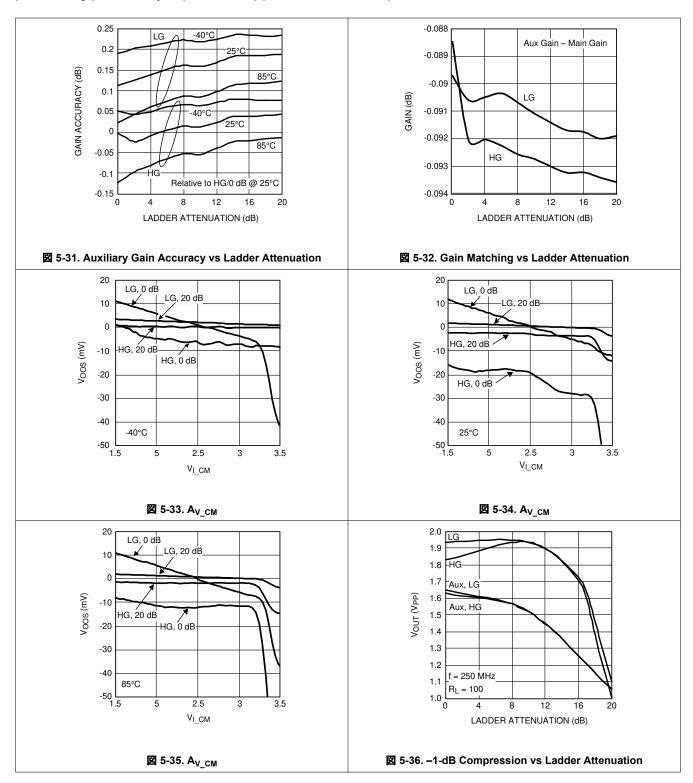

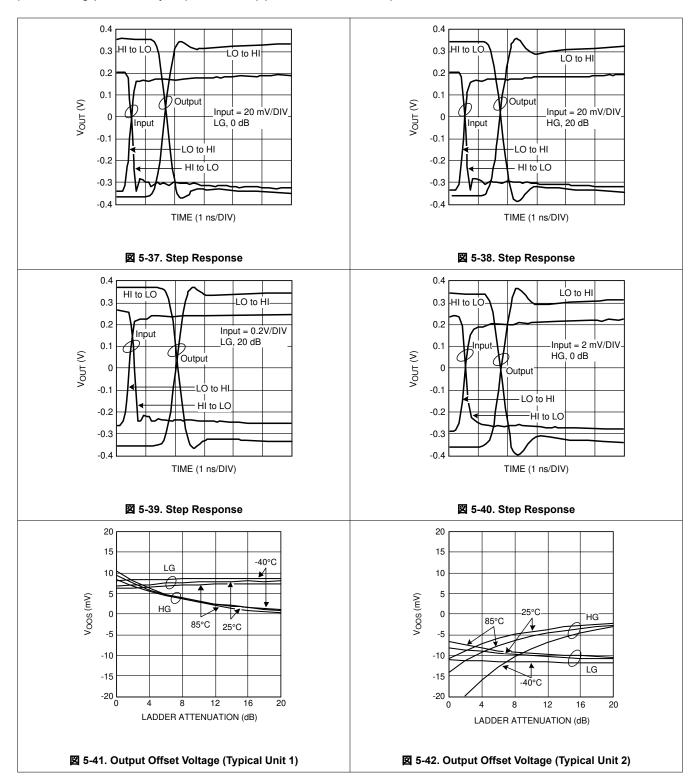

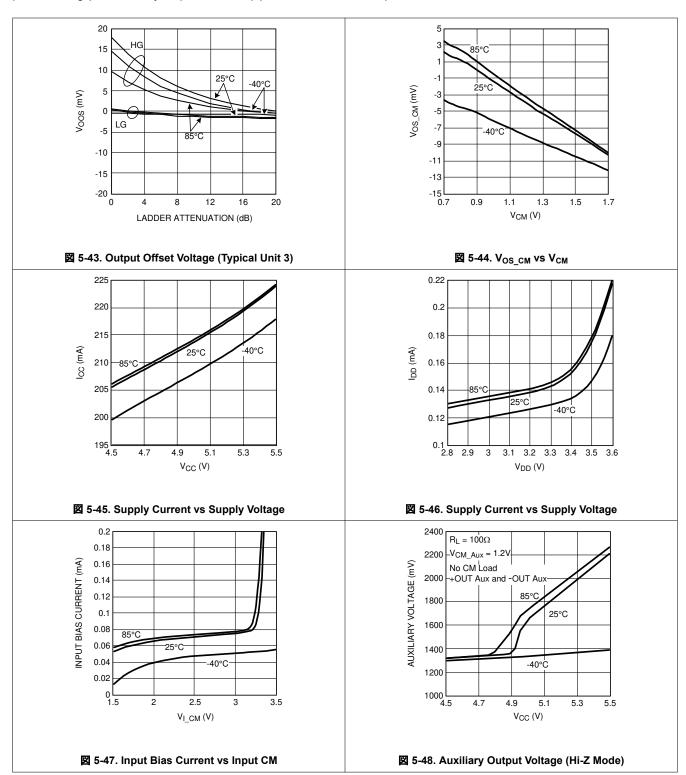

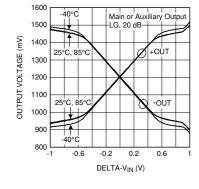

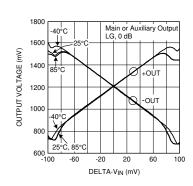

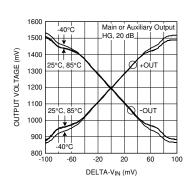

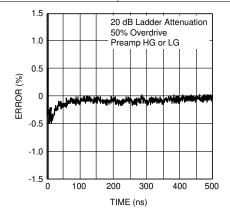

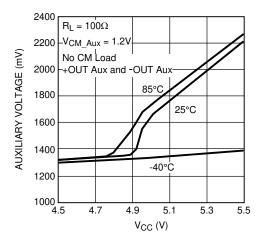

### 5.7 Typical Characteristics

at input CM = 2.5-V,  $V_{CM}$  = 1.2-V,  $V_{CM AUX}$  = 1.2-V, single-ended input drive,  $V_{CC}$  = 5-V,  $V_{DD}$  = 3.3-V,  $V_{CM AUX}$  = 1.2-V, single-ended input drive,  $V_{CC}$  = 5-V,  $V_{DD}$  = 3.3-V,  $V_{CM AUX}$  = 100  $V_{CM AUX}$  differential (both main and auxiliary outputs),  $V_{CUT}$  = 0.7  $V_{PP}$  differential (both main and auxiliary outputs), main output specification (auxiliary is labeled), full bandwidth setting, gain = 18.8-dB (preamp LG, 0-dB ladder attenuation), and full power setting (with auxiliary output turned on) (unless otherwise noted)

at input CM = 2.5-V,  $V_{CM}$  = 1.2-V,  $V_{CM AUX}$  = 1.2-V, single-ended input drive,  $V_{CC}$  = 5-V,  $V_{DD}$  = 3.3-V,  $R_L$  = 100  $\Omega$  differential (both main and auxiliary outputs),  $V_{OUT}$  = 0.7  $V_{PP}$  differential (both main and auxiliary outputs), main output specification (auxiliary is labeled), full bandwidth setting, gain = 18.8-dB (preamp LG, 0-dB ladder attenuation), and full power setting (with auxiliary output turned on) (unless otherwise noted)

Copyright © 2024 Texas Instruments Incorporated

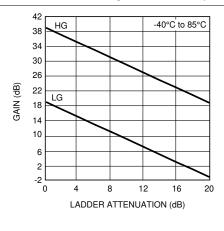

at input CM = 2.5-V,  $V_{CM}$  = 1.2-V,  $V_{CM AUX}$  = 1.2-V, single-ended input drive,  $V_{CC}$  = 5-V,  $V_{DD}$  = 3.3-V,  $R_L$  = 100  $\Omega$  differential (both main and auxiliary outputs),  $V_{OUT}$  = 0.7  $V_{PP}$  differential (both main and auxiliary outputs), main output specification (auxiliary is labeled), full bandwidth setting, gain = 18.8-dB (preamp LG, 0-dB ladder attenuation), and full power setting (with auxiliary output turned on) (unless otherwise noted)

English Data Sheet: SNOSB21

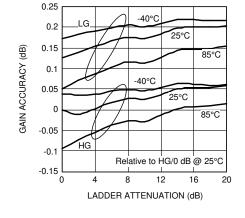

at input CM = 2.5-V,  $V_{CM}$  = 1.2-V,  $V_{CM AUX}$  = 1.2-V, single-ended input drive,  $V_{CC}$  = 5-V,  $V_{DD}$  = 3.3-V,  $R_L$  = 100  $\Omega$  differential (both main and auxiliary outputs),  $V_{OUT}$  = 0.7  $V_{PP}$  differential (both main and auxiliary outputs), main output specification (auxiliary is labeled), full bandwidth setting, gain = 18.8-dB (preamp LG, 0-dB ladder attenuation), and full power setting (with auxiliary output turned on) (unless otherwise noted)

図 5-20. Input Voltage Noise vs Frequency

図 5-21. Input Current Noise vs Frequency

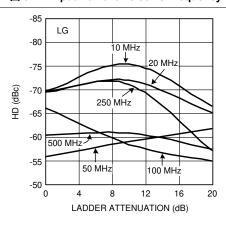

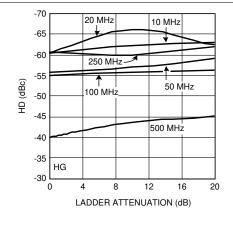

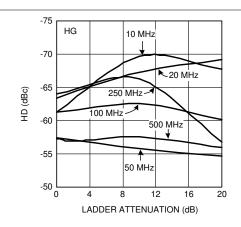

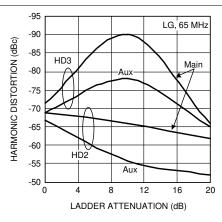

図 5-22. HD2 vs Ladder Attenuation

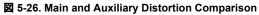

図 5-23. HD3 vs Ladder Attenuation 図 5-24. HD2 vs Ladder Attenuation

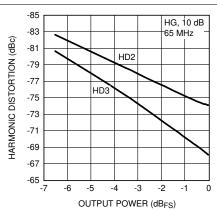

at input CM = 2.5-V,  $V_{CM}$  = 1.2-V,  $V_{CM AUX}$  = 1.2-V, single-ended input drive,  $V_{CC}$  = 5-V,  $V_{DD}$  = 3.3-V,  $R_L = 100 \Omega$  differential (both main and auxiliary outputs),  $V_{OUT} = 0.7 V_{PP}$  differential (both main and auxiliary outputs), main output specification (auxiliary is labeled), full bandwidth setting, gain = 18.8-dB (preamp LG, 0-dB ladder attenuation), and full power setting (with auxiliary output turned on) (unless otherwise noted)

Product Folder Links: LMH6518

HG, 65 MHz -80 HARMONIC DISTORTION (dBc) HD2 -75 -70 -65 HD3 Aux -60 -55 -50 0 8 12 16 20 LADDER ATTENUATION (dB)

図 5-27. Main and Auxiliary Distortion Comparison

図 5-28. Distortion vs Output Power

☑ 5-29. Gain vs Ladder Attenuation

☑ 5-30. Gain Accuracy vs Ladder Attenuation

13

English Data Sheet: SNOSB21

at input CM = 2.5-V,  $V_{CM}$  = 1.2-V,  $V_{CM AUX}$  = 1.2-V, single-ended input drive,  $V_{CC}$  = 5-V,  $V_{DD}$  = 3.3-V,  $R_L$  = 100  $\Omega$  differential (both main and auxiliary outputs),  $V_{OUT}$  = 0.7  $V_{PP}$  differential (both main and auxiliary outputs), main output specification (auxiliary is labeled), full bandwidth setting, gain = 18.8-dB (preamp LG, 0-dB ladder attenuation), and full power setting (with auxiliary output turned on) (unless otherwise noted)

at input CM = 2.5-V,  $V_{CM}$  = 1.2-V,  $V_{CM AUX}$  = 1.2-V, single-ended input drive,  $V_{CC}$  = 5-V,  $V_{DD}$  = 3.3-V,  $V_{CM AUX}$  = 1.00  $V_{CM AUX}$  = 1.2-V, single-ended input drive,  $V_{CC}$  = 5-V,  $V_{DD}$  = 3.3-V,  $V_{CM AUX}$  = 1.00  $V_{CM AUX}$  = 1.2-V, single-ended input drive,  $V_{CC}$  = 5-V,  $V_{DD}$  = 3.3-V,  $V_{CM AUX}$  = 1.2-V, single-ended input drive,  $V_{CC}$  = 5-V,  $V_{DD}$  = 3.3-V,  $V_{CM AUX}$  = 1.2-V, single-ended input drive,  $V_{CC}$  = 5-V,  $V_{DD}$  = 3.3-V,  $V_{CM AUX}$  = 1.2-V, single-ended input drive,  $V_{CC}$  = 5-V,  $V_{DD}$  = 3.3-V,  $V_{CM AUX}$  = 1.2-V, single-ended input drive,  $V_{CC}$  = 5-V,  $V_{DD}$  = 3.3-V,  $V_{DD$

at input CM = 2.5-V,  $V_{CM}$  = 1.2-V,  $V_{CM AUX}$  = 1.2-V, single-ended input drive,  $V_{CC}$  = 5-V,  $V_{DD}$  = 3.3-V,  $R_L$  = 100  $\Omega$  differential (both main and auxiliary outputs),  $V_{OUT}$  = 0.7  $V_{PP}$  differential (both main and auxiliary outputs), main output specification (auxiliary is labeled), full bandwidth setting, gain = 18.8-dB (preamp LG, 0-dB ladder attenuation), and full power setting (with auxiliary output turned on) (unless otherwise noted)

at input CM = 2.5-V,  $V_{CM}$  = 1.2-V,  $V_{CM AUX}$  = 1.2-V, single-ended input drive,  $V_{CC}$  = 5-V,  $V_{DD}$  = 3.3-V,  $R_L$  = 100  $\Omega$  differential (both main and auxiliary outputs),  $V_{OUT}$  = 0.7  $V_{PP}$  differential (both main and auxiliary outputs), main output specification (auxiliary is labeled), full bandwidth setting, gain = 18.8-dB (preamp LG, 0-dB ladder attenuation), and full power setting (with auxiliary output turned on) (unless otherwise noted)

図 5-49. Filter BW vs Gain

図 5-50. Output vs Input

図 5-51. Output vs Input

図 5-52. Output vs Input

☑ 5-53. Overdrive Recovery Time (Return to Zero)

### 6 Detailed Description

#### 6.1 Overview

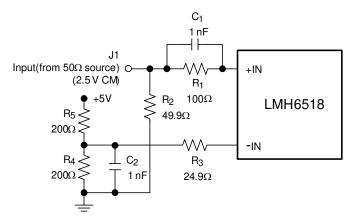

The LMH6518 is a digitally-controlled variable gain amplifier (DVGA) that is designed specifically as an oscilloscope analog front end (AFE). This device samples an analog voltage and conditions the voltage for the analog to digital converter (ADC) input. This device is specifically designed to drive TI's giga sample ADCs that have a  $100-\Omega$  input impedance and  $800 \text{ mV}_{PP}$  full-scale input voltage.

### 6.2 Functional Block Diagram

#### **6.3 Feature Description**

The LMH6518 offers several unique features in addition to being a general purpose digital variable gain amplifier (DVGA).

### 6.3.1 Input Preamplifier

The LMH6518 has a fully differential preamplifier which has a consistent 150-k $\Omega$  impedance across all gain settings. The LMH6518 is also driven with a single-ended signal source. The preamplifier has two gain settings. See  $\frac{1}{2}$  7.2.1.2.2 for details.

#### 6.3.1.1 Primary Output Amplifier

The LMH6518 has two nearly identical amplifiers. The output amplifier was designed as the primary output amplifier. The output amplifier features an internal  $100-\Omega$  termination that interfaces with  $100-\Omega$  input impedance ADCs. The output amplifier has a common-mode voltage control pin that sets the output common-mode voltage of the amplifier.

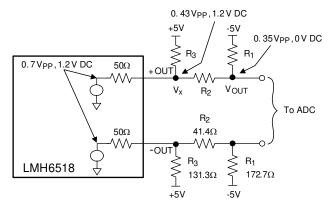

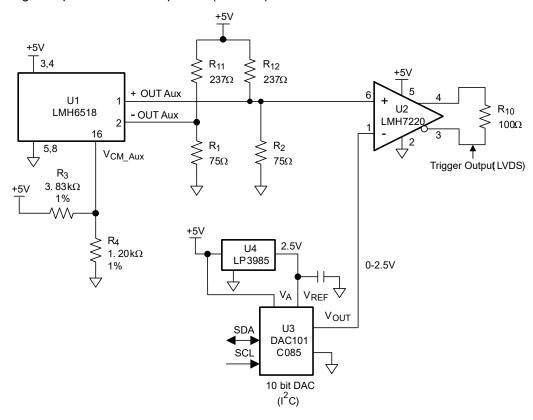

#### 6.3.1.2 Auxiliary Amplifier

The LMH6518 has a second output amplifier that was designed to provide a trigger signal when used as an oscilloscope AFE. The auxiliary amplifier has all of the features of the output amplifier and provides a duplicate signal for use in trigger circuits. The auxiliary amplifier has a common mode voltage control pin which sets the output common mode of the amplifier.

資料に関するフィードバック(ご意見やお問い合わせ)を送信

Copyright © 2024 Texas Instruments Incorporated

### 6.3.2 Overvoltage Clamp

The LMH6518 features two levels of clamps used to protect the amplifier and the ADC from voltage transients. These clamps are placed after the input preamplifier and also after the final output amplifier. The clamp voltages are set by the preamp and ladder attenuator logic functions. The SPI bus is used to set and control the preamp (HG or LG) and ladder attenuator (0-dB to 20-dB, 10 states) logic functions.

#### 6.3.3 Attenuator

The primary gain control feature of the LMH65418 is the digital attenuator. The attenuator controls the overall gain of the amplifier. The attenuator has a range of 0-dB to 20-dB of attenuation.

### 6.3.4 Digital Control Block

The LMH6518 has digitally controlled gain, as well as digitally controlled voltage clamps and digitally controlled bandwidth. If the block is not used, this block can also disable the auxiliary amplifier. セクション 6.5.1 has details on the digital control registers and programming.

#### 6.4 Device Functional Modes

### 6.4.1 Primary Amplifier

The main functional mode of the LMH6518 is as an AFE providing gain, voltage clamping, and frequency limiting. In this mode, the gain, bandwidth, and voltage swing are all programmable using the SPI control block.

### 6.4.2 Auxiliary Output

The secondary functional mode of the LMH6518 is the auxiliary output. This output is nearly identical to the primary amplifier. The only difference is that the auxiliary output has slightly lower distortion performance. The auxiliary output was designed to provide a trigger signal when used as an oscilloscope AFE.

## 6.5 Programming

### 6.5.1 Logic Functions

The following LMH6518 functions are controlled using the SPI-compatible bus:

- Filters (20 MHz, 100 MHz, 200 MHz, 350 MHz, 650 MHz, 750 MHz, or full bandwidth)

- Power mode (full power or auxiliary high impedance, Hi-Z)

- Preamp (HG or LG)

- Attenuation ladder (0 dB to 20 dB, 10 states)

- LMH6518 state write or read back

The SPI bus uses 3.3-V logic. *SDIO* is the serial digital input-output that writes to or reads back from the LMH6518. *SCLK* is the bus clock with chip-select function controlled by  $\overline{CS}$ .

Copyright © 2016, Texas Instruments Incorporated

図 6-1. Serial Interface Protocol, Read Operation

Copyright © 2016, Texas Instruments Incorporated

### 図 6-2. Serial Interface Protocol, Write Operation

図 6-4. Write Timing

Copyright © 2024 Texas Instruments Incorporated

### 表 6-1. Data Field

|              |     |     |     |     |                                |    |           | FILTER |    |                  | PREAMP LADDER ATTENUATI |           |    | JATION |             |

|--------------|-----|-----|-----|-----|--------------------------------|----|-----------|--------|----|------------------|-------------------------|-----------|----|--------|-------------|

| D15<br>(MSB) | D14 | D13 | D12 | D11 | D10                            | D9 | D8        | D7     | D6 | D5               | D4                      | D3        | D2 | D1     | D0<br>(LSB) |

| Х            | 0   | 0   | 0   | 0   | 0 = Full power<br>1 = Aux Hi-Z | 0  | See 表 6-3 |        | 0  | 0 = LG<br>1 = HG |                         | See 表 6-4 |    |        |             |

注

Bits D5, D9, and D11 to D14 must be 0. Otherwise, device operation is undefined and specifications are not valid.

### 表 6-2. Default Power-On Reset Condition

|              |     |     |     |     |     |    | FILTER |    |    | PREAMP | LA | DDER | ATTEN | JATION |             |

|--------------|-----|-----|-----|-----|-----|----|--------|----|----|--------|----|------|-------|--------|-------------|

| D15<br>(MSB) | D14 | D13 | D12 | D11 | D10 | D9 | D8     | D7 | D6 | D5     | D4 | D3   | D2    | D1     | D0<br>(LSB) |

| 0            | 0   | 0   | 0   | 0   | 0   | 0  | 0      | 0  | 0  | 0      | 0  | 1    | 0     | 1      | 0           |

### 表 6-3. Filter Selection Data Field

| 2 C O I I III CO COICCION Data I ICIA |        |                 |                  |  |  |  |  |  |  |

|---------------------------------------|--------|-----------------|------------------|--|--|--|--|--|--|

|                                       | FILTER | BANDWIDTH (MHz) |                  |  |  |  |  |  |  |

| D8                                    | D7     | D6              | BANDWIDTH (WITZ) |  |  |  |  |  |  |

| 0                                     | 0      | 0               | Full             |  |  |  |  |  |  |

| 0                                     | 0      | 1               | 20               |  |  |  |  |  |  |

| 0                                     | 1      | 0               | 100              |  |  |  |  |  |  |

| 0                                     | 1      | 1               | 200              |  |  |  |  |  |  |

| 1                                     | 0      | 0               | 350              |  |  |  |  |  |  |

| 1                                     | 0      | 1               | 650              |  |  |  |  |  |  |

| 1                                     | 1      | 0               | 750              |  |  |  |  |  |  |

| 1                                     | 1      | 1               | Unallowed        |  |  |  |  |  |  |

注

All filters are low-pass, single pole roll-off and operate on both main and auxiliary outputs. These filters are intended as signal path bandwidth and noise limiting.

# 表 6-4. Ladder Attenuation Data Field

|    | BANDWIDTH (dB) |    |    |                |

|----|----------------|----|----|----------------|

| D3 | D2             | D1 | D0 | BANDWIDTH (ub) |

| 0  | 0              | 0  | 0  | 0              |

| 0  | 0              | 0  | 1  | -2             |

| 0  | 0              | 1  | 0  | -4             |

| 0  | 0              | 1  | 1  | -6             |

| 0  | 1              | 0  | 0  | -8             |

| 0  | 1              | 0  | 1  | -10            |

| 0  | 1              | 1  | 0  | -12            |

| 0  | 1              | 1  | 1  | -14            |

| 1  | 0              | 0  | 0  | -16            |

| 1  | 0              | 0  | 1  | -18            |

| 1  | 0              | 1  | 0  | -20            |

| 1  | 0              | 1  | 1  | Unallowed      |

| 1  | 1              | 0  | 0  | Unallowed      |

| 1  | 1              | 0  | 1  | Unallowed      |

| 1  | 1              | 1  | 0  | Unallowed      |

| 1  | 1              | 1  | 1  | Unallowed      |

注

An unallowed SPI state can result in undefined operation where device behavior is not valid.

# 7 Application and Implementation

注

以下のアプリケーション情報は、TIの製品仕様に含まれるものではなく、TIではその正確性または完全性を保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 7.1 Application Information

The LMH6518 device is an excellent choice for applications that require a differential signal path and drive a differential, high-bandwidth analog-to-digital converter. The LMH6581 has 900 MHz of bandwidth and drives signals up to 1.8 V<sub>PP</sub>.

Typical applications for the LMH6518 include an oscilloscope AFE, gain control in a radio receiver, and a data-acquisition system.

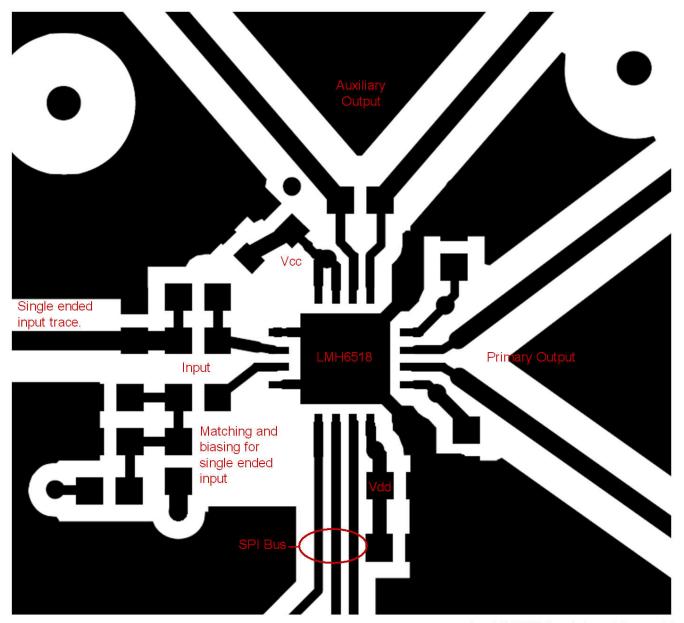

### 7.2 Typical Application

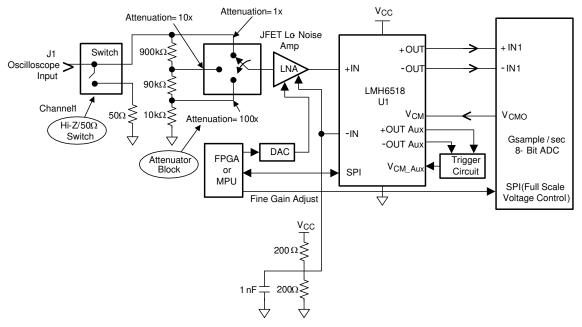

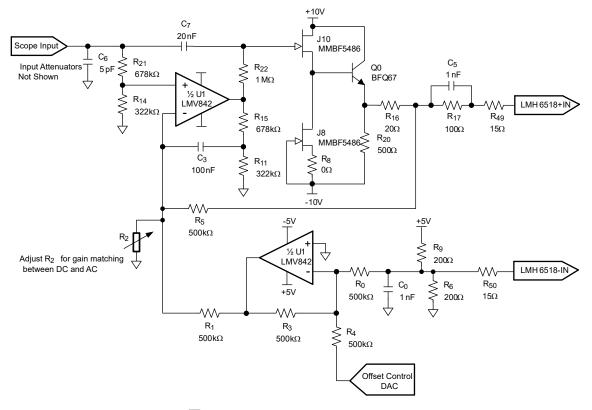

### 7.2.1 Oscilloscope Front End

Copyright © 2016, Texas Instruments Incorporated

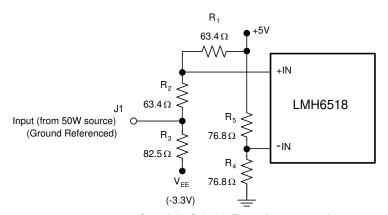

図 7-1. Digital Oscilloscope Front-End

### 7.2.1.1 Design Requirements

An oscilloscope is used to sample signals from millivolts to volts. To make the best use of the limited ADC input range, the oscilloscope input circuitry must have a wide gain range.

Product Folder Links: LMH6518

In this design example, the LMH6518 is driving an ADC12J2700 and has the following requirements:

- Common mode voltage = 1.225-V

- Full scale voltage = 650 mV<sub>PP</sub> to 800 mV<sub>PP</sub>

- Bandwidth = 900-MHz

- Trigger channel

- Spurious free dynamic range = 50-dB

Copyright © 2024 Texas Instruments Incorporated

資料に関するフィードバック(ご意見やお問い合わせ) を送信

23

#### 7.2.1.2 Detailed Design Procedure

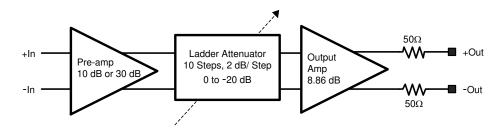

図 7-2. LMH6518 Signal Path Block Diagram

The auxiliary output (not shown) uses another but similar output amplifier that taps into the ladder attenuator output. In this data sheet, preamp gain of 30 dB is referred to as high gain (HG), and preamp gain of 10 dB as low gain (LG).

The LMH6518 2-dB/step gain resolution and 40-dB adjustment range (from −1.16 dB to 38.8 dB). These specifications allow this device to be used with the TI GSPS ADCs, which have full scale (FS) adjustment through the extended control mode (ECM) to provide near-continuous variability (8.5-mdB resolution) that covers 42.6-dB FS input range using 式 1.

$$(20 \times \log \frac{920 \text{ mV}_{PP}}{6.8 \text{ mV}_{PP}} = 42.6 \text{ dB})$$

(1)

TI's GSPS ECM control allows the ADC FS to be set using the ADC SPI bus. The ADC FS voltage range is from 560 mV to 840 mV with 9 bits of FS voltage control.

The ADC ECM gain resolution is calculated with  $\pm 2$ .

Gain Resolution = 20 log

$$\frac{0.56 + \left(\frac{0.84 - 0.56}{2 \times 512}\right)}{0.56 - \left(\frac{0.84 - 0.56}{2 \times 512}\right)} = 8.5 \text{ mdB}$$

(2)

However, the *recommended* ADC FS operating range is narrower: from 595 mV to 805 mV with 700 mV<sub>PP</sub> as the midpoint. Raising the value of ADC FS voltage is tantamount to reducing the signal path gain to accommodate a larger input and vice versa, thus providing a method of gain fine-adjust. The ADC ECM gain adjustment is -1.21-dB, as in  $\pm 3$ .

$$(= 20 \times log \frac{700 \text{ mV}}{805 \text{ mV}}) \text{ to } +1.41 \text{ dB}$$

$$(= 20 \times log \frac{700 \text{ mV}}{595 \text{ mV}})$$

(3)

The ADC FS fine-adjust range of 2.62 dB (= 1.41 dB + 1.21 dB) is larger than the LMH6518 2-dB/step resolution; therefore, there is always at least one LMH6518 gain setting to accommodate any FS signal from 6.8  $mV_{PP}$  to 920  $mV_{PP}$  at the LMH6518 input, with 0.62-dB (= 2.62-2) overlap.

Assuming a nominal 0.7- $V_{PP}$  output, the LMH6518 minimum FS input swing is limited by the maximum signal path gain possible and vice versa with  $\pm 4$ .

Maximum LMH6518 FS Input

$$\frac{0.7 \text{ V}_{PP}}{10 \left( \frac{(38.8 + 1.41) \text{ dB}}{20} \right)} = 6.8 \text{ mV}_{PP}$$

(4)

(or 8 mV<sub>PP</sub> with no ADC fine adjust in 式 5)

Maximum LMH6518 FS Input

$$\frac{0.7 \text{ V}_{PP}}{10\left(\frac{(-1.16-1.21) \text{ dB}}{20}\right)} = 920 \text{ mV}_{PP}$$

(5)

(or 800 mV<sub>PP</sub> with no ADC FS adjust)

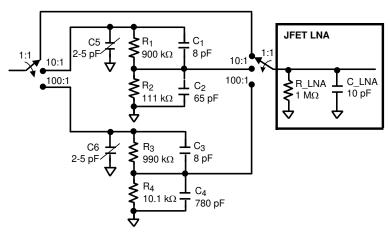

To accommodate a higher FS input, an additional attenuator is required before the LMH6518. This front-end attenuator is shown in the  $\boxtimes$  7-1 with details shown in  $\boxtimes$  7-12. The highest minimum attenuation level is determined by the largest FS input signal (FS<sub>max</sub>) in  $\precsim$  6.

Attenuation (dB) =

$$20 \times log \frac{FS_{MAX} (V_{PP})}{800 \text{ mV}_{PP}}$$

(6)

Therefore, to accommodate 80 V<sub>PP</sub>, a 40-dB minimum attenuation is required before the LMH6518.

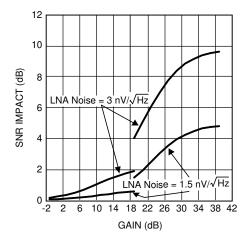

In a typical oscilloscope application, the voltage range encountered is from 1 mV/DIV to 10 V/DIV with eight vertical divisions visible on the screen. One of the primary concerns in a digital oscilloscope is SNR that translates to display trace width to thickness. Typically, oscilloscope manufacturers require the noise level to be low enough so that the *no-input* visible trace width is less than 1% of FS. Experience shows that this corresponds to a minimum SNR of 52 dB.

The factors that influence SNR are:

- Scope front-end noise (Front-end attenuator + scope probe Hi-Z buffer which is discussed later in this data sheet and shown in ⊠ 7-1)

- LMH6518

- ADC

The LMH6518 related SNR factors are:

- Bandwidth

- Preamp used (Preamp HG or LG)

- · Ladder attenuation

- Signal level

SNR increases with the inverse square root of the bandwidth. Therefore, reducing bandwidth from 450 MHz to 200 MHz for example, improves SNR by 3.5-dB, as seen in  $\pm$  7.

$$(20 \times \log \frac{\sqrt{450 \text{ MHz}}}{\sqrt{200 \text{ MHz}}} = 3.5 \text{ dB})$$

(7)

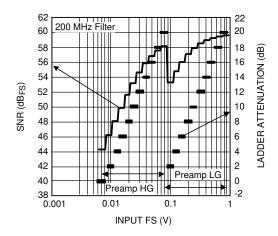

The other factors listed previously, preamp and ladder attenuation, depend on the signal level and also impact SNR. The combined effect of these factors is summarized in  $\boxtimes$  7-3, where SNR is plotted as a function of the LMH6518 FS input voltage (assuming scope bandwidth of 200-MHz) and not including the ADC and the frontend noise.

図 7-3. LMH6518 SNR and Ladder Attenuation Used vs Input

As  $\boxtimes$  7-3 shows, SNR of at least 52 dB is maintained for FS inputs greater than 24 mV<sub>PP</sub> (3 mV/DIV on a scope) assuming the LMH6518 internal 200-MHz filter is enabled. Most oscilloscope manufacturers relax the SNR specifications to 40 dB for the highest gain (lowest scope voltage setting). From  $\boxtimes$  7-3, the LMH6518 minimum SNR is 43.5 dB, thereby meeting the relaxed SNR specification for the lower range of scope front panel voltages.

In  $\boxtimes$  7-3, the step change in SNR near Input FS of 90 mV<sub>PP</sub> is the transition point from preamp LG to preamp HG with a subsequent 3-dB difference due to the preamp HG to 20-dB ladder attenuation lower output noise compared to preamp LG to 2-dB ladder attenuation noise. Judicious choice of front-end attenuators maintains the 52-dB SNR specification for scope FS inputs  $\ge$  24 mV<sub>PP</sub> by confining the LMH6518 gain range to the lower 30.5-dB using  $\pm$  8 from the total range of 40-dB (= 38.8 – (-1.16)) is possible.

$$(= 20 \times \log \frac{0.8 \text{ V}_{PP}}{24 \text{ mV}_{PP}})$$

(8)

For example, to cover the range of 1 mV/DIV to 10 V/DIV (80-dB range), 表 7-1 lists a configuration that affords good SNR.

表 7-1. Oscilloscope Example Including Front-End Attenuators

| ROW | SCOPE FS INPUT<br>(V <sub>PP</sub> ) | S, SCOPE VERTICAL SCALE (V/DIV) |    | LADDER ATTENUATION<br>RANGE (dB) | A, FRONT-END<br>ATTENUATION (V/V) | MINIMUM SNR (dB) WITH 200<br>MHz FILTER |  |

|-----|--------------------------------------|---------------------------------|----|----------------------------------|-----------------------------------|-----------------------------------------|--|

| 1   | 8 m to 24 m                          | 1 m to 3 m                      | HG | 0 to 10                          | 1                                 | 44                                      |  |

| 2   | 24 m to 80 m                         | 3 m to 10 m                     | HG | 10 to 20                         | 1                                 | 52                                      |  |

| 3   | 80 m to 0.8                          | 10 m to 0.1                     | LG | 0 to 20                          | 1                                 | 53.4                                    |  |

| 4   | 0.8 to 8                             | 0.1 to 1                        | LG | 0 to 20                          | 10                                | 53.4                                    |  |

| 5   | 8 to 80                              | 1 to 10                         | LG | 0 to 20                          | 100                               | 53.4                                    |  |

In  $\frac{1}{8}$  7-1, the highest FS input in row 5, column 2 (80 V<sub>PP</sub>), and the LMH6518 highest FS input allowed (0.8 V<sub>PP</sub>) set the front-end attenuator value with  $\frac{1}{8}$  9.

$$100x \left( = \frac{80 \text{ V}_{PP}}{0.8 \text{ V}_{PP}} \right) \tag{9}$$

The 100 × attenuator allows high-SNR operation down to 30.5-dB, as explained earlier, or 2.4  $V_{PP}$  at scope input. In that same table, rows 1 to 3 with no front-end attenuation (1 ×) cover the scope FS input range from 8 mV<sub>PP</sub> to 800 mV<sub>PP</sub>. That leaves the scope FS input range of 0.8  $V_{PP}$  to 2.4  $V_{PP}$ . If the 100 × attenuator is used for the entire scope FS range of 0.8  $V_{PP}$  to 80  $V_{PP}$ , SNR dips below 52-dB for a portion of that range. Another attenuation level is thus required to maintain the SNR specification requirement of 52 dB.

One possible attenuation partitioning is to select the additional attenuator value to cover a 20 dB range above 0.8  $V_{PP}$  FS (to 8  $V_{PP}$ ) with the 100 × attenuator covering the remaining 20-dB range from 8  $V_{PP}$  to 80  $V_{PP}$ . Mapping 8  $V_{PP}$  FS scope input to 0.8  $V_{PP}$  at LMH6518 input means the additional attenuator is 10 ×, as shown in  $\frac{1}{2}$  7-1, row 4. The remaining scope input range of 8  $V_{PP}$  to 80  $V_{PP}$  is then covered by the 100 × front-end attenuator derived earlier. The entire scope input range is now covered with SNR maintained approximately 52 dB for a scope FS input  $\frac{1}{2}$  24 mV<sub>PP</sub>, as shown in  $\frac{1}{2}$  7-1.

### 7.2.1.2.1 Settings and ADC SPI Code (ECM)

Covering the range from 1 mV/div to 10 V/div requires the following adjustment within the digital oscilloscope:

- · Front-end attenuator

- LMH6518 preamp

- LMH6518 ladder attenuation

- ADC FS value (ECM)

The LMH6518 product folder contains a spreadsheet that helps calculate the front-end attenuator, LMH6518 preamp gain (HG or LG), ladder attenuation, and ADC FS setting based on the scope vertical scale (S in V/div).

The following step-by-step procedure explains the operations performed by the spreadsheet based on the scope vertical scale setting (S in V/div) and front-end attenuation A (from  $\gtrsim 7-1$ ). A numerical example is also worked out for more clarification:

1. Determine the required signal path gain, K, with 式 10:

$$K = 20 \times log \frac{0.95 \times 700 \text{ mV}_{PP}}{\frac{8 \times S(V/div)}{A}} = -21.6 + 20 \times log \frac{A}{S(V/div)}$$

(10)

Assuming the full-scale signal occupies 95% of the  $0.7~V_{PP}$  FS for 5% overhead that occupies eight vertical scope divisions.

Required condition: -2.37 dB ≤ K ≤ 40.3 dB