LMH6702-MIL

JAJSDA8 – JUNE 2017

### LMH6702-MIL 1.7GHz、超低歪高帯域オペアンプ

#### 1 特長

$V_S = \pm 5V$ 、 $T_A = 25$ °C、 $A_V = 2V/V$ 、 $R_L = 100\Omega$ 、 $V_{OUT} = 2V_{PP}$ 、特記のない限り標準値

- 2次および3次高調波(5MHz、SOT-23):

-100/-96dBc

- -3dB帯域幅(V<sub>OUT</sub> = 0.5V<sub>PP</sub>) 1.7GHz

- 低ノイズ: 1.83nV/√Hz

Instruments

- 速いセトリング: 0.1%まで13.4ns

- 速いスルーレート: 3100V/μs

- 消費電流12.5mA

- 出力電流80mA

- 低い相互変調歪み(75MHz) -67dBc

- CLC409およびCLC449の上位互換製品

### 2 アプリケーション

- フラッシュA-Dドライバ

- D-Aトランスインピーダンス・バッファ

- 広ダイナミック・レンジIFアンプ

- レーダ/通信機器

- ライン・ドライバ

- 高解像度ビデオ

#### 3 概要

LMH6702-MILはきわめて帯域幅の広いDC結合モノリシック・オペアンプで、優れた信号忠実度を必要とするダイナミック・レンジの広いシステム用に設計されています。電流帰還型アーキテクチャを活かして、外部での補償の必要なしに、非常に高速な動作とユニティ・ゲイン安定性を実現します。

720MHzの帯域幅( $A_V = 2V/V$ 、 $V_O = 2V_{PP}$ )、60MHzまで 10ビットの歪みレベル( $R_L = 100\Omega$ )、入力換算ノイズ 1.83nV/ $\sqrt{Hz}$ 、消費電流12.5mAといった仕様により、LMH6702-MILは高速のフラッシュA-DおよびD-Aコン バータのドライバまたはバッファに理想的です。

レーダや通信受信機など、広帯域幅できわめて純度が高い信号を提供するアンプが必要な、ダイナミック・レンジの広いシステムにおいて、LMH6702-MILは入力換算ノイズが低く、高調波および相互変調歪みが小さいため、魅力的な高速のソリューションです。

LMH6702-MILは、VIP10<sup>TM</sup>相補型バイポーラ・プロセスと、実績のある電流帰還型アーキテクチャで構築されています。LMH6702-MILはSOICおよびSOT-23パッケージで供給されます。

#### 製品情報(1)

| 型番              | パッケージ      | 本体サイズ(公称)     |

|-----------------|------------|---------------|

| LMH6702-MIL     | SOIC (8)   | 4.90mm×3.91mm |

| LIVINO/UZ-IVIIL | SOT-23 (5) | 2.90mm×1.60mm |

(1) 提供されているすべてのパッケージについては、巻末の注文情報 を参照してください。

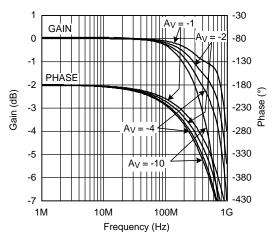

#### 反転側の周波数応答

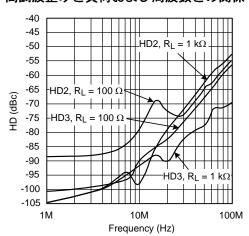

#### 高調波歪みと負荷および周波数との関係

| ·/77 |

|------|

|      |

|      |

|      |

| 1 | 特長1                                  |    | 7.3 Device Functional Modes    | 12 |

|---|--------------------------------------|----|--------------------------------|----|

| 2 | アプリケーション1                            | 8  | Application and Implementation | 13 |

| 3 | 概要1                                  |    | 8.1 Application Information    | 13 |

| 4 | 改訂履歴                                 |    | 8.2 Typical Application        | 13 |

| 5 | Pin Configuration and Functions      | 9  | Power Supply Recommendations   | 15 |

| 6 | Specifications4                      | 10 | Layout                         | 15 |

| - | 6.1 Absolute Maximum Ratings         |    | 10.1 Layout Guidelines         | 15 |

|   | 6.2 ESD Ratings                      |    | 10.2 Layout Example            | 16 |

|   | 6.3 Recommended Operating Conditions | 11 | デバイスおよびドキュメントのサポート             |    |

|   | 6.4 Thermal Information              |    | 11.1 ドキュメントのサポート               | 17 |

|   | 6.5 Electrical Characteristics5      |    | 11.2 コミュニティ・リソース               |    |

|   | 6.6 Typical Characteristics          |    | 11.3 商標                        | 17 |

| 7 | Detailed Description 11              |    | 11.4 静電気放電に関する注意事項             | 17 |

|   | 7.1 Overview 11                      |    | 11.5 Glossary                  |    |

|   | 7.2 Feature Description              | 12 | メカニカル、パッケージ、および注文情報            | 17 |

### 4 改訂履歴

| 日付      | 改訂内容 | 注  |

|---------|------|----|

| 2017年6月 | *    | 初版 |

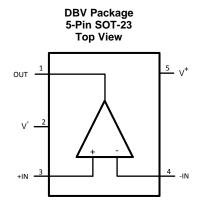

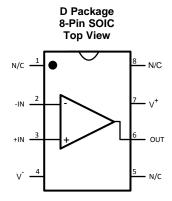

# **5 Pin Configuration and Functions**

NC: No internal connection

#### **Pin Functions**

|        | DIN        |     |     |                             |  |

|--------|------------|-----|-----|-----------------------------|--|

|        | PIN        |     |     |                             |  |

| NAME   | NUMBER I/O |     | 1/0 | DESCRIPTION                 |  |

| NAIVIE | D          | DBV |     |                             |  |

| -IN    | 2          | 4   | I   | Inverting input voltage     |  |

| +IN    | 3          | 3   | I   | Non-inverting input voltage |  |

| N/C    | 1, 5, 8    | _   | _   | No connection               |  |

| OUT    | 6          | 1   | 0   | Output                      |  |

| V-     | 4          | 2   | I   | Negative supply             |  |

| V+     | 7          | 5   | I   | Positive supply             |  |

#### 6 Specifications

#### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)(2)

|                              | ,                             | MIN                | MAX            | UNIT |

|------------------------------|-------------------------------|--------------------|----------------|------|

| V <sub>S</sub>               |                               | ±6.75              | V              |      |

| I <sub>OUT</sub>             |                               | See <sup>(3)</sup> |                |      |

| Common mode input voltage    |                               |                    | $V^-$ to $V^+$ | V    |

| Maximum junction temperature |                               | 150                | °C             |      |

| Storage temperature          |                               |                    | 150            | °C   |

| Coldoring information        | Infrared or convection (20 s) |                    | 235            | °C   |

| Soldering information        | Wave soldering (10 s)         |                    | 260            | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### 6.2 ESD Ratings

|                    |                         |                                                                       | VALUE | UNIT |

|--------------------|-------------------------|-----------------------------------------------------------------------|-------|------|

| .,                 |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>     | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Machine Model (MM), per JEDEC specification JESD22-C101, all pins (2) | ±200  | V    |

<sup>(1)</sup> Human body model: 1.5 kΩ in series with 100 pF. JEDEC document JEP155 states that 2000-V HBM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 2000-V HBM is possible with the necessary precautions. Pins listed as ±2000 V may actually have higher performance.

#### 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)(1)

|                        | MIN | MAX | UNIT |

|------------------------|-----|-----|------|

| Operating temperature  | -40 | 85  | °C   |

| Nominal supply voltage | ±4  | ±6  | V    |

<sup>(1)</sup> Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but specific performance is not ensured. For ensured specifications, see the Electrical Characteristics tables.

#### 6.4 Thermal Information

|                      |                                              | LMH670       |          |      |

|----------------------|----------------------------------------------|--------------|----------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | DBV (SOT-23) | D (SOIC) | UNIT |

|                      |                                              | 5 PINS       | 8 PINS   |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 182          | 133      | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 139          | 79       | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 40           | 73       | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 28           | 28       | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 40           | 73       | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report (SPRA953).

<sup>2)</sup> If Military/Aerospace specified devices are required, please contact the TI Sales Office/ Distributors for availability and specifications.

<sup>(3)</sup> The maximum output current (I<sub>OUT</sub>) is determined by device power dissipation limitations.

<sup>(2)</sup> Machine model: 0 Ω in series with 200 pF. JEDEC document JEP157 states that 200-V MM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 200-V MM is possible with the necessary precautions. Pins listed as ±200 V may actually have higher performance.

www.ti.com

6.5 Electrical Characteristics

### at $A_V = 2$ , $V_S = \pm 5$ V, $R_I = 100$ $\Omega$ , $R_F = 237$ $\Omega$ (unless otherwise noted)<sup>(1)</sup>

|                     | PARAMETER                                  | TEST CONDITIONS                                             | MIN <sup>(2)</sup> | TYP <sup>(3)</sup> | MAX <sup>(2)</sup> | UNIT               |

|---------------------|--------------------------------------------|-------------------------------------------------------------|--------------------|--------------------|--------------------|--------------------|

| FREQUE              | NCY DOMAIN PERFORMANO                      | E                                                           |                    |                    |                    |                    |

| SSBW <sub>SM</sub>  |                                            | $V_{OUT} = 0.5 V_{PP}$                                      |                    | 1700               |                    |                    |

| SSBW <sub>LG</sub>  |                                            | V <sub>OUT</sub> = 2 V <sub>PP</sub>                        |                    | 720                |                    |                    |

| LSBW <sub>LG</sub>  | -3-dB Bandwidth                            | $V_{OUT} = 4 V_{PP}$                                        |                    | 480                |                    | MHz                |

| SSBW <sub>HG</sub>  | -                                          | V <sub>OUT</sub> = 2 V <sub>PP</sub> , A <sub>V</sub> = +10 |                    | 140                |                    |                    |

| GF <sub>0.1dB</sub> | 0.1-dB gain flatness                       | $V_{OUT} = 2 V_{PP}$                                        |                    | 120                |                    | MHz                |

| LPD                 | Linear phase deviation                     | DC to 100 MHz                                               |                    | 0.09               |                    | deg                |

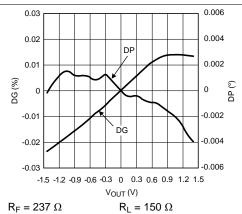

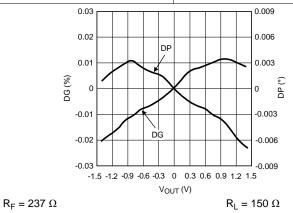

|                     |                                            | R <sub>L</sub> =150 Ω, 3.58 MHz                             |                    | 0.024%             |                    |                    |

| DG                  | Differential gain                          | R <sub>L</sub> =150 Ω, 4.43 MHz                             |                    | 0.021%             |                    |                    |

|                     |                                            | R <sub>L</sub> = 150 Ω, 3.58 MHz                            |                    | 0.004              |                    | _                  |

| DP                  | Differential phase                         | R <sub>L</sub> = 150 Ω, 4.43 MHz                            |                    | 0.007              |                    | deg                |

| TIME DO             | MAIN RESPONSE                              | -                                                           |                    |                    |                    | ,                  |

|                     |                                            | 2-V Step, TRS                                               |                    | 0.87               |                    |                    |

| t <sub>R</sub>      | Rise time                                  | 2-V Step, TRL                                               |                    | 0.77               |                    | ns                 |

|                     |                                            | 6-V Step, TRS                                               |                    | 1.70               |                    |                    |

| t <sub>F</sub>      | Fall time                                  | 6-V Step, TRL                                               |                    | 1.70               |                    | ns                 |

| os                  | Overshoot                                  | 2-V Step                                                    |                    | 0%                 |                    |                    |

| SR                  | Slew rate                                  | 6 V <sub>PP</sub> , 40% to 60% <sup>(4)</sup>               |                    | 3100               |                    | V/µs               |

| T <sub>s</sub>      | Settling time to 0.1%                      | 2-V Step                                                    |                    | 13.4               |                    | ns                 |

|                     | ION AND NOISE RESPONSE                     | •                                                           |                    |                    |                    |                    |

|                     |                                            | 2 V <sub>PP</sub> , 5 MHz <sup>(5)</sup> (SOT-23)           |                    | -100               |                    |                    |

| HD2L                |                                            | 2 V <sub>PP</sub> , 5 MHz <sup>(5)</sup> (SOIC)             |                    | -87                |                    | dBc                |

|                     | -                                          | 2V <sub>PP</sub> , 20 MHz <sup>(5)</sup> (SOT-23)           |                    | -79                |                    |                    |

| HD2                 | 2 <sup>nd</sup> Harmonic distortion        | 2V <sub>PP</sub> , 20 MHz <sup>(5)</sup> (SOIC)             |                    | -72                |                    | dBc                |

|                     | -                                          | 2V <sub>PP</sub> , 60 MHz <sup>(5)</sup> (SOT-23)           |                    | -63                |                    |                    |

| HD2H                |                                            | 2V <sub>PP</sub> , 60 MHz <sup>(5)</sup> (SOIC)             |                    | -64                |                    | dBc                |

|                     |                                            | 2V <sub>PP</sub> , 5 MHz <sup>(5)</sup> (SOT-23)            |                    | -96                |                    |                    |

| HD3L                |                                            | 2V <sub>PP</sub> , 5 MHz <sup>(5)</sup> (SOIC)              |                    | -98                |                    | dBc                |

|                     | -                                          | 2V <sub>PP</sub> , 20 MHz <sup>(5)</sup> (SOT-23)           |                    | -88                |                    |                    |

| HD3                 | 3 <sup>rd</sup> Harmonic distortion        | 2V <sub>PP</sub> , 20 MHz <sup>(5)</sup> (SOIC)             |                    | -82                |                    | dBc                |

|                     | =                                          | 2V <sub>PP</sub> , 60 MHz <sup>(5)</sup> (SOT-23)           |                    | -70                |                    |                    |

| HD3H                |                                            | 2V <sub>PP</sub> , 60 MHz <sup>(5)</sup> (SOIC)             | -65                |                    | dBc                |                    |

| OIM3                | IMD                                        | 75 MHz, P <sub>O</sub> = 10dBm/ tone                        |                    | -67                |                    | dBc                |

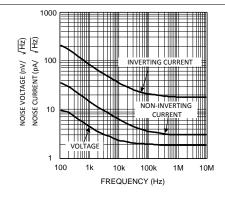

| V <sub>N</sub>      | Input referred voltage noise               | >1 MHz                                                      |                    | 1.83               |                    | nV/√ <del>Hz</del> |

| I <sub>N</sub>      | Input referred inverting noise current     | >1 MHz                                                      |                    | 18.5               |                    | pA/√ <del>Hz</del> |

| I <sub>NN</sub>     | Input referred non-inverting noise current | >1 MHz                                                      |                    | 3.0                |                    | pA/√Hz             |

| SNF                 | Total input noise floor                    | >1 MHz                                                      |                    | -158               |                    | dBm <sub>1Hz</sub> |

| INV                 | Total integrated input noise               | 1 MHz to 150 MHz                                            |                    | 35                 |                    | μV                 |

Electrical Table values apply only for factory testing conditions at the temperature indicated. Factory testing conditions result in very limited self-heating of the device such that  $T_J = T_A$ . No guarantee of parametric performance is indicated in the electrical tables under conditions of internal self-heating where  $T_J > T_A$ . Min/Max ratings are based on production testing unless otherwise specified. All limits are ensured by testing or statistical analysis. Typical numbers are the most likely parametric norm.

Slew Rate is the average of the rising and falling edges.

Harmonic distortion is strongly influenced by package type (SOT-23 or SOIC). See Application Note section under Harmonic Distortion for more information.

### **Electrical Characteristics (continued)**

at A<sub>V</sub> = 2, V<sub>S</sub> = ±5 V, R<sub>L</sub> = 100  $\Omega$ , R<sub>F</sub> = 237  $\Omega$  (unless otherwise noted)<sup>(1)</sup>

|                  | PARAMETER                          |                              | CONDITIONS                | MIN <sup>(2)</sup> | TYP <sup>(3)</sup> | MAX <sup>(2)</sup> | UNIT   |

|------------------|------------------------------------|------------------------------|---------------------------|--------------------|--------------------|--------------------|--------|

| STATIC,          | DC PERFORMANCE                     |                              |                           | ,                  |                    |                    |        |

| V                | Innut offeet voltege               |                              |                           |                    | ±1.0               | ±4.5               | mV     |

| V <sub>IO</sub>  | Input offset voltage               |                              | $-40 \le T_J \le 85$      |                    |                    | ±6.0               | IIIV   |

| $DV_IO$          | Input offset voltage average drift | See <sup>(6)</sup>           |                           |                    | -13                |                    | μV/°C  |

| I                | Input bias current                 | Non-Inverting <sup>(7)</sup> |                           |                    | -6                 | -15                |        |

| I <sub>BN</sub>  | input bias current                 | Non-inverting \              | $-40 \le T_J \le 85$      |                    |                    | -21                | μA     |

| $DI_BN$          | Input bias current average drift   | Non-Inverting <sup>(6)</sup> |                           |                    | +40                |                    | nA/°C  |

|                  | Input bigg ourrent                 | Inverting <sup>(7)</sup>     |                           |                    | -8                 | ±30                |        |

| I <sub>BI</sub>  | Input bias current                 | inverting (**)               | -40 ≤ T <sub>J</sub> ≤ 85 |                    |                    | ±34                | ±34 μΑ |

| $DI_BI$          | Input bias current average drift   | Inverting <sup>(6)</sup>     |                           |                    | -10                |                    | nA/°C  |

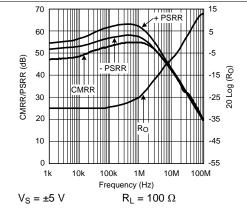

| DCDD             | Davisa avanti maia atian matia     | o DC                         |                           | 47                 | 52                 |                    | dB     |

| PSRR             | Power supply rejection ratio       |                              | $-40 \le T_J \le 85$      | 45                 |                    |                    | uБ     |

| CMRR             | Common mode rejection              | DC                           |                           | 45                 | 48                 |                    | dB     |

| CIVIKK           | ration                             | DC                           | $-40 \le T_J \le 85$      | 44                 |                    |                    | uБ     |

|                  | Cumply augrent                     | D                            |                           | 11.0               | 12.5               | 16.1               | mA     |

| I <sub>CC</sub>  | Supply current                     | R <sub>L</sub> = ∞           | $-40 \le T_J \le 85$      | 10.0               |                    | 17.5               | MA     |

| MISCEL           | LANEOUS PERFORMANCE                |                              |                           |                    |                    |                    |        |

| $R_{\text{IN}}$  | Input resistance                   | Non-Inverting                |                           |                    | 1.4                |                    | МΩ     |

| $C_{IN}$         | Input capacitance                  | Non-Inverting                |                           |                    | 1.6                |                    | pF     |

| R <sub>OUT</sub> | Output resistance                  | Closed Loop                  |                           |                    | 30                 |                    | mΩ     |

| V                | Output voltage range               | R <sub>I</sub> = 100 Ω       |                           | ±3.3               | ±3.5               |                    | ٧      |

| V <sub>OL</sub>  | Output voltage range               | V = 100 77                   | $-40 \le T_J \le 85$      | ±3.2               |                    |                    | V      |

| CMIR             | Input voltage range                | Common Mode                  |                           | ±1.9               | ±2.2               |                    | ٧      |

| Io               | Output current                     |                              |                           | 50                 | 80                 |                    | mA     |

<sup>(6)</sup> Drift determined by dividing the change in parameter at temperature extremes by the total temperature change.(7) Negative input current implies current flowing out of the device.

www.ti.com

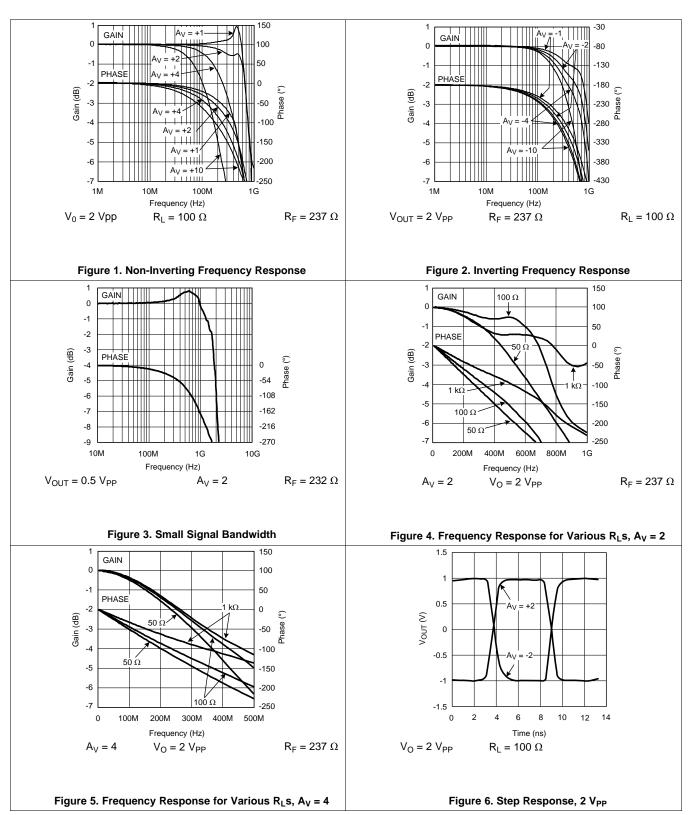

6.6 Typical Characteristics

$T_A$  = 25°C,  $V_S$  = ±5 V,  $R_L$  = 100  $\Omega$ ,  $R_f$  = 237  $\Omega$  (unless otherwise noted)

# TEXAS INSTRUMENTS

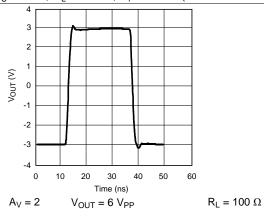

### **Typical Characteristics (continued)**

$T_A = 25$ °C,  $V_S = \pm 5$  V,  $R_L = 100$   $\Omega$ ,  $R_f = 237$   $\Omega$  (unless otherwise noted)

Figure 8. Percent Settling vs Time

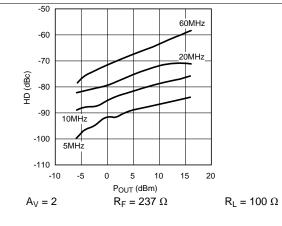

Figure 9. Harmonic Distortion vs Load and Frequency (SOIC Package)

Figure 10. 2 Tone 3rd Order Spurious Level (SOIC Package)

$R_F = 237 \Omega$

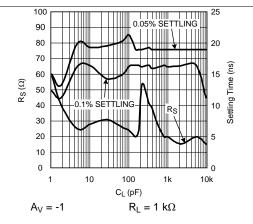

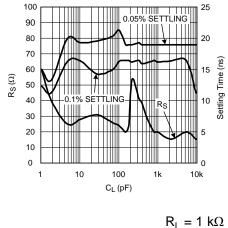

Figure 11.  $\rm R_{S}$  and Settling Time vs  $\rm C_{L}$

Figure 12. HD2 vs Output Power (Across 100  $\Omega$ ) (SOIC Package)

www.ti.com

## **Typical Characteristics (continued)**

$T_A = 25$ °C,  $V_S = \pm 5$  V,  $R_L = 100$   $\Omega$ ,  $R_f = 237$   $\Omega$  (unless otherwise noted)

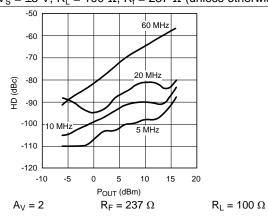

Figure 13. HD3 vs Output Power (Across 100  $\Omega$ ) (SOIC Package)

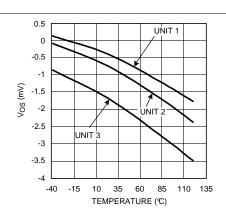

Figure 14. Input Offset for 3 Representative Units

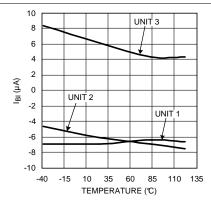

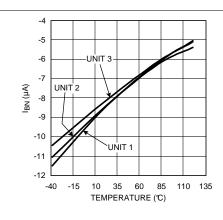

Figure 15. Inverting Input Bias for 3 Representative Units

Figure 16. Non-Inverting Input Bias for 3 Representative Units

Figure 17. Noise

Figure 18. CMRR, PSRR,  $R_{\rm OUT}$

# TEXAS INSTRUMENTS

#### **Typical Characteristics (continued)**

$T_A = 25$ °C,  $V_S = \pm 5$  V,  $R_L = 100$   $\Omega$ ,  $R_f = 237$   $\Omega$  (unless otherwise noted)

Figure 19. Transimpedance

Figure 20. DG/DP (NTSC)

Figure 21. DG/DP (PAL)

#### 7 Detailed Description

#### 7.1 Overview

The LMH6702-MIL has been optimized for exceptionally low harmonic distortion while driving very demanding resistive or capacitive loads. Generally, when used as the input amplifier to very high speed flash ADCs, the distortions introduced by the converter will dominate over the low LMH6702-MIL distortions shown in Typical Characteristics.

#### 7.2 Feature Description

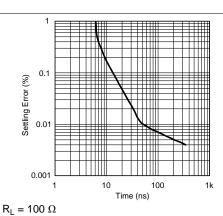

#### 7.2.1 Harmonic Distortion

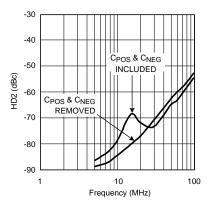

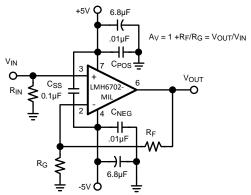

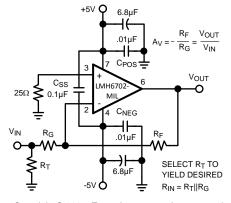

The capacitor C<sub>SS</sub>, shown across the supplies in Figure 24 and Figure 25, is critical to achieving the lowest 2<sup>nd</sup> harmonic distortion. For absolute minimum distortion levels, it is also advisable to keep the supply decoupling currents (ground connections to C<sub>POS</sub>, and C<sub>NEG</sub> in Figure 24 and Figure 25) separate from the ground connections to sensitive input circuitry (such as R<sub>G</sub>, R<sub>T</sub>, and R<sub>IN</sub> ground connections). Splitting the ground plane in this fashion and separately routing the high frequency current spikes on the decoupling caps back to the power supply (similar to Star Connection layout technique) ensures minimum coupling back to the input circuitry and results in best harmonic distortion response (especially 2<sup>nd</sup> order distortion).

If this layout technique has not been observed on a particular application board, designer may actually find that supply decoupling caps could adversely affect HD2 performance by increasing the coupling phenomenon already mentioned. Figure 22 shows actual HD2 data on a board where the ground plane is shared between the supply decoupling capacitors and the rest of the circuit. Once these capacitors are removed, the HD2 distortion levels reduce significantly, especially between 10 MHz to 20 MHz, as shown in Figure 22:

Figure 22. Decoupling Current Adverse Effect on a Board with Shared Ground Plane

At these extremely low distortion levels, the high frequency behavior of decoupling capacitors themselves could be significant. In general, lower value decoupling caps tend to have higher resonance frequencies making them more effective for higher frequency regions. A particular application board which has been laid out correctly with ground returns split to minimize coupling, would benefit the most by having low value and higher value capacitors paralleled to take advantage of the effective bandwidth of each and extend low distortion frequency range.

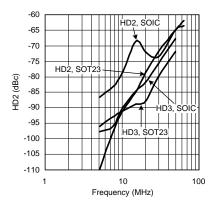

Another important variable in getting the highest fidelity signal from the LMH6702-MIL is the package itself. As already noted, coupling between high frequency current transients on supply lines and the device input can lead to excess harmonic distortion. An important source of this coupling is in fact through the device bonding wires. A smaller package, in general, will have shorter bonding wires and therefore lower coupling. This is true in the case of the SOT-23 compared to the SOIC package where a marked improvement in HD can be measured in the SOT-23 package. Figure 23 shows the HD comparing SOT-23 to SOIC package:

# TEXAS INSTRUMENTS

#### **Feature Description (continued)**

Figure 23. SOIC and SOT-23 Packages Distortion Terms Compared

The LMH6702-MIL data sheet shows both SOT-23 and SOIC data in *Electrical Characteristics* to aid in selecting the right package. *Typical Characteristics* shows SOIC package plots only.

#### 7.3 Device Functional Modes

#### 7.3.1 2-Tone 3<sup>rd</sup> Order Intermodulation

Figure 10 shows a relatively constant difference between the test power level and the spurious level with the difference depending on frequency. The LMH6702-MIL does not show an intercept type performance, (where the relative spurious levels change at a 2X rate versus the test tone powers), due to an internal full power bandwidth enhancement circuit that boosts the performance as the output swing increases while dissipating negligible quiescent power under low output power conditions. This feature enhances the distortion performance and full power bandwidth to match that of much higher quiescent supply current parts.

#### 7.3.2 DC Accuracy and Noise

The example in Equation 1 shows the output offset computation equation for the non-inverting configuration using the typical bias current and offset specifications for  $A_{V} = 2$ :

Output Offset:

$$V_O = (\pm I_{BN} \cdot R_{IN} \pm V_{IO}) (1 + R_F/R_G) \pm I_{BI} \cdot R_F$$

where

R<sub>IN</sub> is the equivalent input impedance on the non-inverting input.

Example computation for  $A_V = +2$ ,  $R_F = 237\Omega$ ,  $R_{IN} = 25\Omega$ :

$$V_O = (\pm 6 \mu A \times 25 \Omega \pm 1 mV) (1 + 237/237) \pm 8 \mu A \times 237 = \pm 4.20 mV$$

(2)

A good design, however, should include a worst case calculation using min/max numbers in the data sheet tables, in order to ensure *worst case* operation.

Further improvement in the output offset voltage and drift is possible using the composite amplifiers described in Application Note OA--07, *Current Feedback Op Amp Applications Circuit Guide* (SNOA365). The two input bias currents are physically unrelated in both magnitude and polarity for the current feedback topology. It is not possible, therefore, to cancel their effects by matching the source impedance for the two inputs (as is commonly done for matched input bias current devices).

The total output noise is computed in a similar fashion to the output offset voltage. Using the input noise voltage and the two input noise currents, the output noise is developed through the same gain equations for each term but combined as the square root of the sum of squared contributing elements. See Application Note OA-12, *Noise Analysis for Comlinear Amplifiers* (SNOA375) for a full discussion of noise calculations for current feedback amplifiers.

(1)

#### 8 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

#### 8.1 Application Information

The LMH6702-MIL achieves its excellent pulse and distortion performance by using the current feedback topology. The loop gain for a current feedback op amp, and hence the frequency response, is predominantly set by the feedback resistor value. The LMH6702-MIL is optimized for use with a 237- $\Omega$  feedback resistor. Using lower values can lead to excessive ringing in the pulse response while a higher value will limit the bandwidth.

#### 8.2 Typical Application

#### 8.2.1 Feedback Resistor

The LMH6702-MIL achieves its excellent pulse and distortion performance by using the current feedback topology. The loop gain for a current feedback op amp, and hence the frequency response, is predominantly set by the feedback resistor value. The LMH6702-MIL is optimized for use with a  $237-\Omega$  feedback resistor. Using lower values can lead to excessive ringing in the pulse response while a higher value will limit the bandwidth.

Copyright © 2017, Texas Instruments Incorporated

Figure 24. Recommended Non-Inverting Gain Circuit

Copyright © 2017, Texas Instruments Incorporated

Figure 25. Recommended Inverting Gain Circuit

# TEXAS INSTRUMENTS

#### **Typical Application (continued)**

#### 8.2.2 Design Requirements

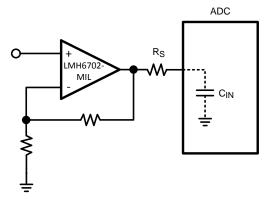

The exceptional performance and uniquely targeted superior technical specifications of the LMH6702-MIL make it a natural choice for high speed data acquisition applications as a front end amplifier driving the input of a high performance ADC. Of these specifications, the following can be discussed in more detail:

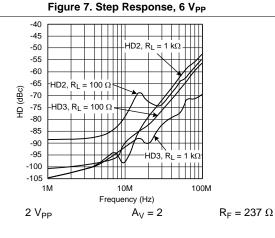

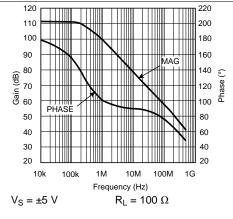

- 1. A bandwidth of 1.7 GHz and relative insensitivity of bandwidth to closed loop gain (characteristic of Current Feedback architecture when compared to the traditional voltage feedback architecture) as shown in Figure 1.

- 2. Ultra-low distortion approaching -87 dBc at the lower frequencies and exceptional noise performance (see Figure 9 and Figure 17).

- 3. Fast settling in less than 20 ns (see Figure 27).

As the input of an ADC could be capacitive in nature and could also alternate in capacitance value during a typical acquisition cycle, the driver amplifier (LMH6702-MIL in this case) should be designed so that it avoids instability, peaking, or other undesirable artifacts.

For Capacitive Load Drive, see Figure 26, which shows a typical application using the LMH6702-MIL to drive an ADC.

Copyright © 2017, Texas Instruments Incorporated

Figure 26. Input Amplifier to ADC

#### 8.2.3 Detailed Design Procedure

The series resistor,  $R_S$ , between the amplifier output and the ADC input is critical to achieving best system performance. This load capacitance, if applied directly to the output pin, can quickly lead to unacceptable levels of ringing in the pulse response. Figure 27 in *Application Curve* ( $R_S$  and Settling Time vs  $C_L$ ) is an excellent starting point for selecting  $R_S$ . The value derived in that plot minimizes the step settling time into a fixed discrete capacitive load with the output driving a very light resistive load (1 k $\Omega$ ). Sensitivity to capacitive loading is greatly reduced once the output is loaded more heavily. Therefore, for cases where the output is heavily loaded,  $R_S$  value may be reduced. The exact value may best be determined experimentally for these cases.

In applications where the LMH6702-MIL is replacing the CLC409, care must be taken when the device is lightly loaded and some capacitance is present at the output. Due to the much higher frequency response of the LMH6702-MIL compared to the CLC409, there could be increased susceptibility to low value output capacitance (parasitic or inherent to the board layout or otherwise being part of the output load). As already mentioned, this susceptibility is most noticeable when the LMH6702-MIL's resistive load is light. Parasitic capacitance can be minimized by careful lay out. Addition of an output snubber R-C network will also help by increasing the high frequency resistive loading.

Referring back to Figure 26, it must be noted that several additional constraints should be considered in driving the capacitive input of an ADC. There is an option to increase  $R_S$ , band-limiting at the ADC input for either noise or Nyquist band-limiting purposes. However, increasing  $R_S$  too much can induce an unacceptably large input glitch due to switching transients coupling through from the *convert* signal. Also,  $C_{IN}$  is oftentimes a voltage dependent capacitance. This input impedance non-linearity will induce distortion terms that will increase as  $R_S$  is increased. Only slight adjustments up or down from the recommended  $R_S$  value should therefore be attempted in optimizing system performance.

JAJSDA8-JUNE 2017

#### **Typical Application (continued)**

#### 8.2.4 Application Curve

$A_{V} = -1$

Figure 27. R<sub>S</sub> and Settling Time vs C<sub>L</sub>

#### 9 Power Supply Recommendations

The LMH6702-MIL can operate off a single supply or with dual supplies as long as the input CM voltage range (CMIR) has the required headroom to either supply rail. Supplies should be decoupled with low inductance, often ceramic, capacitors to ground less than 0.5 inches from the device pins. The use of ground plane is recommended, and as in most high speed devices, it is advisable to remove ground plane close to device sensitive pins such as the inputs.

#### 10 Layout

#### 10.1 Layout Guidelines

Generally, a good high frequency layout will keep power supply and ground traces away from the inverting input and output pins. Parasitic capacitances on these nodes to ground will cause frequency response peaking and possible circuit oscillations. See Frequent Faux Pas in Applying Wideband Current Feedback Amplifiers, Application Note OA-15 (SNOA367). Texas Instruments suggests the following evaluation boards as a guide for high frequency layout and as an aid in device testing and characterization. See Table 1 for details.

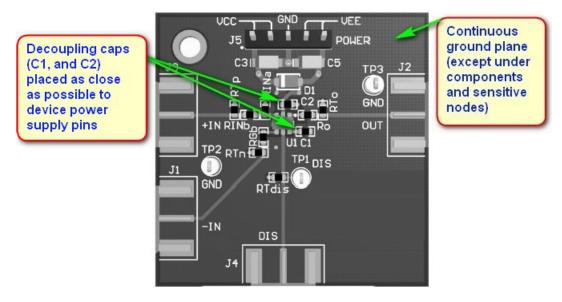

The LMH6702-MIL evaluation board(s) is a good example of high frequency layout techniques as a reference. General high-speed, signal-path layout suggestions include:

- Continuous ground planes are preferred for signal routing with matched impedance traces for longer runs. However, open up both ground and power planes around the capacitive sensitive input and output device pins as shown in Figure 28. After the signal is sent into a resistor, parasitic capacitance becomes more of a bandlimiting issue and less of a stability issue.

- Use good, high-frequency decoupling capacitors (0.1 μF) on the ground plane at the device power pins as shown in Figure 28. Higher value capacitors (2.2 µF) are required, but may be placed further from the device power pins and shared among devices. For best high-frequency decoupling, consider X2Y supply-decoupling capacitors that offer a much higher self-resonance frequency over standard capacitors.

- When using differential signal routing over any appreciable distance, use microstrip layout techniques with matched impedance traces.

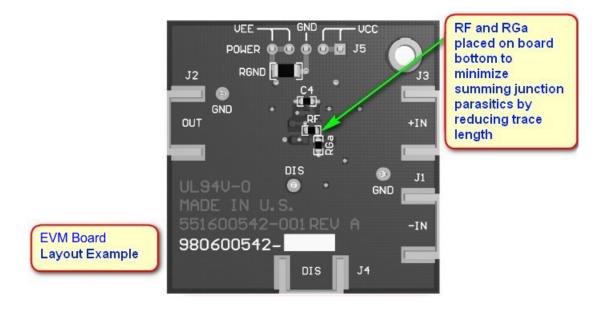

- The input summing junction is very sensitive to parasitic capacitance. Connect any Rf, and Rg elements into the summing junction with minimal trace length to the device pin side of the resistor, as shown in Figure 29. The other side of these elements can have more trace length if needed to the source or to ground.

# TEXAS INSTRUMENTS

#### 10.2 Layout Example

Figure 28. LMH6702-MIL Evaluation Board Layer 1

Figure 29. LMH6702-MIL Evaluation Board Layer 2

**Table 1. Evaluation Board Comparison**

| DEVICE        | PACKAGE | EVALUATION BOARD PART NUMBER |

|---------------|---------|------------------------------|

| LMH6702-MILMF | SOT-23  | LMH730216                    |

| LMH6702-MILMA | SOIC    | LMH730227                    |

JAJSDA8 - JUNE 2017 www.tij.co.jp

### 11 デバイスおよびドキュメントのサポート

#### 11.1 ドキュメントのサポート

#### 11.1.1 関連資料

関連資料については、以下を参照してください。

- 『ハンダ付けの絶対最大定格』(SNOA549)

- 『電流帰還型オペアンプ・アプリケーション回路ガイド』、アプリケーション・ノートOA-07 (SNOA365)

- 『広帯域電流帰還型アンプ適用時に多見される失敗』、アプリケーション・ノートOA-15 (SNOA367)

- 『Comlinearアンプのノイズ解析』、アプリケーション・ノートOA-12 (SNOA375)

- 『半導体およびICパッケージの熱指標』(SPRA953)

#### 11.2 コミュニティ・リソース

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

TI E2E™オンライン・コミュニティ *TIのE2E(Engineer-to-Engineer)コミュニティ。*エンジニア間の共同作業を促進するために開設されたものです。e2e.ti.comでは、他のエンジニアに質問し、知識を共有 し、アイディアを検討して、問題解決に役立てることができます。

設計サポート *TIの設計サポート* 役に立つE2Eフォーラムや、設計サポート・ツールをすばやく見つけることが できます。技術サポート用の連絡先情報も参照できます。

#### 11.3 商標

VIP10, E2E are trademarks of Texas Instruments. All other trademarks are the property of their respective owners.

#### 11.4 静電気放電に関する注意事項

これらのデバイスは、限定的なESD(静電破壊)保護機能を内 蔵しています。保存時または取り扱い時は、MOSゲートに対す る静電破壊を防 止するために、リード線同士をショートさせておくか、デバイスを導電フォームに入れる必要があります。

#### 11.5 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

#### 12 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、そのデバイスについて利用可能な最新のデータです。このデータは予告なく変更されることがあり、ドキュメントが改訂される場合もありま す。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

#### PACKAGE OPTION ADDENDUM

10-Dec-2020

#### PACKAGING INFORMATION

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp    | Op Temp (°C) | Device Marking (4/5) | Samples |

|------------------|--------|--------------|--------------------|------|----------------|--------------|-------------------------------|------------------|--------------|----------------------|---------|

|                  |        |              |                    |      |                |              | (6)                           |                  |              |                      |         |

| LMH6702 MDC      | ACTIVE | DIESALE      | Y                  | 0    | 754            | RoHS & Green | Call TI                       | Level-1-NA-UNLIM | -40 to 85    |                      | Samples |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### 重要なお知らせと免責事項

TI は、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス・デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションが適用される各種規格や、その他のあらゆる安全性、セキュリティ、またはその他の要件を満たしていることを確実にする責任を、お客様のみが単独で負うものとします。上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TIの製品は、TIの販売条件(www.tij.co.jp/ja-jp/legal/termsofsale.html)、または ti.com やかかる TI 製品の関連資料などのいずれかを通じて提供 する適用可能な条項の下で提供されています。TI がこれらのリソースを提供することは、適用されるTI の保証または他の保証の放棄の拡大や変更を意味するものではありません。

Copyright © 2020, Texas Instruments Incorporated 日本語版 日本テキサス・インスツルメンツ株式会社