Sample &

Buy

LMH6882

SNOSC84D – AUGUST 2012 – REVISED FEBRUARY 2015

20

# LMH6882 DC to 2.4-GHz, High-Linearity, Dual, Programmable Differential Amplifier

Technical

Documents

### 1 Features

- Small Signal Bandwidth: 2400 MHz

- OIP3 @ 100 MHz: 42 dBm

- HD3 @ 100 MHz: -100 dBc

- Noise Figure: 9.7 dB

- Voltage Gain: 26 dB to 6 dB

- Voltage Gain Step Size: 0.25 dB

- Input Impedance: 100 Ω

- Parallel and Serial Gain Control

- Power Down Capability

# 2 Applications

- Microwave Backhaul Radio Receiver

- Zero IF Sampling

- In-Phase/Quadrature (I/Q) Sampling

- Medical Imaging

- RF/IF and Baseband Gain Blocks

- Differential Cable Driver

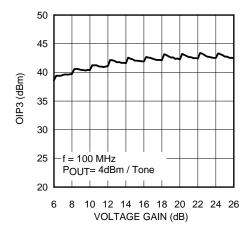

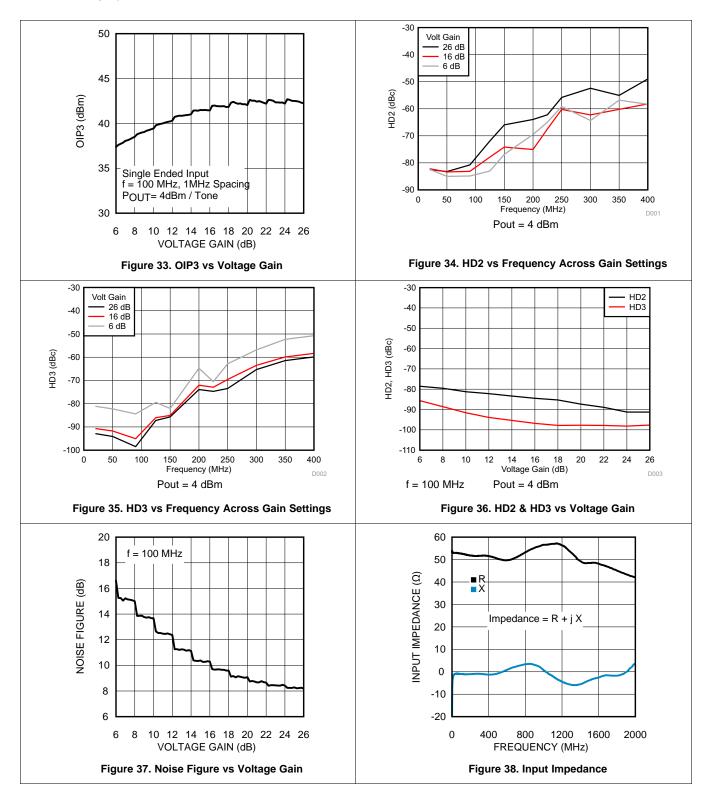

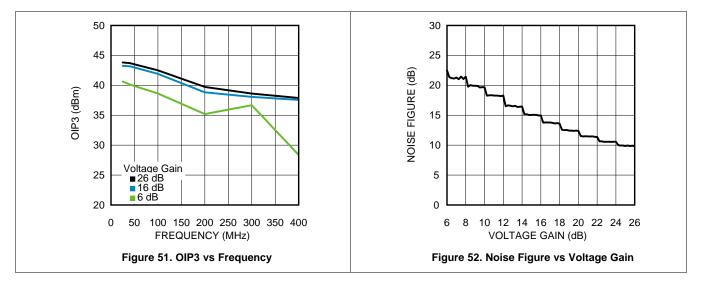

### **OIP3 vs Voltage Gain**

## 3 Description

Tools &

Software

The LMH6882 is a high-speed, high-performance programmable differential amplifier. With a bandwidth of 2.4 GHz and high linearity of 42 dBm OIP3, the LMH6882 is suitable for a wide variety of signal conditioning applications.

Support &

Community

The LMH6882 programmable differential amplifier combines the best of both fully differential amplifiers and variable-gain amplifiers. The device offers superior noise and distortion performance over the entire gain range without external resistors, enabling the use of just one device and one design for multiple applications requiring different gain settings.

The LMH6882 is an easy-to-use amplifier that can replace both fully differential, fixed-gain amplifiers as well as variable-gain amplifiers. The LMH6882 requires no external gain-setting components and supports gain settings from 6 dB to 26 dB with small, accurate 0.25-dB gain steps. As shown in the adjacent voltage gain chart the gain steps are very accurate over the entire gain range. With an input impedance of 100  $\Omega$ , the LMH6882 is easy to drive from a variety of sources such as mixers or filters. The LMH6882 also supports 50- $\Omega$  single-ended signal sources and supports DC- and AC-coupled applications.

Parallel gain control allows the LMH6882 to be soldered down in a fixed-gain so that no control circuit is required. If dynamic gain control is desired, the LMH6882 can be changed with SPI<sup>™</sup> serial commands or with the parallel pins.

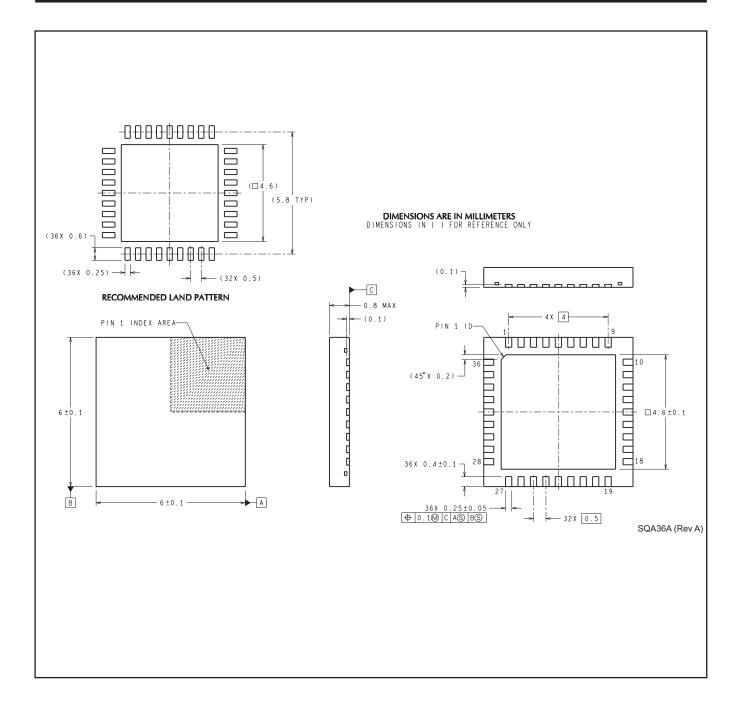

The LMH6882 is fabricated in TI's CBiCMOS8 proprietary complementary silicon germanium process and is available in a space-saving, thermally enhanced 36-pin WQFN package. The same amplifier is offered in a single package as the LMH6881.

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)   |  |

|-------------|-----------|-------------------|--|

| LMH6882     | WQFN (36) | 6.00 mm × 6.00 mm |  |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

# **Table of Contents**

| 1 | Feat | tures 1                            |

|---|------|------------------------------------|

| 2 | Арр  | lications 1                        |

| 3 | Des  | cription 1                         |

| 4 | Rev  | ision History 2                    |

| 5 | Pin  | Configuration and Functions 3      |

| 6 | Spe  | cifications 4                      |

|   | 6.1  | Absolute Maximum Ratings 4         |

|   | 6.2  | ESD Ratings 4                      |

|   | 6.3  | Recommended Operating Conditions 4 |

|   | 6.4  | Thermal Information 4              |

|   | 6.5  | Electrical Characteristics 5       |

|   | 6.6  | Typical Characteristics 7          |

| 7 | Deta | ailed Description 14               |

|   | 7.1  | Overview 14                        |

|   | 7.2  | Functional Block Diagram 14        |

|   | 7.3  | Feature Description 14             |

|    | 7.4  | Device Functional Modes           | 15 |

|----|------|-----------------------------------|----|

|    | 7.5  | Programming                       | 16 |

| 8  | App  | lication and Implementation       | 21 |

|    | 8.1  | Application Information           | 21 |

|    | 8.2  | Typical Applications              | 26 |

| 9  | Pow  | er Supply Recommendations         | 29 |

| 10 | Lay  | out                               | 29 |

|    | 10.1 | Layout Guidelines                 | 29 |

|    | 10.2 | Layout Example                    | 30 |

|    | 10.3 | Thermal Considerations            | 31 |

| 11 | Dev  | ice and Documentation Support     | 32 |

|    | 11.1 | Documentation Support             | 32 |

|    | 11.2 | Trademarks                        | 32 |

|    | 11.3 | Electrostatic Discharge Caution   | 32 |

|    | 11.4 | Glossary                          | 32 |

| 12 | Mec  | hanical, Packaging, and Orderable |    |

|    |      | mation                            | 32 |

|    |      |                                   |    |

Copyright © 2012–2015, Texas Instruments Incorporated

### 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

#### Changes from Revision C (March 2013) to Revision D

| • | Added Pin Configuration and Functions section, ESD Ratings table, Feature Description section, Device Functional |

|---|------------------------------------------------------------------------------------------------------------------|

|   | Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device      |

|   | and Documentation Support section, and Mechanical, Packaging, and Orderable Information section                  |

### Changes from Revision B (March 2013) to Revision C

Submit Documentation Feedback

www.ti.com

Page

Page

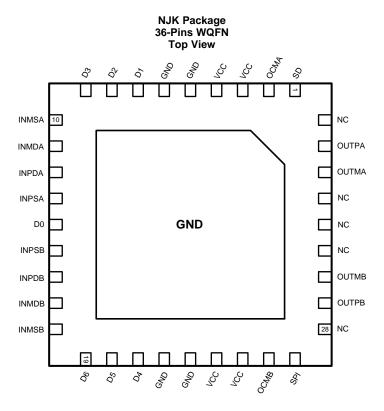

# 5 Pin Configuration and Functions

#### **Pin Functions**

| PIN                        |                         | ТҮРЕ                            | DESCRIPTION                                                                                                                                                                                             |  |  |

|----------------------------|-------------------------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME                       | NO.                     | ITPE                            | DESCRIPTION                                                                                                                                                                                             |  |  |

| ANALOG I/O                 | •                       | •                               |                                                                                                                                                                                                         |  |  |

| INPD, INMD                 | 11, 12, 16, 17          | Analog Input                    | Differential inputs 100 Ω                                                                                                                                                                               |  |  |

| INPS, INMS                 | 10, 13, 15, 18          | Analog Input                    | Single ended inputs 50 $\Omega$                                                                                                                                                                         |  |  |

| OUTP, OUTM                 | 35, 34, 30, 29          | Analog Output                   | Differential outputs, low impedance                                                                                                                                                                     |  |  |

| POWER                      |                         |                                 |                                                                                                                                                                                                         |  |  |

| GND                        | 5, 6, 22, 23            | Ground                          | Ground pins. Connect to low-impedance ground plane.<br>All pin voltages are specified with respect to the voltage<br>on these pins. The exposed thermal pad is internally<br>bonded to the ground pins. |  |  |

| VCC                        | 3, 4, 24, 25            | Power                           | Power supply pins. Valid power supply range is 4.75 V to 5.25 V.                                                                                                                                        |  |  |

|                            | Exposed Center Pad      | Thermal/ Ground                 | Thermal management/ Ground                                                                                                                                                                              |  |  |

| DIGITAL INPUTS             |                         |                                 |                                                                                                                                                                                                         |  |  |

| SPI                        | 27                      | Digital Input                   | 0 = Parallel Mode, 1 = Serial Mode                                                                                                                                                                      |  |  |

| PARALLEL MODE DIGITAL      | PINS, SPI = LOGIC LO    | W                               |                                                                                                                                                                                                         |  |  |

| D0, D1, D2, D3, D4, D5, D6 | 14, 7, 8, 9, 21, 29, 19 | Digital Input                   | Attenuator control, D0 = 0.25 dB, D6 = 16 dB                                                                                                                                                            |  |  |

| SD                         | 1                       | Digital Input                   | Shutdown $0 = amp on, 1 = amp off$                                                                                                                                                                      |  |  |

| SERIAL MODE DIGITAL PIN    | S, SPI = LOGIC HIGH (   | SPI COMPATIBLE)                 |                                                                                                                                                                                                         |  |  |

| CS                         | 9                       | Digital Input                   | Chip Select (active low)                                                                                                                                                                                |  |  |

| CLK                        | 8                       | Digital Input                   | Clock                                                                                                                                                                                                   |  |  |

| SDO                        | 14                      | Digital Output- Open<br>Emitter | Serial Data Output (Requires external bias.)                                                                                                                                                            |  |  |

| SDI                        | 7                       | Digital Input                   | Serial Data In                                                                                                                                                                                          |  |  |

Copyright © 2012–2015, Texas Instruments Incorporated

STRUMENTS

XAS

## 6 Specifications

## 6.1 Absolute Maximum Ratings<sup>(1)(2)</sup>

|                                                        | MIN  | MAX      | UNIT |

|--------------------------------------------------------|------|----------|------|

| Positive supply voltage (VCC)                          | -0.6 | 5.5      | V    |

| Differential voltage between any two grounds           |      | < 200    | mV   |

| Analog input voltage                                   | -0.6 | 5.5      | V    |

| Digital input voltage                                  | -0.6 | 5.5      | V    |

| Output short circuit duration (one pin to ground)      |      | Infinite |      |

| Junction temperature                                   |      | +150     | °C   |

| Soldering information: infrared or convection (30 sec) |      | 260      | °C   |

| Storage temperature, T <sub>stg</sub>                  | -65  | 150      | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/Distributors for availability and specifications.

### 6.2 ESD Ratings

|                    |                         |                                                                                       | VALUE | UNIT |

|--------------------|-------------------------|---------------------------------------------------------------------------------------|-------|------|

|                    |                         | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>                     | ±1000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 $^{\left( 2\right) }$ | ±250  | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                                              | MIN  | MAX  | UNIT |

|----------------------------------------------|------|------|------|

| Supply voltage (VCC)                         | 4.75 | 5.25 | V    |

| Differential voltage between any two grounds |      | < 10 | mV   |

| Analog input voltage,<br>AC coupled          | 0    | VCC  | V    |

| Temperature range <sup>(1)</sup>             | -40  | 85   | °C   |

(1) The maximum power dissipation is a function of  $T_{J(MAX)}$ ,  $\theta_{JA}$  and the ambient temperature  $T_A$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_{J(MAX)} - T_A)/\theta_{JA}$ . All numbers apply for packages soldered directly onto a PC Board.

### 6.4 Thermal Information

|                       |                                              | LMH6882    |      |

|-----------------------|----------------------------------------------|------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | NJK (WQFN) | UNIT |

|                       |                                              | 36 PINS    |      |

| R <sub>θJA</sub>      | Junction-to-ambient thermal resistance       | 33.6       |      |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 16.9       |      |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 7.8        | °C/W |

| Ψ <sub>JT</sub>       | Junction-to-top characterization parameter   | 0.3        | C/VV |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 7.7        |      |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 3.5        |      |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

#### 6.5 Electrical Characteristics

| The following specifications apply for single supply with VCC = | 5 V. Maximum Gain (26 dB), $R_1 = 200 \Omega_1^{(1)(2)(3)}$ |

|-----------------------------------------------------------------|-------------------------------------------------------------|

| The following opcomodions apply for single supply with voc -    | $0 v_1 maximum Ount (20 aD), 10 = 200 32.$                  |

|                  |                                                   | TEST CONDITIONS                                                                                | MIN <sup>(4)</sup> TYP <sup>(5)</sup> MAX <sup>(4)</sup> | UNIT             |

|------------------|---------------------------------------------------|------------------------------------------------------------------------------------------------|----------------------------------------------------------|------------------|

| DYNAMIC          | C PERFORMANCE                                     | · · · · · · · · · · · · · · · · · · ·                                                          |                                                          |                  |

| 3dBBW            | −3-dB Bandwidth                                   | V <sub>OUT</sub> = 2 V <sub>PPD</sub>                                                          | 2.4                                                      | GHz              |

| NF               | Noise Figure                                      | Source Resistance (Rs) = $100 \Omega$                                                          | 9.7                                                      | dB               |

| OIP3             | Output Third Order Intercept Point <sup>(6)</sup> | $f = 100 \text{ MHz}, P_{OUT} = 4 \text{ dBm per tone, tone}$<br>spacing = 1 MHz               | 42                                                       | dBm              |

|                  |                                                   | $f = 200 \text{ MHz}, P_{OUT} = 4 \text{ dBm per tone, tone}$<br>spacing = 2 MHz               | 40                                                       |                  |

| OIP2             | Output Second Order Intercept Point               | P <sub>OUT</sub> = 4 dBm per Tone, f1 = 112.5 MHz,<br>f2=187.5 MHz                             | 76                                                       | dBm              |

| IMD3             | Third Order Intermodulation<br>Products           | f = 100 MHz, $V_{OUT}$ = 4 dBm per tone, tone spacing = 1 MHz                                  | -76                                                      | dBc              |

|                  |                                                   | $f = 200 \text{ MHz}, P_{OUT} = 4 \text{ dBm per tone, tone}$<br>spacing = 2 MHz               | -72                                                      |                  |

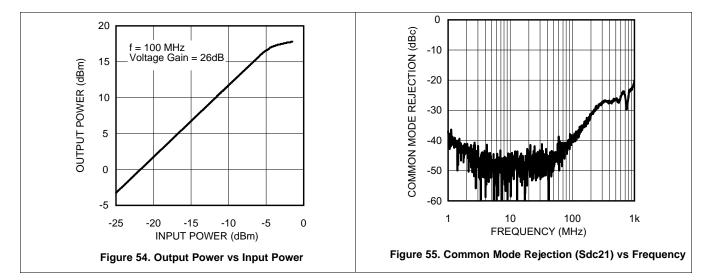

| P1dB             | 1-dB Compression Point                            | Output power                                                                                   | 17                                                       | dBm              |

| HD2              | Second Order Harmonic Distortion                  | f = 200 MHz, V <sub>OUT</sub> = 4 dBm                                                          | -70                                                      | dBc              |

| HD3              | Third Order Harmonic Distortion                   | f = 200 MHz, P <sub>OUT</sub> = 4 dBm                                                          | -76                                                      | dBc              |

| CMRR             | Common Mode Rejection Ratio (7)                   | Pin = −15 dBm, f = 100 MHz                                                                     | -40                                                      | dBc              |

| SR               | Slew Rate                                         |                                                                                                | 6000                                                     | V/us             |

|                  | Output Voltage Noise                              | Maximum Gain f > 1 MHz                                                                         | 47                                                       | nV/√Hz           |

|                  | Input Referred Voltage Noise                      | Maximum Gain f > 1 MHz                                                                         | 2.3                                                      | nV/√Hz           |

| ANALOG           | 1/0                                               |                                                                                                |                                                          |                  |

| R <sub>IN</sub>  | Input Resistance                                  | Differential, INPD to INMD                                                                     | 100                                                      | Ω                |

| R <sub>IN</sub>  | Input Resistance                                  | Single Ended, INPS or INMS, $50-\Omega$ termination on unused input                            | 50                                                       | Ω                |

| V <sub>ICM</sub> | Input Common Mode Voltage                         | Self Biased                                                                                    | 2.5                                                      | V                |

|                  | Maximum Input Voltage Swing                       | Volts peak to peak, differential                                                               | 2                                                        | V <sub>PPD</sub> |

|                  | Maximum Differential Output Voltage Swing         | Differential, f < 10 MHz                                                                       | 6                                                        | V <sub>PPD</sub> |

| R <sub>OUT</sub> | Output Resistance                                 | Differential, f = 100 MHz                                                                      | 0.4                                                      | Ω                |

| GAIN PA          | RAMETERS                                          |                                                                                                |                                                          |                  |

|                  | Maximum Voltage Gain                              | Parallel Inputs (INPD and INMD), Rs = $100 \Omega$                                             | 26                                                       | ٩D               |

|                  |                                                   | Single ended input (INMS or INPS), 50 $\Omega$ Rs and 50 $\Omega$ termination on unused input. | 26.6                                                     | dB               |

|                  | Minimum Gain                                      | Gain Code = 80d or 50h                                                                         | 6                                                        | dB               |

|                  | Gain Steps                                        |                                                                                                | 80                                                       |                  |

|                  | Gain Step Size                                    |                                                                                                | 0.25                                                     | dB               |

|                  | Gain Step Error                                   | Any two adjacent steps over entire range                                                       | ±0.125                                                   | dB               |

|                  | Gain Step Phase Shift                             | Any two adjacent steps over entire range                                                       | ±3                                                       | Degrees          |

(1) Electrical Table values apply only for factory testing conditions at the temperature indicated. No specification of parametric performance is indicated in the electrical tables under conditions different than those tested

(2) Negative input current implies current flowing out of the device.

(3) Drift determined by dividing the change in parameter at temperature extremes by the total temperature change.

(4) Limits are 100% production tested at 25°C. Limits over the operating temperature range are specified through correlation using Statistical Quality Control (SQC) methods.

(5) Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not ensured on shipped production material.

(6) OIP3 is the third order intermodulation intercept point. In this data sheet OIP3 numbers are single power measurements where OIP3 = IMD3 / 2 + POUT (per tone). OIP2 is the second order intercept point where OIP2 = IMD2 + POUT (per tone). HD2 is the second order harmonic distortion and is a single tone measurement. HD3 is the third order harmonic distortion and is a single tone measurement. Power measurements are made at the amplifier output pins.

(7) CMRR is defined as the differential response at the output in response to a common mode signal at the input.

Copyright © 2012–2015, Texas Instruments Incorporated

SNOSC84D - AUGUST 2012 - REVISED FEBRUARY 2015

www.ti.com

STRUMENTS

EXAS

# **Electrical Characteristics (continued)**

The following specifications apply for single supply with VCC = 5 V, Maximum Gain (26 dB),  $R_L = 200 \Omega$ .<sup>(1)(2)(3)</sup>

|                  |                                   | TEST CONDITIONS                       | MIN <sup>(4)</sup> | TYP <sup>(5)</sup> | MAX <sup>(4)</sup> | UNIT    |

|------------------|-----------------------------------|---------------------------------------|--------------------|--------------------|--------------------|---------|

|                  | Channel to Channel Gain Matching  | f = 100 MHz, over entire gain range   |                    | 0.2                |                    | dB      |

|                  | Channel to Channel Phase Matching | f= 100 MHz, over entire gain range    |                    | 1.5                |                    | Degrees |

|                  | Gain Step Switching Time          |                                       |                    | 20                 |                    | ns      |

|                  | Enable/ Disable Time              | Settled to 90% level                  |                    | 15                 |                    | ns      |

| POWER            | REQUIREMENTS                      |                                       |                    |                    |                    |         |

| ICC              | Supply Current                    |                                       |                    | 200                | 270                | mA      |

| Р                | Power                             |                                       |                    | 1                  |                    | W       |

| ICC              | Disabled Supply Current           |                                       |                    | 25                 |                    | mA      |

| ALL DIG          | GITAL INPUTS                      |                                       |                    |                    |                    |         |

|                  | Logic Compatibility               | TTL, 2.5 V CMOS, 3.3 V CMOS, 5 V CMOS | 5                  |                    |                    |         |

| VIL              | Logic Input Low Voltage           |                                       |                    | 0.4                |                    | V       |

| VIH              | Logic Input High Voltage          |                                       |                    | 2.0-5.0            |                    | V       |

| IIH              | Logic Input High Input Current    |                                       |                    | -9                 |                    | μA      |

| IIL              | Logic Input Low Input Current     |                                       |                    | -47                |                    | μA      |

| PARALI           | LEL MODE TIMING                   |                                       |                    |                    |                    |         |

| t <sub>GS</sub>  | Setup Time                        |                                       |                    | 3                  |                    | ns      |

| t <sub>GH</sub>  | Hold Time                         |                                       |                    | 3                  |                    | ns      |

| SERIAL           | MODE                              |                                       |                    |                    |                    |         |

| f <sub>CLK</sub> | SPI Clock Frequency               | 50% duty cycle, ATE tested @ 10 MHz   | 10                 | 50                 |                    | MHz     |

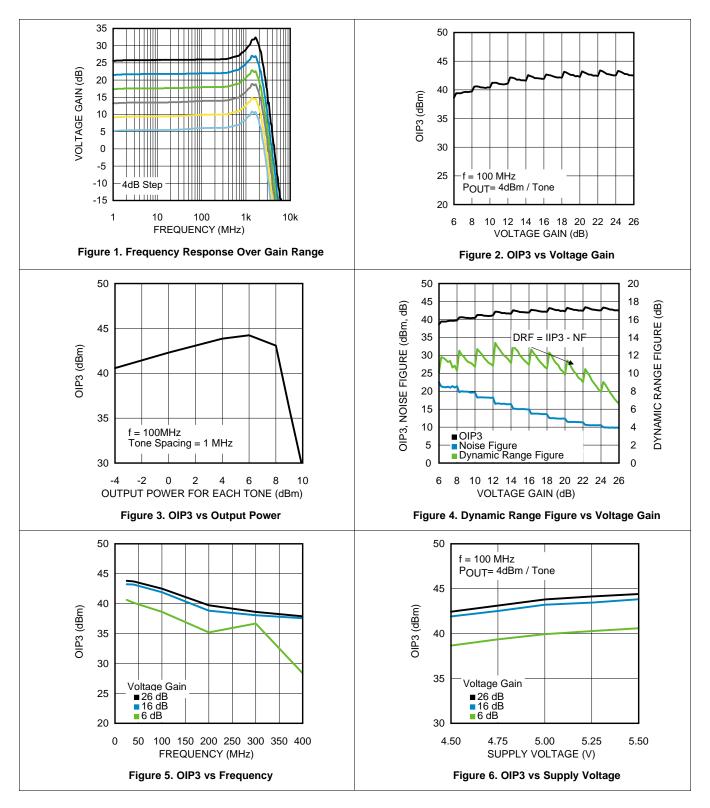

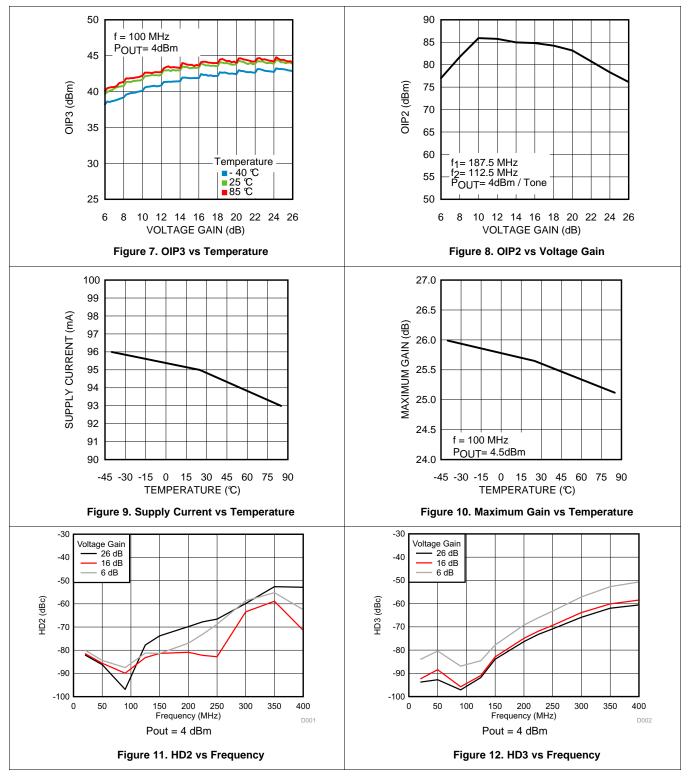

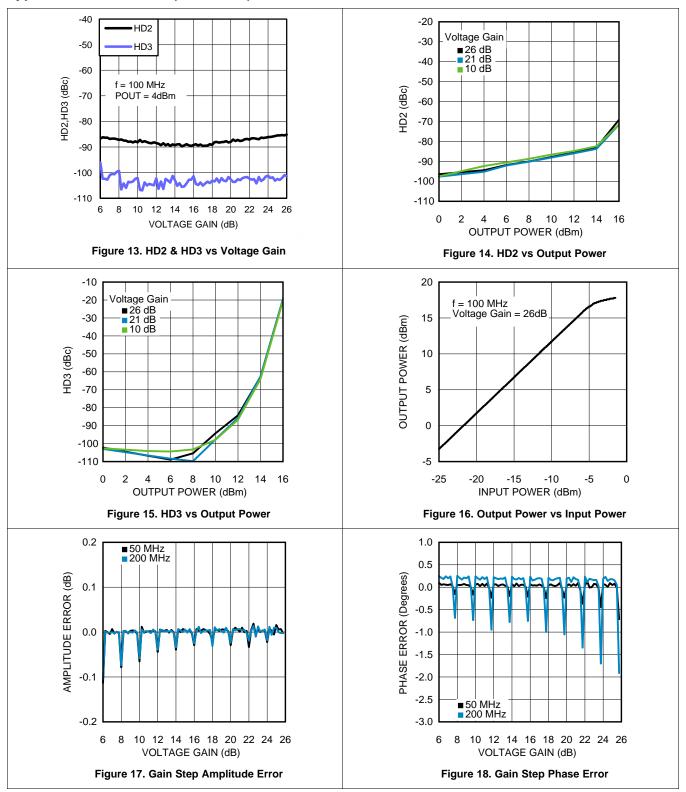

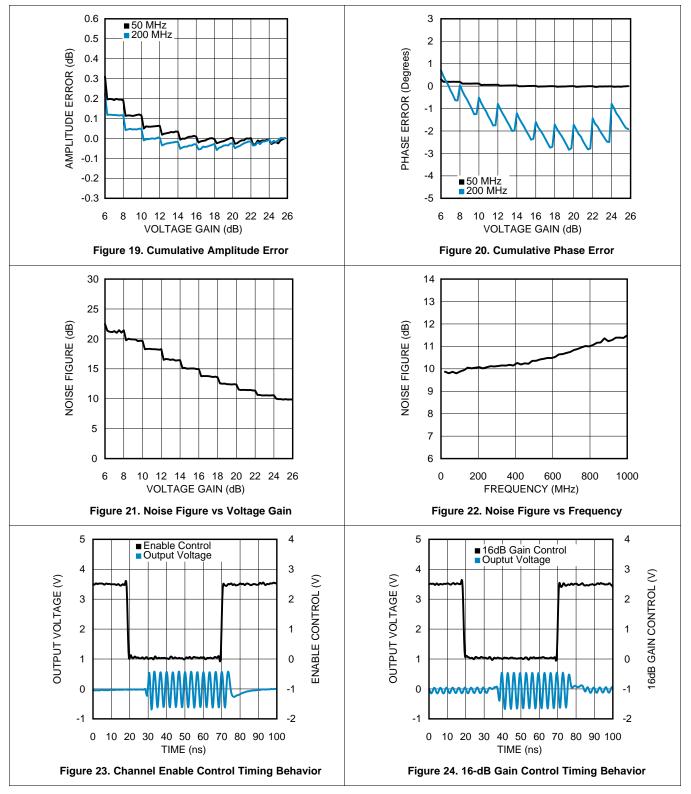

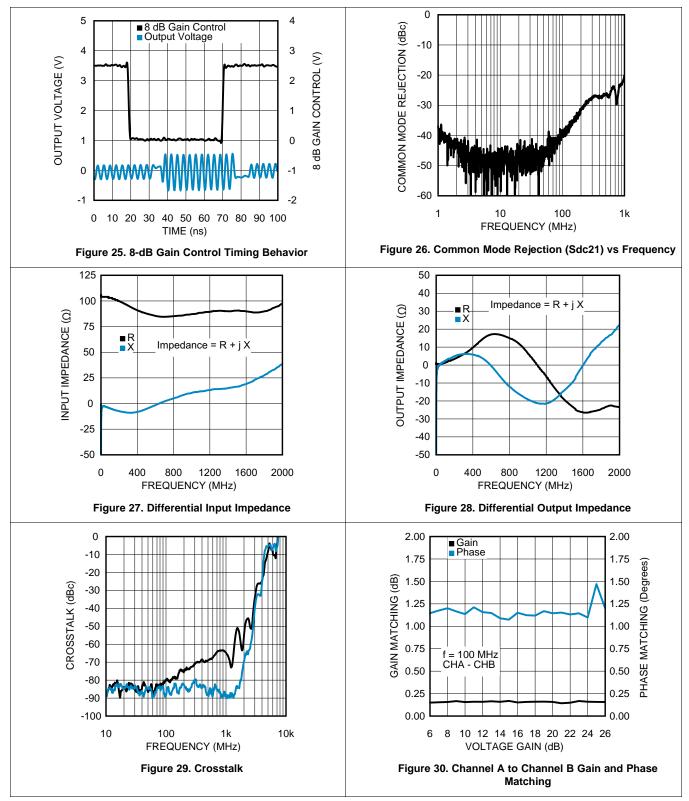

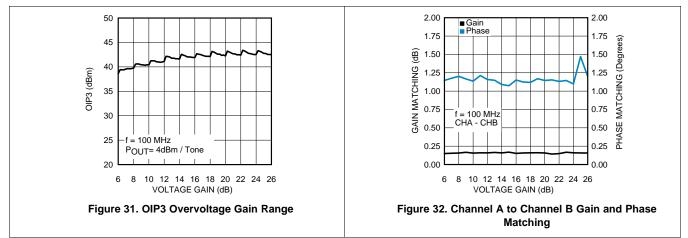

### 6.6 Typical Characteristics

(Unless otherwise specified, the following conditions apply:  $T_A = 25^{\circ}C$ , VCC = 5 V,  $R_L = 200 \Omega$ , Maximum Gain, Differential Input.)<sup>(8)</sup>

(8) LMH6881 devices have been used for some typical performance plots.

#### 6.6.1 Single-Ended Input

(Unless otherwise specified, the following conditions apply:  $T_A = 25^{\circ}C$ , VCC = 5 V,  $R_L = 200\Omega$ , Maximum Gain, Differential Input).

## 7 Detailed Description

### 7.1 Overview

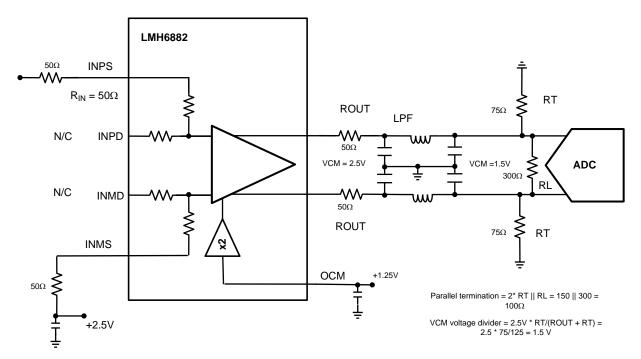

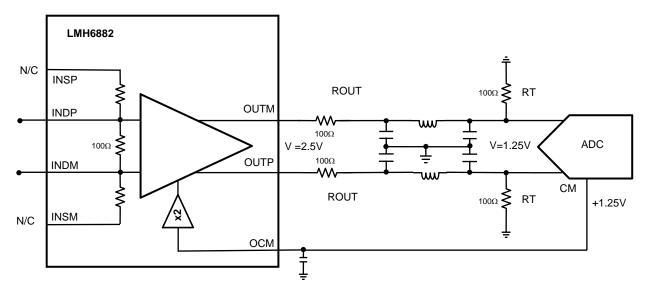

The LMH6882 has been designed to replace traditional, fixed-gain amplifiers, as well as variable-gain amplifiers, with an easy-to-use device which can be flexibly configured to many different gain settings while maintaining excellent performance over the entire gain range. Many systems can benefit from this programmable-gain, DC-capable, differential amplifier. Last minute design changes can be implemented immediately, and external resistors are not required to set the gain. Gain control is enabled with a parallel- or a serial-control interface and as a result, the amplifier can also serve as a digitally controlled variable-gain amplifier (DVGA) for automatic gain control applications. Figure 50 and Figure 53 show typical implementations of the amplifier.

The LMH6882 is a fully differential amplifier optimized for signal path applications up to 1000 MHz. The LMH6882 has a 100- $\Omega$  input impedance and a low (less than 0.5  $\Omega$ ) impedance output. The gain is digitally controlled over a 20 dB range from 26 dB to 6 dB. The LMH6882 is designed to replace fixed-gain differential amplifiers with a single, flexible-gain device. It has been designed to provide good noise figure and OIP3 over the entire gain range. This design feature is highlighted by the Dynamic Range Figure of merit (DRF). Traditional variable gain amplifiers generally have the best OIP3 and NF performance at maximum gain only.

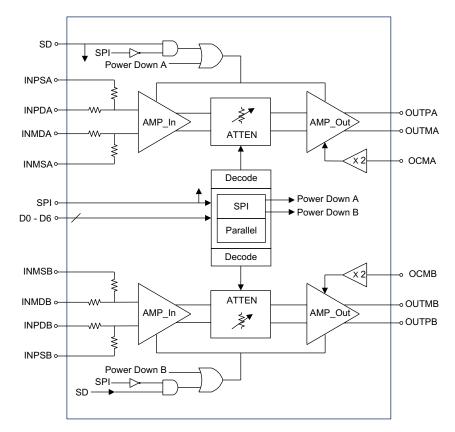

# 7.2 Functional Block Diagram

### 7.3 Feature Description

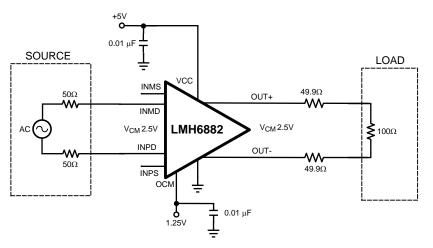

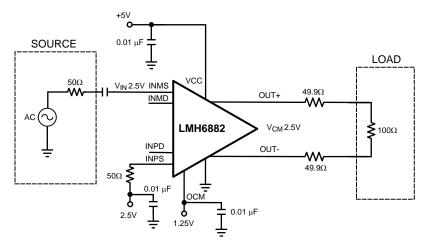

The LMH6882 has three functional stages, a low-noise amplifier, followed by a digital attenuator, and a lowdistortion, low-impedance output amplifier. The amplifier has four signal input pins to accommodate both differential signals and single-ended signals. The amplifier has an OCM pin used to set the output common-mode voltage. There is a gain of 2 on this pin so that 1.25 V applied on that pin will place the output common mode at 2.5 V.

#### **Feature Description (continued)**

Figure 39. Typical Implementation With a Differential Input Signal

Figure 40. Typical Implementation With a Single-Ended Input Signal

#### 7.4 Device Functional Modes

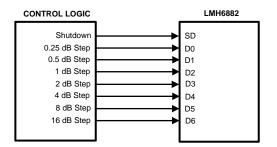

The LMH6882 will support two modes of control for its gain: a parallel mode and a serial mode (SPI compatible). Parallel mode is fastest and requires the most board space for logic line routing. Serial mode is compatible with existing SPI-compatible systems. The device has gain settings covering a range of 20 dB. In parallel mode, only 2-dB steps are available. The serial interface should be used for finer gain control of 0.25 dB for a gain between 6 dB and 26 dB of voltage gain. If fixed gain is desired, the digital pins can be strapped to ground or VCC, as required.

The device also supports two modes of power down control to enable power savings when the amplifier is not being used: using the SD pin (when SPI pin = Logic 0) and the power-down register (when SPI pin = Logic 1).

### 7.5 Programming

#### 7.5.1 Digital Control of the Gain and Power-Down Pins

The LMH6882 was designed to interface with 2.5-V to 5-V CMOS logic circuits. If operation with 5-V logic is required care should be taken to avoid signal transients exceeding the amplifier supply voltage. Long, unterminated digital signal traces should be avoided. Signal voltages on the logic pins that exceed the device power-supply voltage may trigger ESD protection circuits and cause unreliable operation. Some digital input-output pins have different functions depending on the digital control mode. Table 1 shows the mapping of the digital pins. These functions for each pin will be described in the sections *Parallel Interface* and *SPI-Compatible Serial Interface*.

While the full gain range is available in parallel mode both channels must be set to the same gain. If independent channel control is desired, SPI mode must be used.

| PIN | SPI = 0 | SPI = 1            |

|-----|---------|--------------------|

| 7   | D1      | SDI                |

| 14  | D0      | SDO <sup>(1)</sup> |

| 8   | D2      | CLK                |

| 9   | D3      | CS (active low)    |

#### Table 1. Pins With Dual Functions

(1) Pin 14 requires external bias. See *SPI-Compatible Serial Interface* for details.

#### 7.5.2 Parallel Interface

Parallel mode offers the fastest gain update capability with the drawback of requiring the most board space dedicated to control lines. To place the LMH6882 into parallel mode the SPI pin (pin 27) is set to the logical zero state. Alternately, the SPI pin can be connected directly to ground. The SPI pin has a weak internal resistor to ground. If left unconnected, the amplifier will operate in parallel mode.

In parallel mode the gain can be changed in 0.25-dB steps with a 7-bit gain control bus. The attenuator control pins are internally biased to logic high state with weak pull-up resistors, with the exception of D0 (pin 14) which is biased low due to the shared SDO function. If the control bus is left unconnected, the amplifier gain will be set to 6 dB. Table 2 shows the gain of the amplifier when controlled in parallel mode.

The LMH6882 has a 7-bit gain control bus. Data from the gain control pins is immediately sent to the gain circuit (that is, gain is changed immediately). To minimize gain change glitches all gain pins should change at the same time. Gain glitches could result from timing skew between the gain set bits. This is especially the case when a small gain change requires a change in state of three or more gain control pins. If necessary the PDA could be put into a disabled state while the gain pins are reconfigured and then brought active when they have settled.

| PIN                       | NAME                                        | GAIN STEP SIZE (dB)                   |

|---------------------------|---------------------------------------------|---------------------------------------|

| 14                        | D0                                          | 0.25                                  |

| 7                         | D1                                          | 0.5                                   |

| 8                         | D2                                          | 1                                     |

| 9                         | D3                                          | 2                                     |

| 21                        | D4                                          | 4                                     |

| 20                        | D5                                          | 8                                     |

| 19                        | D6                                          | 16                                    |

| Coin combinations that av | acad 90 will recult in minimum acin of 6 dP | · · · · · · · · · · · · · · · · · · · |

#### Table 2. Gain Change Values for the Parallel-Gain Pins

Gain combinations that exceed 80 will result in minimum gain of 6 dB.

| CON | TROL PIN | S LOGICA | L LEVEL<br>CAF |    | EL MODE. () |    | GAIN = 26 - 0.25 × DECIMAL VALUE AND GAIN<br>≥ 6 dB |                             |

|-----|----------|----------|----------------|----|-------------|----|-----------------------------------------------------|-----------------------------|

| D6  | D5       | D4       | D3             | D2 | D1          | D0 | Decimal/<br>Hex<br>Value                            | Amplifier Voltage Gain (dB) |

| 0   | 0        | 0        | 0              | 0  | 0           | 0  | 0 / 0                                               | 26                          |

| 0   | 0        | 0        | 0              | 0  | 0           | 1  | 1/1                                                 | 25.75                       |

| 0   | 0        | 0        | 0              | 0  | 1           | 0  | 2/2                                                 | 25.5                        |

| 0   | 0        | 0        | 0              | 0  | 1           | 1  | 3/3                                                 | 25.25                       |

| 0   | 0        | 0        | 0              | 1  | 0           | 0  | 4 / 4                                               | 25                          |

| 0   | 0        | 0        | 0              | 1  | 0           | 1  | 5/5                                                 | 24.75                       |

| 0   | 0        | 0        | 0              | 1  | 1           | 0  | 6 / 5                                               | 24.5                        |

| 0   | 0        | 0        | 0              | 1  | 1           | 1  | 7/7                                                 | 24.25                       |

| 0   | 0        | 0        | 1              | 0  | 0           | 0  | 8 / 8                                               | 24                          |

| 0   | 0        | 1        | 0              | 0  | 0           | 0  | 16 / 10                                             | 22                          |

| 0   | 0        | 1        | 1              | 0  | 0           | 0  | 24 / 18                                             | 20                          |

| 0   | 1        | 0        | 0              | 0  | 0           | 0  | 32 / 20                                             | 18                          |

| 0   | 1        | 0        | 1              | 0  | 0           | 0  | 40 / 28                                             | 16                          |

| 0   | 1        | 1        | 0              | 0  | 0           | 0  | 48 / 30                                             | 14                          |

| 0   | 1        | 1        | 1              | 0  | 0           | 0  | 56 / 38                                             | 12                          |

| 1   | 0        | 0        | 0              | 0  | 0           | 0  | 64 / 40                                             | 10                          |

| 1   | 0        | 0        | 1              | 0  | 0           | 0  | 72 / 48                                             | 8                           |

| 1   | 0        | 1        | 0              | 0  | 0           | 0  | 80 / 50                                             | 6                           |

| 1   | 0        | 1        | Х              | Х  | Х           | Х  | > 80 / 50                                           | 6                           |

| 1   | 1        | Х        | Х              | Х  | Х           | Х  | > 80 / 50                                           | 6                           |

#### Table 3. Amplifier Gain for Selected Control Pin Combinations

For fixed-gain applications the attenuator control pins should be connected to the desired logic state instead of relying on the weak internal bias. Data from the gain-control pins directly drive the amplifier gain circuits. To minimize gain change glitches all gain pins should be driven with minimal skew. If gain-pin timing is uncertain, undesirable transients can be avoided by using the shutdown pin to disable the amplifier while the gain is changed. Gain glitches are most likely to occur when multiple bits change value for a small gain change, such as the gain change from 10 dB to 12 dB which requires changing all 4 gain control pins.

A shutdown pin (SD == 0, amplifier on, SD == 1, amplifier off) is provided to reduce power consumption by disabling the highest power portions of the amplifier. The digital control circuit is not shut down and will preserve the last active gain setting during the disabled state. See the *Typical Characteristics* section for disable and enable timing information. The SD pin is functional in parallel mode only and disabled in serial mode.

Figure 41. Parallel Mode Connection

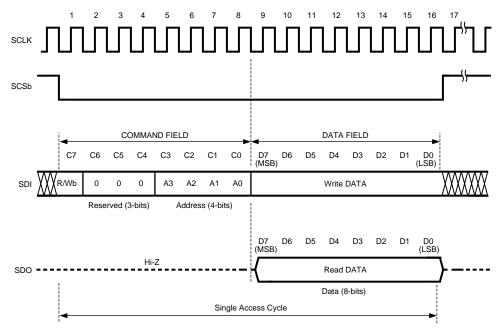

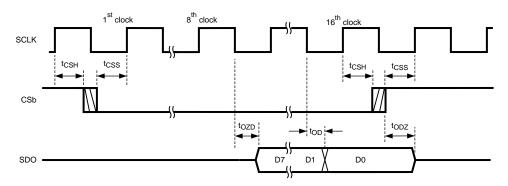

#### 7.5.3 SPI-Compatible Serial Interface

The serial interface allows a great deal of flexibility in gain programming and reduced board complexity. The LMH6882 serial interface is a generic 4-wire synchronous interface compatible with SPI type interfaces that are used on many microcontrollers and DSP controllers. Using only 4 wires, the SPI mode offers access to the 0.25-dB gain steps of the amplifier.

For systems where gain is changed only infrequently, or where only slower gain changes are required, serial mode is the best choice. To place the LMH6882 into serial mode the SPI pin (Pin 27) should be put into the logic high state. Alternatively the SPI pin can be connected directly to the 5-V supply bus. In this configuration the pins function as shown in Table 2. The SPI interface uses the following signals: clock input (CLK); serial data in (SDI); serial data out (SDO); and serial chip select (CS). The chip-select pin is active low meaning the device is selected when the pin is low.

The SD pin is inactive in the serial mode. This pin can be left disconnected for serial mode. The SPI interface has the ability to shutdown the amplifier without using the SD pin.

The CLK pin is the serial clock pin. It is used to register the input data that is presented on the SDI pin on the rising edge and to source the output data on the SDO pin on the falling edge. The user may disable clock and hold it in the low state, as long as the clock pulse-width minimum specification is not violated when the clock is enabled or disabled. The clock pulse-width minimum is equal to one setup plus one hold time, or 6 ns.

The CS pin is the chip-select pin. This pin is active low; the chip is selected in the logic low state. Each assertion starts a new register access - i.e., the SDATA field protocol is required. The user is required to de-assert this signal after the 16th clock. If the CS pin is de-asserted before the 16th clock, no address or data write will occur. The rising edge captures the address just shifted in and, in the case of a write operation, writes the addressed register. There is a minimum pulse-width requirement for the deasserted pulse - which is specified in the Electrical Characteristics section.

The SDI pin is the input pin for the serial data. It must observe setup / hold requirements with respect to the SCLK. Values can be found in the *Electrical Characteristics* table (refer to electrical table of the DS). Each write cycle is 16-bit long.

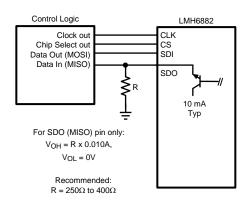

The SDO pin is the data output pin. This output is normally at a high-impedance state, and is driven only when CS is asserted. Upon CS assertion, contents of the register addressed during the first byte are shifted out with the second 8 SCLK falling edges. The SDO pin is a current output and requires external bias resistor to develop the correct logic voltage. See Figure 43 for details on sizing the external bias resistor. Resistor values of 180  $\Omega$  to 400  $\Omega$  are recommended. The SDO pin can source 10 mA in the logic high state. With a bias resistor of 250  $\Omega$  the logic 1 voltage would be 2.5 V. In the logic 0 state, the SDO output is off, and no current flows, so the bias resistor will pull the voltage to 0 V.

Each serial interface access cycle is exactly 16 bits long as shown in Figure 42. Each signal's function is described below. the read timing is shown in Figure 44.

The external bias resistor means that in the high impedance state the SDO pin impedance is equal to the external bias resistor value. If bussing multiple SPI devices make sure that the SDO pins of the other devices can drive the bias resistor.

The serial interface has 6 registers with address [0] to address [6]. Table 4 shows the content of each SPI register. Registers 0 and 1 are read only. Registers 2 through 6 are read/write and control the gain and power of the amplifier. Register contents and functions are detailed below.

| Address | R/W | Name            | Default Value Hex (Dec) |

|---------|-----|-----------------|-------------------------|

| 0       | R   | Revision ID     | 1 (1)                   |

| 1       | R   | Product ID      | 21 (33)                 |

| 2       | R/W | Power Control   | 0 (0)                   |

| 3       | R/W | Attenuation A   | 50 (80)                 |

| 4       | R/W | Attenuation B   | 50 (80)                 |

| 5       | R/W | Channel Control | 3 (3)                   |

#### Table 4. SPI Registers by Address and Function

#### Table 5. Serial Word Format for Register 2: Power Control

| 7                                                   | 6   | 5    | 4    | 3    | 2    | 1   | 0   |

|-----------------------------------------------------|-----|------|------|------|------|-----|-----|

| RES                                                 | RES | CHA1 | CHB1 | CHA2 | CHB2 | RES | RES |

| CHA1 and CHA2 = 0 for ON, CHA1 and CHA2 = 1 for OFF |     |      |      |      |      |     |     |

| CHB1 and CHB2 = 0 for ON, CHB1 and CHB2 = 1 for OFF |     |      |      |      |      |     |     |

#### Table 6. Serial Word Format for Registers 3, 4: Gain Control

| 7   | 6                                                          | 5 | 4 | 3 | 2 | 1 | 0 |

|-----|------------------------------------------------------------|---|---|---|---|---|---|

| RES | Gain = 26 — (register value * 0.25) valid range is 0 to 80 |   |   |   |   |   |   |

#### Table 7. Serial Word Format for Register 5: Channel Control

| 7   | 6 | 5 | 4 | 3 | 2    | 1      | 1      |

|-----|---|---|---|---|------|--------|--------|

| RES |   |   |   |   | SYNC | Load A | Load B |

The Channel Control register controls how registers 3 and 4 work. When the SYNC bit is set to 1 both channel A and channel B are set to the gain indicated in register 3. When the SYNC bit is set to zero, register 3 controls channel A, and register 4 controls channel B. When the Load A bit is zero data written to register 3 does not transfer to channel A. When the Load A bit is set to 1 the gain of channel A is set equal to the value indicated in register 3. The Load B bit works the same for channel B and register 4.

Figure 42. Serial Interface Protocol (SPI Compatible)

| R/Wb     | Read / Write bit. A value of 1 indicates a read operation, while a value of 0 indicates a write operation.                                                                    |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reserved | Not used. Must be set to 0.                                                                                                                                                   |

| ADDR:    | Address of register to be read or written.                                                                                                                                    |

| DATA     | In a write operation the value of this field will be written to the addressed register when the chip-<br>select pin is deasserted. In a read operation this field is ignored. |

### 8 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

#### 8.1 Application Information

#### 8.1.1 Input Characteristics

The LMH6882 has internally terminated inputs. The INMD and INPD pins are intended to be the differential input pins and have an internal  $100-\Omega$  resistive termination. An example differential circuit is shown in Figure 39. When using the differential inputs, the single-ended inputs should be left disconnected.

The INMS and INPS pins are intended for use as single-ended inputs and have been designed to support singleended termination of 50  $\Omega$  working as an active termination. For single-ended signals an external 50- $\Omega$  resistor is required as shown in Figure 40. When using the single-ended inputs, the differential inputs should be left disconnected.

All of the input pins are self biased to 2.5 V. When using the LMH6882 for DC-coupled applications, it is possible to externally bias the input pins to voltages from 1.5 V to 3.5 V. Performance is best at the 2.5-V level specified. Performance will degrade slightly as the common mode shifts away from 2.5 V.

The first stage of the LMH6882 is a low-noise amplifier that can accommodate a maximum input signal of 2  $V_{ppd}$  on the differential input pins and 1  $V_{pp}$  on either of the single-ended pins. Signals larger than this will cause severe distortion. Although the inputs are protected against ESD, sustained electrical overstress will damage the part. Signal power over 13 dBm should not be applied to the amplifier differential inputs continuously. On the single-ended pins the power limit is 10 dBm for each pin.

#### 8.1.2 Output Characteristics

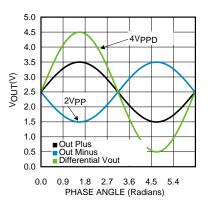

The LMH6882 has a low-impedance output very similar to a traditional Op-amp output. This means that a wide range of loads can be driven with good performance. Matching load impedance for proper termination of filters is as easy as inserting the proper value of resistor between the filter and the amplifier (See Figure 50 for example.) This flexibility makes system design and gain calculations very easy. By using a differential output stage the LMH6882 can achieve large voltage swings on a single 5-V supply. This is illustrated in Figure 45. This figure shows how a voltage swing of 4 V<sub>ppd</sub> is realized while only swinging 2 V<sub>pp</sub> on each output. A 1-V<sub>p</sub> signal on one branch corresponds to 2 V<sub>pp</sub> on that branch and 4 V<sub>ppd</sub> when looking at both branches (positive and negative).

Figure 45. Differential Output Voltage

# **Application Information (continued)**

The LMH6882 has been designed for both AC-coupled and DC-coupled applications. To give more flexibility in DC-coupled applications, the common-mode voltage of the output pins is set by the OCM pin. The OCM pin needs to be driven from an external low-noise source. If the OCM pin is left floating, the output common-mode is undefined, and the amplifier will not operate properly.

There is a DC gain of 2 between the OCM pin and the output pins so that the OCM voltage should be between 1 V and 1.5 V. This will set the output common mode voltage between 2 V and 3 V. Output common-mode voltages outside the recommended range will exhibit poor voltage swing and distortion performance. The amplifier will give optimum performance when the output common mode is set to half of the supply voltage (2.5 V or 1.25 V at the OCM pin).

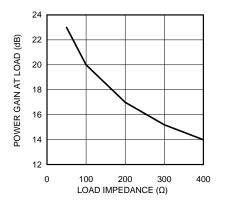

The ability of the LMH6882 to drive low-impedance loads while maintaining excellent OIP3 performance creates an opportunity to greatly increase power gain and drive low-impedance filters. This gives the system designer much needed flexibility in filter design. In many cases using a lower impedance filter will provide better component values for the filter. Another benefit of low-impedance filters is that they are less likely to be influenced by circuit board parasitic reactances such as pad capacitance or trace inductance. The output stage is a low-impedance voltage amplifier, so voltage gain is constant over different load conditions. Power gain will change based on load conditions. See Figure 46 for details on power gain with respect to different load conditions. The graph was prepared for the 26 dB voltage gain. Other gain settings will behave similarly.

All measurements in this data sheet, unless specified otherwise, refer to voltage or power at the device output pins. For instance, in an OIP3 measurement the power out will be equal to the output voltage at the device pins squared, divided by the total load voltage. In back-terminated applications, power to the load would be 3 dB less. Common back-terminated applications include driving a matched filter or driving a transmission line.

Figure 46. Power Gain as a Function of the Load

Printed circuit board (PCB) design is critical to high-frequency performance. In order to ensure output stability the load-matching resistors should be placed as close to the amplifier output pins as possible. This allows the matching resistors to mask the board parasitics from the amplifier output circuit. An example of this is shown in Figure 50. Also note that the low-pass filters in Figure 48 and Figure 49 use center-tapped capacitors. Having capacitors to ground provides a path for high-frequency, common-mode energy to dissipate. This is equally valuable for the ADC, so there are also capacitors to ground on the ADC side of the filter. The LMH6882EVAL evaluation board is available to serve a guide for system board layout. See also application note AN-2235 (SNOA869) for more details.

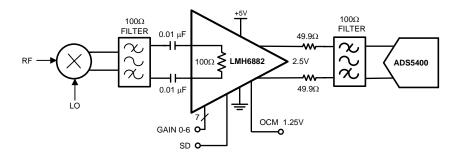

#### 8.1.3 Interfacing to an ADC

The LMH6882 is an excellent choice for driving high-speed ADCs such as the ADC12D1800RF, ADC12D1600RF or the ADS5400. The following sections will detail several elements of ADC system design, including noise filters, AC, and DC coupling options.

### **Application Information (continued)**

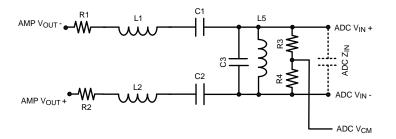

#### 8.1.3.1 ADC Noise Filter

When connecting a broadband amplifier to an analog to digital converter it is nearly always necessary to filter the signal before sampling it with the ADC. Figure 47 shows a schematic of a second order Butterworth filter and Table 8 shows component values for some common IF frequencies. These filters, shown in Table 8, offer a good compromise between bandwidth, noise rejection and cost. This filter topology is the same as is used on the ADC14V155KDRB High IF Receiver reference design board. This filter topology is adequate for reducing aliasing of broadband noise and will also provide rejection of harmonic distortion and many of the images that are commonly created by mixers.

Figure 47. Sample Filter

| CENTER<br>FREQUENCY | BANDWIDTH | R1, R2 | L1, L2 | C1, C2 | С3    | L5     | R3, R4 |

|---------------------|-----------|--------|--------|--------|-------|--------|--------|

| 75 MHz              | 40 MHz    | 90 Ω   | 390 nH | 10 pF  | 22 pF | 220 nH | 100 Ω  |

| 150 MHz             | 60 MHz    | 90 Ω   | 370 nH | 3 pF   | 19 pF | 62 nH  | 100 Ω  |

| 180 MHz             | 75 MHz    | 90 Ω   | 300 nH | 2.7 pF | 15 pF | 54 nH  | 100 Ω  |

| 250 MHz             | 100 MHz   | 90 Ω   | 225 nH | 1.9 pF | 11 pF | 36 nH  | 100 Ω  |

#### Table 8. Filter Component Values<sup>(1)</sup>

(1) Resistor values are approximate, but have been reduced due to the internal 10  $\Omega$  of output resistance per pin.

### 8.1.3.2 AC Coupling to an ADC

AC coupling is an effective method for interfacing to an ADC for many communications systems. In many applications this will be the best choice. The LMH6882 evaluation board is configured for AC coupling as shipped from the factory. Coupling with capacitors is usually the most cost-effective method. Transformers can provide both AC coupling and impedance transformation as well as single-ended-to-differential conversion. One of the key benefits of AC coupling is that each stage of the system can be biased to the ideal DC operating point. Many systems operate with lower overall power dissipation when DC bias currents are eliminated between stages.

### 8.1.3.3 DC Coupling to an ADC

The LMH6882 supports DC-coupled signals. In order to successfully implement a DC-coupled signal chain the common-mode voltage requirements of every stage need to be met. This requires careful planning, and in some cases there will be signal-level, gain or termination compromises required to meet the requirements of every part. Shown in Figure 48 and Figure 49 is a method using resistors to change the 2.5-V common mode of the amplifier output to a common mode compatible for the input of a low-input voltage ADC such as the ADC12D1800RF. This DC level shift is achieved while maintaining an AC impedance match with the filter in Figure 48 while in Figure 49 there is a small mismatch between the amplifier termination resistors and the ADC input. Because there is no universal ADC input common mode, and some ADC's have impedance controlled input, each design will require a different resistor ratio. For high-speed data-conversion systems it is very important to keep the physical distance between the amplifier and the ADC electrically short. When connections between the amplifier and the ADC are electrically short, termination mismatches are not critical.

Figure 48. DC-Coupled ADC Driver Example 1, High Input Impedance ADC

#### 8.1.4 Figure of Merit: Dynamic Range Figure

The dynamic range figure (DRF) as illustrated in Figure 4, is defined as the input third order intercept point (IIP3) minus the noise figure (NF). The combination of noise figure and linearity gives a good proxy for the total dynamic range of an amplifier. In some ways this figure is similar to the SFDR of an analog to digital converter. In contrast to an ADC, however, an amplifier will not have a full-scale input to use as a reference point. With amplifiers, there is no one point where signal amplitude hits "full scale". Yet, there are real limitations to how large a signal the amplifier can handle. Normally, the distortion products produced by the amplifier will determine the upper limit to signal amplitude. The intermodulation intercept point is an imaginary point that gives a well-understood figure of merit for the maximum signal an amplifier can handle. For low-amplitude signals the noise figure gives a threshold of the lowest signal that the amplifier can reproduce. By combining the third-order input intercepts point and the noise figure the DRF gives a very good indication of the available dynamic range offered.

# Table 9. Compatible High-Speed Analog-to-Digital Converters

| PRODUCT NUMBER | MAX SAMPLING RATE (MSPS) | RESOLUTION | CHANNELS |

|----------------|--------------------------|------------|----------|

| ADC12D1800RF   | 1800                     | 12         | DUAL     |

| ADC12D1600RF   | 1600                     | 12         | DUAL     |

| ADC12D1000RF   | 1000                     | 12         | DUAL     |

| ADS5400        | 1000                     | 12         | SINGLE   |

| ADC12D1800     | 1800                     | 12         | DUAL     |

| ADC12D1600     | 1600                     | 12         | DUAL     |

| ADC12D1000     | 1000                     | 12         | DUAL     |

| ADC10D1000     | 1000                     | 10         | DUAL     |

| ADC10D1500     | 1500                     | 10         | DUAL     |

| ADC12C105      | 105                      | 12         | SINGLE   |

| ADC12C170      | 170                      | 12         | SINGLE   |

| ADC12V170      | 170                      | 12         | SINGLE   |

| ADC14C080      | 80                       | 14         | SINGLE   |

| ADC14C105      | 105                      | 14         | SINGLE   |

| ADC14DS105     | 105                      | 14         | DUAL     |

| ADC14155       | 155                      | 14         | SINGLE   |

| ADC14V155      | 155                      | 14         | SINGLE   |

| ADC16V130      | 130                      | 16         | SINGLE   |

| ADC16DV160     | 160                      | 16         | DUAL     |

| ADC08D500      | 500                      | 8          | DUAL     |

| ADC08500       | 500                      | 8          | SINGLE   |

| ADC08D1000     | 1000                     | 8          | DUAL     |

| ADC081000      | 1000                     | 8          | SINGLE   |

| ADC08D1500     | 1500                     | 8          | DUAL     |

| ADC081500      | 1500                     | 8          | SINGLE   |

| ADC08(B)3000   | 3000                     | 8          | SINGLE   |

| ADC08100       | 100                      | 8          | SINGLE   |

| ADCS9888       | 170                      | 8          | SINGLE   |

| ADC08(B)200    | 200                      | 8          | SINGLE   |

| ADC11C125      | 125                      | 11         | SINGLE   |

| ADC11C170      | 170                      | 11         | SINGLE   |

|                |                          |            |          |

### 8.2 Typical Applications

### 8.2.1 LMH6882 Typical Application

Figure 50. LMH6882 Typical Application

#### 8.2.1.1 Design Requirements

Figure 50 shows a design example for an IF amplifier in a typical direct-IF receiver application and LMH6881 meets these requirements.

| 1 0                                                                         | • • •                                                                                  |  |  |

|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--|--|

| SPECIFICATION                                                               | EXAMPLE DESIGN REQUIREMENT                                                             |  |  |

| Supply Voltage and Current                                                  | 4.75V to 5.25V, with a minimum 150-mA supply current                                   |  |  |

| Input structure and Impedance                                               | DC coupled Single-ended or Differential with 100 $\Omega$ input differential impedance |  |  |

| Output control                                                              | DC coupled with output common mode control capability                                  |  |  |

| RF input frequency range                                                    | DC to 250MHz                                                                           |  |  |

| Voltage Gain Range                                                          | 26dB to 6dB                                                                            |  |  |

| OIP3 in RF input frequency range for Pout = 4dBm/tone with $RL = 200\Omega$ | > 38 dBm at 200MHz for Max Gain                                                        |  |  |

| Noise Figure                                                                | < 12dB at Max Gain across RF input frequency                                           |  |  |

| Attenuation Control                                                         | Parallel control as well as SPI control                                                |  |  |

#### Table 10. Example Design Requirement for an IF Receiver Application

#### 8.2.1.2 Detailed Design Procedure

The LMH6882 device can be included in most receiver applications by following these basic procedures:

- Select an appropriate input drive circuitry to the LMH6882 by frequency planning the signal chain properly such that the down-converted input signal is within the input frequency specifications of the device. Identify whether dc-or ac-coupling is required or filtering is needed to optimize the system. Follow the guidelines mentioned in *Input Characteristics* for interfacing the LMH6882 inputs.

- Choose the right speed grade ADC that meets the signal bandwidth application. Based upon the noise filtering and anti-aliasing requirement, determine the right order & type for the anti-aliasing filter. Follow the guidelines mentioned in *Output Characteristics* and *Interfacing to an ADC* when interfacing the device to an anti-aliasing filter.

- Optimize the signal chain gain leading up to the ADC for best SNR and SFDR performance by employing the device in automatic gain control (AGC) loop using serial or parallel digital interface.

- While interfacing the digital inputs, verify the electrical and functional compatibility of the LMH6882 digital input pins with the external micro-controller (μC).

- Choose the appropriate power-supply architecture and supply bypass filtering devices to provide stable, low noise supplies as mentioned in the *Power Supply Recommendations*.

#### 8.2.1.3 Application Curves

#### 8.2.2 LMH6882 Used as Twisted Pair Cable Driver

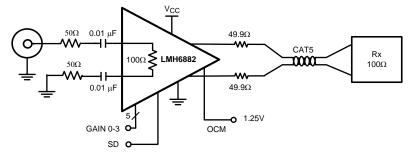

Figure 53. LMH6882 Used as Twisted Pair Cable Driver

### 8.2.2.1 Design Requirements

Table 11 shows a design example for LMH6882 used as cable driver for driving un-shielded twisted pair (UTP) CAT-5 cables.

| SPECIFICATION                        | EXAMPLE DESIGN REQUIREMENT                             |  |  |  |

|--------------------------------------|--------------------------------------------------------|--|--|--|

| Supply Voltage and Current           | 4.75 V to 5.25 V, with a minimum 150-mA supply current |  |  |  |

| Input to Output Device Configuration | Single-ended input to differential output              |  |  |  |

| Input frequency range                | 0.1 to 100 MHz                                         |  |  |  |

| Voltage Gain Range                   | 26-dB to 6-dB gain range                               |  |  |  |

| Output voltage swing                 | 4 Vppdiff into a 200- $\Omega$ load at the output      |  |  |  |

| Cable length to be driven            | 300 to 400 feet                                        |  |  |  |

#### Table 11. Example Design Requirement for a Cable Driver

#### 8.2.2.2 Detailed Design Procedure

The LMH6882 device can be used as a cable driver to drive (UTP) CAT-5 cable by following these basic procedures:

Select an appropriate input buffer or drive circuitry to the LMH6882 that provides pre-equalization in the frequency range of interest that needs to be driven down the CAT-5 cable. The cable usually presents attenuation of the signal at the receive end which is proportional to the length of the cable and the frequency being transmitted. In some cases, use of the pre-equalization buffer is not possible which mandates the use of a post-equalizer at the receive end to gain up the received signal.

LMH6882

SNOSC84D - AUGUST 2012 - REVISED FEBRUARY 2015

- Determine the maximum output swing required to be transmitted in-order to receive the signal with good signal integrity. When driving long cable lengths, there is a possibility of corruption of differential signals due to common mode signals which requires the use of devices that offer good common mode rejection. Also, care must be taken to match the source impedance with the characteristic impedance of the CAT-5 cable to minimize signal reflections at higher frequencies. The LMH6882 offers low differential output resistance that makes source matching of driven cable very convenient.

- Verify the electrical and functional compatibility when interfacing LMH6882 digital input pins with the external micro-controller (μC).

- Also, use appropriate power-supply architecture and supply bypass filtering devices to provide stable, low noise supplies as mentioned in the *Power Supply Recommendations*.

#### 8.2.2.3 Application Curves

### 9 Power Supply Recommendations

The LMH6882 was designed to be operated on 5-V power supplies. The voltage range for VCC is 4.75 V to 5.25 V. Power supply accuracy of 5% or better is advised. When operated on a board with high-speed digital signals it is important to provide isolation between digital-signal noise and the analog input pins. The SP16160CH1RB reference board provides an example of good board layout.

Each power supply pin should be decoupled with a low inductance, surface-mount ceramic capacitor of approximately 10 nF as close to the device as possible. When vias are used to connect the bypass capacitors to a ground plane the vias should be configured for minimal parasitic inductance. One method of reducing via inductance is to use multiple vias. For broadband systems two capacitors per supply pin are advised.

To avoid undesirable signal transients the LMH6882 should not be powered on with large inputs signals present. Careful planning of system power-on sequencing is especially important to avoid damage to ADC inputs when an ADC is used in the application.

### 10 Layout

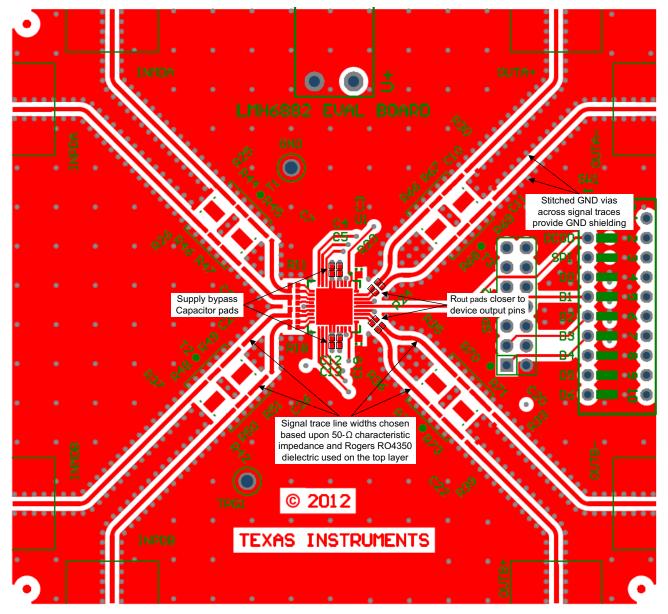

### 10.1 Layout Guidelines

It is very important to employ good high-speed layout techniques when dealing with devices having relatively high gain bandwidth in excess of 1GHz to ensure stability and optimum performance. The LMH6882 evaluation board provides a good reference for suggested layout techniques. The LMH6882 evaluation board was designed for both good signal integrity and thermal dissipation using higher performance (Rogers) dielectric on the top layer. The high performance dielectric provides well matched impedance and low loss to frequencies beyond 1GHz.

TI recommends that the LMH6882 board be multi-layered to improve thermal performance, grounding and power-supply decoupling. The LMH6882 evaluation board is an 8-layered board with the supply sandwiched inbetween the GND layers for decoupling and having the stack up as Top layer - GND - GND - GND - Supply - GND - GND - Bottom layer. All signal paths are routed on the top layer on the higher performance (Rogers) dielectric, while the remainder signal layers are conventional FR4.

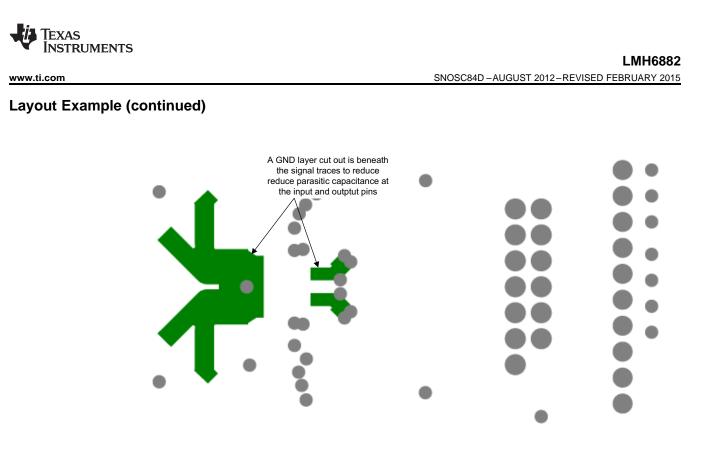

#### **10.1.1 Uncontrolled Impedance Traces**

It is important to pay careful attention while routing high-frequency signal traces on the PCB to maintain signal integrity. A good board layout software package can simplify the trace thickness design to maintain controlled characteristic impedances for high-frequency signals. Eliminating copper (the ground and power plane) from underneath the input and output pins of the device also helps in minimizing parasitic capacitance affecting the high frequency signals near the PCB and package junctions. The LMH6882 evaluation board has copper keep-out areas under both the input and the output traces for this purpose. It is recommended that the application board also follow these keep-out areas to avoid any performance degradation.

### 10.2 Layout Example

Figure 56. Top Layer

#### Figure 57. GND Layer

### **10.3 Thermal Considerations**

The LMH6882 is packaged in a thermally enhanced package. The exposed pad on the bottom of the package is the primary means of removing heat from the package. It is recommended, but not necessary, that the exposed pad be connected to the supply ground plane. In any case, the thermal dissipation of the device is largely dependent on the attachment of the exposed pad to the system printed circuit board (PCB). The exposed pad should be attached to as much copper on the PCB as possible, preferably external layers of copper.

TEXAS INSTRUMENTS

www.ti.com

### **11** Device and Documentation Support

### **11.1 Documentation Support**

#### 11.1.1 Related Documentation

For related documentation see the following:

AN-2235 Circuit Board Design for LMH6517/21/22 and Other High-Speed IF/RF Feedback Amplifiers, SNOA869

#### 11.2 Trademarks

SPI is a trademark of Motorola, Inc. All other trademarks are the property of their respective owners.

#### 11.3 Electrostatic Discharge Caution

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

### 11.4 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

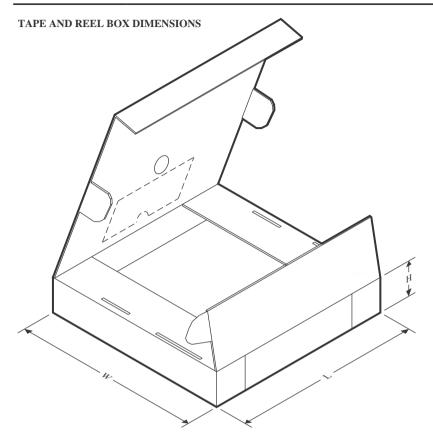

### 12 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

10-Dec-2020

# PACKAGING INFORMATION

| Orderable Device | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan<br>(2) | Lead finish/<br>Ball material | MSL Peak Temp       | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|---------------|--------------|--------------------|------|----------------|-----------------|-------------------------------|---------------------|--------------|-------------------------|---------|

|                  |               |              |                    |      |                |                 | (6)                           |                     |              |                         |         |

| LMH6882SQ/NOPB   | ACTIVE        | WQFN         | NJK                | 36   | 1000           | RoHS & Green    | SN                            | Level-3-260C-168 HR | -40 to 85    | LMH6882                 | Samples |

| LMH6882SQE/NOPB  | ACTIVE        | WQFN         | NJK                | 36   | 250            | RoHS & Green    | SN                            | Level-3-260C-168 HR | -40 to 85    | LMH6882                 | Samples |

| LMH6882SQX/NOPB  | ACTIVE        | WQFN         | NJK                | 36   | 2500           | RoHS & Green    | SN                            | Level-3-260C-168 HR | -40 to 85    | LMH6882                 | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

**RoHS Exempt:** TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

(5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.