SN6507-Q1 JAJSL90 - SEPTEMBER 2022

# SN6507-Q1 絶縁型電源向け、低エミッション 36V プッシュプル・トランス・ ドライバ、デューティ・サイクル制御機能付き

### 1 特長

TEXAS

INSTRUMENTS

- 機能安全対応 - 機能安全システムの設計に役立つ資料を利用可 能 SN6507-Q1

- 車載アプリケーション用に AEC-Q100 (グレード 1) 認 定済み

- WEBENCH<sup>®</sup> Power Designer により、SN6507-Q1 を使用するカスタム設計を作成

- 絶縁トランス用のプッシュプル・ドライバ

- 広い入力電圧範囲:3V~36V

- 最大 60V の入力電圧で動作

- ライン・レギュレーションのデューティ・サイクル制御

- プログラマブル電流制限機能を備えた 0.5A スイッチ

- 広いスイッチング周波数範囲:100kHz~2MHz

- 小さいフットプリントのトランスに対応可能

- プログラマブルなスイッチング周波数

- 外部クロックとの同期オプション

- 低いノイズとエミッション

- 対称型のプッシュプル・トポロジ

- スペクトラム拡散クロック

- ピンで設定可能なスルーレート制御

- 保護機能

- 調整可能な低電圧誤動作防止 (UVLO)

- プログラム可能な過電流保護 (OCP)

- 過電圧誤動作防止 (OVLO)

- サーマル・シャットダウン (TSD)

- 広い温度範囲:-55℃~125℃

- プログラム可能なソフトスタートにより突入電流を低減

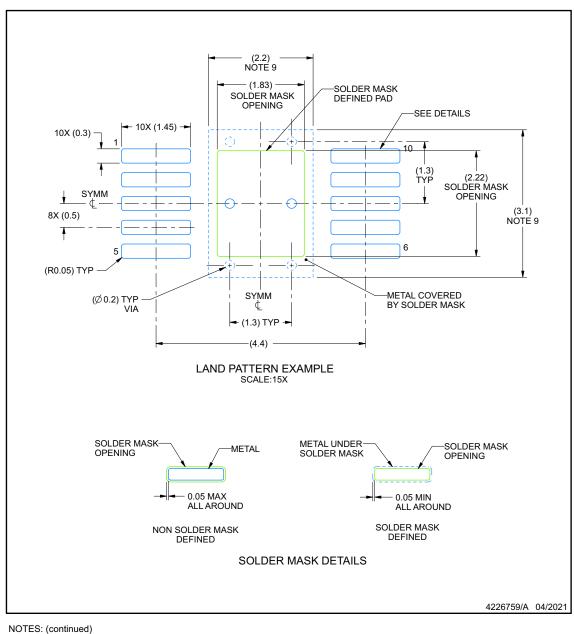

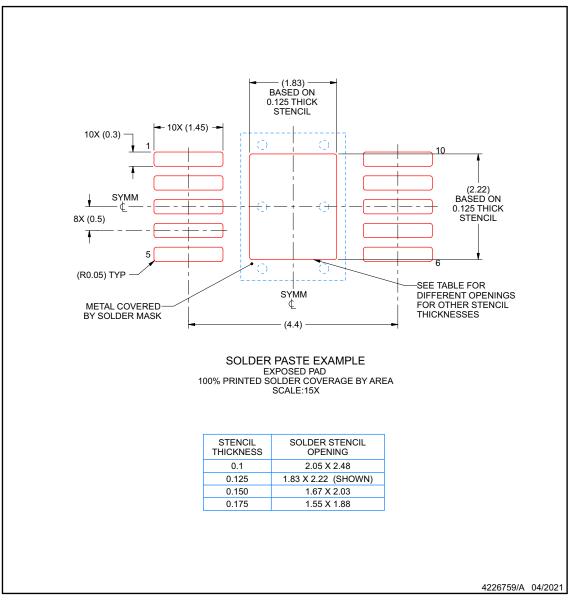

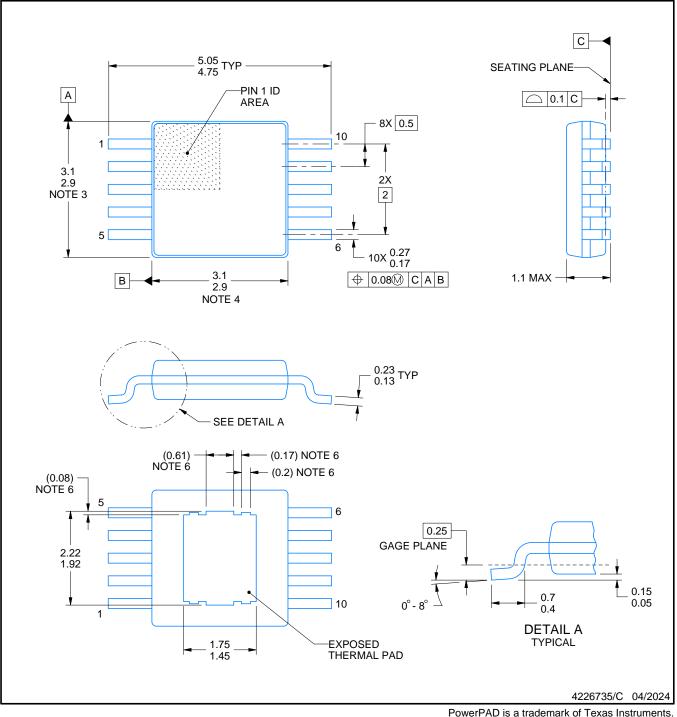

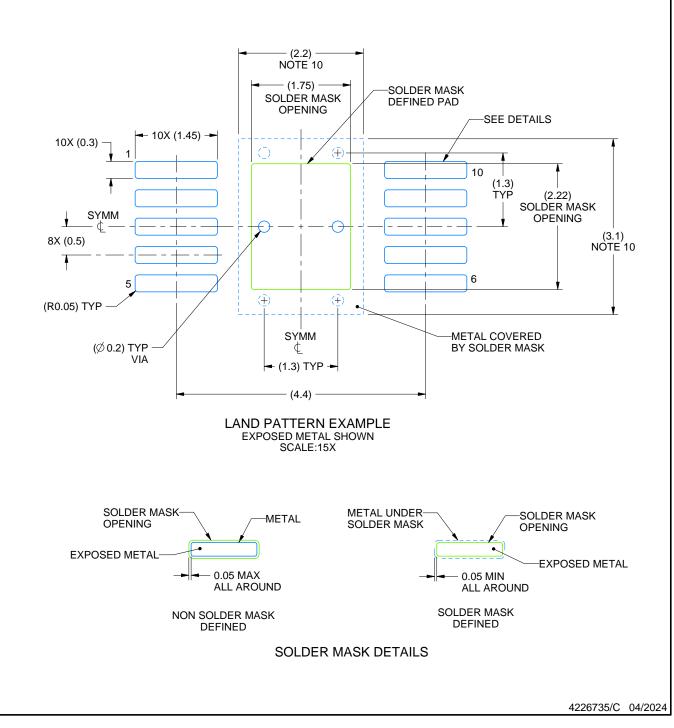

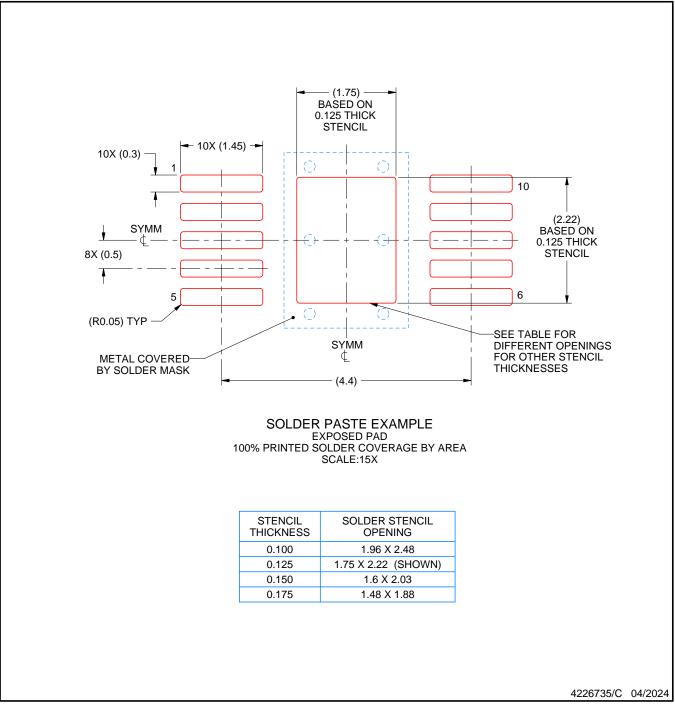

- サーマル・パッド付き 10 ピン HVSSOP (DGQ) パッケ ージ

# 2 アプリケーション

次の用途の絶縁電源:

- · バッテリ管理システム (BMS)

- オンボード・チャージャ

- DC/DC コンバータ

- インバータおよびモータ制御

# 3 概要

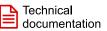

SN6507-Q1 は、小さいソリューション・サイズで絶縁電源 を実現する高電圧、高周波プッシュプル・トランス・ドライバ です。このデバイスは、簡単、低 EMI、磁束キャンセルに よるトランスの飽和防止というプッシュプル・トポロジの利点 を備えています。デューティ・サイクル制御 (広い入力範囲 にかかわらず部品数を低減)と高いスイッチング周波数の 選択 (トランスを小型化可能) により、さらにスペースを節 約できます。

このデバイスは、コントローラと、スイッチングする位相が異 なる 2 つの 0.5A NMOS パワー・スイッチとを内蔵してい ます。本デバイスの入力動作範囲は、高精度の低電圧誤 動作防止によってプログラムされます。本デバイスは、過 電流保護 (OCP)、調整可能な低電圧誤動作防止 (UVLO)、過電圧誤動作防止 (OVLO)、サーマル・シャット ダウン (TSD)、ブレイク・ビフォー・メイク回路によりフォルト 状態から保護されます。

プログラマブル・ソフトスタート (SS) は突入電流を最小限 に抑え、厳しい起動要件を満たす電源シーケンスを実現 します。スペクトラム拡散クロック (SSC) と、ピンで設定可 能なスケーラブル・スルーレート制御 (SRC) は、超低 EMI 要件に対応して伝導および放射によるノイズをさらに 低減します。

SN6507-Q1 は、10 ピン HVSSOP DGQ パッケージで供 給されます。このデバイスは、-55℃~125℃の温度範囲 で動作が規定されています。

#### パッケージ情報

| 部品番号      | パッケージ <sup>(1)</sup> | 本体サイズ (公称)      |

|-----------|----------------------|-----------------|

| SN6507-Q1 | HVSSOP (10 ピン)       | 3.00mm × 3.00mm |

利用可能なパッケージについては、このデータシートの末尾にあ (1)る注文情報を参照してください。

概略回路図

英語版のTI製品についての情報を翻訳したこの資料は、製品の概要を確認する目的で便宜的に提供しているものです。該当する正式な英語版の最新情報は、 🐼 www.ti.com で閲覧でき、その内容が常に優先されます。 TI では翻訳の正確性および妥当性につきましては一切保証いたしません。 実際の設計などの前には、必ず 最新版の英語版をご参照くださいますようお願いいたします。

# **Table of Contents**

| 1 特長1                                   |   |

|-----------------------------------------|---|

| <b>2</b> アプリケーション1                      |   |

| 3 概要1                                   |   |

| 4 Revision History                      | 2 |

| 5 Pin Configuration and Functions       | 5 |

| 6 Specifications                        |   |

| 6.1 Absolute Maximum Ratings4           | ŀ |

| 6.2 ESD Ratings4                        | Ļ |

| 6.3 Recommended Operating Conditions4   | Ļ |

| 6.4 Thermal Information4                | Ļ |

| 6.5 Electrical Characteristics5         | ; |

| 6.6 Switching Characteristics7          | 1 |

| 6.7 Typical Characteristics, SN6507-Q18 | 5 |

| 7 Parameter Measurement Information11   |   |

| 8 Detailed Description12                | 2 |

| 8.1 Overview                            |   |

| 8.2 Functional Block Diagram                          | .13  |

|-------------------------------------------------------|------|

| 8.3 Feature Description                               |      |

| 8.4 Device Functional Modes                           | .20  |

| 9 Application and Implementation                      | . 22 |

| 9.1 Application Information                           |      |

| 9.2 Typical Application                               | . 23 |

| 9.3 Power Supply Recommendations                      | .32  |

| 9.4 Layout                                            | . 32 |

| 10 Device and Documentation Support                   |      |

| 10.1 Documentation Support                            | . 34 |

| 10.2 Receiving Notification of Documentation Updates. |      |

| 10.3 Community Resources                              | .34  |

| 10.4 Trademarks                                       | .34  |

| 11 Mechanical, Packaging, and Orderable               |      |

| Information                                           | . 34 |

|                                                       |      |

4 Revision History 資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| DATE           | REVISION | NOTES           |

|----------------|----------|-----------------|

| September 2022 | *        | Initial Release |

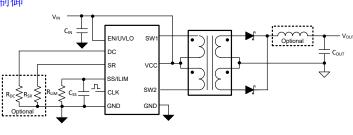

## **5** Pin Configuration and Functions

#### 図 5-1. DGQ Package, 10-Pin HVSSOP (Top View)

#### 表 5-1. Pin Functions

| PIN      |     |                     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------|-----|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME     | NO. | TYPE <sup>(1)</sup> | - DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| SW1      | 1   | 0                   | Open drain output of the first power MOSFET, switch 1. Typically connected to either of the outer terminals of the center tap transformer. Because large currents flow through these pins, their external traces should be kept short.                                                                                                                                                                                                             |

| GND      | 2   | GND                 | Ground connection of internal control circuits and power MOSFET. Pin 2 and Pin 9 must be shorted on PCB for optimzed emissions and efficiency.                                                                                                                                                                                                                                                                                                     |

| VCC      | 3   | Р                   | The VCC pin is the main supply pin for the power and analog circuits. Short duration, high-current pulses are produced during the turn on and turn off of the power switches.                                                                                                                                                                                                                                                                      |

| EN/UVLO  | 4   | I                   | <ul> <li>Enable input and undervoltage lockout (UVLO) programming pin.</li> <li>If the pin voltage is above EN_UVLO threshold, the device is enabled and will start switching when VCC is above VCC_UVLO threshold.</li> <li>If the pin is shorted to VCC, the device is self-started when VCC is above VCC_UVLO threshold.</li> <li>If the pin is floating, or the pin voltage is below EN_UVLO threshold, the device stops switching.</li> </ul> |

| DC       | 5   | I                   | Duty cycle control pin to compensate input variation. A resistor on this pin to GND sets the duty cycle. If unused, leave the pin floating, the duty cycle is set to the default value (48%). Duty cyle control is disabled in SYNC mode.                                                                                                                                                                                                          |

| SR       | 6   | I                   | Slew rate control pin to further optimize emission performance. This pin adjusts slew rate of SW1 and SW2 by connecting a resistor to GND. If the pin is left floating, the device switches at the default slew rate.                                                                                                                                                                                                                              |

| CLK      | 7   | I                   | This pin is used to sync the device with an external clock (SYNC mode) or program the switching frequency by connecting the pin to ground through a resistor. If shorted to GND, the device will switch at its default frequency (1MHz typical). If left floating, the device will stop switching.                                                                                                                                                 |

| SS/ILIM  | 8   | I                   | <ul> <li>Multifunction Soft-Start (SS) and Current-Limit (ILIM) input pin.</li> <li>A capacitor to GND is needed to set the output soft-start time and input inrush current.</li> <li>A resistor to GND is needed to protect the device through the programmable current limit.</li> </ul>                                                                                                                                                         |

| GND      | 9   | GND                 | Ground connection of internal control circuits and power MOSFET. Pin 2 and Pin 9 must be shorted on PCB for optimized emissions and efficiency.                                                                                                                                                                                                                                                                                                    |

| SW2      | 10  | 0                   | Open drain output of the second power MOSFET, switch 2. Typically connected to either of the outer terminals of the center tap transformer. Because large currents flow through these pins, their external traces should be kept short.                                                                                                                                                                                                            |

| PowerPAD | 11  | GND                 | GND pins (Pin 2 and Pin 9) must be electrically connected to the power pad (Pin 11) on the printed circuit board for proper operation.                                                                                                                                                                                                                                                                                                             |

(1) I = input, O = output, P = power, GND = ground

### 6 Specifications

#### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>.

|                                      |                                           | MIN  | MAX                   | UNIT |

|--------------------------------------|-------------------------------------------|------|-----------------------|------|

| Supply voltage <sup>(2)</sup>        | V <sub>CC</sub>                           | -0.5 | 60                    | V    |

| Voltage                              | EN/UVLO                                   | -0.5 | V <sub>CC</sub> + 0.5 | V    |

| Voltage                              | SS/ILIM, CLK, DC                          | -0.5 | 6                     | V    |

| Output switch voltage                | SW1, SW2                                  |      | 85                    | V    |

| Peak output switch current           | I <sub>(D1)Pk</sub> , I <sub>(D2)Pk</sub> |      | 1.6                   | А    |

| Junction temperature, T <sub>J</sub> |                                           | -55  | 150                   | °C   |

| Storage temperature range, T         | stg                                       | -65  | 150                   | °C   |

(1) Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

(2) All voltage values are with respect to the local ground terminal (GND) and are peak voltage values.

#### 6.2 ESD Ratings

|                    |                         |                                                                                            | VALUE | UNIT |

|--------------------|-------------------------|--------------------------------------------------------------------------------------------|-------|------|

|                    | Electrostatic discharge | Human-body model (HBM), per AEC Q100-002 <sup>(1)</sup><br>HBM ESD Classification Level 3A | ±4000 | V    |

| V <sub>(ESD)</sub> |                         | Charged-device model (CDM), per AEC Q100-011<br>CDM ESD Classification Level C6            | ±1500 | v    |

(1) AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

#### 6.3 Recommended Operating Conditions

|                                     |                                                |                              | MIN  | NOM MA | X UNIT |

|-------------------------------------|------------------------------------------------|------------------------------|------|--------|--------|

| V <sub>CC</sub>                     | Input Voltage                                  |                              | 3    | 3      | 6 V    |

|                                     | Output switch current - Primary side           | 3 V < V <sub>CC</sub> < 6 V  |      | 0.     | 4 A    |

| I <sub>SW1</sub> , I <sub>SW2</sub> | Output switch current - Frinary side           | 6 V < V <sub>CC</sub> < 36 V |      | 0.     | 0.5    |

| T <sub>A</sub>                      | Ambient temperature                            |                              | -55  | 12     | 5 °C   |

| TJ                                  | Junction temperature                           |                              | -55  | 15     | 0 °C   |

| C <sub>SS</sub>                     | Soft-start capacitor on SS/ILIM pin            |                              | 0.05 | 1      | 0 µF   |

| R <sub>ILIM</sub>                   | Current limiting resistor on SS/ILIM pin       |                              | 18   | 26     | 1 kΩ   |

| R <sub>SR</sub>                     | Resistor on SR pin for Slew rate control       |                              | 4.8  | 2      | 1 kΩ   |

| R <sub>CLK</sub>                    | Resistor on CLK pin for programmable frequency |                              | 4    | 11     | 1 kΩ   |

#### 6.4 Thermal Information

|                          | THERMAL METRIC <sup>(1)</sup>                |         |      |

|--------------------------|----------------------------------------------|---------|------|

|                          |                                              |         | UNIT |

|                          |                                              | 10 PINS |      |

| R <sub>θJA</sub>         | Junction-to-ambient thermal resistance       | 48.2    | °C/W |

| R <sub>0JC(top)</sub>    | Junction-to-case (top) thermal resistance    | 61.6    | °C/W |

| R <sub>θJB</sub>         | Junction-to-board thermal resistance         | 18.4    | °C/W |

| TιΨ                      | Junction-to-top characterization parameter   | 1.7     | °C/W |

| Ψ <sub>JB</sub>          | Junction-to-board characterization parameter | 18.3    | °C/W |

| R <sub>0JC(bottom)</sub> | Junction-to-case(bottom) thermal resistance  | 5.8     | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

#### **6.5 Electrical Characteristics**

Minimum and maximum limits apply over the recommended junction temperature range, unless otherwise indicated. All typical values are at  $T_A = 25^{\circ}$ C,  $V_{CC} = 24$  V, CLK  $F_{SW} = 1$  MHz and  $V_{EN/UVLO} = 2.5$  V unless otherwise stated.

|                                 | PARAMETER                                                                               | TEST CONDITIONS                                                                                                                  | MIN  | TYP  | MAX  | UNIT |

|---------------------------------|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| SUPPLY CUR                      | RENT                                                                                    |                                                                                                                                  |      |      |      |      |

| I <sub>cc</sub>                 | VIN Supply Current (3 V < V <sub>C C</sub> < 36V) , not including switch drive currents | $V_{\text{EN/UVLO}}$ =2.5 V, R <sub>L</sub> = 50 $\Omega$                                                                        |      | 3    | 4    | mA   |

| I <sub>SHUTDOWN</sub>           | VIN shutdown current                                                                    | $V_{\text{EN/UVLO}}$ =0 V, R <sub>L</sub> = 50 $\Omega$                                                                          |      | 0.8  | 2.5  | μA   |

| I <sub>LKG(SS/ILIM)</sub>       | Leakage Current on SS/ILIM pin                                                          | V <sub>EN/UVLO</sub> = 0 V, Voltage of SS/ILIM = 5 V                                                                             |      |      | 0.7  | μA   |

| ENABLE AND                      | UVLO                                                                                    |                                                                                                                                  |      |      |      |      |

| VCC <sub>UVLO-</sub><br>RISING  | VCC Positive-going UVLO threshold                                                       | $V_{CC}$ rising , EN/UVLO is shorted to $V_{CC}$                                                                                 |      | 2.8  | 2.9  | V    |

| VCC <sub>UVLO-</sub><br>FALLING | VCC Negative-going UVLO threshold                                                       | $V_{CC}$ falling, EN/UVLO is shorted to $V_{CC}$                                                                                 | 2.5  | 2.67 |      | V    |

| VCC <sub>UVLO-HYS</sub>         | VCC UVLO threshold hysteresis                                                           | EN/UVLO is shorted to $V_{\mbox{CC}}$                                                                                            | 0.1  | 0.12 |      | V    |

| EN <sub>UVLO-</sub><br>RISING   | EN/UVLO Positive-going UVLO threshold                                                   | EN/UVLO rising                                                                                                                   | 1.4  | 1.5  | 1.6  | V    |

| EN <sub>UVLO-</sub><br>FALLING  | EN/UVLO Negative-going UVLO threshold                                                   | EN/UVLO falling                                                                                                                  | 1.25 | 1.35 | 1.45 | V    |

| EN <sub>UVLO-HYS</sub>          | EN/UVLO UVLO threshold hysteresis                                                       |                                                                                                                                  | 0.14 | 0.15 |      | V    |

| POWER STAC                      | ĴE                                                                                      |                                                                                                                                  |      |      |      |      |

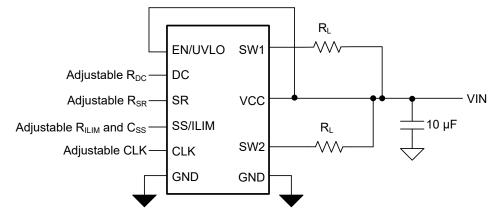

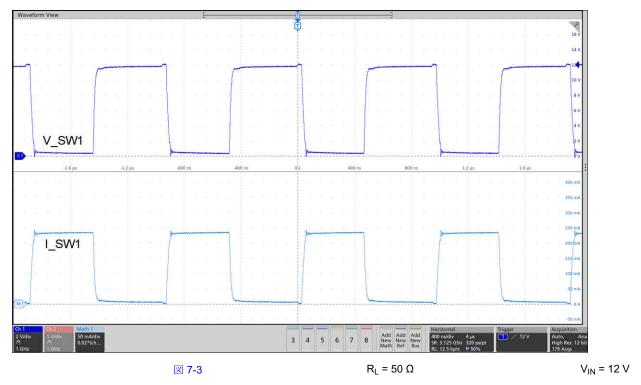

| DMM                             | Average ON time mismatch between SW1 and SW2                                            | $R_L$ = 50 $\Omega$ to V <sub>CC</sub> , Pull-Up Resistor Test Circuit Configuration                                             |      | 0    |      | %    |

| R <sub>(ON)</sub>               | Output switch ON resistance                                                             | V <sub>CC</sub> = 24 V, I <sub>SW1</sub> , I <sub>SW2</sub> = 0.5 A                                                              |      | 0.45 | 1    | Ω    |

| V <sub>(SLEW)</sub>             | Voltage slew rates on SW1 and SW2                                                       | $R_L$ = 50 $\Omega$ to $V_{CC}, V_{CC}$ = 12 V; $R_{SR}$ = 9.6 k $\Omega$ (Default), Pull-Up Resistor Test Circuit Configuration |      | 298  |      | V/µs |

| V <sub>(SLEW)</sub>             | Voltage slew rates on SW1 and SW2                                                       | $R_L$ = 50 $\Omega$ to $V_{CC}, V_{CC}$ = 12 V; $R_{SR}$ = 9.6 k $\Omega$ (Default), Pull-Up Resistor Test Circuit Configuration |      | 369  |      | V/µs |

| CLK                             |                                                                                         |                                                                                                                                  |      |      |      |      |

| F <sub>SW</sub>                 | D1, D2 average switching Frequency (Default)                                            | $R_L$ = 50 $\Omega$ , $R_{CLK}$ = 0 k $\Omega$ , Pull-Up Resistor Test<br>Circuit Configuration                                  | 780  | 1000 | 1296 | kHz  |

| F <sub>(SYNC)</sub>             | External clock frequency on CLK pin                                                     | External clock applied on CLK pin for SYNC<br>mode. SW1/SW2 switches at 1/2 the external<br>CLK frequency                        | 200  |      | 4000 | kHz  |

| V <sub>CLK(High)</sub>          | CLK pin logic high threshold                                                            |                                                                                                                                  |      | 1.6  | 1.8  | V    |

| V <sub>CLK(Low)</sub>           | CLK pin logic low threshold                                                             |                                                                                                                                  | 1.0  | 1.2  |      | V    |

| SOFT-START                      | •                                                                                       |                                                                                                                                  |      |      | I    |      |

| I <sub>SS</sub>                 | SS ext capacitor charging current                                                       |                                                                                                                                  |      | 275  |      | μA   |

| C <sub>SS</sub> Range           | SS ext capacitor range                                                                  |                                                                                                                                  | 0.05 |      | 5    | μF   |

| CURRENT LI                      | міт                                                                                     |                                                                                                                                  |      |      |      |      |

| I <sub>LIM</sub>                | SW1 and SW2 Current Limit                                                               | $R_{LIM}$ = 18.2 kΩ, 5 V < V <sub>CC</sub> < 36 V                                                                                | 1.00 | 1.30 | 1.59 | Α    |

| I <sub>LIM</sub>                | SW1 and SW2 Current Limit                                                               | $R_{LIM} = 30.1 \text{ k}\Omega, 5 \text{ V} < V_{CC} < 36 \text{ V}$                                                            | 0.56 | 0.79 | 1.02 | Α    |

| I <sub>LIM</sub>                | SW1 and SW2 Current Limit                                                               | R <sub>LIM</sub> = 261 kΩ, 5 V < V <sub>CC</sub> < 36 V                                                                          | 0.06 | 0.10 | 0.14 | А    |

#### SN6507-Q1 JAJSL90 – SEPTEMBER 2022

# Minimum and maximum limits apply over the recommended junction temperature range, unless otherwise indicated. All typical values are at $T_A = 25^{\circ}$ C, $V_{CC} = 24$ V, CLK $F_{SW} = 1$ MHz and $V_{EN/UVLO} = 2.5$ V unless otherwise stated.

|                                     | PARAMETER                                    | TEST CONDITIONS                                                        | MIN  | TYP  | MAX  | UNIT |

|-------------------------------------|----------------------------------------------|------------------------------------------------------------------------|------|------|------|------|

| DC CONTRO                           | L                                            |                                                                        |      |      |      |      |

| D <sub>sw1</sub> , D <sub>sw2</sub> | Switching Duty Cycle on SW1 and SW2          | DC pin floating (Default), F <sub>SW</sub> = 300KHz, Timing<br>Diagram |      | 48   |      | %    |

| D <sub>sw1</sub> , D <sub>sw2</sub> | Switching Duty Cycle on SW1 and SW2          | External CLK (SYNC mode), F <sub>SW</sub> =<br>300KHz, Timing Diagram  |      | 48   |      | %    |

| INPUT OVLO                          |                                              |                                                                        |      |      |      |      |

| VCC <sub>OVLO-</sub><br>RISING      | Input Over-voltage Lockout Rising Threshold  | V <sub>CC</sub> rising                                                 | 36.9 | 38.7 | 40.5 | V    |

| VCC <sub>OVLO-</sub><br>Falling     | Input Over-voltage Lockout Falling Threshold | V <sub>CC</sub> falling                                                | 36.5 | 38.2 | 40.0 | V    |

| VCC <sub>OVLO-HYS</sub>             | Input Over-voltage Lockout Hysteresis        | V <sub>CC</sub> hysteresis voltage                                     | 0.47 | 0.57 |      | V    |

| THERMAL SI                          | IUT DOWN                                     |                                                                        |      |      |      |      |

| T <sub>SD+</sub>                    | T <sub>SD</sub> turn on temperature          | T <sub>J</sub> rising                                                  | 170  | 184  | 198  | °C   |

| T <sub>SD-</sub>                    | T <sub>SD</sub> turn off temperature         | T <sub>J</sub> falling                                                 | 135  | 147  | 159  | °C   |

| T <sub>SD-HYST</sub>                | T <sub>SD</sub> hysteresis                   |                                                                        | 32   | 37   | 42   | °C   |

### 6.6 Switching Characteristics

Minimum and maximum limits apply over the recommended junction temperature range, unless otherwise indicated. All typical values are at  $T_A = 25^{\circ}$ C,  $V_{CC} = 24$  V, CLK  $F_{SW} = 1$  MHz and  $V_{EN/UVLO} = 2.5$  V unless otherwise stated.

|                        | PARAMETER              | TEST CONDITIONS                                                                                                                                                                                                               | MIN | TYP | MAX | UNIT |

|------------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| ENABLE A               | ND UVLO                |                                                                                                                                                                                                                               |     |     |     |      |

| T <sub>EN_glitch</sub> | EN glitch filter       |                                                                                                                                                                                                                               | 5   |     |     | μs   |

| POWER ST               | AGE                    |                                                                                                                                                                                                                               |     |     |     |      |

| t <sub>BBM</sub>       | Break-before-make time | $\begin{array}{l} \mbox{Measured at } 0.5 \mbox{V}_{CC} \mbox{ with } \mbox{R}_L = 50 \ \Omega,  \mbox{F}_{SW} = 1 \\ \mbox{MHz},  \mbox{R}_{SR} = 9.6 \ \mbox{k}    \mbox{ or Default}), \mbox{ Timing Diagram} \end{array}$ |     | 70  |     | ns   |

| SOFT-STAF              | RT                     |                                                                                                                                                                                                                               |     |     |     |      |

| t <sub>PWRUP</sub>     | Power-up time          | $C_{SS}$ = 0 $\mu F$ , from EN = High to full drive-current available at $S_{W1}$ and $S_{W2}$                                                                                                                                |     | 300 | 400 | μs   |

| t <sub>PWRDN</sub>     | Power-down time        | $C_{SS}$ = 0 µF, from EN = Low to output MOSFETs off (no current on $S_{W1}$ and $S_{W2}$ )                                                                                                                                   |     |     | 30  | μs   |

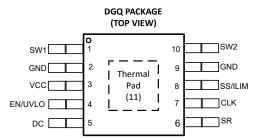

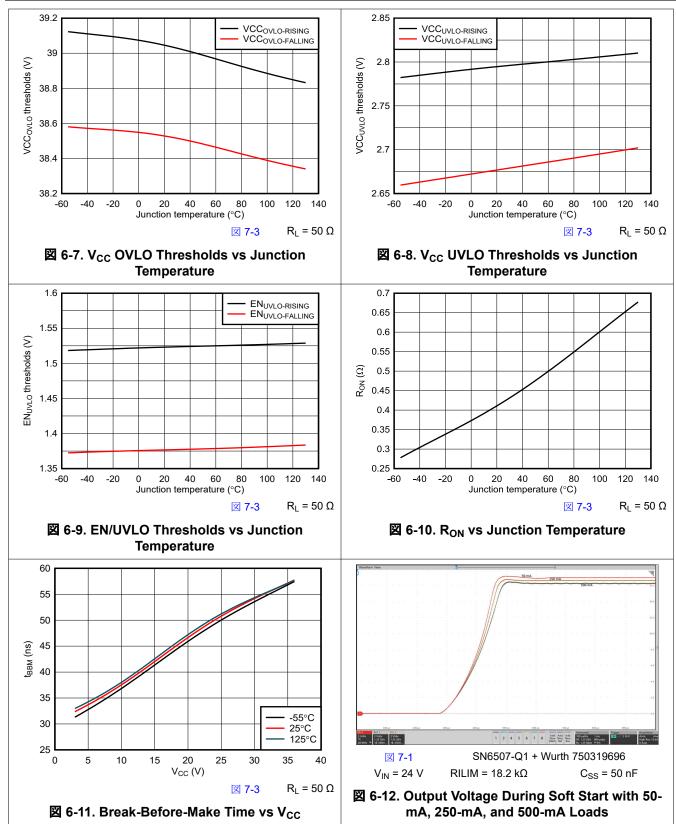

### 6.7 Typical Characteristics, SN6507-Q1

SN6507-Q1 JAJSL90 – SEPTEMBER 2022

SN6507-Q1 JAJSL90 – SEPTEMBER 2022

### **7 Parameter Measurement Information**

🛛 7-2. Timing Diagram

# 8 Detailed Description

### 8.1 Overview

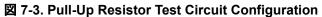

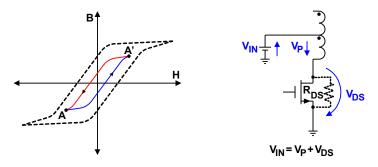

The SN6507-Q1 is a 36-V, 0.5-A push-pull transformer driver with two integrated n-channel power MOSFETs. It is designed for low cost, small size, low EMI isolated DC/DC power supplies.

The device includes an oscillator that feeds a gate-drive circuit. The gate-drive, comprising a frequency divider and a break-before-make (BBM) logic, provides two complementary output signals which alternately turn the two output NMOS transistors on and off. A subsequent break-before-make logic inserts a dead-time between the high-pulses of the two signals to avoid shorting out both ends of the transformer's primary windings. The resulting output signals drive an isolation transformer and rectifier, converting the input voltage to an isolated output voltage.

To improve performance at wide-input applications, the device implements a Duty Cycle Control (DCC) feature that the duty cyle is dynamically adjusted to compensate for the input variation. It removes the need of preregulation if the input variation is within a certain degree. Or even if at wide input conditions where the input variation is out of regulation range, it saves secondary-side LDO size and power loss. The wide switching frequency range allows for better efficiency and smaller output ripple, as well as size optimization when selecting the transformers.

The transformer driver comes with multiple protection features to ensure robust operation, such as programmable overcurrent protection (OCP), input OVP, input UVLO and TSD. The device minimizes excessive output overvoltage transients by taking advantage of the overvoltage comparator. When the overvoltage comparator is activated, the MOSFETs are turned off and prevented from turning on until the overvoltage condition is removed. The device implements overload protection for both MOSFETs which help control the transformer current and avoid transformer saturation. It also shuts down if the junction temperature is higher than the thermal shutdown trip point. A programmable soft-start period reduces the inrush current during start-up and fault recovery.

For ultra-low EMI applications, the slew rate control feature provides design flexibility and simplicity to further improve emissions with a resistor-programmable option.

#### 8.2 Functional Block Diagram

#### 8.3 Feature Description

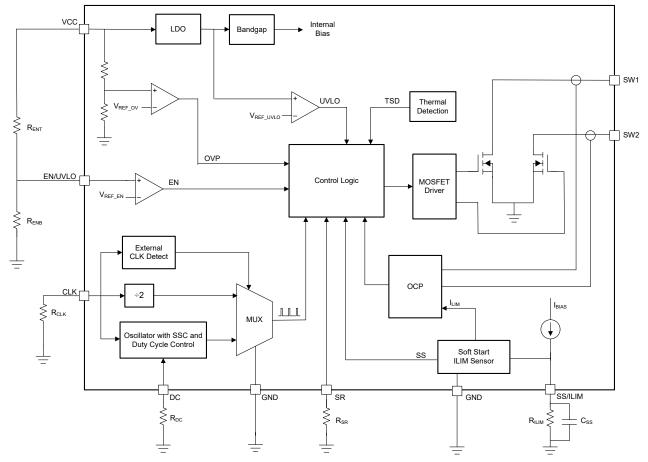

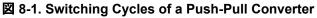

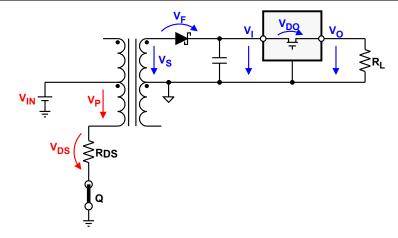

#### 8.3.1 Push-Pull Converter

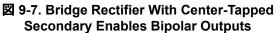

Push-pull converters require transformers with center-taps to transfer power from the primary to the secondary as shown in  $\boxtimes$  8-1. When Q<sub>1</sub> conducts, V<sub>IN</sub> drives a current through the lower half of the primary to ground, thus creating a negative voltage potential at the lower primary end with regards to the V<sub>IN</sub> potential at the center-tap.

At the same time the voltage across the upper half of the primary is such that the upper primary end is positive with regards to the center-tap in order to maintain the previously established current flow through  $Q_2$ , which now has turned high-impedance. The two voltage sources, each of which equaling  $V_{IN}$ , appear in series and cause a voltage potential at the open end of the primary of  $2 \times V_{IN}$  with regards to ground.

Per dot convention the same voltage polarities that occur at the primary also occur at the secondary. The positive potential of the upper secondary end therefore forward biases diode  $CR_1$ . The secondary current starting from the upper secondary end flows through  $CR_1$ , charges capacitor C, and returns through the load impedance  $R_L$  back to the center-tap.

When  $Q_2$  conducts,  $Q_1$  goes high-impedance and the voltage polarities at the primary and secondary reverse. Now the lower end of the primary presents the open end with a  $2 \times V_{IN}$  potential against ground. In this case  $CR_2$  is forward biased while  $CR_1$  is reverse biased and current flows from the lower secondary end through  $CR_2$ , charging the capacitor and returning through the load to the center-tap.

#### 8.3.2 Core Magnetization

⊠ 8-2 shows the ideal magnetizing curve for a push-pull converter with B as the magnetic flux density and H as the magnetic field strength. When  $Q_1$  conducts the magnetic flux is pushed from A to A', and when  $Q_2$  conducts the flux is pulled back from A' to A. The difference in flux and thus in flux density is proportional to the product of the primary voltage,  $V_P$ , and the time,  $t_{ON}$ , it is applied to the primary: B ≈  $V_P \times t_{ON}$ .

#### 図 8-2. Core Magnetization and Self-Regulation Through Positive Temperature Coefficient of R<sub>DS(on)</sub>

This volt-seconds (V-t) product is important as it determines the core magnetization during each switching cycle. If the V-t products of both phases are not identical, an imbalance in flux density swing results with an offset from the origin of the B-H curve. If balance is not restored, the offset increases with each following cycle and the transformer slowly creeps toward the saturation region.

Fortunately, due to the positive temperature coefficient of a MOSFET's on-resistance, the output FETs of the SN6507-Q1 have a self-correcting effect on V-t imbalance. In the case of a slightly longer on-time, the prolonged current flow through a FET gradually heats the transistor which leads to an increase in  $R_{DS-on}$ . The higher resistance then causes the drain-source voltage, VDS, to rise. Because the voltage at the primary is the difference between the constant input voltage,  $V_{IN}$ , and the voltage drop across the MOSFET,  $V_P = V_{IN} - V_{DS}$ ,  $V_P$  is gradually reduced and V-t balance restored.

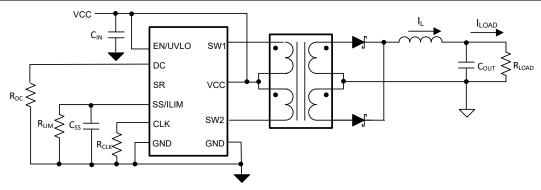

#### 8.3.3 Duty Cycle Control

The SN6507-Q1 implements a duty cycle control feature to provide line regulation to a certain degree through a resistor on DC pin. By making the DC pin voltage a function of the input, the duty cycle will adjust with  $V_{IN}$ , so that  $V_{OUT}$  can be kept constant. Compared to fixed duty cycle transformer drivers, this dynamic duty cycle control feature reduces LDO power loss for wide  $V_{IN}$  variations by pseudo-regulating the output. For applications where input variation is within a certain range, this feature can eliminate the post-regulation LDO. Another benefit of duty cycle control is to reduce the transformer cost and size because of the limited input range to primary side of the transformer.

図 8-3. Schematic with duty cycle control

The calculation of DC pin resistor is shown in  $\not \equiv$  1, where both R<sub>DC</sub> and R<sub>CLK</sub> are in k $\Omega$ .

$$R_{DC} = 0.816 \times D \times VCC \times (R_{CLK} + 1) - 1$$

(1)

For fixed oscillator cases where  $R_{CLK}$  is shorted to GND, a value of  $R_{CLK}$  = 9.6k $\Omega$  should be used in the equation above to calculate  $R_{DC}$ .

The duty cycle control can compensate for input variation up to ±35%, where line regulation within ±5% can be achieved. To achieve this range, it is recommended that duty cycle at nominal V<sub>IN</sub> is centered at 25% (D = 0.25). The transformer turns ratio needs take this duty cycle into calculation to ensure the expected output voltage level at all V<sub>IN</sub> voltages, as discussed in 2922.5.

The duty cycle control features supports up to a certain duty cycle and  $V_{IN}$  range. The minimum duty cycle is determined by the charge and discharge time of the gate capacitance of Power FETs, while the maximum duty cycle is limited by the dead time (70 ns typical). For example, at 1 MHz, the adjustable duty cycle is between 10% and 43%. Exceeding above duty cycle range, the line regulation may saturate and input compensation does not work anymore. Meanwhile, if the duty cycle is lower than the minimum spec, the part may hit current limit at heavy loads. The V<sub>IN</sub> range that duty cycle feature is applicable is from 6 V to 36 V.

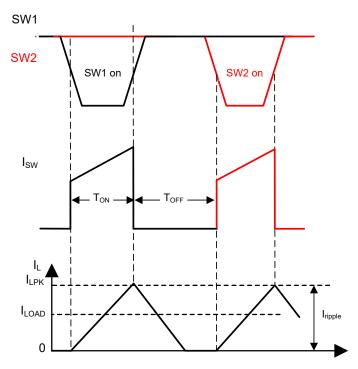

To enable the duty cycle control feature, an inductor is required on the output side. The selection of the output inductor should make sure the inductor current will not go into discountinous conduction mode (DCM), meaning the inductor current ramp should not drop to zero at any time. The minimum inductance  $L_{MIN}$  is therefore calculated by the conditions that the part stays in continuous conduction mode (CCM) where the load DC current is smaller than half the current ramp amplitude seen on the inductor. Therefore  $L_{MIN}$  is a function of the load current and switching frequency as shown by below equation where  $I_{load}$  is in A,  $f_{SW}$  is in Hz, D is the duty cycle as a decimal (for 25% duty cycle, 0.25 would be used), and  $L_{min}$  is in H.

$$L_{MIN} = V_{OUT} \times \frac{1 - 2 \times D \times (V_{IN TYP} / V_{IN MAX})}{4 \times I_{LOAD MIN} \times f_{SW}}$$

(2)

図 8-4. Waveforms in Continuous Conduction Mode (CCM)

図 8-5. Waveforms in Discontinuous conduction Mode (DCM)

#### **Programmable Switching Frequency**

SN6507-Q1 has an internal oscillator to set the switching frequency of the power stage. As the two power switches are out of phase, the oscillator frequency is twice of the actual switching frequency of each power

switch. The duty cycle is fixed with 70 ns deadtime to avoid shoot-through. The duty cycle is changeable if duty cycle feature is enabled. Please refer to セクション 8.3.3.

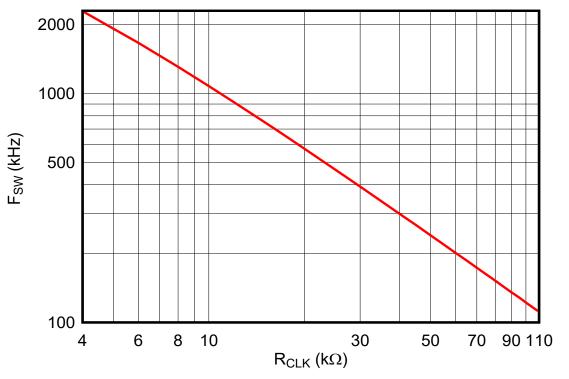

SN6507-Q1 has a wide switching frequency range from 100 kHz up to 2 MHz, which is pin-programmable through a resistor ( $R_{CLK}$ ) to GND. Below table lists the value of  $R_{CLK}$  to achieve certain operating frequencies ( $f_{SW}$ ). The choice of switching frequency is a trade-off between power efficiency and size of capacitive and inductive components. For example, when operating at higher switching frequency, the size of the transformer and inductor is reduced, resulting in a smaller design footprint and lower cost. However, higher frequency increases switching losses and consequently degrades the overall power supply efficiency.

| R <sub>CLK</sub>    | f <sub>SW</sub> (Typical) |  |  |  |  |  |

|---------------------|---------------------------|--|--|--|--|--|

| 111 kΩ              | 105 kHz                   |  |  |  |  |  |

| 21 kΩ               | 523 kHz                   |  |  |  |  |  |

| 9.6 kΩ              | 1.07 MHz                  |  |  |  |  |  |

| 4.1 kΩ              | 2.13 MHz                  |  |  |  |  |  |

| 0 kΩ (Short to GND) | Default (1 MHz)           |  |  |  |  |  |

#### 表 8-1. Recommended 1% R<sub>CLK</sub> values and f<sub>SW</sub> Look-up Table

$\boxtimes$  8-6 can also be used to estimate the programmable switching frequency,  $f_{SW}$ , using an external resistor value,  $R_{CLK}$ , where  $R_{CLK}$  is in  $k\Omega$  and  $f_{SW}$  is in kHz:

If CLK pin is shorted to GND, the part switches at its default frequency, F<sub>SW</sub>. CLK pin floating is not a valid state of operation and will cause the part to stop switching until an external clock signal is present.

#### 8.3.4 Spread Spectrum Clocking

Radiated emissions is an important concern in high current switching power supplies. Due to the periodicity of the digital clock signals, the energy concentrates in one particular frequency and also in its odds harmonics, causing EMI issues. SN6507-Q1 implements Spread spectrum clocking (SSC) to reduce the radiated emissions of digital clock signals. The device modulates its internal clock in such a way that the emitting energy is spread

over multiple frequency bins. This feature greatly improves the emissions performance of the entire power supply block and hence relieves the system designer from one major concern in isolated power supply design.

#### 8.3.5 Slew Rate Control

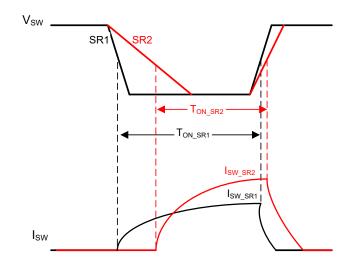

To allow optimization of EMI with respect to efficiency, the SN6507-Q1 is designed to allow a resistor ( $R_{SR}$ ) to select the strength of the driver of PowerFETs turning on. As shown in  $\boxtimes$  8-7 below, the slew rate of the switching edges is controllable with the resistor. Rolling off harmonics through slew rate control can eliminate the need for shielding and common mode chokes in many applications.

The EMI benefit of slew rate control may result in slightly reduced efficiency and higher peak current ( $I_{SW_SR}$ ). When the feature slows down the charging and discharging of the gate capacitance, the extended transition times of the FETs increases the transition losses during each switching cycle. This increases power dissipation, which decreases efficiency and exacerbates thermal concerns. This will limit how much the slew rate can be reduced. Another cost is the peak current of each cyle will be increased. It is because the slow edges reduce the on-time ( $I_{ON_SR}$ ) and eventually the peak current ( $I_{SW_SR}$ ) will increase to deliver the same average current to the load on each cycle.

☑ 8-7. Slew Rate Control Scheme

The slew rate at different V<sub>IN</sub> is programmed by R<sub>SR</sub>. Higher R<sub>SR</sub> values configure SN6507-Q1 for slower slew rates across V<sub>CC</sub> levels while lower R<sub>SR</sub> values configure SN6507-Q1 for faster slew rates. The relationship between V<sub>CC</sub> and the slew rate for 12 V and 24 V cases are listed in  $\frac{1}{2}$  8-2 below. As the slew rate is independent of the switching frequency, care must be taken that at high frequencies, the slew rate should be fast enough to maximize the output power delivery to the load. If the SR pin is left floating, the slew rate will be set to the default value. An SR pin short to GND is read as a fault condition, and the device will stop switching.

| 表 8-2. Slew Rate Control Look | -up Table |

|-------------------------------|-----------|

|-------------------------------|-----------|

| VCC (V) | R <sub>SR</sub> (kΩ) | Typical SLEW RATE (V/μs) |

|---------|----------------------|--------------------------|

| 5       | 4.8                  | 337                      |

| 5       | Floating (Default)   | 263                      |

| 5       | 15                   | 224                      |

| 5       | 21                   | 198                      |

| 12      | 4.8                  | 424                      |

| 12      | Floating (Default)   | 298                      |

| 12      | 15                   | 237                      |

| 12      | 21                   | 199                      |

| 24      | 4.8                  | 583                      |

| VCC (V) | R <sub>SR</sub> (kΩ) | Typical SLEW RATE (V/µs) |

|---------|----------------------|--------------------------|

| 24      | Floating (Default)   | 369                      |

| 24      | 15                   | 273                      |

| 24      | 21                   | 218                      |

#### 表 8-2. Slew Rate Control Look-up Table (continued)

#### 8.3.6 Protection Features

SN6507-Q1 is protected by multiple protection features to improve the system level robustness and reliability. The protection features include programmable input undervoltage protection (UVLO), input over-voltage protection (OVP), programmable over current protection (OCP), and over-temperature protection (TSD).

#### 8.3.6.1 Over Voltage Protection (OVP)

As SN6507-Q1 is a open-loop transformer driver, the over voltage protection feature is implemented to prevent the output voltage from rising too high. The overvoltage protection threshold is a fixed value and cannot be programmed. If the VCC pin voltage exceeds the overvoltage rising threshold, device stops switching after a 550 ns (typical) response time. To recover from an over voltage event, the input voltage must drop below the OVP falling threshold.

#### 8.3.6.2 Over Current and Short Circuit Protection (OCP)

The SN6507-Q1 is protected from overcurrent conditions with cycle-by-cycle current limiting on both NMOS switches. OCP is disabled during soft-start. After soft-start finishes, the OCP is enabled, and the threshold is set at the programmed value. The switch current is sensed and compared to the current threshold that is programmed by the external resistor on SS/ILIM pin,  $R_{ILIM}$ . Common current limit thresholds ( $I_{LIM}$ ) and their corresponding resistor values for  $R_{ILIM}$  are listed in  $\gtrsim 8-3$  below. Leaving the ILIM/SS pin floating is not recommended for this device.

| R <sub>ILIM</sub> I <sub>LIM</sub> (Typical) |  |  |  |  |  |  |  |

|----------------------------------------------|--|--|--|--|--|--|--|

|                                              |  |  |  |  |  |  |  |

| 1.3 A                                        |  |  |  |  |  |  |  |

| 1.2 A                                        |  |  |  |  |  |  |  |

| 1.1 A                                        |  |  |  |  |  |  |  |

| 1.0 A                                        |  |  |  |  |  |  |  |

| 900 mA                                       |  |  |  |  |  |  |  |

| 800 mA                                       |  |  |  |  |  |  |  |

| 700 mA                                       |  |  |  |  |  |  |  |

| 600 mA                                       |  |  |  |  |  |  |  |

| 500 mA                                       |  |  |  |  |  |  |  |

| 400 mA                                       |  |  |  |  |  |  |  |

| 300 mA                                       |  |  |  |  |  |  |  |

| 200 mA                                       |  |  |  |  |  |  |  |

| 100 mA                                       |  |  |  |  |  |  |  |

|                                              |  |  |  |  |  |  |  |

#### 表 8-3. Recommended 1% R<sub>ILIM</sub> values

In case of an extreme over-load condition on the isolated output due to a short circuit, the device behaves as follows:

- In the event of a transient overload or short circuit, if the resulting voltage dip is lower than 2.5 V (typical) on the SS/I<sub>LIM</sub> pin, the device considers it as a "soft-short" condition. In soft-shorts, the converter goes into hiccup mode: on hitting the programmed OCP threshold, the driver will be shut-off for 100 ns (typical), and then retry driving. If the OCP trips again, the cycle continues. This retry keeps occurring for entire T<sub>ON</sub> time of SW1 and SW2 until OCP does not trip or a "hard-short" is triggered. During the OCP retry events, both FETs are turned OFF, and the transient peak current may go higher than OCP limit.

- If the voltage dip is more than 2.5 V (typical), the devices considers it as a "hard-short" condition. The hard-short OCP threshold is fixed at 5 A (typical). If a hard-short condition lasts more than 200 µs, it indicates that the system is in a serious short-circuit fault condition, the device will fully discharge the soft-start cap and

enters soft start once the short circuit is cleared. Note there is a 65 ns (typ.) response time to trigger hard-short OCP.

#### 8.3.6.3 Under Voltage Lock-Out (UVLO)

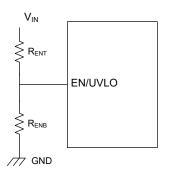

Start-up and shutdown are controlled by the both EN/UVLO pin and VCC pin. For the device to remain in shutdown mode, apply a voltage below  $EN_{UVLO}$  to the EN/UVLO pin. In shutdown mode, the quiescent current is less than 0.8  $\mu$ A (typical). If EN/UVLO pin sees a voltage higher than  $EN_{UVLO}$ , but  $V_{IN}$  is still below  $VCC_{UVLO}$ , the SW node is inactive. Once the  $V_{IN}$  is above  $VCC_{UVLO}$ , the chip begins to switch normally, provided the EN/UVLO voltage is above 1.5 V.

There are three ways to enable the device operation. The simplest way is to connect the EN/UVLO pin to VCC pin, allowing self-start-up of the device when VCC pin voltage is above VCC<sub>UVLO</sub> level. However, many applications benefit from an input UVLO level different than that provided internal UVLO. So another way is to employ an enable resistor divider network as shown in Figure below, which establishes a programmable UVLO threshold. The thrid way is to connect an external logic output to drive this pin, allowing user-defined system power sequencing.

EN/UVLO pin has a 5 µs (typical) glitch filter to help avoid false turn-on and turn-off due to noise coupling. It also comes with an internal pull down design to ensure the device is in shutdown mode when the pin is left floating.

#### Programmable UVLO using EN/UVLO pin

Resistor values can be calculated using Equation below, where the input turn on threshold  $V_{IN\_UVLO}$  is the desired typical start-up input voltage,  $EN_{UVLO}$  is 1.5 V typical, and  $R_{ENT}$  and  $R_{ENB}$  are in  $\Omega$ .

$$V_{IN\_UVLO} = \left(1 + \frac{R_{ENT}}{R_{ENB}}\right) \times EN_{UVLO}$$

(3)

#### 8.3.6.4 Thermal Shut Down (TSD)

Thermal shutdown prevents the device from reaching extreme junction temperatures by turning off the internal switches when the IC junction temperature exceeds 180°C (typical). In TSD, the switching stops immediately to prevent the internal MOSFETs from failing in either high ambient temperature operation conditions or due to self-heating from high switching current. To recover from thermal shut down condition, the junction temperature must be below the overtemperature protection falling threshold. When the junction temperature falls below 147°C (typical), the power FET switching is enabled.

#### 8.4 Device Functional Modes

The functional modes of the device are divided into start-up, operating, and off-mode.

#### 8.4.1 Start-Up Mode

When VCC pin voltage ramps up to VCC<sub>UVLO</sub>, and EN/UVLO pin voltage is over  $EN_{UVLO}$  the internal oscillator starts operating. The output stage begins switching but the amplitude of the drain signals at SW1 and SW2 have not reached its full maximum yet.

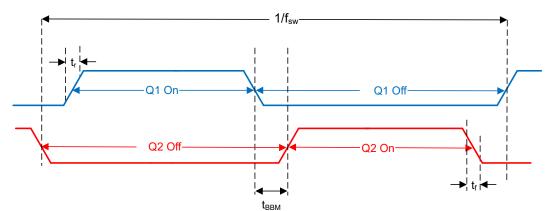

#### 8.4.1.1 Soft-Start

SN6507-Q1 device supports soft-start feature. Upon power up or when EN/UVLO pin transitions from Low to High, the gate drive of the output powerFET is gradually increased over a period of time from 0 V to full driving

strength. Soft-start prevents high inrush current from VCC while charging large secondary side decoupling capacitors, and also prevents overshoot in secondary voltage during power-up.

The sort-start time to ramp to the peak switch current is calculated by the capacitor and resistor on SS/ILIM pin with the following formula.

$$T_{SS} = \frac{C_{SS}}{275\mu A - \frac{0.6}{R_{ILIM}}}$$

(4)

During soft-start, the over-current protection is disabled. To ensure a smooth transition between soft-start and the steady state, it's recommended to have a  $C_{SS}$  value between 50 nF and 5  $\mu$ F with an output capacitor,  $C_{OUT}$ , of less than 10 times the value of  $C_{SS}$ .

#### 8.4.2 Operation Mode

The SN6507-Q1 driver is in operation mode when EN pin is above  $EN_{UVLO}$ , VIN pin is above  $VCC_{UVLO}$ , and soft-start completes. In normal operation mode, the switching frequency is fixed, determined either by the CLK pin resistor or external Clock signal.

#### 8.4.3 Shutdown Mode

The device has a dedicated EN/UVLO pin to put the device in very low power mode to save power when not in use. EN/UVLO pin has an internal pull down resistor which keeps device disabled when not driven. When disabled or when  $V_{CC}$  is < 2.8 V, both drain outputs, SW1 and SW2, are tri-stated.

#### 8.4.4 SYNC Mode

The SN6507-Q1 has a CLK pin which can be used to synchronize the device with system clock and in turn with other SN6507-Q1 devices so that the system can control the exact switching frequency of the device. In SYNC mode, the CLK frequency is divided by two to drive the gates of powerFETs.  $\boxtimes$  9-2 shows the timing diagram for the same.

The device cannot automatically change from SYNC mode to switching frequency control using the internal oscillator or resistor-programmable switching frequency mode. If a valid external CLK signal is not present, the output will stop switching, and a power cycle will be required to change the switching mode back to using the internal oscillator or the adjustable switching frequency using  $R_{CLK}$ .

When the device is in SYNC mode, duty cycle control and SSM are not supported, therefore it's recommended to leave DC pin floating in SYNC mode to reduce the solution size.

Note that it is recommended that the SN6507-Q1  $V_{CC}$  pin powers up before CLK pin. Before device power-up, the initial state of external clock should be high-impedance.

### 9 Application and Implementation

注

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

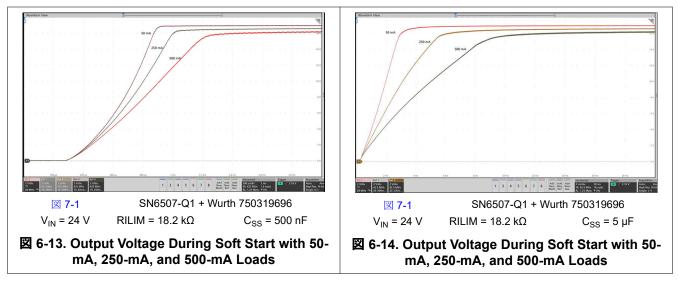

#### 9.1 Application Information

The SN6507-Q1 is a transformer driver designed for low-cost, small form-factor, isolated DC/DC converters using the push-pull topology. The device includes an oscillator that feeds a gate-drive circuit. The gate-drive, comprising a frequency divider and a break-before-make (BBM) logic, provides two complementary output signals which alternately turn the two output transistors on and off.

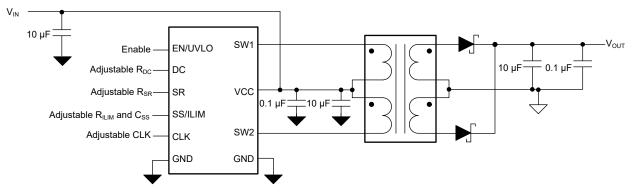

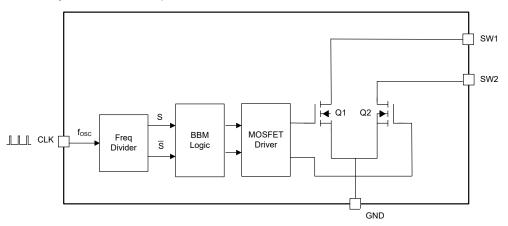

図 9-1. Block Diagram With Break-Before-Make Action

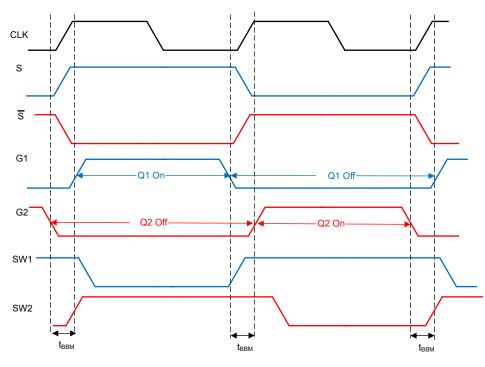

図 9-2. Output timing with Break-Before-Make Action

The output frequency of the oscillator is divided down by an asynchronous divider that provides two complementary output signals, S and  $\overline{S}$ , with a 50% duty cycle. A subsequent break-before-make logic inserts a dead-time between the high-pulses of the two signals. The resulting output signals, G<sub>1</sub> and G<sub>2</sub>, present the gate-drive signals for the output transistors Q<sub>1</sub> and Q<sub>2</sub>. As shown in  $\boxtimes$  9-2, before either one of the gates can assume logic high, there must be a short time period during which both signals are low and both transistors are high-impedance. This short period, known as break-before-make time, is required to avoid shorting out both ends of the primary.

### 9.2 Typical Application

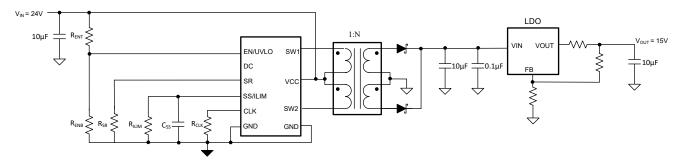

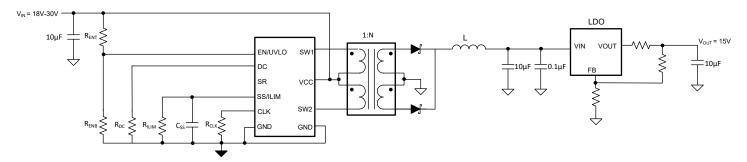

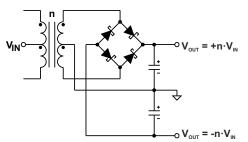

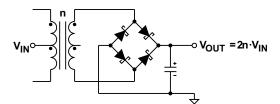

Two application cases are discussed. One is for Fixed input with slew rate control. The other is for wide-ranging input with duty cycle control.

図 9-3. Typical Application Schematic for Fixed Input with Slew Rate Control

図 9-4. Typical Application Schematic for Wide-Ranging Input with Duty Cycle Control

#### 9.2.1 Design Requirements

For this design example, use the parameters listed in  $\pm$  9-1 as design parameters.

| 表 9-1. Design F | Parameters |

|-----------------|------------|

|-----------------|------------|

| PARAMETER                    | COMMENT                                 | EXAMPLE VALUE                           |

|------------------------------|-----------------------------------------|-----------------------------------------|

| Fixed V <sub>IN</sub>        | Input voltage for fixed input case      | 24 V ± 2%                               |

| Wide-ranging V <sub>IN</sub> | Input voltage range for wide-input case | 18 V (min)<br>24 V (typ.)<br>30 V (max) |

| f <sub>SW</sub>              | Switching frequency                     | 1 MHz ± 10%                             |

| V <sub>OUT</sub>             | Output voltage                          | 15 V                                    |

| I <sub>LOAD</sub>            | Load current                            | 200 mA                                  |

| ILIM                         | Peak Current Limit                      | 500 mA                                  |

| UVLO                         | Under Voltage Lockout                   | 9 V                                     |

| SS                           | Soft-Start Time                         | 2 ms                                    |

#### 9.2.2 Detailed Design Procedure

This section presents a detailed design procedures using the SN6507-Q1 transformer driver. The following recommendations on components selection focus on the design of an efficient push-pull converter with high current drive capability. Two cases are discussed: wide input range with duty cycle control, and a compact design with a fixed input voltage.

The pin configuration of SN6507-Q1 are discussed by 5 simple steps, followed by the selection of external components, including diodes, capacitors, inductor, LDO and transformers.

#### 9.2.2.1 Pin Configuration

Here is an example of how to configure the SN6507-Q1 pins in 5 simple steps.

#### Step 1: Set the Switching Frequency

First, set the driver switching frequency with  $R_{CLK}$  using  $\frac{1}{5}$  8-1.

For example:  $R_{CLK}$  = 9.6 k $\Omega$  or shorted to GND, sets typical f<sub>SW</sub> at about 1 MHz.

#### Step 2: Set the Input UVLO

The EN/UVLO (undervoltage lockout) pins are used to set minimum input voltage that the driver starts switching. The resister divider value can be calculated by  $\pm 3$ .

For example, if the input threshold ( $V_{ON}$ ) is expected to be at 9 V, the resistors are calculated as  $R_{ENT}/R_{ENB}$  = 5

Therefore, the resistors values are chosen as:

$R_{ENT} = 5 k\Omega, R_{ENB} = 1 k\Omega$

To make the device self-start at default UVLO thresold (2.8 V typical), users can skip Step 2 and directly short the EN/UVLO pin to VCC.

#### Step 3: Set the Current Limit and Soft-Start Time

The current limit can be set by a resistor on SS/ILIM pin according to  $\frac{1}{5}$  8-3. Peak currents may be very high during operation of the overcurrent protection system until the fault is cleared.

For example, to set the current limit is set at 500 mA (typical), the recommended R<sub>ILIM</sub> is 50 kΩ.

Once  $R_{ILIM}$  is determined, substitue  $R_{ILIM}$  into  $\pm 4$ , the soft-time calculation is:

$$T_{SS} = \frac{C_{SS}}{275\mu A - \frac{0.6}{50k}}$$

Taking 2 ms (typical) soft-start time as an example, the capacitor on SS/ILIM pin : $C_{SS}$  = 0.5 uF.

Note that both  $R_{ILIM}$  and  $C_{SS}$  are required on SS/ILIM pin to ensure the robust operation of this device. Missing the RC connection or leaving the pin floating should be avoided.

#### Step 4: Set the Duty Cycle

For fixed input cases, the duty cycle feature is not needed. This step can be skipped by leaving DC pin floating, so that the device will operate at default maximum duty (48% typical). The maximum duty cycle is determined by the switching period and the deadtime (70 ns typical) to avoid overlap of two power switches.

For wide-input cases, the duty cycle feature can be enabled by connecting a resistor  $R_{DC}$  on DC pin, and an inductor at the output side. The inductor selection is presented in 2222.2.4.

To achieve maximum input compensation, the DC is set close to 0.25 (25% duty cycle) at typical V<sub>CC</sub> (24 V). The R<sub>DC</sub> is calculated as 50.9 k $\Omega$  by substituting DC = 0.25, V<sub>CC</sub> = 24 V, and R<sub>CLK</sub> = 9.6 into  $\pm$  1, where both R<sub>CLK</sub> and R<sub>DC</sub> are in k $\Omega$ .

(5)

(6)

#### 9.2.2.2 LDO Selection

SN6507-Q1 is an open-loop transformer driver without load regulation capability. The output voltage may vary over a wide range load current. Therefore, if a high-accuracy, load independent supply is required, the implementation of a low dropout regulator (LDO) on the output side is strongly advised.

The minimum requirements for a suitable low dropout regulator are:

- Its current drive capability should slightly exceed the specified load current of the application to prevent the LDO from dropping out of regulation. Therefore, for a load current of 200 mA, choose a 200 mA to 300 mA LDO. While regulators with higher drive capabilities are acceptable, they also usually possess higher dropout voltages that will reduce overall converter efficiency.

- The internal dropout voltage, V<sub>DO</sub>, at the specified load current should be as low as possible to maintain efficiency. For a low-cost 300 mA LDO, a V<sub>DO</sub> of 600 mV at 300 mA is common. Be aware; however, that this lower value is usually specified at room temperature and can increase by a factor of 2 over temperature, which in turn will raise the required minimum input voltage.

- The required minimum input voltage preventing the regulator from dropping out of line regulation is given with:

$$V_{I-min} = V_{DO-max} + V_{O-max}$$

This means in order to determine V<sub>I</sub> for worst-case condition, the user must take the maximum values for V<sub>DO</sub> and V<sub>O</sub> specified in the LDO data sheet for rated output current (that is, 200 mA) and add them together. Also specify that the output voltage of the push-pull rectifier at the specified load current is equal or higher than V<sub>I-min</sub>. If it is not, the LDO will lose line-regulation and any variations at the input passes straight through to the output. Hence, below V<sub>I-min</sub> the output voltage follows the input and the regulator behaves like a simple conductor.

• The maximum regulator input voltage must be higher than the rectifier output under no-load. Under this condition there is no secondary current reflected back to the primary, thus making the voltage drop across R<sub>DS-on</sub> negligible and allowing the entire converter input voltage to drop across the primary. At this point, the secondary reaches its maximum voltage of

$$V_{S-max} = V_{IN-max} \times N$$

with  $V_{IN-max}$  as the maximum converter input voltage and n as the transformer turns ratio. Thus to prevent the LDO from damage the maximum regulator input voltage must be higher than  $V_{S-max}$ .  $\gtrsim$  9-2 lists the maximum secondary voltages for various turns ratios commonly applied in push-pull converters.

|                                           | LDO                    |                        |    |    |

|-------------------------------------------|------------------------|------------------------|----|----|

| CONFIGURATION                             | V <sub>S-max</sub> [V] | V <sub>I-max</sub> [V] |    |    |

| 24 V <sub>IN</sub> to 15 V <sub>OUT</sub> | 25                     | 1.38:1                 | 18 | 25 |

| 12 $V_{IN}$ to 15 $V_{OUT}$               | 12.5                   | 1:1.5                  | 19 | 25 |

#### 表 9-2. Required Maximum LDO Input Voltages for Various Push-Pull Configurations

#### 9.2.2.3 Diode Selection

A rectifier diode should always possess low-forward voltage to provide as much voltage to the converter output as possible. However, when SN6507-Q1 is used in high-frequency switching applications, the diode must also possess a low total capacitance, a short recovery time and a current rating greater than the load current. Schottky diodes meet these requirements and are therefore strongly recommended in SN6507-Q1 push-pull converter designs.

The necessary diode reverse voltage rating,  $V_R$ , is determined by the transformer secondary side voltage plus any voltage ringing. The voltage ringing, however, is difficult to predict, because it depends on multiple factors, such as loop resistance, the leakage inductance of the transformer, and the diode junction capacitance. As a rule of thumb, the diode voltage rating should be greater than 1.5 times the transformer turns ratio multiplied by the maximum input voltage. Because the two secondary windings are connected across the rectifier bridge, a factor of two is needed, producing the diode maximum DC blocking voltage rating:

(7)

Diode  $V_R > 1.5 \times 2 \times N \times V_{IN(MAX)}$

For high-efficiency designs, diodes with low forward voltage,  $V_F$ , and diode capacitance,  $C_T$ , can be used, like BAT165E6327HTSA1 or equivalent can be used for high-efficiency 15-V outputs. Diode parameters like these parasitics and reverse recovery will impact system efficiency and can affect emissions. For low-emissions designs, low-emissions diodes can be used, like PMEG200G20ELRX or equivalent can be used for low-emissions outputs up to 100 V.

#### 9.2.2.4 Capacitor and Inductor Selection

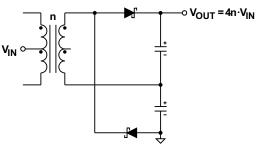

#### **Capacitor Selection**

The capacitors in the push-pull converter circuits are normally multi-layer ceramic chip (MLCC) capacitors. As with many high speed CMOS ICs, the device requires a bypass capacitor of 100 nF. Ensure this capacitor is placed within 2 mm of the SN6507-Q1 VCC pin.

The input bulk capacitor at the center-tap of the transformer primary side supports large currents into the primary winding during the fast switching transients. For minimum ripple make this capacitor 1  $\mu$ F to 10  $\mu$ F, where 10  $\mu$ F is preferred. Place this capacitor close to the transformer primary winding center-tap to minimize trace inductance. If placed on the opposite side of the PCB from the transformer, an additional 100 nF capacitor can be placed on the same layer and close to the transformer center tap. Use two vias in parallel for each connection between these capacitors to the transformer center tap to ensure low-inductance paths.

The bulk capacitor at the rectifier output smooths the output voltage. Make this capacitor 500 nF to 10  $\mu$ F. To avoid hitting OCP at the transistion from soft-start to steady state, the output capacitor C<sub>OUT</sub> is recommended to be less than 10 times of C<sub>SS</sub> connected to the SS/ILIM pin. Otherwise, if there is a short soft-start time due to a small C<sub>SS</sub> value, the output capacitor is only partially charged and sees high current spikes on the first switching cycles after the device exits soft start mode.

Optional capacitors of values between 1 nF to 4.7 nF can be connected to the control pins of SN6507-Q1 for filtering if operating in noisy environments.

If an LDO is used, an additional small capacitor at the LDO input is not necessarily required. However, good analog design practice suggests using a small value of 47 nF to 100 nF improves the regulator's transient response and noise rejection.

If an LDO is used, an additional capacitor at the LDO output buffers the regulated output supply for the subsequent isolator and transceiver circuitry. The choice of output capacitor depends on the LDO stability requirements specified in the data sheet. However, in most cases, a low-ESR ceramic capacitor in the range of  $4.7 \,\mu\text{F}$  to  $10 \,\mu\text{F}$  will satisfy these requirements.

#### Inductor Selection

The inductor is required only for duty cycle feature. The minimum inductor value ( $L_{MIN}$ ) is is calculated by  $\neq 2$ . Higher inductance produces better regulation and lower voltage ripple, but requires a correspondingly larger size inductor. The optimum inductor value is determined by taking into account the tradeoff between the regulation performance and the size.

For example, when V<sub>OUT</sub> = 15 V, V<sub>IN TYP</sub> = 15 V, V<sub>IN MAX</sub> = 18 V, I<sub>LOAD MIN</sub> = 250 mA,  $f_{SW}$  = 1 MHz, D = 0.25, the minimum inductance is calculated to be 50 µH.

$$L_{MIN} = 15V \times \frac{1 - 2 \times 0.25 \times (15V/18V)}{4 \times 0.25A \times 1MHz} = 8.75\mu H$$

(8)

#### 9.2.2.5 Transformer Selection

#### 9.2.2.5.1 V-t Product Calculation

To prevent a transformer from saturation its V-t product must be greater than the maximum V-t product applied by the device: the maximum time this voltage is applied to the primary for half the period of the lowest frequency at the specified input voltage. For designs using duty cycle control, the maximum V-t applied by the device can be calculated by the typical voltage applied for one quarter of the period of the lowest switching frequency. For systems using a clock frequency set by  $R_{CLK}$ , f<sub>min</sub> can be estimated as 15% below the typical or approximate

switching frequency value,  $f_{SW}$ , for the corresponding  $R_{CLK}$  from  $\forall 2 \neq \forall \exists \forall Programmable Switching Frequency$ . For systems where the CLK pin is connected to GND, the minimum specified  $F_{SW}$  from  $\forall 2 \neq \forall \exists \forall 6$  should be used. Therefore, the transformer's minimum V-t product is determined through  $\exists 9$  for fixed inputs and  $\exists 10$  for wide-ranging inputs using duty cycle control:

$$Vt_{min} \ge V_{IN(max)} \times \frac{T_{max}}{2} = \frac{V_{IN(max)}}{2 \times f_{min}}$$

(9)

$$Vt_{min} \ge V_{IN(typ)} \times \frac{T_{max}}{4} = \frac{V_{IN(typ)}}{4 \times f_{min}}$$

(10)

#### **Example of Fixed Input:**

For a fixed input system with  $f_{SW(min)}$  of 780 kHz and a  $V_{IN}$  = 24 V supply with ±10 % tolerance,  $\neq$  9 yields the minimum V-t product of:

$$Vt_{min} \ge \frac{26.4V}{2 \times 780kHz} = 16.9 \, V\mu s \tag{11}$$

#### Example of Wide-Ranging Input:

Taking the assumption of f<sub>SW(min)</sub> as 780 kHz with a V<sub>IN(typ)</sub> 24 V supply, 式 10 yields the minimum V-t product of:

$$Vt_{min} \ge \frac{24V}{4 \times 780 kHz} = 7.7 V \mu s$$

(12)

While Vt-wise all of these transformers can be driven by the device, other important factors such as isolation voltage, transformer wattage, and turns ratio must be considered before making the final decision.

#### 9.2.2.5.2 Turns Ratio Estimate

From previous section, it has been determined that the transformer chosen must have a V-t product of 15 V $\mu$ s. However, before searching the manufacturer web sites for a suitable transformer, the user still needs to know its minimum turns ratio that allows the push-pull converter to operate flawlessly over the specified current and temperature range. This minimum transformation ratio is expressed through the ratio of minimum secondary to minimum primary voltage multiplied by a correction factor that takes the transformer's typical efficiency of 97% into account:

$$V_{P-min} = V_{IN-min} - V_{DS-max}$$

(13)

$V_{S-min}$  must be large enough to allow for a maximum voltage drop,  $V_{F-max}$ , across the rectifier diode and still provide sufficient input voltage for the regulator to remain in regulation. From the  $\frac{2}{2} \frac{2}{2} \frac{9.2.2.2}{2}$  section, this minimum input voltage is known and by adding  $V_{F-max}$  gives the minimum secondary voltage with:

$$V_{\text{S-min}} = V_{\text{F-max}} + V_{\text{DO-max}} + V_{\text{O-max}}$$

(14)

図 9-5. Establishing the Required Minimum Turns Ratio Through N<sub>min</sub> = 1.03 × V<sub>S-min</sub> / V<sub>P-min</sub>

Then calculating the available minimum primary voltage,  $V_{P-min}$ , involves subtracting the maximum possible drain-source voltage of the device,  $V_{DS-max}$ , from the minimum converter input voltage  $V_{IN-min}$ :

(15)

$V_{DS-max}$  however, is the product of the maximum  $R_{DS(on)}$  and  $I_D$  values for a given supply specified in the data sheet:

$$V_{\rm DS-max} = R_{\rm DS-max} \times I_{\rm Dmax}$$

(16)

Then inserting  $\neq$  16 into  $\neq$  15 yields:

$$V_{P-min} = V_{IN-min} - R_{DS-max} \times I_{Dmax}$$

(17)

and inserting  $\neq$  17 and  $\neq$  14 into  $\neq$  13 provides the minimum turns ration with:

$$N_{min} = 1.03 \times \frac{V_F - max + V_{DO} - max + V_O - max}{V_{IN} - min - R_{DS} - max \times I_D - max}$$

(18)

Examples are given on the calculation method. One is for the fixed input case without duty cycle control. The other is for the wide-ranging input, with or without duty cycle control.

#### Example of Fixed Input:

For a fixed 24 V V<sub>IN</sub> to 15 V<sub>OUT</sub> converter using the rectifier diode PMEG200G20ELRX and the LM317A LDO, the data sheet values taken for a load current of 500mA and a maximum temperature of 85°C are V<sub>F-max</sub> = 0.5 V, V<sub>DO-max</sub> = 0.7 V, and V<sub>O-max</sub> = 15.15 V.

Then assuming that the converter input voltage is taken from a 24V regulated supply with a maximum  $\pm 2\%$  accuracy makes V<sub>IN-min</sub> = 23.52 V. Finally the maximum values for drain-source resistance and drain current at 24 V are taken from the data sheet with R<sub>DS-max</sub> = 1  $\Omega$  and I<sub>D-max</sub> = 0.5 A.

Inserting the values above into the Equation above yields a minimum turns ratio of:

$$N_{min} = 1.03 \times \frac{0.5 \, V + 0.7 \, V + 15.1 \, V}{23.52 \, V - 1 \, \Omega \times 0.5 \, A} = 0.72 \tag{19}$$

#### Example of Wide-Ranging Input:

#### • Wide-Ranging Input without Duty-Cycle Control

For converter designs with wide-input range but no duty cycle control, the turns ratio needs to take the minimum input voltage into consideration.

Assuming the same diode and LDO are used, the calculation, so  $V_{F-max}$  = 0.5 V,  $V_{DO-max}$  = 0.7 V, and  $V_{O-max}$  = 15.15 V.

The input range from 18 V up to 30 V makes  $V_{IN-min}$  = 18 V. The input range from 18 V up to 30 V with 24 V typical makes  $V_{IN-min}$  = 18 V. Substituting the same  $R_{DS-max}$  = 1  $\Omega$  and  $I_{D-max}$  = 0.5 A into the Equation above yields to a minimum turns ratio of:

$$N_{min} = 1.03 \times \frac{0.5 \, V + 0.7 \, V + 15.1 \, V}{18 \, V - 1 \, \Omega \times 0.5 \, A} = 0.96 \tag{20}$$

#### • Wide-Ranging Input with Duty-Cycle Control

For converter designs with wide-input range, the duty cycle feature is useful to compensate input variaton. But care must be taken to make sure that high turns ratios don't lead to primary currents that exceed the specified current limits of the device.

$$N_{min} = 1.03 \times \frac{V_F - max + V_{DO} - max + V_O - max}{V_{IN} - typ - R_{DS} - max \times I_D - max} \times \frac{1}{2D_{typ}}$$

(21)

Assuming the same diode and LDO are used, so  $V_{F-max} = 0.5 \text{ V}$ ,  $V_{DO-max} = 0.7 \text{ V}$ , and  $V_{O-max} = 15.15 \text{ V}$ .

It's recommends the use to set the DC=25% at typical V<sub>IN-typ</sub> = 24 V. Substituting the same R<sub>DS-max</sub> = 1  $\Omega$  and I<sub>D-max</sub> = 0.5 A into the Equation above yields to a minimum turns ratio of:

$$N_{min} = 1.03 \times \frac{0.5 \, V + 0.7 \, V + 15.1 \, V}{24 \, V - 1 \, \Omega \times 0.5 \, A} \times \frac{1}{2 \times 0.25} = 1.38 \tag{22}$$

#### 9.2.2.6 Low-Emissions Designs

For isolated power supply designs requiring low levels of radiated and conducted emissions, the following recommendations can help minimize emissions from SN6507-Q1 and its surrounding components:

- Ensure a push-pull isolation transformer with low parasitics, like leakage inductance and parasitic capacitances, is used to minimize common-mode currents across the isolation barrier and antenna effects in the system.

- Use low-emissions rectifier diodes with low recovery times, like PMEG200G20ELRX or equivalent.