**TAD5142**

# TAD5142 110dB のダイナミック レンジを持ち、ヘッドホン/ライン ドライバ を備えたハードウェア制御ステレオ オーディオ DAC

## 1 特長

- ステレオ オーディオ DAC の性能:

- DAC から差動ライン出力までのダイナミックレ ンジ:110dB

- DAC から疑似差動ヘッドホン出力までのダイナ ミック レンジ:107dB

- **DAC** から差動ライン出力までの THD+N:-100dB

- 出力電圧:

- 差動ライン出力 / レシーバ、2V<sub>RMS</sub> フルスケ

- 疑似差動ヘッドホン、1V<sub>RMS</sub>フルスケール

- シングルエンドライン出力、1V<sub>RMS</sub>フルスケ

- DAC サンプルレート (f<sub>s</sub>) = 8kHz~192kHz

- 主な特長

- ピンまたはハードウェア制御

- オーディオ シリアル インターフェイス

- フォーマット:TDM、LJ または I<sup>2</sup>S

- バスコントローラおよびターゲットモード

- TDM モードのデイジーチェーン

- ワード長:24 ビットまたは32 ビットを選択可

- ピンで選択可能なデジタル補間フィルタオプシ ョン:

- リニア位相

- 低レイテンシ

- 自動クロック検出

- クロック エラー時の割り込み出力

- 単一電源動作 AVDD: 1.8V または 3.3V

- I/O 電源動作:1.8V または 3.3V

- 温度グレード 1:-40°C ≤ T<sub>A</sub> ≤ +125°C

# 2 アプリケーション

- AV レシーバ

- IP ネットワーク カメラ

- サウンドバー

- テレビ会議システム

#### 3 概要

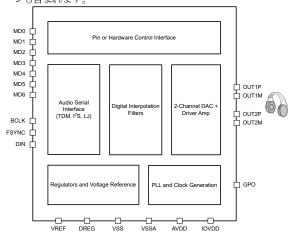

TAD5142 は、ライン出力とヘッドホン負荷のどちらにも構 成でき、シングルエンド出力と差動出力の両方をサポート している、 $2V_{RMS}$ 、110dB のステレオ オーディオ DAC で す。 本デバイスはフェーズ ロック ループ (PLL) を内蔵し ており、最大 192kHz のサンプル レートに対応していま す。TAD5142 は、16Ω のヘッドホン負荷を最大 62.5mW で駆動できます。TAD5142 は、コントローラおよびターゲ ット モードの時分割多重化 (TDM)、左揃え (LJ)、I<sup>2</sup>S オ ーディオ フォーマットをサポートしており、ピンまたはハー ドウェアで制御できます。このように高性能な機能、ピン制 御、そして単一電源動作であるため、TAD5142 はスペー スに制約のあるオーディオ アプリケーションに最適な選択 肢となっています。

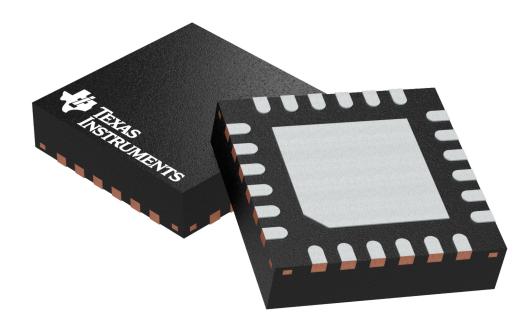

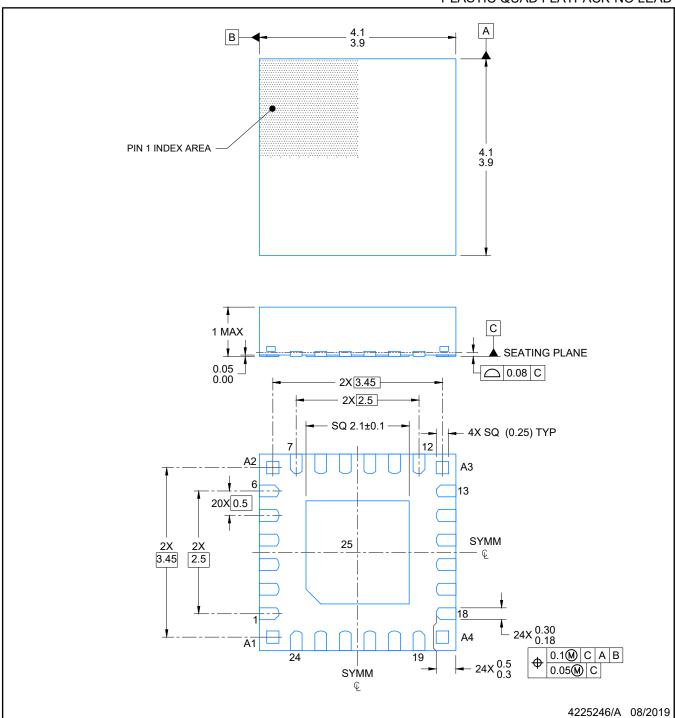

## 製品情報

| 部品番号    | パッケージ <sup>(1)</sup> | パッケージ サイズ (公<br>称) <sup>(2)</sup> |

|---------|----------------------|-----------------------------------|

| TAD5142 |                      | <b>4mm×4mm、0.5mm</b><br>ピッチ       |

- (1) 利用可能なすべてのパッケージについては、データシートの末尾 にある注文情報を参照してください。

- パッケージ サイズ (長さ×幅) は公称値であり、該当する場合はピ ンも含まれます。

概略ブロック図

## **Table of Contents**

| 4 柱目                                                           |                  |

|----------------------------------------------------------------|------------------|

| 1 特長                                                           |                  |

| 2 アプリケーション                                                     | 1                |

| 3 概要                                                           | 1                |

| 4 Pin Configuration and Functions                              |                  |

| 5 Specifications                                               |                  |

| 5.1 Absolute Maximum Ratings                                   |                  |

| 5.2 ESD Ratings                                                |                  |

| 5.3 Recommended Operating Conditions                           |                  |

| 5.4 Thermal Information                                        |                  |

| 5.5 Electrical Characteristics                                 | 6                |

| 5.6 Timing Requirements: TDM, I <sup>2</sup> S or LJ Interface | 9                |

| 5.7 Switching Characteristics: TDM, I <sup>2</sup> S or LJ     |                  |

| Interface                                                      | 9                |

| 5.8 Timing Diagrams                                            | 10               |

| 5.9 Typical Characteristics                                    | <mark>1</mark> 1 |

| 6 Detailed Description                                         | 14               |

| 6.1 Overview                                                   | 14               |

| 6.2 Functional Block Diagram                                   | 14               |

| 6.3 realure Description                 | <del>  4</del>  |

|-----------------------------------------|-----------------|

| 6.4 Device Functional Modes             | 32              |

| 7 Application and Implementation        | 33              |

| 7.1 Application Information             | 33              |

| 7.2 Typical Application                 |                 |

| 7.3 Power Supply Recommendations        | 35              |

| 7.4 Layout                              | 35              |

| 8 Device and Documentation Support      | <mark>37</mark> |

| 8.1 Documentation Support               | 37              |

| 8.2ドキュメントの更新通知を受け取る方法                   | 37              |

| 8.3 サポート・リソース                           | 37              |

| 8.4 Trademarks                          | 37              |

| 8.5 静電気放電に関する注意事項                       | 37              |

| 8.6 用語集                                 | 37              |

| 9 Revision History                      | 37              |

| 10 Mechanical, Packaging, and Orderable |                 |

| Information                             | 37              |

|                                         |                 |

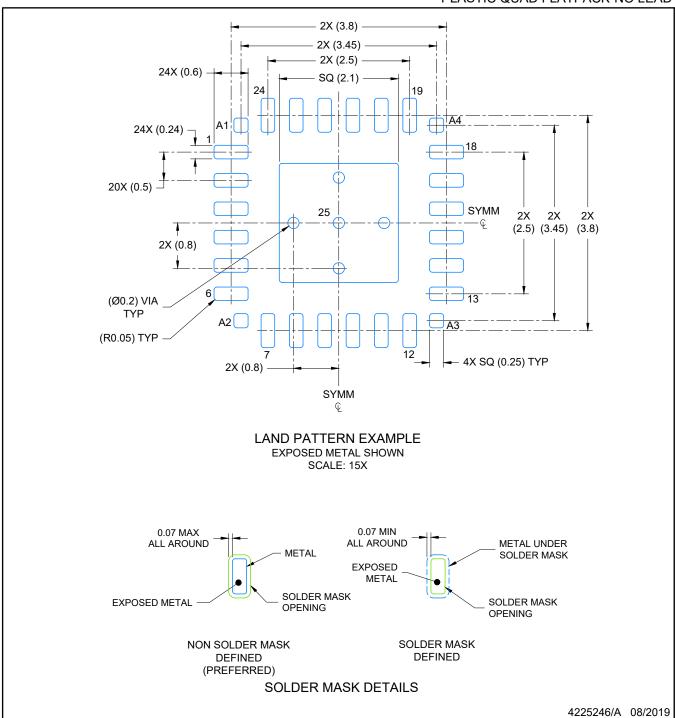

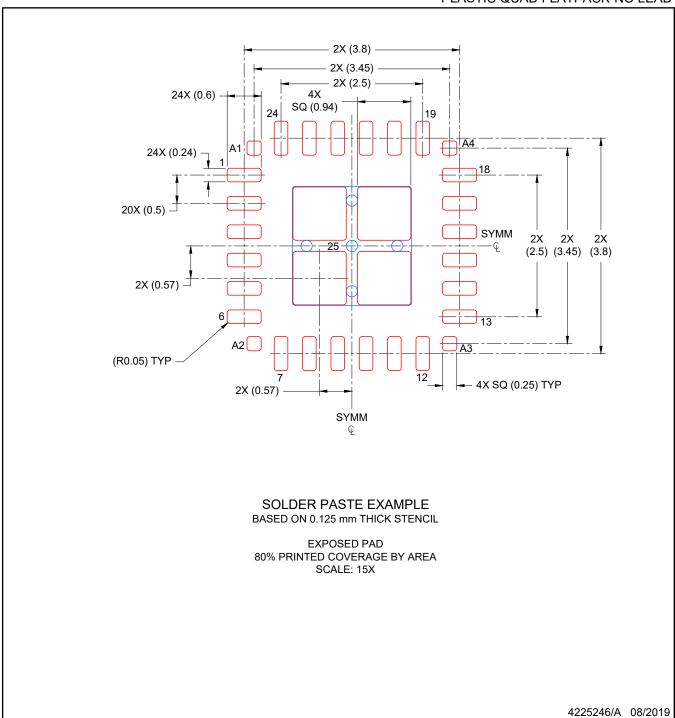

# 4 Pin Configuration and Functions

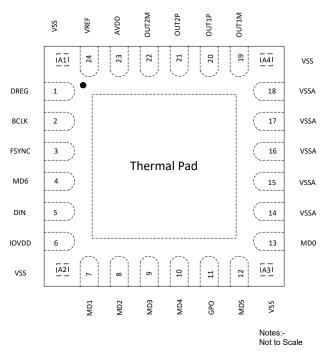

図 4-1. 24-Pin QFN Package with Exposed Thermal Pad and Corner Pins, Top View

表 4-1. Pin Functions

| P     | IN  | TYPE                                                             | DESCRIPTION                                                                    |  |

|-------|-----|------------------------------------------------------------------|--------------------------------------------------------------------------------|--|

| NAME  | NO. | ITPE                                                             | DESCRIPTION                                                                    |  |

| VSS   | A1  | Ground                                                           | Ground pin. Short directly to board ground plane.                              |  |

| DREG  | 1   | Digital<br>Supply                                                | Digital on-chip regulator output voltage for digital supply (1.55V, nominal)   |  |

| BCLK  | 2   | Digital<br>I/O                                                   | Audio serial data interface bus bit clock                                      |  |

| FSYNC | 3   | Digital<br>I/O                                                   | Audio serial data interface bus frame synchronization signal                   |  |

| MD6   | 4   | Digital                                                          | TDM mode: Daisy chain output                                                   |  |

|       |     | I/O I <sup>2</sup> S/LJ mode: Mono/Stereo DAC Channels selection |                                                                                |  |

| DIN   | 5   | Digital<br>Input                                                 | Audio serial data interface bus input                                          |  |

| IOVDD | 6   | Digital<br>Supply                                                | Digital I/O power supply (1.8V or 3.3V, nominal)                               |  |

| VSS   | A2  | Ground                                                           | Ground pin. Short directly to board ground plane.                              |  |

| MD1   | 7   | Digital                                                          | Controller mode: Frame rate and BCLK frequency selection                       |  |

| INIDT | /   | Input                                                            | Target mode: AVDD supply, word length, and interpolation filter type selection |  |

| MD2   | 8   | Digital                                                          | Controller mode: Frame rate and BCLK frequency selection                       |  |

| IVIDZ | 0   | Input                                                            | Target mode: AVDD supply, word length, and interpolation filter type selection |  |

| MD3   | 9   | Digital                                                          | Controller mode: Controller clock input                                        |  |

|       |     | Input                                                            | Target mode: Short directly to board ground plane.                             |  |

| MD4   | 10  | Digital<br>Input                                                 | DAC output configuration selection                                             |  |

| GPO   | 11  | Digital<br>Output                                                | Interrupt output (latched)                                                     |  |

# 表 4-1. Pin Functions (続き)

| PI    | N   | TYPE             | DESCRIPTION                                                                                    |  |

|-------|-----|------------------|------------------------------------------------------------------------------------------------|--|

| NAME  | NO. | ITPE             | DESCRIPTION                                                                                    |  |

| MD5   | 12  | Digital<br>Input | DAC output configuration selection                                                             |  |

| VSS   | A3  | Ground           | Ground pin. Short directly to board ground plane.                                              |  |

| MD0   | 13  | Analog<br>Input  | fulti-level analog input for controller/target mode and I <sup>2</sup> S/TDM/LJ mode selection |  |

| VSSA  | 14  | Ground           | Short directly to board ground plane                                                           |  |

| VSSA  | 15  | Ground           | Short directly to board ground plane                                                           |  |

| VSSA  | 16  | Ground           | Short directly to board ground plane                                                           |  |

| VSSA  | 17  | Ground           | Short directly to board ground plane                                                           |  |

| VSSA  | 18  | Ground           | Short directly to board ground plane                                                           |  |

| VSS   | A4  | Ground           | Ground pin. Short directly to board ground plane.                                              |  |

| OUT1M | 19  | Analog<br>Output | Analog output 1M pin                                                                           |  |

| OUT1P | 20  | Analog<br>Output | Analog output 1P pin                                                                           |  |

| OUT2P | 21  | Analog<br>Output | Analog output 2P pin                                                                           |  |

| OUT2M | 22  | Analog<br>Output | Analog output 2M pin                                                                           |  |

| AVDD  | 23  | Analog<br>Supply | Analog power supply (1.8V or 3.3V, nominal)                                                    |  |

| VREF  | 24  | Analog           | Analog reference voltage filter output                                                         |  |

4

Product Folder Links: TAD5142

## **5 Specifications**

## 5.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

| 1 5 1                      | 3 (                                             | MIN  | MAX         | UNIT |

|----------------------------|-------------------------------------------------|------|-------------|------|

| Supply voltage             | AVDD to VSS (thermal pad)                       | -0.3 | 3.9         | V    |

| Supply voltage             | IOVDD to VSS (thermal pad)                      | -0.3 | 3.9         | V    |

| Ground voltage differences | VSSA to VSS (thermal pad)                       | -0.3 | 0.3         | V    |

| Digital input voltage      | Digital input pins voltage to VSS (thermal pad) | -0.3 | IOVDD + 0.3 | V    |

|                            | Functional ambient, T <sub>A</sub>              | -55  | 125         |      |

| Temperature                | Operating ambient, T <sub>A</sub>               | -40  | 125         | °C   |

|                            | Junction, T <sub>J</sub>                        | -40  | 150         | C    |

|                            | Storage, T <sub>stg</sub>                       | -65  | 150         |      |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

## 5.2 ESD Ratings

|                    |                         |                                                                       | VALUE | UNIT |

|--------------------|-------------------------|-----------------------------------------------------------------------|-------|------|

| V <sub>(ESD)</sub> | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>     | ±2000 | V    |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per ANSI/ESDA/JEDEC JS-002 <sup>(2)</sup> | ±500  | V    |

- (1) JEDEC document JEP155 states that 500V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250V CDM allows safe manufacturing with a standard ESD control process.

## **5.3 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)

|                                                                  | MIN                                                                                                                                                                                                                                                                                           | NOM                                                                                                                                                                                                                                                                                                                                                                                          | MAX                                                                                                                                                                                                                                                                                                                                                                                                               | UNIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                  |                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Analog supply voltage to VSS (thermal pad) - AVDD 3.3V operation | 3.0                                                                                                                                                                                                                                                                                           | 3.3                                                                                                                                                                                                                                                                                                                                                                                          | 3.6                                                                                                                                                                                                                                                                                                                                                                                                               | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Analog supply voltage to VSS (thermal pad) - AVDD 1.8V operation | 1.65                                                                                                                                                                                                                                                                                          | 1.8                                                                                                                                                                                                                                                                                                                                                                                          | 1.95                                                                                                                                                                                                                                                                                                                                                                                                              | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| IO supply voltage to VSS (thermal pad) - IOVDD 3.3V operation    | 3.0                                                                                                                                                                                                                                                                                           | 3.3                                                                                                                                                                                                                                                                                                                                                                                          | 3.6                                                                                                                                                                                                                                                                                                                                                                                                               | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| IO supply voltage to VSS (thermal pad) - IOVDD 1.8V operation    | 1.65                                                                                                                                                                                                                                                                                          | 1.8                                                                                                                                                                                                                                                                                                                                                                                          | 1.95                                                                                                                                                                                                                                                                                                                                                                                                              | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| ,                                                                | 1                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                              | '                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Digital input pins (MD1 to MD6) voltage to VSS (thermal pad)     | 0                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                              | IOVDD                                                                                                                                                                                                                                                                                                                                                                                                             | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| MD0 pin w.r.t VSS (thermal pad)                                  | 0                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                              | AVDD                                                                                                                                                                                                                                                                                                                                                                                                              | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| TURE                                                             | -                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                              | '                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Operating ambient temperature                                    | -40                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                              | 125                                                                                                                                                                                                                                                                                                                                                                                                               | °C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                  | Analog supply voltage to VSS (thermal pad) - AVDD 1.8V operation  IO supply voltage to VSS (thermal pad) - IOVDD 3.3V operation  IO supply voltage to VSS (thermal pad) - IOVDD 1.8V operation  Digital input pins (MD1 to MD6) voltage to VSS (thermal pad)  MD0 pin w.r.t VSS (thermal pad) | Analog supply voltage to VSS (thermal pad) - AVDD 3.3V operation  Analog supply voltage to VSS (thermal pad) - AVDD 1.8V operation  1.65  IO supply voltage to VSS (thermal pad) - IOVDD 3.3V operation  3.0  IO supply voltage to VSS (thermal pad) - IOVDD 1.8V operation  1.65  Digital input pins (MD1 to MD6) voltage to VSS (thermal pad)  0  MD0 pin w.r.t VSS (thermal pad)  0  TURE | Analog supply voltage to VSS (thermal pad) - AVDD 3.3V operation  3.0 3.3  Analog supply voltage to VSS (thermal pad) - AVDD 1.8V operation  1.65 1.8  IO supply voltage to VSS (thermal pad) - IOVDD 3.3V operation  3.0 3.3  IO supply voltage to VSS (thermal pad) - IOVDD 1.8V operation  1.65 1.8  Digital input pins (MD1 to MD6) voltage to VSS (thermal pad)  0  MD0 pin w.r.t VSS (thermal pad)  0  TURE | Analog supply voltage to VSS (thermal pad) - AVDD 3.3V operation   3.0   3.3   3.6     Analog supply voltage to VSS (thermal pad) - AVDD 1.8V operation   1.65   1.8   1.95     IO supply voltage to VSS (thermal pad) - IOVDD 3.3V operation   3.0   3.3   3.6     IO supply voltage to VSS (thermal pad) - IOVDD 1.8V operation   1.65   1.8   1.95     Digital input pins (MD1 to MD6) voltage to VSS (thermal pad)   0   IOVDD     MD0 pin w.r.t VSS (thermal pad)   0   AVDD     TURE |

資料に関するフィードバック(ご意見やお問い合わせ)を送信

5

English Data Sheet: SLASF32

over operating free-air temperature range (unless otherwise noted)

|        |                                                                   | MIN | NOM | MAX                   | UNIT     |  |

|--------|-------------------------------------------------------------------|-----|-----|-----------------------|----------|--|

| OTHERS |                                                                   |     |     | •                     |          |  |

| CCLK   | MD3 controller mode clock frequency (CCLK) - IOVDD 3.3V operation |     |     | 36.864 <sup>(2)</sup> | )<br>MHz |  |

| CCLK   | MD3 controller mode clock frequency (CCLK) - IOVDD 1.8V operation |     |     | 24.576 <sup>(2)</sup> | IVITIZ   |  |

| CL     | Digital output load capacitance                                   |     | 20  | 50                    | pF       |  |

- (1) VSSA and VSS (thermal pad); all ground pins must be tied together and must not differ in voltage by more than 0.2V.

- (2) CCLK input rise time (V<sub>IL</sub> to V<sub>IH</sub>) and fall time (V<sub>IH</sub> to V<sub>IL</sub>) must be less than 5ns. For better audio noise performance, CCLK input must be used with low jitter.

#### **5.4 Thermal Information**

|                       |                                              | TAD5142    |      |

|-----------------------|----------------------------------------------|------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | RGE (VQFN) | UNIT |

|                       |                                              | 24 PINS    |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 38.4       | °C/W |

| $R_{\theta JC(top)}$  | Junction-to-case (top) thermal resistance    | 26.3       | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 15.9       | °C/W |

| ΨЈТ                   | Junction-to-top characterization parameter   | 0.5        | °C/W |

| ΨЈВ                   | Junction-to-board characterization parameter | 15.8       | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 13.8       | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

## 5.5 Electrical Characteristics

At  $T_A$  = 25°C, AVDD = 3.3V, IOVDD = 3.3V,  $f_{IN}$  = 1kHz sinusoidal signal,  $f_S$  = 48kHz, 32-bit audio data, BCLK = 256 ×  $f_S$ , TDM target mode, and linear phase interpolation filter, with 1200 $\Omega$ /600 $\Omega$  line-out load in differential/single-ended configuration or 32 $\Omega$  receiver differential load as applicable; measured filter free with an Audio Precision with a 20Hz to 20kHz un-weighted bandwidth, unless otherwise noted

|         | PARAMETER                   | TEST CONDITIONS                                                                                 | MIN | NOM | MAX | UNIT      |

|---------|-----------------------------|-------------------------------------------------------------------------------------------------|-----|-----|-----|-----------|

| DAC Per | rformance for Line Output/l | Head Phone Playback                                                                             |     |     |     |           |

|         |                             | Differential output between OUTxP and OUTxM, AVDD = 3.3V                                        |     | 2   |     |           |

|         |                             | Differential output between OUTxP and OUTxM, AVDD = 1.8V                                        |     | 1   |     |           |

|         |                             | Single-ended output, AVDD = 3.3V                                                                |     | 1   |     |           |

|         | Full Scale Output           | Single-ended output, AVDD = 1.8V                                                                |     | 0.5 |     | $V_{RMS}$ |

|         | Voltage                     | Pseudo-differential output between OUTxP and OUT1M with external common-mode sense, AVDD = 3.3V |     | 1   |     | Tuvio     |

|         |                             | Pseudo-differential output between OUTxP and OUT1M with external common-mode sense, AVDD = 1.8V |     | 0.5 |     |           |

|         |                             | Differential output, 0dBFS Signal, AVDD = 3.3V                                                  |     | 110 |     |           |

|         |                             | Single-ended output, 0dBFS Signal, AVDD = 3.3V                                                  |     | 107 |     |           |

| SNR     | Signal-to-noise ratio, A-   | Pseudo-differential output, 0dBFS Signal, AVDD                                                  |     | 107 |     | dB        |

| SINK    | weighted <sup>(1)</sup> (2) | Differential output, 0dBFS Signal, AVDD = 1.8V                                                  |     | 109 |     | ав        |

|         |                             | Single-ended output, 0dBFS Signal, AVDD = 1.8V                                                  |     | 104 |     |           |

|         |                             | Pseudo-differential output, 0dBFS Signal, AVDD = 1.8V                                           |     | 103 |     |           |

Product Folder Links: TAD5142

資料に関するフィードバック (ご意見やお問い合わせ) を送信

Copyright © 2024 Texas Instruments Incorporated

6

English Data Sheet: SLASF32

At  $T_A$  = 25°C, AVDD = 3.3V, IOVDD = 3.3V,  $f_{IN}$  = 1kHz sinusoidal signal,  $f_S$  = 48kHz, 32-bit audio data, BCLK = 256 ×  $f_S$ , TDM target mode, and linear phase interpolation filter, with 1200 $\Omega$ /600 $\Omega$  line-out load in differential/single-ended configuration or 32 $\Omega$  receiver differential load as applicable; measured filter free with an Audio Precision with a 20Hz to 20kHz un-weighted bandwidth, unless otherwise noted

|                  | PARAMETER                                       | TEST CONDITIONS                                                                               | MIN             | NOM  | MAX             | UNIT    |

|------------------|-------------------------------------------------|-----------------------------------------------------------------------------------------------|-----------------|------|-----------------|---------|

|                  |                                                 | Differential output, -60dBFS Signal, AVDD = 3.3V                                              |                 | 110  |                 |         |

|                  |                                                 | Single-ended output, –60dBFS Signal, AVDD = 3.3V                                              |                 | 107  |                 |         |

| DB.              | Dynamic range, A-weighted <sup>(2)</sup>        | Pseudo-differential output, –60dBFS Signal, AVDD = 3.3V                                       |                 | 107  |                 | dB      |

| DR               |                                                 | Differential output, –60dBFS Signal, AVDD = 1.8V                                              |                 | 109  |                 | αБ      |

|                  |                                                 | Single-ended output, –60dBFS Signal, AVDD = 1.8V                                              |                 | 104  |                 |         |

|                  |                                                 | Pseudo-differential output, –60dBFS Signal, AVDD = 1.8V                                       |                 | 103  |                 |         |

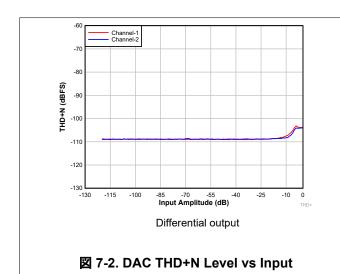

| THD+N            | Total harmonic distortion <sup>(2)</sup>        | Differential output, –1dBFS Signal, AVDD = 3.3V                                               |                 | -100 |                 | dB      |

| THD+N            | Total harmonic distortion <sup>(2)</sup>        | Single-ended output, –1dBFS Signal, AVDD = 3.3V                                               |                 | -96  |                 | dB      |

|                  | Headphone Load<br>Range <sup>(3)</sup>          |                                                                                               | 8               | 16   | 300             | Ω       |

|                  | Headphone/Line-out<br>Cap Load                  |                                                                                               | 0               | 100  | 550             | pF      |

|                  | Line-out Load Range                             |                                                                                               | 600             |      |                 | Ω       |

| DAC Cha          | nnel OTHER PARAMETER                            | RS                                                                                            |                 |      |                 |         |

|                  | Output Offset                                   | 0 Input, Differential Line-output                                                             |                 | 0.5  |                 | mV      |

|                  | Output Common Mode                              | Common Mode Level for OUTxP and OUTxM,<br>AVDD = 1.8V                                         |                 | 0.9  |                 | V       |

|                  | Output Common Mode                              | Common Mode Level for OUTxP and OUTxM,<br>AVDD = 3.3V                                         |                 | 1.65 |                 | V       |

|                  | Common Mode Error                               | DC Error in Common Mode Voltage                                                               |                 | ±10  |                 | mV      |

|                  | Output Signal<br>Bandwidth                      |                                                                                               |                 | 20   |                 | kHz     |

|                  | Input data word length                          | Pin-selectable                                                                                | 24              |      | 32              | Bits    |

|                  | Interchannel isolation                          |                                                                                               |                 | -120 |                 | dB      |

|                  | Gain Error                                      |                                                                                               |                 | 0.1  |                 | dB      |

|                  | Interchannel gain mismatch                      |                                                                                               |                 | 0.1  |                 | dB      |

|                  | Interchannel phase mismatch                     | 1kHz sinusoidal signal                                                                        |                 | 0.01 |                 | Degrees |

| PSRR             | Power-supply rejection ratio                    | 100mV <sub>PP</sub> , 1kHz sinusoidal signal on AVDD,<br>differential input, 0dB channel gain |                 | 110  |                 | dB      |

| P <sub>out</sub> | Output Power Delivery                           | Receiver/Headphone R <sub>L</sub> =16Ω, THD+N<1% in Differential or Pseudo-differential mode  |                 | 62.5 |                 | mW      |

| DIGITAL I        | 1/0                                             |                                                                                               |                 |      |                 |         |

| V <sub>IL</sub>  | Low-level digital input logic voltage threshold | All digital pins, IOVDD 1.8V operation                                                        | -0.3            |      | 0.35 x<br>IOVDD | V       |

|                  | - Sgio voltago tilicollola                      | All digital pins, IOVDD 3.3V operation                                                        | -0.3            |      | 0.8             | 3       |

| V <sub>IH</sub>  | High-level digital input                        | All digital pins, IOVDD 1.8V operation                                                        | 0.65 x<br>IOVDD |      | IOVDD +<br>0.3  | V       |

| · III            | logic voltage threshold                         | All digital pins, IOVDD 3.3V operation                                                        | 2               |      | IOVDD +<br>0.3  |         |

At  $T_A$  = 25°C, AVDD = 3.3V, IOVDD = 3.3V,  $f_{IN}$  = 1kHz sinusoidal signal,  $f_S$  = 48kHz, 32-bit audio data, BCLK = 256 ×  $f_S$ , TDM target mode, and linear phase interpolation filter, with 1200 $\Omega$ /600 $\Omega$  line-out load in differential/single-ended configuration or 32 $\Omega$  receiver differential load as applicable; measured filter free with an Audio Precision with a 20Hz to 20kHz un-weighted bandwidth, unless otherwise noted

|                    | PARAMETER                                                                                                                                       | TEST CONDITIONS                                                 | MIN             | NOM  | MAX  | UNIT |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|-----------------|------|------|------|

| V                  | Low-level digital output                                                                                                                        | All digital pins, $I_{OL} = -2$ mA, IOVDD 1.8V operation        |                 |      | 0.45 | V    |

| V <sub>OL</sub>    | voltage                                                                                                                                         | All digital pins, I <sub>OL</sub> = -2 mA, IOVDD 3.3V operation |                 |      | 0.4  | V    |

| V <sub>OH</sub>    | High-level digital output voltage                                                                                                               | All digital pins, I <sub>OH</sub> = 2 mA, IOVDD 1.8V operation  | IOVDD –<br>0.45 |      |      | V    |

|                    | voltage                                                                                                                                         | All digital pins, I <sub>OH</sub> = 2 mA, IOVDD 3.3V operation  | 2.4             |      |      |      |

| I <sub>IL</sub>    | Input logic-low leakage for digital inputs                                                                                                      | All digital pins, input = 0V                                    | <b>-</b> 5      | 0.1  | 5    | μΑ   |

| I <sub>IH</sub>    | Input logic-high leakage for digital inputs                                                                                                     | All digital pins, input = IOVDD                                 | <b>–</b> 5      | 0.1  | 5    | μΑ   |

| C <sub>IN</sub>    | Input capacitance for digital inputs                                                                                                            | All digital pins                                                |                 | 5    |      | pF   |

| R <sub>PD</sub>    | Pulldown resistance for digital I/O pins when asserted on                                                                                       |                                                                 |                 | 20   |      | kΩ   |

| TYPICAL            | SUPPLY CURRENT CONS                                                                                                                             | UMPTION                                                         |                 |      |      |      |

| I <sub>AVDD</sub>  |                                                                                                                                                 | All external clocks stopped with MD3 pin grounded, AVDD = 3.3V  |                 | 0.8  |      | mA   |

| I <sub>IOVDD</sub> | Current consumption in sleep mode or low power mode                                                                                             | All external clocks stopped with MD3 pin grounded, IOVDD = 3.3V |                 | 0.6  |      |      |

| I <sub>IOVDD</sub> | power mede                                                                                                                                      | All external clocks stopped with MD3 pin grounded, IOVDD = 1.8V |                 | 0.2  |      | μA   |

| I <sub>AVDD</sub>  | Current consumption                                                                                                                             | AVDD = 3.3V                                                     |                 | 16.4 |      |      |

| I <sub>IOVDD</sub> | with DAC to Headphone 2-channel operation at                                                                                                    | IOVDD = 3.3V                                                    |                 | 0.06 |      | mA   |

| I <sub>IOVDD</sub> | f <sub>S</sub> 16kHz, I <sup>2</sup> S Target<br>Mode, BCLK = 64 × f <sub>S</sub>                                                               | IOVDD = 1.8V                                                    |                 | 0.03 |      |      |

| I <sub>AVDD</sub>  | Current consumption                                                                                                                             | AVDD = 3.3V                                                     |                 | 20   |      |      |

| I <sub>IOVDD</sub> | with DAC to Headphone 2-channel operation at                                                                                                    | IOVDD = 3.3V                                                    |                 | 0.06 |      | mA   |

| I <sub>IOVDD</sub> | f <sub>S</sub> 48kHz, I <sup>2</sup> S Target<br>Mode, BCLK = 64 × f <sub>S</sub>                                                               | IOVDD = 1.8V                                                    |                 | 0.03 |      |      |

| I <sub>AVDD</sub>  | Current consumption with DAC to Line-out 2- channel operation at f <sub>S</sub> 16kHz, I <sup>2</sup> S Target Mode, BCLK = 64 × f <sub>S</sub> | AVDD = 3.3V                                                     |                 | 16.4 |      | mA   |

| I <sub>AVDD</sub>  | Current consumption                                                                                                                             | AVDD = 3.3V                                                     |                 | 17   |      |      |

| I <sub>IOVDD</sub> | with DAC to Line-out 2-<br>channel operation at f <sub>S</sub>                                                                                  | IOVDD = 3.3V                                                    |                 | 0.06 |      | mA   |

| I <sub>IOVDD</sub> | 48kHz, I <sup>2</sup> S Target<br>Mode, BCLK = 64 × f <sub>S</sub>                                                                              | IOVDD = 1.8V                                                    |                 | 0.02 |      |      |

<sup>(1)</sup> Ratio of output level with 1kHz full-scale sine-wave input, to the output level with no generator input signal and input shorted to ground, measured with an A-weighted filter over a 20Hz to 20kHz bandwidth

<sup>(2)</sup> All performance measurements done with 20kHz low-pass filter and, where noted, an A-weighted filter. Failure to use such a filter can result in higher THD+N and lower SNR and dynamic range readings than shown in the Electrical Characteristics. The low-pass filter removes out-of-band noise, which, although not audible, can affect dynamic specification values.

<sup>(3)</sup> For headphone loads  $<32\Omega$ , input signal level should be limited as per the output power delivery specifications.

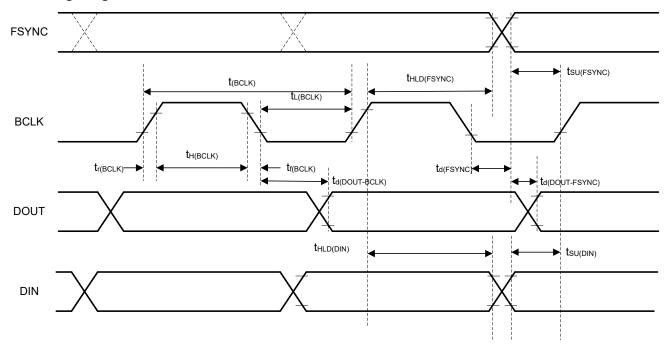

# 5.6 Timing Requirements: TDM, I<sup>2</sup>S or LJ Interface

at  $T_A = 25$ °C, IOVDD = 3.3V or 1.8V and 20pF load on all outputs (unless otherwise noted), see Figure 5-1 for timing diagram where DOUT refers to Daisy Chain Output when applicable

|                         |                                         |                                   | MIN | NOM | MAX | UNIT |

|-------------------------|-----------------------------------------|-----------------------------------|-----|-----|-----|------|

| _                       | DOLK maried                             | IOVDD = 1.8V                      | 80  |     |     |      |

| t <sub>(BCLK)</sub>     | BCLK period                             | IOVDD = 3.3V                      | 40  |     |     | ns   |

|                         | DCI K high pulse duration(1)            | IOVDD = 1.8V                      | 36  |     |     |      |

| t <sub>H(BCLK)</sub>    | BCLK high pulse duration <sup>(1)</sup> | IOVDD = 3.3V                      | 18  |     |     | ns   |

|                         | BCLK low pulse duration <sup>(1)</sup>  | IOVDD = 1.8V                      | 36  |     |     |      |

| t <sub>L(BCLK)</sub>    | BCLK low pulse duration(*)              | IOVDD = 3.3V                      | 18  |     |     | ns   |

| t <sub>SU(FSYNC)</sub>  | FSYNC setup time                        | IOVDD = 1.8V                      | 8   |     |     |      |

|                         | F31NC Setup time                        | IOVDD = 3.3V                      | 8   |     |     | ns   |

| +                       | FSYNC hold time                         | IOVDD = 1.8V                      | 8   |     |     | no   |

| t <sub>HLD(FSYNC)</sub> | FSYNC noid time                         | IOVDD = 3.3V                      | 8   |     |     | ns   |

| +                       | DIN setup time                          | IOVDD = 1.8V                      | 8   |     |     | ns   |

| t <sub>SU(DIN)</sub>    | Div setup time                          | IOVDD = 3.3V                      | 8   |     |     | 115  |

| +                       | DIN hold time                           | IOVDD = 1.8V                      | 16  |     |     | ns   |

| t <sub>HLD(DIN)</sub>   | DIN fiold time                          | IOVDD = 3.3V                      | 8   |     |     | ns   |

|                         | BCLK rise time                          | 10% - 90% rise time, IOVDD = 1.8V |     |     | 10  |      |

| t <sub>r(BCLK)</sub>    | BCLK fise time                          | 10% - 90% rise time, IOVDD = 3.3V |     |     | 10  | ns   |

| +                       | BCLK fall time                          | 90% - 10% fall time, IOVDD = 1.8V |     |     | 10  | 200  |

| t <sub>f(BCLK)</sub>    | DOLK IAII UITIE                         | 90% - 10% fall time, IOVDD = 3.3V |     |     | 10  | ns   |

<sup>(1)</sup> To meet the timing specifications, the BCLK minimum high or low pulse duration must be higher than 25ns, if the DOUT data line is latched on the opposite BCLK edge polarity from the one used by the device to transmit the DOUT data at IOVDD = 3.3V.

## 5.7 Switching Characteristics: TDM, I<sup>2</sup>S or LJ Interface

at  $T_A$  = 25°C, IOVDD = 3.3V or 1.8V and 20pF load on all outputs (unless otherwise noted); see Figure 5-1 for timing diagram where DOUT refers to Daisy Chain Output when applicable

|                             | PARAMETER                         | TEST CONDITIONS                           | MIN    | TYP MA | X  | UNIT    |  |

|-----------------------------|-----------------------------------|-------------------------------------------|--------|--------|----|---------|--|

| •                           | BCLK to DOUT delay                | 50% of BCLK to 50% of DOUT, IOVDD = 1.8V  | 26     |        |    | ns      |  |

| t <sub>d</sub> (DOUT-BCLK)  | BCLN to DOOT delay                | 50% of BCLK to 50% of DOUT, IOVDD = 3.3V  |        |        | 19 | 115     |  |

| <b>t</b>                    | FSYNC to DOUT delay in TDM mode   | 50% of FSYNC to 50% of DOUT, IOVDD = 1.8V |        |        | 26 | ns      |  |

| t <sub>d(DOUT-</sub> FSYNC) | FSYNC to DOUT delay in TDM mode   | 50% of FSYNC to 50% of DOUT, IOVDD = 3.3V |        |        | 19 | 115     |  |

| f                           | BCLK output clock frequency;      | IOVDD = 1.8V                              | 12.288 |        |    | MHz     |  |

| f <sub>(BCLK)</sub>         | controller mode <sup>(1)</sup>    | IOVDD = 3.3V                              | 24.576 |        |    | 1711 12 |  |

| •                           | BCLK to FSYNC delay; controller   | 50% of BCLK to 50% of FSYNC, IOVDD = 1.8V |        |        | 26 | ns      |  |

| t <sub>d(FSYNC)</sub>       | mode                              | 50% of BCLK to 50% of FSYNC, IOVDD = 3.3V |        |        | 19 |         |  |

| t                           | BCLK high pulse duration;         | IOVDD = 1.8V                              | 36     |        |    | ns      |  |

| t <sub>H(BCLK)</sub>        | controller mode                   | IOVDD = 3.3V                              | 18     |        |    | 115     |  |

|                             | BCLK low pulse duration;          | IOVDD = 1.8V                              | 36     |        |    |         |  |

| t <sub>L(BCLK)</sub>        | controller mode                   | IOVDD = 3.3V                              | 18     |        |    | ns      |  |

|                             | BCLK rise time; controller mode   | 10% - 90% rise time, IOVDD = 1.8V         | 10     |        | 10 | ns      |  |

| t <sub>r(BCLK)</sub>        | BOLK fise time, controller filode | 10% - 90% rise time, IOVDD = 3.3V         |        | 10     |    |         |  |

資料に関するフィードバック(ご意見やお問い合わせ)を送信

9

at  $T_A = 25^{\circ}$ C, IOVDD = 3.3V or 1.8V and 20pF load on all outputs (unless otherwise noted); see Figure 5-1 for timing diagram where DOUT refers to Daisy Chain Output when applicable

|                      | PARAMETER                       | TEST CONDITIONS                   | MIN | TYP | MAX | UNIT |

|----------------------|---------------------------------|-----------------------------------|-----|-----|-----|------|

|                      | BCLK fall time; controller mode | 90% - 10% fall time, IOVDD = 1.8V |     |     | 10  | no   |

| <sup>T</sup> f(BCLK) | BOLK IAII UITIE, CONTIONEI MODE | 90% - 10% fall time, IOVDD = 3.3V |     |     | 10  | ns   |

(1) To meet the timing specifications, the BCLK output clock frequency must be lower than 18.5MHz, if the DOUT data line is latched on the opposite BCLK edge polarity from the one used by the device to transmit DOUT data at IOVDD = 3.3V.

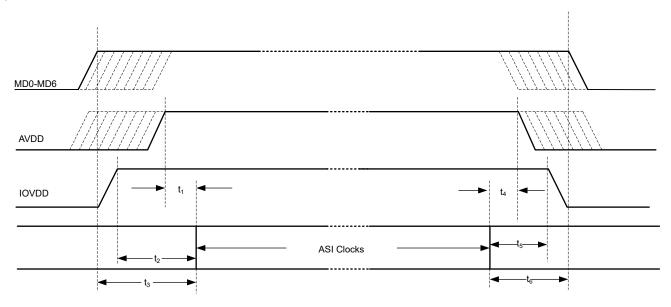

## 5.8 Timing Diagrams

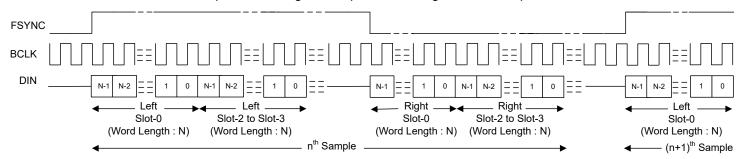

図 5-1. TDM, I<sup>2</sup>S, and LJ Interface Timing Diagram

資料に関するフィードバック (ご意見やお問い合わせ) を送信

Copyright © 2024 Texas Instruments Incorporated

English Data Sheet: SLASF32

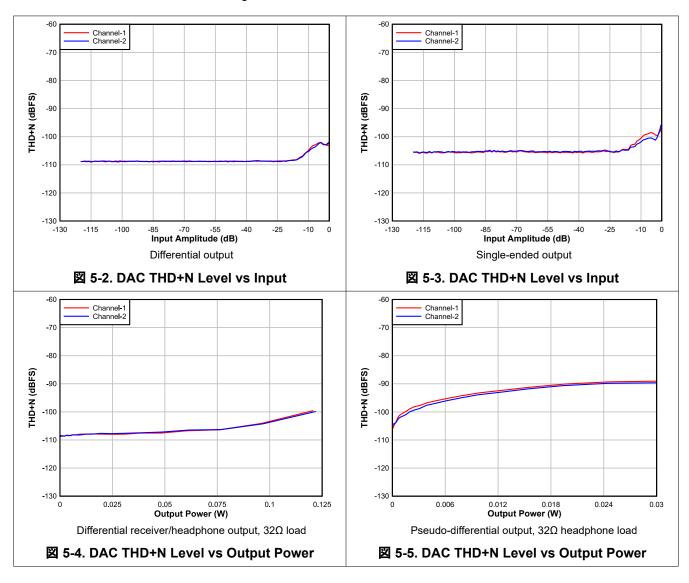

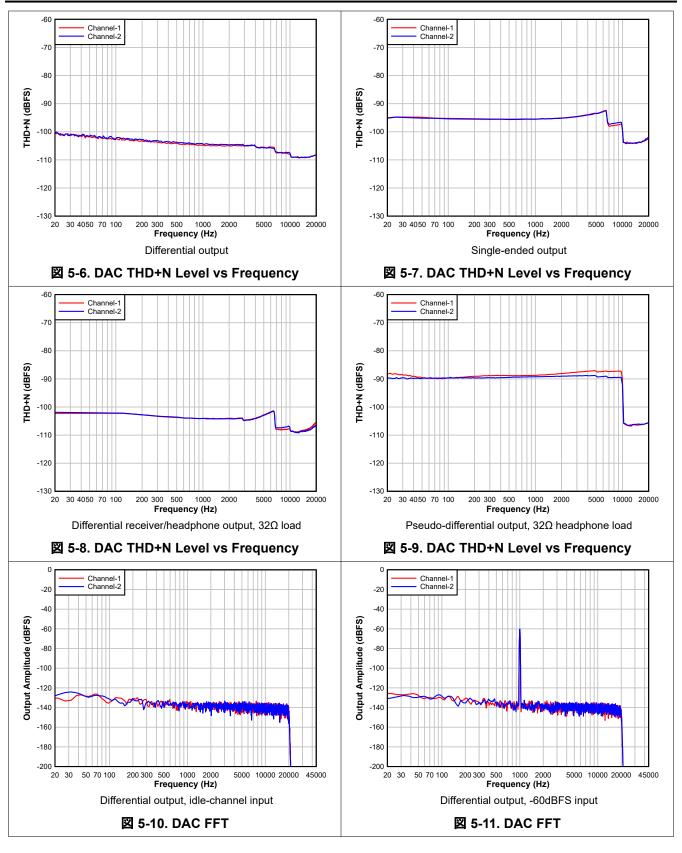

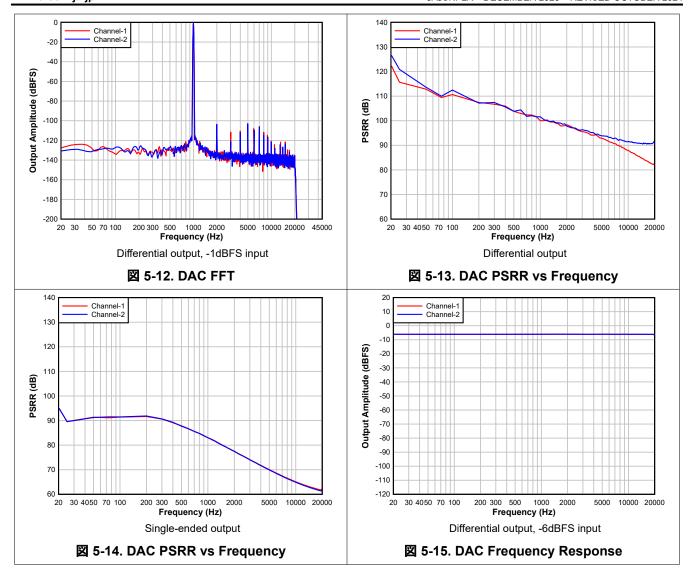

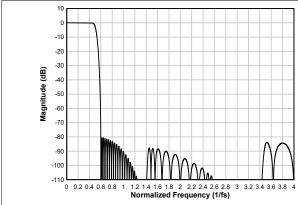

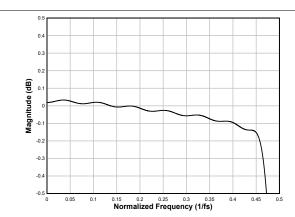

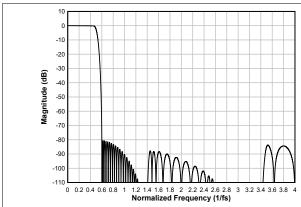

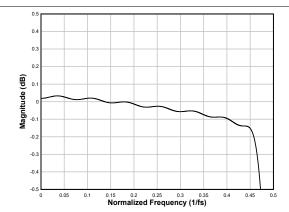

## **5.9 Typical Characteristics**

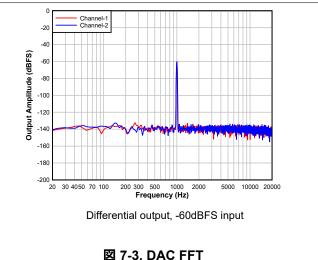

At  $T_A$  = 25°C, AVDD = 3.3V, IOVDD = 3.3V,  $f_{IN}$  = 1kHz sinusoidal signal,  $f_S$  = 48kHz, 32-bit audio data, BCLK = 256× $f_S$ , TDM target mode, and linear phase interpolation filter, with 1200 $\Omega$ /600 $\Omega$  line-out load in differential/single-ended configuration or 32 $\Omega$  receiver differential load as applicable; measured filter free with an Audio Precision with a 20Hz to 20kHz un-weighted bandwidth, unless otherwise noted

13

Product Folder Links: TAD5142

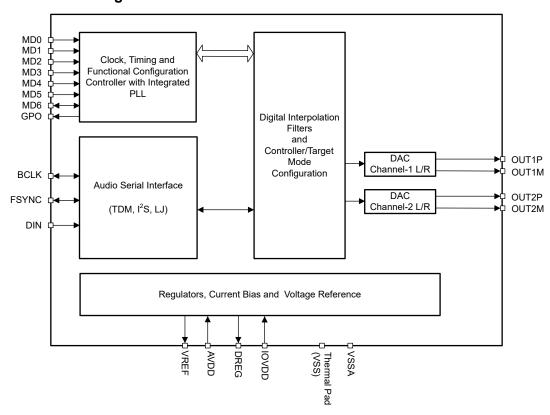

## 6 Detailed Description

#### 6.1 Overview

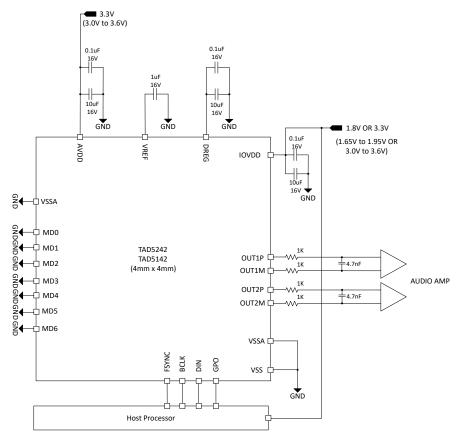

The TAD5142 is a high-performance, low-power, stereo audio digital-to-analog converter (DAC). This device is intended for broad market applications such as ruggedized communication equipment, IP network camera, professional audio and multimedia applications. This device integrates a host of features that reduce cost, board space, and power consumption in space-constrained system designs. Package, performance, and compatible configuration across an extended family makes this device well suited for scalable system designs.

The TAD5142 consists of the following features:

- 2-channel, multi-bit, high-performance delta-sigma (ΔΣ) DACs

- Pin or Hardware controlled device configurations

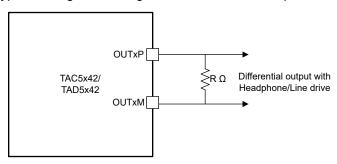

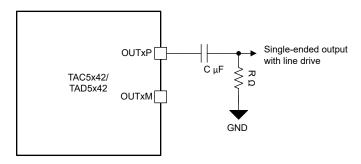

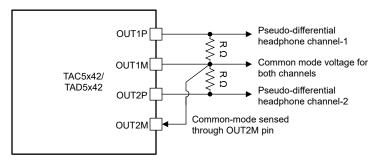

- · Configurable single-ended, differential or pseudo-differential audio outputs

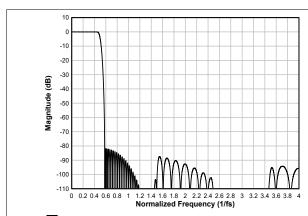

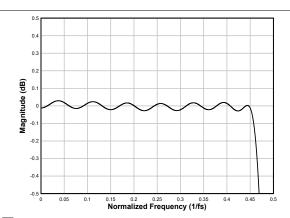

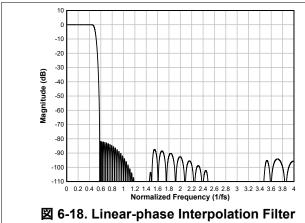

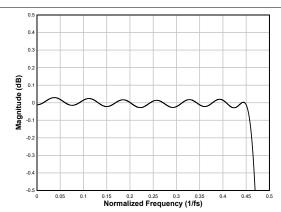

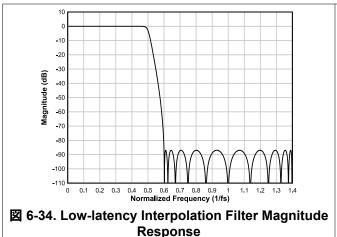

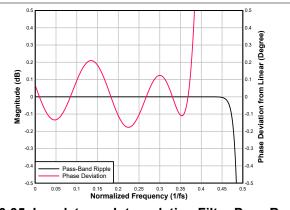

- Linear-phase or Low-latency digital interpolation filters

- · Integrated low-jitter, phase-locked loop (PLL) supporting a wide range of system clocks

- · Integrated digital and analog voltage regulators to support single-supply operation

## 6.2 Functional Block Diagram

図 6-1. Functional Block Diagram

#### 6.3 Feature Description

#### 6.3.1 Hardware Control

The device supports simple hardware-pin-controlled options to select a specific mode of operation and audio interface for a given system as summarized in 表 6-1. The MD1 to MD6 pins are connected to either logic low (VSS) or logic high (IOVDD), and the MD0 pin can be connected to AVDD or VSS through different pull-up or pull-down resistors.

世) を送信 Copyright © 2024 Texas Instruments Incorporated Product Folder Links: *TAD5142*

表 6-1. Pin Selectable Configurations Summary

|     | & 0-1.1 in delectable domingurations duminary                                                  |                                                      |  |  |  |  |  |  |  |  |

|-----|------------------------------------------------------------------------------------------------|------------------------------------------------------|--|--|--|--|--|--|--|--|

| PIN | TARGET MODE CONTROLLER MODE                                                                    |                                                      |  |  |  |  |  |  |  |  |

| MD0 | Multi-level analog input for controller/target mode and I <sup>2</sup> S/TDM/LJ mode selection |                                                      |  |  |  |  |  |  |  |  |

| MD1 | AVDD supply, word length, and interpolation filter                                             | Frame rate and BCLK frequency selection              |  |  |  |  |  |  |  |  |

| MD2 | type selection                                                                                 |                                                      |  |  |  |  |  |  |  |  |

| MD3 | Ground                                                                                         | Controller clock input                               |  |  |  |  |  |  |  |  |

| MD4 | DAC output configuration selection (Differential Lir                                           | ne-out/ Differential Receiver/Headphone/Single-ended |  |  |  |  |  |  |  |  |

| MD5 | Line-out/ Pseudo-differential Headphone)                                                       |                                                      |  |  |  |  |  |  |  |  |

| MD6 | TDM mode: Daisy chain output or I <sup>2</sup> S/LJ mode: M                                    | ono/Stereo selection                                 |  |  |  |  |  |  |  |  |

#### 6.3.2 Audio Serial Interfaces

Digital audio data flows between the host processor and the TAD5142 on the digital audio serial interface (ASI), or audio bus. This bus can be operated in target or controller mode through pin control. The ASI supports TDM, I<sup>2</sup>S and Left-Justified bus protocols. The data is in MSB-first, two's-complement pulse code modulation (PCM) format, with pin-selectable word-length configuration.

The device supports an audio bus controller or target mode of operation using the hardware pin MD0. In target mode, FSYNC and BCLK work as input pins whereas in controller mode, FSYNC and BCLK work as output pins generated by the device. 表 6-2 shows the controller and target mode selection using the MD0 pin.

表 6-2. Controller and Target Mode Selection

| MD0                            | CONTROLLER AND TARGET SELECTION  |

|--------------------------------|----------------------------------|

| Short to Ground                | Target I <sup>2</sup> S Mode     |

| Short to Ground with 4.7K Ohms | Target TDM Mode                  |

| Short to AVDD                  | Controller I <sup>2</sup> S Mode |

| Short to AVDD with 4.7K Ohms   | Controller TDM Mode              |

| Short to AVDD with 22K Ohms    | Target LJ Mode                   |

The word length for audio serial interface (ASI) in TAD5142 can be selected through MD1 and MD2 Pins in target mode of operation. The TAD5142 also supports 1.8V AVDD operation in target mode with 32-bit word length. 表 6-3 shows the configuration table for setting the word length, AVDD supply voltage and interpolation filter type applicable in Target Mode. In controller mode, AVDD supply mode is 3.3V, word length of 32-bits is supported, interpolation filter is configured in the linear-phase and the MD1 and MD2 Pins control the system clock configuration described in 表 6-8.

表 6-3. Word Length, Supply Mode, and Interpolation Filter Selection

| MD2  |      | WORD LENGTH, SUPPLY MODE, AND INTERPOLATION FILTER SELECTION (Valid for Target Mode only) |

|------|------|-------------------------------------------------------------------------------------------|

| Low  | Low  | AVDD=3.3V, Word Length=32, Linear-phase Filter                                            |

| Low  | High | AVDD=1.8V, Word Length=32, Linear-phase Filter                                            |

| High | Low  | AVDD=3.3V, Word Length=24, Linear-phase Filter                                            |

| High | High | AVDD=3.3V, Word Length=32, Low-latency phase Filter                                       |

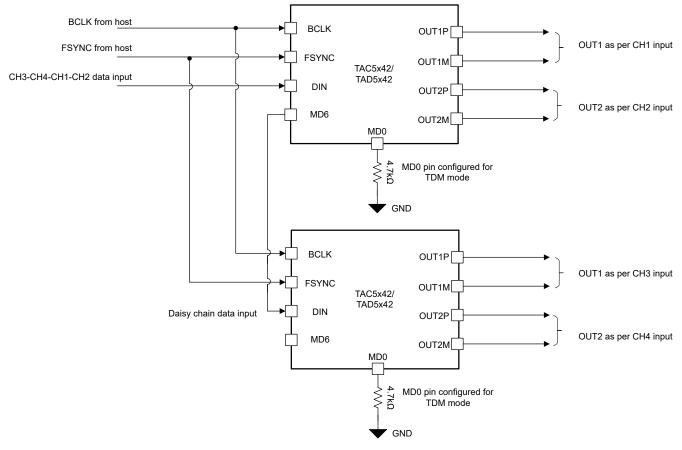

The TAD5142 also offers daisy chain option for TDM mode of operation. This option is auto enabled whenever device is selected to be in TDM Mode with MD0. MD6 Pin acts as a Daisy Chain output in this mode. In this case, for a TDM with N slots, the device plays the audio present on the last 2 slots, and the remaining slots are shifted to the right and sent on the MD6 pin, as shown in the block diagram in the  $\boxtimes$  6-2.

Product Folder Links: TAD5142

Copyright © 2024 Texas Instruments Incorporated

資料に関するフィードバック(ご意見やお問い合わせ)を送信

15

図 6-2. Daisy Chain in TDM Mode Block Diagram

## 6.3.2.1 Time Division Multiplexed Audio (TDM) Interface

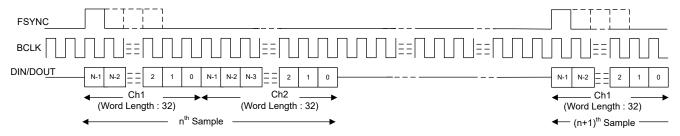

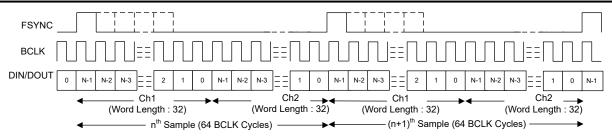

In TDM mode, also known as DSP mode, the rising edge of FSYNC starts the data transfer with the slot 0 data first. Immediately after the slot 0 data transmission, the remaining slot data are transmitted in order. FSYNC and each data bit is transmitted on the rising edge of BCLK and received on the falling edge of BCLK.  $\boxtimes$  6-3 and  $\boxtimes$  6-4 show the protocol timing for TDM operation with various configurations. DOUT refers to the Daisy Chain Output.

図 6-3. TDM Mode Protocol Timing (MD0 shorted to ground with 4.7K Ohms) in Target Mode

図 6-4. TDM Mode Protocol Timing (MD0 shorted to AVDD with 4.7K Ohms) in Controller Mode

For proper operation of the audio bus in TDM mode, the number of bit clocks per frame must be greater than or equal to the number of active input and output channels times the configured word length of the input and output channel data. The DOUT pin is in a Hi-Z state for the extra unused bit clock cycles. The device supports FSYNC as a pulse with a 1-cycle-wide bit clock, but also supports multiples as well.

## 6.3.2.2 Inter IC Sound (I2S) Interface

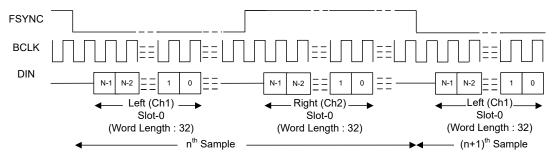

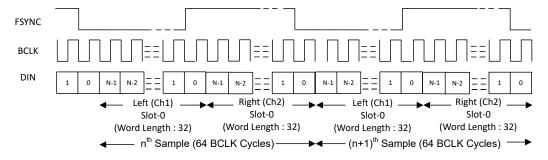

The standard I<sup>2</sup>S protocol is defined for only two channels: left and right. In I<sup>2</sup>S mode, the MSB of the left slot 0 is received on the rising edge of BCLK in the second cycle after the *falling* edge of FSYNC. The MSB of the right slot 0 is received on the rising edge of BCLK in the second cycle after the *rising* edge of FSYNC. Each subsequent data bit is received on the rising edge of BCLK. In controller mode, FSYNC is transmitted on the falling edge of BCLK.  $\boxtimes$  6-5 and  $\boxtimes$  6-6 show the protocol timing for I<sup>2</sup>S operation in target and controller mode of operation.

図 6-5. I<sup>2</sup>S Mode Protocol Timing (MD0 shorted to ground) in Target Mode

図 6-6. I<sup>2</sup>S Protocol Timing (MD0 shorted to AVDD) in Controller Mode

For proper operation of the audio bus in I<sup>2</sup>S mode, the number of bit clocks per frame must be greater than or equal to the number of active input channels (including left and right slots) times the configured word length of the input channel data.

## 6.3.2.3 Left-Justified (LJ) Interface

The standard LJ protocol is defined for only two channels: left and right. In LJ mode, the MSB of the left slot 0 is received in the same BCLK cycle after the *rising* edge of FSYNC. Each subsequent data bit is received on the

Copyright © 2024 Texas Instruments Incorporated

資料に関するフィードバック(ご意見やお問い合わせ)を送信

17

rising edge of BCLK. The MSB of the right slot 0 is received in the same BCLK cycle after the *falling* edge of FSYNC.  $\boxtimes$  6-7 illustrates the protocol timing for LJ operation in target mode of coperation.

図 6-7. LJ Mode Standard Protocol Timing (MD0 shorted to AVDD with 22K Ohms) in Target Mode

For proper operation of the audio bus in LJ mode, the number of bit clocks per frame must be greater than or equal to the number of active input channels (including left and right slots) times the configured word length of the input channel data.

## 6.3.3 Phase-Locked Loop (PLL) and Clock Generation

The device uses an integrated, low-jitter, phase-locked loop (PLL) to generate internal clocks required for the DAC modulators and digital filter engine, as well as other control blocks.

In target mode of operation, the device supports the various output data sample rates (of the FSYNC signal frequency) and the BCLK to FSYNC ratio to configure all clock dividers, including the PLL configuration, internally without host programming.  $\frac{1}{2}$  6-4 to  $\frac{1}{2}$  6-7 list the supported FSYNC and BCLK frequencies depending on IOVDD Supply.

表 6-4. Supported FSYNC (Multiples or Submultiples of 48 kHz) and BCLK Frequencies (IOVDD - 3.3V Operation)

|                        |                  |                   | -                 | uti 011,          |                   |                   |                    |  |

|------------------------|------------------|-------------------|-------------------|-------------------|-------------------|-------------------|--------------------|--|

|                        |                  | BCLK (MHz)        |                   |                   |                   |                   |                    |  |

| BCLK TO<br>FSYNC RATIO | FSYNC<br>(8 kHz) | FSYNC<br>(16 kHz) | FSYNC<br>(24 kHz) | FSYNC<br>(32 kHz) | FSYNC<br>(48 kHz) | FSYNC<br>(96 kHz) | FSYNC<br>(192 kHz) |  |

| 16                     | Reserved         | 0.256             | 0.384             | 0.512             | 0.768             | 1.536             | 3.072              |  |

| 24                     | Reserved         | 0.384             | 0.576             | 0.768             | 1.152             | 2.304             | 4.608              |  |

| 32                     | 0.256            | 0.512             | 0.768             | 1.024             | 1.536             | 3.072             | 6.144              |  |

| 48                     | 0.384            | 0.768             | 1.152             | 1.536             | 2.304             | 4.608             | 9.216              |  |

| 64                     | 0.512            | 1.024             | 1.536             | 2.048             | 3.072             | 6.144             | 12.288             |  |

| 96                     | 0.768            | 1.536             | 2.304             | 3.072             | 4.608             | 9.216             | 18.432             |  |

| 128                    | 1.024            | 2.048             | 3.072             | 4.096             | 6.144             | 12.288            | 24.576             |  |

| 192                    | 1.536            | 3.072             | 4.608             | 6.144             | 9.216             | 18.432            | Reserved           |  |

| 256                    | 2.048            | 4.096             | 6.144             | 8.192             | 12.288            | 24.576            | Reserved           |  |

| 384                    | 3.072            | 6.144             | 9.216             | 12.288            | 18.432            | Reserved          | Reserved           |  |

| 512                    | 4.096            | 8.192             | 12.288            | 16.384            | 24.576            | Reserved          | Reserved           |  |

表 6-5. Supported FSYNC (Multiples or Submultiples of 44.1 kHz) and BCLK Frequencies (IOVDD - 3.3V Operation)

|                        |                     |                     | - P                  | utioii,             |                     |                     |                      |  |  |

|------------------------|---------------------|---------------------|----------------------|---------------------|---------------------|---------------------|----------------------|--|--|

|                        |                     | BCLK (MHz)          |                      |                     |                     |                     |                      |  |  |

| BCLK TO<br>FSYNC RATIO | FSYNC<br>(7.35 kHz) | FSYNC<br>(14.7 kHz) | FSYNC<br>(22.05 kHz) | FSYNC<br>(29.4 kHz) | FSYNC<br>(44.1 kHz) | FSYNC<br>(88.2 kHz) | FSYNC<br>(176.4 kHz) |  |  |

| 16                     | Reserved            | Reserved            | 0.3528               | 0.4704              | 0.7056              | 1.4112              | 2.8224               |  |  |

| 24                     | Reserved            | 0.3528              | 0.5292               | 0.7056              | 1.0584              | 2.1168              | 4.2336               |  |  |

| 32                     | Reserved            | 0.4704              | 0.7056               | 0.9408              | 1.4112              | 2.8224              | 5.6448               |  |  |

| 48                     | 0.3528              | 0.7056              | 1.0584               | 1.4112              | 2.1168              | 4.2336              | 8.4672               |  |  |

| 64                     | 0.4704              | 0.9408              | 1.4112               | 1.8816              | 2.8224              | 5.6448              | 11.2896              |  |  |

| 96                     | 0.7056              | 1.4112              | 2.1168               | 2.8224              | 4.2336              | 8.4672              | 16.9344              |  |  |

| 128                    | 0.9408              | 1.8816              | 2.8224               | 3.7632              | 5.6448              | 11.2896             | 22.5792              |  |  |

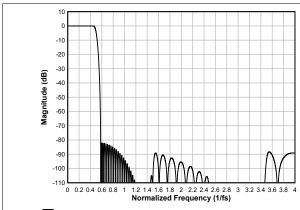

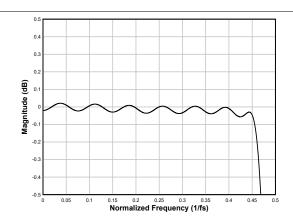

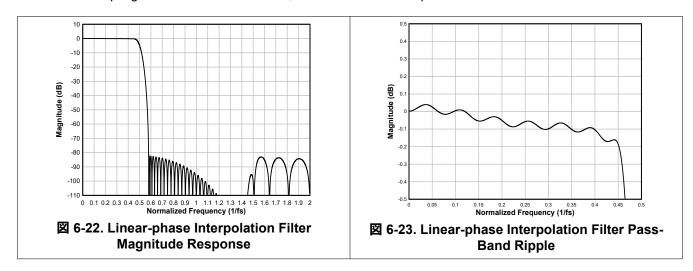

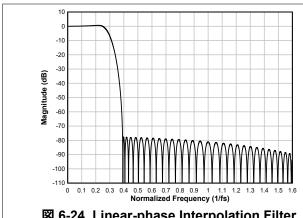

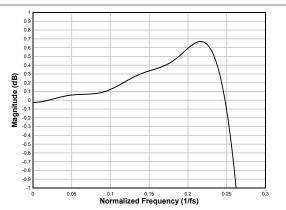

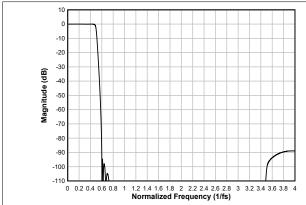

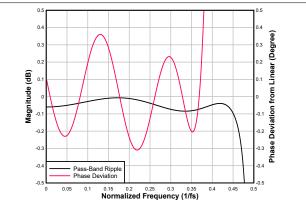

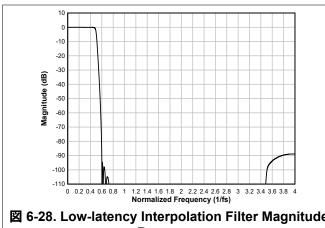

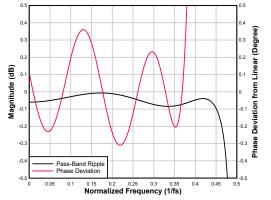

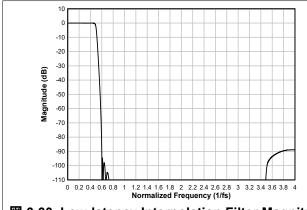

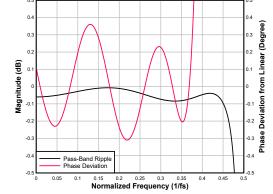

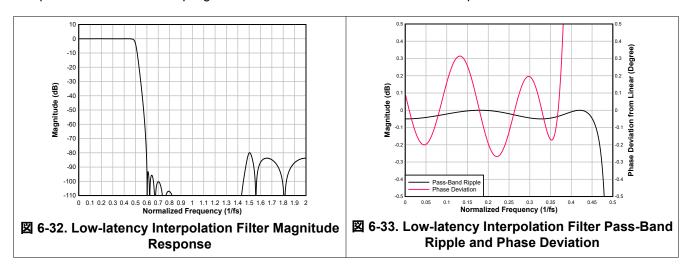

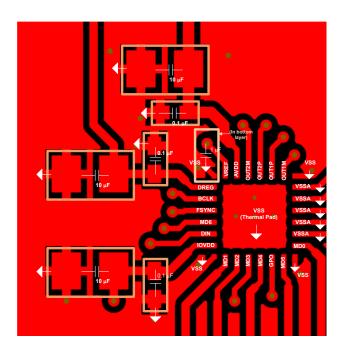

| 192                    | 1.4112              | 2.8224              | 4.2336               | 5.6448              | 8.4672              | 16.9344             | Reserved             |  |  |