**TLC6984**

JAJSNK8D - NOVEMBER 2021 - REVISED JULY 2022

# TLC6984 48 電流源、64 スキャン、共通力ソード・マトリクス LED ディスプ レイ・ドライバ

# 1 特長

Texas

INSTRUMENTS

- 独立した V<sub>CC</sub> および V<sub>R/G/B</sub> 電源

- V<sub>CC</sub> 電圧範囲:2.5V~5.5V

- V<sub>R/G/B</sub>の電圧範囲:2.5V~5.5V

- 48 個の 0.2mA~20mA 電流源チャネル

- チャネル間精度:±0.5% (標準値)、±2% (最大値)、 デバイス間精度:±0.5% (標準値)、±2% (最大値)

- 低いニー電圧:0.26V (最大値) (I<sub>OUT</sub> = 5mA 時)

- 3ビット(8ステップ)のグローバル輝度制御

- 8ビット (256 ステップ)の色輝度制御

- 最大 16 ビット (65536 ステップ)の PWM グレイス ケール制御

- R<sub>DS(ON)</sub> = 190mΩの 16 個のスキャン・ライン・スイッ チ

- 非常に低い消費電力

- 独立した最小 2.5V の V<sub>CC</sub>

- 最小 3.6mA の小さい I<sub>CC</sub> (GCLK = 50MHz)

- Icc を最小 0.9mA に低減したインテリジェント省電 カモード

- 1~64 のマルチプレクシングをサポートする内蔵 SRAM

- 1 つのデバイス:16 マルチプレクシングにより 48 × 16 の LED または 16 × 16 の RGB ピクセルをサ ポート

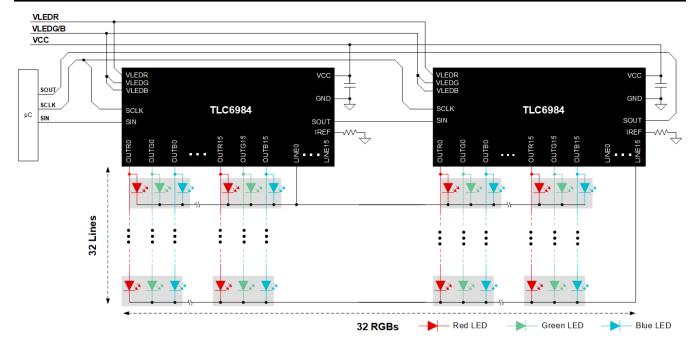

- 2 つのデバイスのスタック接続:32 マルチプレクシ ングにより 96 × 32 の LED または 32 × 32 の RGB ピクセルをサポート

- 3 つのデバイスのスタック接続:48 マルチプレクシ ングにより 144 × 48 の LED または 48 × 48 の RGB ピクセルをサポート

- 4 つのデバイスのスタック接続:64 マルチプレクシ ングにより 192 × 64 の LED または 64 × 64 の RGB ピクセルをサポート

- 高速および低 EMI の連続クロック・シリーズ・インター フェイス (CCSI)

- わずか3本の信号線:SCLK/SIN/SOUT

- デュアル・エッジ伝送機能を備えた外部 25MHz (最大值) SCLK (内部 50MHz)

- 高い GCLK 周波数をサポートするための内部周波 数逓倍器

- 最適化されたディスプレイ性能

- プログラム可能なスキャン・ライン・シーケンス

- 上側と下側のゴーストの除去

- 低グレイスケール強調

- LED の開放、短絡、弱短絡の検出と除去

# 2 アプリケーション

- 狭ピクセル・ピッチ (NPP) LED ディスプレイ

- 小型および超小型 LED 製品

# 3 概要

ピクセル・ピッチが狭い LED ディスプレイや小型およびマ イクロ LED 製品などでピクセル密度がより高くなり、これら の製品における課題について、LEDドライバの緊急な対 応が求められています。この課題としては、厳しい基板面 積制限に対応する超高集積化、システム・レベルでの消 費電力最小化を可能にする超低消費電力、高いデータ・ リフレッシュ・レートと EMI の影響低減を実現する新しいイ ンターフェイス、高いディスプレイ品質のニーズの増大に 対応する優れたディスプレイ性能などが挙げられます。

| 製品情報    |                      |                 |  |  |  |

|---------|----------------------|-----------------|--|--|--|

| 部品番号    | パッケージ <sup>(1)</sup> | 本体サイズ (公称)      |  |  |  |

| TLC6984 | VQFN (76)            | 9.00mm × 9.00mm |  |  |  |

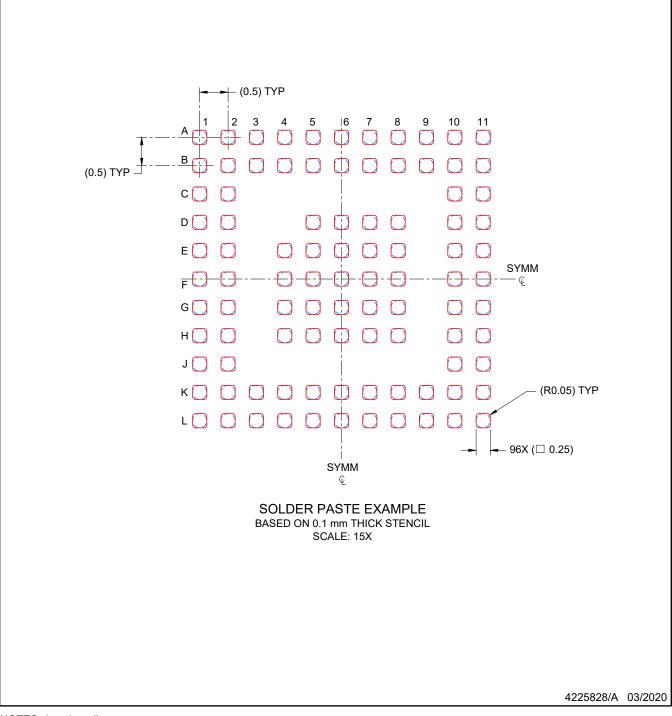

|         | BGA (96)             | 6.00mm × 6.00mm |  |  |  |

利用可能なパッケージについては、このデータシートの末尾にあ (1) る注文情報を参照してください。

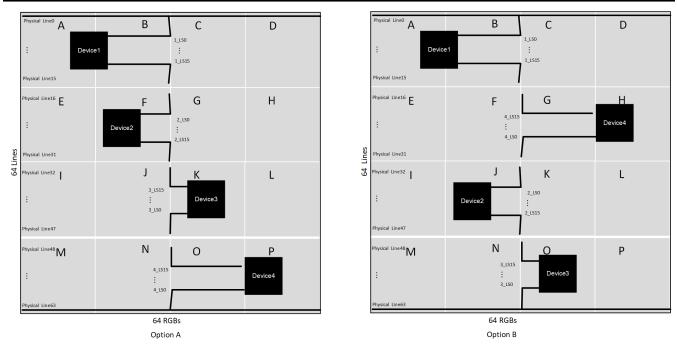

4 デバイス・スタック接続の TLC6984

英語版のTI製品についての情報を翻訳したこの資料は、製品の概要を確認する目的で便宜的に提供しているものです。該当する正式な英語版の最新情報は、 🐼 www.ti.com で閲覧でき、その内容が常に優先されます。 TI では翻訳の正確性および妥当性につきましては一切保証いたしません。 実際の設計などの前には、必ず 最新版の英語版をご参照くださいますようお願いいたします。

# **Table of Contents**

| 1 | 特長                                   | 1  |

|---|--------------------------------------|----|

|   | アプリケーション                             |    |

| 3 | 概要                                   | 1  |

|   | Revision History                     |    |

| 5 | 概要 (続き)                              | .3 |

| 6 | Pin Configuration and Functions      | 4  |

| 7 | Specifications                       | 6  |

|   | 7.1 Absolute Maximum Ratings         |    |

|   | 7.2 ESD Ratings                      | 6  |

|   | 7.3 Recommended Operating Conditions | 6  |

|   | 7.4 Thermal Information              | 6  |

|   | 7.5 Electrical Characteristics       |    |

|   | 7.6 Timing Requirements1             | 0  |

|   | 7.7 Switching Characteristics1       |    |

|   | 7.8 Typical Characteristics1         |    |

| 8 | Detailed Description1                |    |

|   | 8.1 Overview1                        |    |

|   | 8.2 Functional Block Diagram1        | 4  |

|   | 8.3 Feature Description1             | 4  |

|   | 8.4 Device Functional Modes2         | 26 |

|    | 8.5 Continuous Clock Series Interface                 | .27 |

|----|-------------------------------------------------------|-----|

|    | 8.6 PWM Grayscale Control                             | 33  |

|    | 8.7 Register Maps                                     |     |

| 9  | Application and Implementation                        |     |

|    | 9.1 Application Information                           |     |

|    | 9.2 Typical Application                               |     |

| 1( | 0 Power Supply Recommendations                        |     |

|    | 1 Layout                                              |     |

|    | 11.1 Layout Guidelines                                | 61  |

|    | 11.2 Layout Example                                   |     |

| 12 | 2 Device and Documentation Support                    |     |

|    | 12.1 Documentation Support                            |     |

|    | 12.2 Receiving Notification of Documentation Updates. |     |

|    | 12.3 サポート・リソース                                        |     |

|    | 12.4 Trademarks                                       |     |

|    | 12.5 Electrostatic Discharge Caution                  |     |

|    | 12.6 Glossary                                         |     |

| 1: | 3 Mechanical, Packaging, and Orderable                |     |

|    | Information                                           | 66  |

|    |                                                       | ~~  |

# **4 Revision History**

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

|                                                                       | 1    |

|-----------------------------------------------------------------------|------|

| Changed the description of FREQ_MOD                                   |      |

| Changed the name of register field                                    |      |

| Changes from Revision B (March 2022) to Revision C (March 2022)       | Page |

| • 「 <i>特長</i> 」および「 <i>概要 (続き</i> )」セクションの GCLK の説明を更新                | 1    |

| Changes from Revision A (December 2021) to Revision B (March 2022)    | Page |

| <ul> <li>データシートのステータスを「事前情報」から「量産データ」に変更</li> </ul>                   | 1    |

| Changes from Revision * (November 2021) to Revision A (December 2021) | Page |

| - データシートの最初の公開リリース                                                    | 1    |

# 5 概要 (続き)

TLC6984 は、48 個の定電流源と16 個のスキャン FET を備えた高集積の共通カソード・マトリクス LED ディスプレイ・ド ライバです。TLC6983 のように 16 × 16 および 32 × 32 の RGB LED ピクセルを駆動するだけでなく、3 つの TLC6984 をスタック接続すると 48 × 48 の RGB LED ピクセルを駆動でき、4 つの TLC6984 をスタック接続すると 64 × 64 の RGB LED ピクセルを駆動できます。低消費電力を実現するため、共通カソード構造によって、赤、緑、青の LED に独立 した電源をサポートしています。さらに、非常に低い動作電圧範囲 (最小 2.5V の Vcc)と非常に低い動作電流 (最小 3.6mA) により、TLC6984 の動作電力は大幅に低減されています。

TLC6984 は、多数のデバイスによるデイジーチェーン接続と高いリフレッシュ・レートをサポートすると同時に、電磁干渉 (EMI)を最小化するため、高速デュアル・エッジ伝送インターフェイスを実装しています。このデバイスは、最高 25MHz の SCLK (外部)および 40MHz~160MHz の GCLK (内部、標準値)を、各種の GCLK 乗算器モードおよび周波数で サポートします。また、本デバイスは拡張回路とインテリジェント・アルゴリズムを内蔵しており、狭ピクセル・ピッチ (NPP) LED ディスプレイ・アプリケーションと小型および超小型 LED 製品における表示に関する各種課題を解決しています。そ の課題としては、最初のスキャン・ラインの輝度低下、上側および下側ゴースト、低グレイスケールでの不均一性、カップリ ング、LED の開放または短絡に起因するキャタピラーなどがあります。TLC6984 は、このようなアプリケーションでの理想 的な選択肢です。

TLC6984 は LED の開放、弱短絡、短絡検出および動作中の取り外しにも対応しており、接続されているデジタル・プロ セッサにこの情報を報告することもできます。

# 6 Pin Configuration and Functions

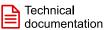

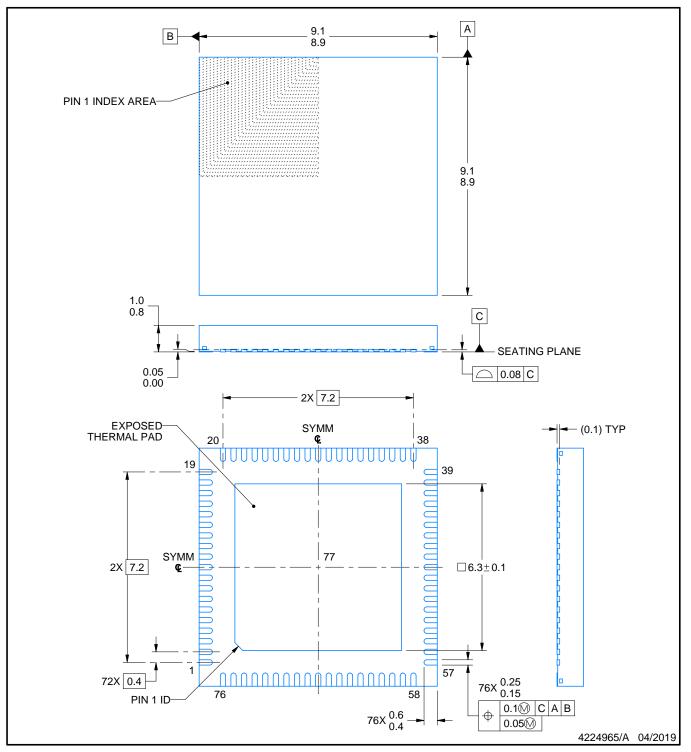

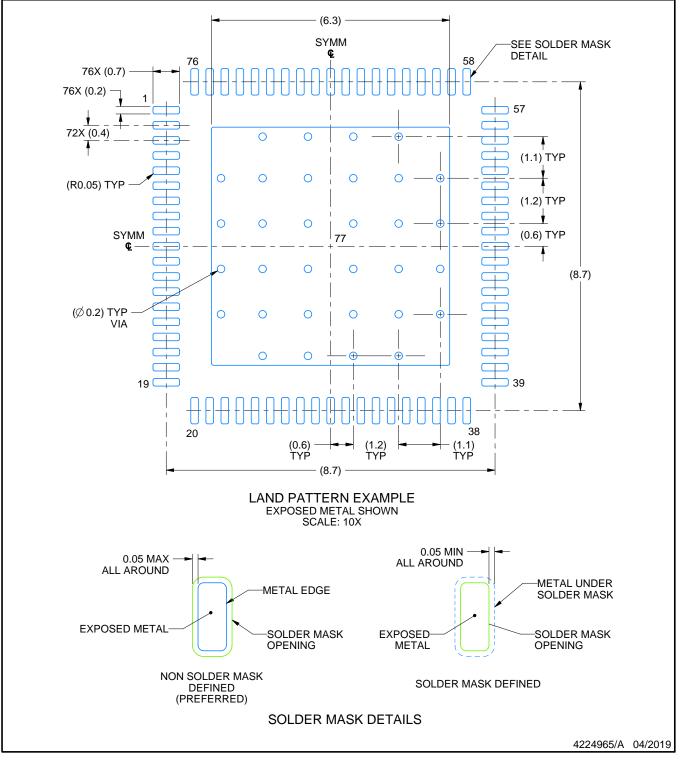

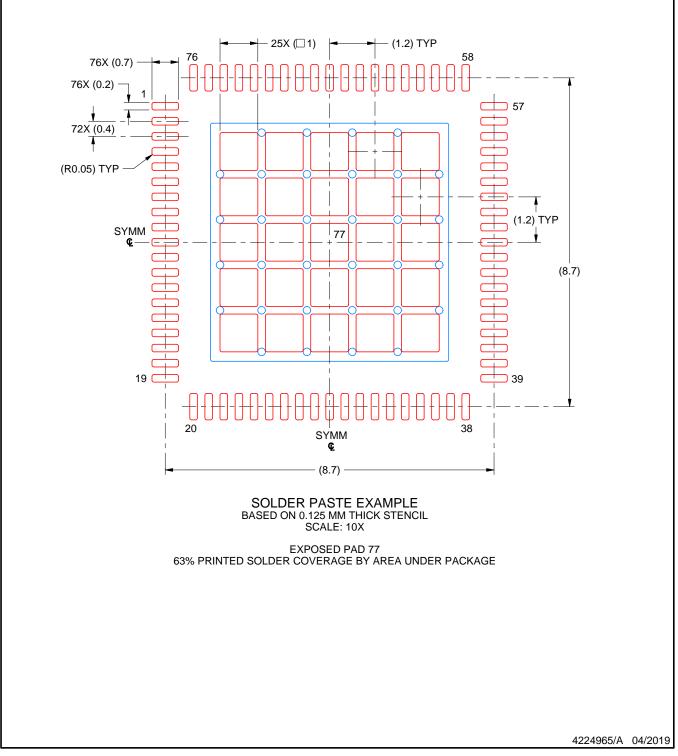

図 6-1. TLC6984 RRF Package 76-Pin VQFN With Exposed Thermal Pad Top View

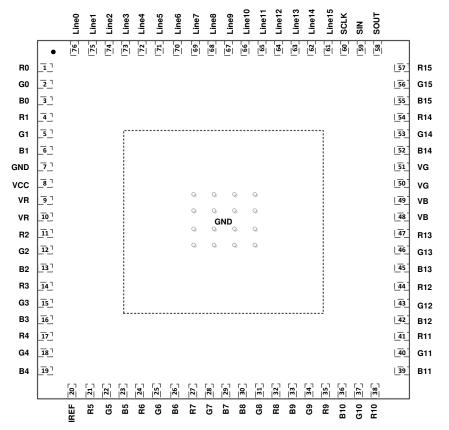

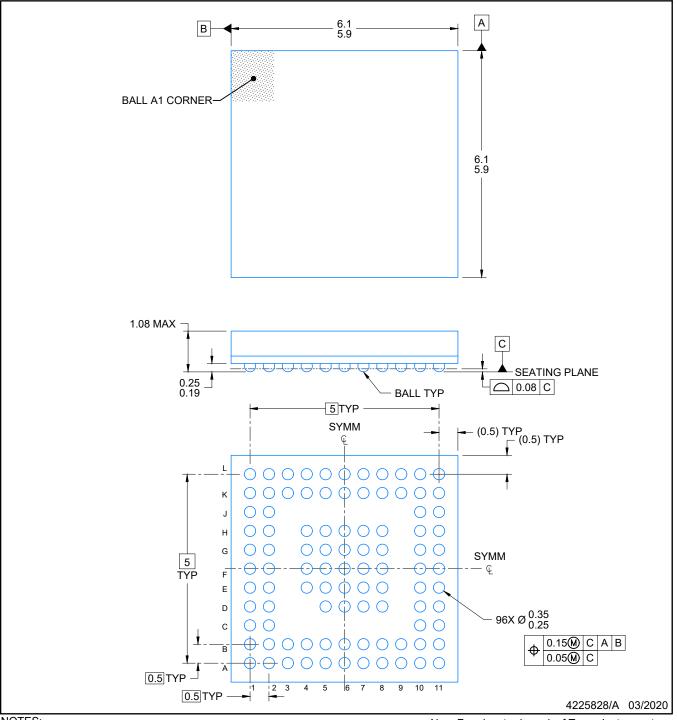

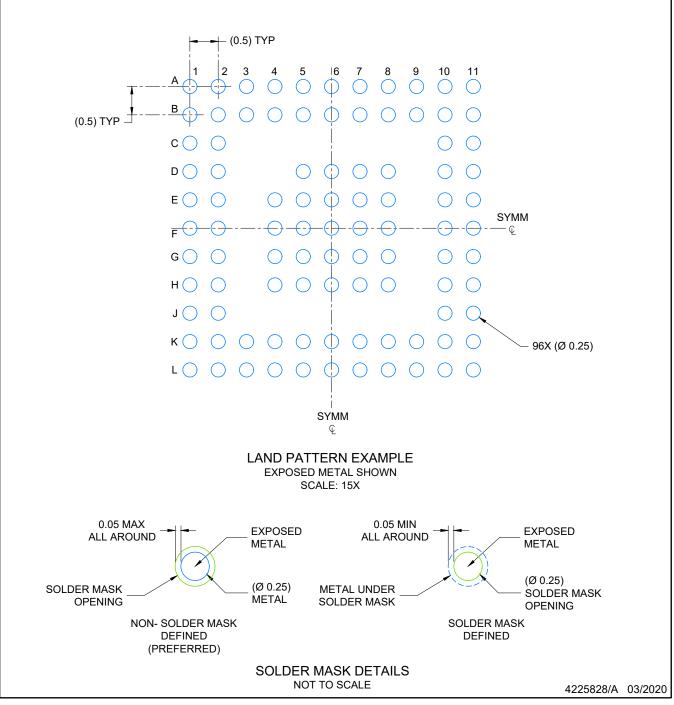

図 6-2. TLC6984 ZXL Package 96-Pin BGA Top View

# 表 6-1. Pin Functions

| PIN              |                                                                               | I/O                                                                                               | DESCRIPTION |                                                                                                                                                                                                                                                                                                               |  |

|------------------|-------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME             | RRF NO.                                                                       | ZXL NO.                                                                                           |             | DESCRIPTION                                                                                                                                                                                                                                                                                                   |  |

| IREF             | 20                                                                            | J1                                                                                                | I           | Pin for setting the maximum constant-current value. Connecting an external resistor between IREF and GND sets the maximum current for each constant-current output channel. When this pin is connected directly to GND, all outputs are forced off. The external resistor must be placed close to the device. |  |

| VCC              | 8                                                                             | F1                                                                                                | I           | Device power supply                                                                                                                                                                                                                                                                                           |  |

| VR               | 9, 10                                                                         | G1, H1                                                                                            | I           | Red LED power supply                                                                                                                                                                                                                                                                                          |  |

| VG               | 51, 50                                                                        | E11, F11                                                                                          | I           | Green LED power supply                                                                                                                                                                                                                                                                                        |  |

| VB               | 49, 48                                                                        | G11, H11                                                                                          | I           | Blue LED power supply                                                                                                                                                                                                                                                                                         |  |

| R0-R15           | 1, 4, 11, 14,<br>17, 21, 24,<br>27, 32, 35,<br>38, 41, 44,<br>47, 54, 57      | B5, B2,F2, F4,<br>J2, L1, K3, H5,<br>L6, L7, L8, L10,<br>K10, H10, E10,<br>E8                     | 0           | Red LED constant-current output                                                                                                                                                                                                                                                                               |  |

| G0-G15           | 2, 5, 12, 15,<br>18, 22, 25,<br>28, 31, 34,<br>37, 40, 43,<br>46, 53, 56      | B4, C2, G2, G4,<br>K1, L2, K4, K5,<br>K6, K7, K8, L9,<br>K11, J10, F10,<br>F8                     | 0           | Green LED constant-current output                                                                                                                                                                                                                                                                             |  |

| B0-B15           | 3, 6, 13, 16,<br>19, 23, 26,<br>29, 30, 33,<br>36, 39, 42,<br>45, 52, 55      | B3, D2, H2, H4,<br>K2, L3, L4, L5,<br>H6, H7, H8, K9,<br>L11, J11, G10,<br>G8                     | 0           | Blue LED constant-current output                                                                                                                                                                                                                                                                              |  |

| LINE0-<br>LINE15 | 76, 75, 74,<br>73, 72, 71,<br>70, 69, 68,<br>67, 66, 65,<br>64, 63, 62,<br>61 | D1, C1, B1, A1,<br>A2, A3, A4, A5,<br>A6, A7, A8, A9,<br>A10, A11, B11,<br>C11                    | 0           | Scan lines                                                                                                                                                                                                                                                                                                    |  |

| SCLK             | 60                                                                            | В9                                                                                                | I           | Clock-signal input pin                                                                                                                                                                                                                                                                                        |  |

| SIN              | 59                                                                            | B8                                                                                                | I           | Serial-data input pin                                                                                                                                                                                                                                                                                         |  |

| SOUT             | 58                                                                            | B7                                                                                                | 0           | Serial data output pin                                                                                                                                                                                                                                                                                        |  |

| GND              | 7                                                                             | C10, E1, E2,<br>D5, D6, D7, D8,<br>D10, D11,<br>E1,E2, E4, E5,<br>E6,E7, F5, F6,<br>F7,G5, G6, G7 | _           | Power-ground reference                                                                                                                                                                                                                                                                                        |  |

| Thermal pad      | _                                                                             | —                                                                                                 | _           | The thermal pad and the GND pin must be connected together on the board.                                                                                                                                                                                                                                      |  |

# 7 Specifications

# 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                                |                              | MIN  | MAX | UNIT |

|------------------------------------------------|------------------------------|------|-----|------|

|                                                | VCC                          | -0.3 | 6   | V    |

|                                                | VR/G/B                       | -0.3 | 6   | V    |

| Voltage                                        | IREF, SCLK, SIN, SOUT, VSYNC | -0.3 | 6   | V    |

|                                                | RX/GX/BX                     | -0.3 | 6   | V    |

|                                                | LINE0 to LINE15              | -0.3 | 6   | V    |

| Operating junction temperature, T <sub>J</sub> |                              | -40  | 150 | °C   |

| Storage temperature, T <sub>stg</sub>          |                              | -55  | 150 | °C   |

(1) Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

## 7.2 ESD Ratings

|                    |                         |                                                                       | VALUE | UNIT |

|--------------------|-------------------------|-----------------------------------------------------------------------|-------|------|

|                    | Electrostatic discharge | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>     | ±4000 | V    |

| V <sub>(ESD)</sub> | Lieu ostatic discridige | Charged device model (CDM), per ANSI/ESDA/JEDEC JS-002 <sup>(2)</sup> | ±1000 | v    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                   |                                                   | MIN       | NOM MAX   | UNIT |

|-------------------|---------------------------------------------------|-----------|-----------|------|

| VCC               | Device supply voltage                             | 2.5       | 5.5       | V    |

| VLEDR/G/B         | LED supply voltage                                | 2.5       | 5.5       | V    |

| V <sub>IH</sub>   | High level logic input voltage (SCLK, SIN, VSYNC) | 0.7 × VCC |           | V    |

| V <sub>IL</sub>   | Low level logic input voltage (SCLK, SIN, VSYNC)  |           | 0.3 × VCC | V    |

| I <sub>OH</sub>   | High level logic output current (SOUT)            |           | -2        | mA   |

| I <sub>OL</sub>   | Low level logic output current (SOUT)             |           | 2         | mA   |

| I <sub>CH</sub>   | Constant output source current                    | 0.2       | 20        | mA   |

| I <sub>LINE</sub> | Line scan switch load current                     | 0         | 2         | А    |

| T <sub>A</sub>    | Ambient operating temperature                     | -40       | 85        | °C   |

# 7.4 Thermal Information

|                       |                                              | TLC        |           |      |

|-----------------------|----------------------------------------------|------------|-----------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | RRF (VQFN) | ZXL (BGA) | UNIT |

|                       |                                              | 76 PINS    | 96 PINS   |      |

| R <sub>θJA</sub>      | Junction-to-ambient thermal resistance       | 22.2       | 33.5      | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 10.7       | 18.6      | °C/W |

| R <sub>θJB</sub>      | Junction-to-board thermal resistance         | 7.2        | 11.7      | °C/W |

| ΨJT                   | Junction-to-top characterization parameter   | 0.1        | 0.3       | °C/W |

| Ψјв                   | Junction-to-board characterization parameter | 7.1        | 11.6      | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 1.7        |           | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

# 7.5 Electrical Characteristics

| At VCC = VR = 2.8 V, VG/B = 3.8 V and $T_A = -4$ | 10°C to +85°C: Typical values are at 1 | $T_{\Lambda} = 25^{\circ}C$ (unless otherwise specified) |

|--------------------------------------------------|----------------------------------------|----------------------------------------------------------|

|                                                  |                                        |                                                          |

|                      | PARAMETER                                            | TEST CONDITIONS                                                                                                                                                                                                                                                                                                                                                                | MIN       | TYP MAX   | UNIT |

|----------------------|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------|------|

| VCC                  | Device supply voltage                                |                                                                                                                                                                                                                                                                                                                                                                                | 2.5       | 5.5       | V    |

| / <sub>UVR</sub>     | Undervoltage restart                                 | VCC rising                                                                                                                                                                                                                                                                                                                                                                     |           | 2.3       | V    |

| V <sub>UVF</sub>     | Undervoltage shutdown                                | VCC falling                                                                                                                                                                                                                                                                                                                                                                    | 2.0       |           | V    |

| V <sub>UV(HYS)</sub> | Undervoltage shutdown<br>hysteresis                  |                                                                                                                                                                                                                                                                                                                                                                                |           | 0.1       | V    |

|                      |                                                      | SCLK/SIN = 10 MHz, MPSM_EN =<br>1bit, Matrix PSM enable, internal<br>GCLK off, GSn = 0000h, BC = 2h,<br>CCR/G/B = 63h, PS_EN= 1h,<br>VOUTn = floating, R <sub>IREF</sub> = 7.8 kΩ (In<br>intelligent power save mode)                                                                                                                                                          |           | 0.9       | mA   |

|                      |                                                      | $\begin{array}{l} \text{SCLK/SIN} = 10 \text{ MHz}, \text{ Standby} \\ \text{enable, internal GCLK off, GSn} = \\ 0000h, BC = 2h, CCR/G/B = 63h, \\ \text{PS}\_\text{EN} = 1h, \text{VOUTn} = \text{floating,} \\ \text{R}_{\text{IREF}} = 7.8 \text{ k}\Omega \text{ (In intelligent power} \\ \text{save mode)} \end{array}$                                                 |           | 0.9       | mA   |

| ICC                  | Device supply current                                | $\begin{array}{l} \text{SCLK/SIN} = 10 \text{ MHz}, \text{PSP}\_\text{MOD} = \\ 1 \text{bit, internal GCLK} = 50 \text{MHz}, \text{ GSn} = \\ 0000\text{h}, \text{BC} = 2\text{h}, \text{CCR/G/B} = 63\text{h}, \\ \text{PS}\_\text{EN} = 1\text{h}, \text{VOUTn} = \text{floating}, \\ \text{R}_{\text{IREF}} = 7.8 \text{ k}\Omega \text{ (In power save mode)} \end{array}$ |           | 3.6       | mA   |

|                      |                                                      | $\begin{array}{l} \text{SCLK} = 10 \text{ MHz, internal GCLK} = 50 \\ \text{MHz, GSn} = 1\text{FFFh, BC} = 2h, \\ \text{CCR/G/B} = 63h, \text{VOUTn} = \text{floating,} \\ \text{R}_{\text{IREF}} = 7.8  \text{k}\Omega, \text{ I}_{\text{CH}} = 2 \text{ mA} \end{array}$                                                                                                     |           | 3.6       | mA   |

|                      |                                                      | SCLK = 10 MHz, internal GCLK =<br>100 MHz, GSn = 1FFFh, BC = 2h,<br>CCR/G/B = 63h, VOUTn = floating,<br>$R_{IREF}$ = 7.8 kΩ, $I_{CH}$ = 2 mA                                                                                                                                                                                                                                   |           | 4.9       | mA   |

| /R/G/B               | LED supply voltage                                   |                                                                                                                                                                                                                                                                                                                                                                                | 2.5       | 5.5       | V    |

| Ин                   | High level input voltage (SCLK, SIN)                 |                                                                                                                                                                                                                                                                                                                                                                                | 0.7 × VCC |           | V    |

| / <sub>IL</sub>      | Low level input voltage (SCLK, SIN)                  |                                                                                                                                                                                                                                                                                                                                                                                |           | 0.3 × VCC | V    |

| / <sub>OH</sub>      | High level output voltage (SOUT)                     | IOH = –2 mA at SOUT                                                                                                                                                                                                                                                                                                                                                            | VCC-0.4   | VCC       | V    |

| / <sub>OL</sub>      | Low level output voltage (SOUT)                      | IOL = 2 mA at SOUT                                                                                                                                                                                                                                                                                                                                                             |           | 0.4       | V    |

| OGIC                 | Logic pin current (SCLK, SIN)                        | SCLK/SIN = VCC or GND                                                                                                                                                                                                                                                                                                                                                          | -1        | 1         | uA   |

| R <sub>DS(ON)</sub>  | Scan switches' on-state resistance (LINE0 to LINE15) | VCC = 2.8 V, T <sub>A</sub> = 25°C                                                                                                                                                                                                                                                                                                                                             |           | 190       | mΩ   |

| / <sub>IREF</sub>    | Reference voltage                                    | $\begin{array}{l} \text{SCLK/SIN} = \text{GND, internal GCLK} \\ \text{0MHz, GSn} = \text{0000h, BC} = 2h, \\ \text{CCR/G/B} = 63h, \text{VOUTn} = \text{floating,} \\ \text{R}_{\text{IREF}} = 7.8 \text{ k}\Omega \end{array}$                                                                                                                                               |           | 0.8       | V    |

# 7.5 Electrical Characteristics (continued)

<u>At VCC = VR = 2.8 V</u>, VG/B = 3.8 V and  $T_A = -40^{\circ}$ C to +85°C; Typical values are at  $T_A = 25^{\circ}$ C (unless otherwise specified)

|                   | PARAMETER                                                       | TEST CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                               | MIN | TYP  | MAX  | UNIT |

|-------------------|-----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|------|------|

|                   |                                                                 | VLEDR/G/B ≥ 2.8 V, all channel<br>outputs on, output current at 1 mA                                                                                                                                                                                                                                                                                                                                          |     |      | 0.25 | V    |

|                   |                                                                 | VLEDR/G/B ≥ 2.8 V, all channel<br>outputs on, output current at 5 mA                                                                                                                                                                                                                                                                                                                                          |     |      | 0.26 | V    |

| V <sub>KNEE</sub> | Channel knee voltage (R0-R15 /                                  | VLEDR/G/B ≥ 2.8 V, all channel<br>outputs on, output current at 10 mA                                                                                                                                                                                                                                                                                                                                         |     |      | 0.3  | V    |

| INE               | G0-G15 / B0-B15)                                                | VLEDR/G/B $\ge$ 2.8 V, IMAX = 1b, all channel outputs on, output current at 15 mA                                                                                                                                                                                                                                                                                                                             |     |      | 0.37 | V    |

|                   |                                                                 | VLEDR/G/B ≥ 2.8 V, IMAX=1b, all<br>channel outputs on, output current at<br>20 mA                                                                                                                                                                                                                                                                                                                             |     |      | 0.41 | V    |

| CH(LKG)           | Channel leakage current (R0-<br>R15 / G0-G15 / B0-B15)          | Channel voltage at 0 V                                                                                                                                                                                                                                                                                                                                                                                        |     |      | 1    | uA   |

|                   |                                                                 | All CHn = on, BC = 00h, CC = 31h,<br>VOUTn = (VLED-1)V, R <sub>IREF</sub> = 19.05<br>k $\Omega$ (I <sub>CH</sub> = 0.2-mA target), T <sub>A</sub> = 25°C,<br>includes the V <sub>IREF</sub> tolerance, at<br>same color grouped outputs of R0-<br>R15 / G0-G15 / B0-B15                                                                                                                                       |     | ±1   | ±2.5 | %    |

|                   |                                                                 | $\begin{array}{l} \mbox{All CHn} = \mbox{on, BC} = \mbox{00h, CC} = \mbox{7Dh,} \\ \mbox{VOUTn} = (VLED-1)V, \mbox{$R_{IREF}$} = \mbox{19.05} \\ \mbox{$k\Omega$} (\mbox{$I_{CH}$} = \mbox{0.5-mA} target), \mbox{$T_{A}$} = \mbox{25}^{\circ}\mbox{$C$}, \\ \mbox{includes the $V_{IREF$}$ tolerance, at} \\ \mbox{same color grouped outputs of $R0$-} \\ \mbox{$R15$ / $G0$-$G15$ / $B0$-B15} \end{array}$ |     | ±0.5 | ±1.5 | %    |

|                   | Constant-current channel to                                     | All CHn = on, BC = 00h, CC = FBh,<br>VOUTn = (VLED-1)V, $R_{IREF} = 19.05$<br>$k\Omega$ (I <sub>CH</sub> = 1-mA target), $T_A = 25^{\circ}$ C,<br>includes the V <sub>IREF</sub> tolerance, at<br>same color grouped outputs of R0-<br>R15 / G0-G15 / B0-B15                                                                                                                                                  |     | ±0.5 | ±1.5 | %    |

|                   | channel deviation (R0-R15 / G0-<br>G15 / B0-B15) <sup>(1)</sup> | All CHn = on, BC = 2h, CC = FBh,<br>VOUTn = (VLED-1)V, $R_{IREF} = 7.8 \text{ k}\Omega$<br>( $I_{CH} = 5$ -mA target), $T_A = 25^{\circ}$ C,<br>includes the V <sub>IREF</sub> tolerance, at<br>same color grouped outputs of R0-<br>R15 / G0-G15 / B0-B15                                                                                                                                                    |     | ±0.5 | ±2   | %    |

|                   | -                                                               | All CHn = on, BC = 6h, CC = A7h,<br>VOUTn = (VLED-1)V, $R_{IREF} = 7.8 \text{ k}\Omega$<br>( $I_{CH} = 10$ -mA target), $T_A = 25^{\circ}$ C,<br>includes the V <sub>IREF</sub> tolerance, at<br>same color grouped outputs of R0-<br>R15 / G0-G15 / B0-B15                                                                                                                                                   |     | ±0.5 | ±2   | %    |

|                   |                                                                 | All CHn = on, BC = 7h, CC = FBh,<br>IMAX=1b, VOUTn = (VLED-1)V,<br>$R_{IREF} = 6.8 k\Omega (I_{CH} = 20$ -mA target),<br>$T_A = 25^{\circ}$ C, includes the V <sub>IREF</sub><br>tolerance, at same color grouped<br>outputs of R0-R15 / G0-G15 / B0-<br>B15                                                                                                                                                  |     | ±0.5 | ±2.5 | %    |

# 7.5 Electrical Characteristics (continued)

At VCC = VR = 2.8 V, VG/B = 3.8 V and  $T_A = -40^{\circ}$ C to +85°C; Typical values are at  $T_A = 25^{\circ}$ C (unless otherwise specified)

|                         | PARAMETER                                                      | TEST CONDITIONS                                                                                                                                                                                                                                                  | MIN TYP | MAX  | UNIT |

|-------------------------|----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|------|

|                         |                                                                | All CHn = on, BC = 00h, CC = 31h,<br>VOUTn = (VLED-1)V, $R_{IREF}$ = 19.05<br>k $\Omega$ (I <sub>CH</sub> = 0.2-mA target), T <sub>A</sub> = 25°C,<br>includes the V <sub>IREF</sub> tolerance, at<br>same color grouped outputs of R0-<br>R15 / G0-G15 / B0-B15 | ±1      | ±2.5 | %    |

|                         |                                                                | All CHn = on, BC = 00h, CC = 7Dh,<br>VOUTn = (VLED-1)V, $R_{IREF}$ = 19.05<br>k $\Omega$ (I <sub>CH</sub> = 0.5-mA target), T <sub>A</sub> = 25°C,<br>includes the V <sub>IREF</sub> tolerance, at<br>same color grouped outputs of R0-<br>R15 / G0-G15 / B0-B15 | ±0.5    | ±1.5 | %    |

|                         | Constant-current device to                                     | All CHn = on, BC = 00h, CC = FBh,<br>VOUTn = (VLED-1)V, $R_{IREF} = 19.05$<br>$k\Omega$ (I <sub>CH</sub> = 1-mA target), $T_A = 25^{\circ}$ C,<br>includes the V <sub>IREF</sub> tolerance, at<br>same color grouped outputs of R0-<br>R15 / G0-G15 / B0-B15     | ±0.5    | ±1   | %    |

| ΔI <sub>ERR(DD)</sub>   | device deviation (R0-R15 / G0-<br>G15 / B0-B15) <sup>(2)</sup> | All CHn = on, BC = 2h, CC = FBh,<br>VOUTn = (VLED-1)V, $R_{IREF} = 7.8 \text{ k}\Omega$<br>( $I_{CH} = 5$ -mA target), $T_A = 25^{\circ}$ C,<br>includes the V <sub>IREF</sub> tolerance, at<br>same color grouped outputs of R0-<br>R15 / G0-G15 / B0-B15       | ±0.5    | ±1.5 | %    |

|                         |                                                                | All CHn = on, BC = 6h, CC = A7h,<br>VOUTn = (VLED-1)V, $R_{IREF} = 7.8 \text{ k}\Omega$<br>( $I_{CH} = 10$ -mA target), $T_A = 25^{\circ}C$ ,<br>includes the V <sub>IREF</sub> tolerance, at<br>same color grouped outputs of R0-<br>R15 / G0-G15 / B0-B15      | ±0.5    | ±2   | %    |

|                         |                                                                | All CHn = on, BC = 7h, CC = FBh,<br>IMAX=1b, VOUTn = (VLED-1)V,<br>$R_{IREF}$ = 6.8 k $\Omega$ (I <sub>CH</sub> = 20-mA target),<br>$T_A$ = 25°C, includes the V <sub>IREF</sub><br>tolerance, at same color grouped<br>outputs of R0-R15 / G0-G15 / B0-<br>B15  | ±0.5    | ±2   | %    |

| ∆I <sub>REG(LINE)</sub> | Line regulation (R0-R15 / G0-<br>G15 / B0-B15) <sup>(3)</sup>  | VLED = 2.5 to 5.5 V, All CHn = on,<br>VOUTn = (VLED-1)V, at same color<br>grouped outputs of R0-R15 / G0-<br>G15 / B0-B15                                                                                                                                        |         | ±1   | %/V  |

| IJ <sub>REG(LOAD)</sub> | Load regulation (R0-R15 / G0-<br>G15 / B0-B15) <sup>(4)</sup>  | VOUTn = (VLED-1)V to (VLED-3)V,<br>VR=VG/B=VLED = 3.8 V, All CHn =<br>on, at same color grouped outputs of<br>R0-R15 / G0-G15 / B0-B15                                                                                                                           |         | ±1   | %/V  |

| Г <sub>TSD</sub>        | Thermal shutdown threshold                                     |                                                                                                                                                                                                                                                                  | 170     |      | °C   |

|                         |                                                                |                                                                                                                                                                                                                                                                  |         |      |      |

(1) The deviation of each output in same color group (OUTR0-15 or OUTG0-15 or OUTB0-15) from the average of same color group

constant current. The deviation is calculated by the formula. (X = R or G or B, n = 0-15)  $\Delta(\%) = \left[\frac{I_{Xn}}{\frac{I_{X0} + I_{X1} + \dots + I_{X14} + I_{X15}}{16}} - 1\right] \times 100$

(2) The deviation of the average of constant-current in each color group from the ideal constant-current value. (X = R or G or B) :

$\Delta(\%) = \left[\frac{I_{X0} + I_{X1} + \dots + I_{X14} + I_{X15}}{16} - \text{Ideal Output Current}}\right] \times 100$   $I_{IDEAL_R(or \ G \ or \ B)} = \frac{V_{IREF}}{R_{IREF}} \times GAIN_{(BC)} \times \frac{1 + CC_R(or \ CC_G \ or \ CC_B)}{256}$

(3) Line regulation is calculated by the following equation. (X = R or G or B, n = 0-15):  $\int_{(0,1)} \left[ (I_{Xn} at V_{LED} = 5.5 V) - (I_{Xn} at V_{LED} = 2.5 V) \right]_{1.1} = 100$

$$\Delta(\%V) = \left[\frac{(XR - BBD) - (XR - BBD)}{(I_{XR} at V_{LED} = 2.5 V)}\right] \times \frac{100}{5.5 V - 2.5 V}$$

be a regulation is calculated by the following equation. (X = R or G or B, n =

(4) Load regulation is calculated by the following equation. (X = R or G or B, n = 0-15):

$$\Delta(\%V) = \left[\frac{(I_{Xn} at V_{Xn} = 1 V) - (I_{Xn} at V_{Xn} = 3 V)}{(I_{Xn} at V_{Xn} = 3 V)}\right] \times \frac{100}{3 V - 1 V}$$

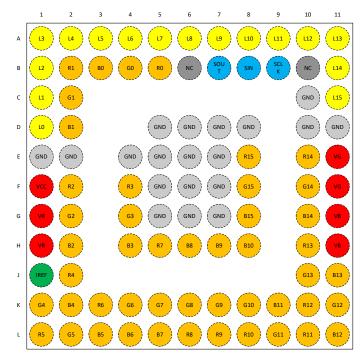

# 7.6 Timing Requirements

| At VCC = VR = 2.8 V, VG/B = 3.8 V and T <sub>A</sub> | $-10^{\circ}$ C to $+85^{\circ}$ C. Typical values are at $-10^{\circ}$ | $T_{\rm e} = 25^{\circ}C$ (unless otherwise specified) |

|------------------------------------------------------|-------------------------------------------------------------------------|--------------------------------------------------------|

| AI V C C = VI I = 2.0 V, V G/D = 3.0 V and I P       | = $-40$ C to $100$ C, Typical values are at                             | $I_A = 20 \text{ C (ulliess otherwise specified)}$     |

|                    | PARAMETER                        | TEST CONDITIONS                                | MIN | TYP | MAX | UNIT |

|--------------------|----------------------------------|------------------------------------------------|-----|-----|-----|------|

| f <sub>SCLK</sub>  | Clock frequency (SCLK)           |                                                |     |     | 25  | MHz  |

| t <sub>w(H1)</sub> | High level pulse duration (SCLK) |                                                | 18  |     |     | ns   |

| t <sub>w(L1)</sub> | Low level pulse duration (SCLK)  |                                                | 18  |     |     | ns   |

| t <sub>su(0)</sub> | Setup time                       | SIN to SCLK ↑                                  | 10  |     |     | ns   |

| t <sub>su(1)</sub> | Setup time                       | SIN to SCLK $\downarrow$                       | 10  | ·   |     | ns   |

| t <sub>h(0)</sub>  | Hold time                        | SCLK $\uparrow$ to SIN $\uparrow \downarrow$   | 2   |     |     | ns   |

| t <sub>h(1)</sub>  | Hold time                        | SCLK $\downarrow$ to SIN $\uparrow \downarrow$ | 2   |     |     | ns   |

# 7.7 Switching Characteristics

At VCC = VR = 2.8 V, VG/B = 3.8 V and  $T_A = -40^{\circ}$ C to +85°C; Typical values are at  $T_A = 25^{\circ}$ C (unless otherwise specified)

|                    | PARAMETER         | TEST CONDITIONS                                                                      | MIN | TYP | MAX  | UNIT |

|--------------------|-------------------|--------------------------------------------------------------------------------------|-----|-----|------|------|

| t <sub>r</sub>     | Rise time (SOUT)  | VCC = 3.3 V, C <sub>SOUT</sub> = 30 pF                                               |     | 2   | 10   | ns   |

| t <sub>f</sub>     | Fall time (SOUT)  | VCC = 3.3 V, C <sub>SOUT</sub> = 30 pF                                               |     | 2   | 10   | ns   |

| t <sub>pd(0)</sub> | Propagation delay | SCLK $\uparrow~$ to SOUT $\uparrow~\downarrow$ , full temperature, C_SOUT = 30 pF    | 3.5 |     | 14.2 | ns   |

| t <sub>pd(1)</sub> | Propagation delay | SCLK $\downarrow $ to SOUT $\uparrow  \downarrow$ , full temperature, C_SOUT = 30 pF | 3.5 |     | 14.2 | ns   |

(1). Input pulse rise and fall time is 2 ns typically.

### 図 7-1. Timing and Switching Diagram (Dual Edge)

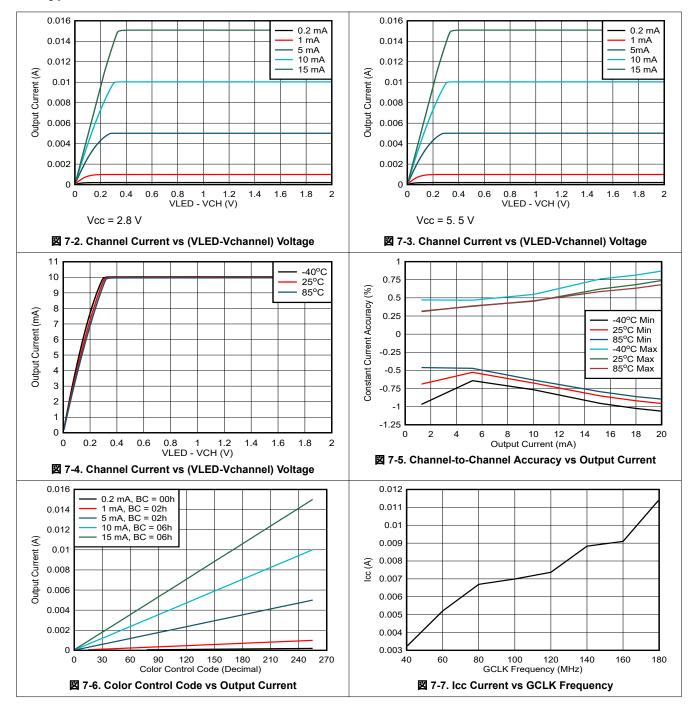

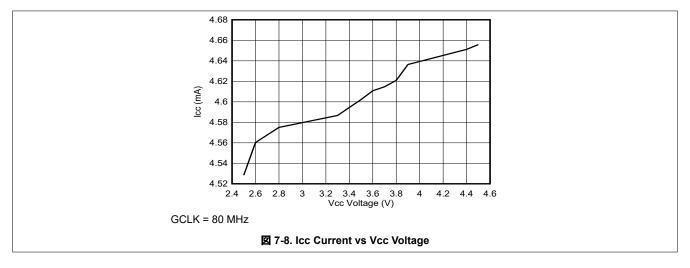

## 7.8 Typical Characteristics

Copyright © 2022 Texas Instruments Incorporated

# 7.8 Typical Characteristics (continued)

# 8 Detailed Description

## 8.1 Overview

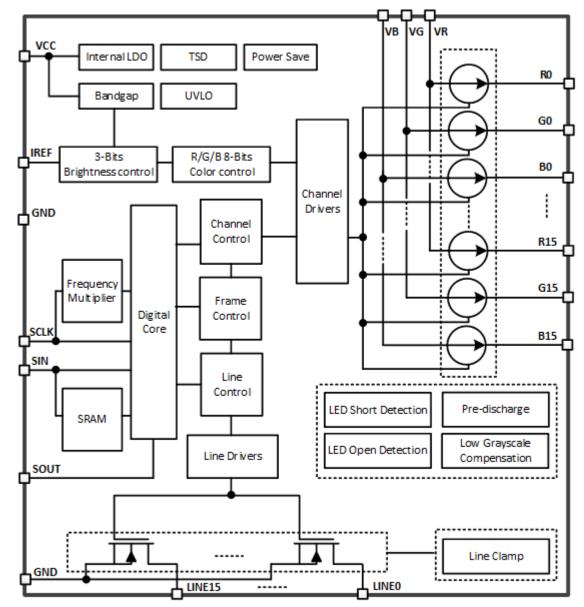

The TLC6984 is a highly-integrated, common cathode LED-display driver with 48 constant current sources and 16 scanning FETs. A single TLC6984 is capable of driving 16 × 16 RGB LED pixels while stacking four TLC6984s can drive 64 × 64 RGB LED pixels. To achieve low-power consumption, the device supports separated power supplies for the red, green, and blue LEDs by its common cathode structure. Furthermore, the operation power of the TLC6984 is significantly reduced by ultra-low operation voltage range (V<sub>CC</sub> down to 2.5 V) and ultra-low operation current (I<sub>CC</sub> down to 3.6 mA).

The TLC6984 supports per channel current from 0.2 mA to 20 mA, with typical 0.5% channel-to-channel current deviation and typical 0.5% device-to-device current deviation. The DC current value of all 48 channels is set by an external IREF resistor and can be adjusted by the 8-step global brightness control (BC) and the 256-step per-color group brightness control (CC\_R/CC\_G/CC\_B).

The TLC6984 implements a high-speed, dual-edge transmission interface to support high device count daisychained and high-refresh rate while minimizing electrical-magnetic interference (EMI). The TLC6984 supports up to 25-MHz SCLK (external) and up to 160-MHz GCLK (internal). Meanwhile, the device integrates enhanced circuits and intelligent algorithms to solve the various display challenges in Narrow Pixel Pitch (NPP) LED display applications and mini and micro-LED products: dim at the fist scan line, upper and downside ghosting, non-uniformity in low grayscale, coupling, caterpillar caused by open or short LEDs, which make the TLC6984 a perfect choice in such applications.

The TLC6984 also implements LED open, weak-short, short detections and removals during operations and can also report this information out to the accompanying digital processor.

# 8.2 Functional Block Diagram

# 8.3 Feature Description

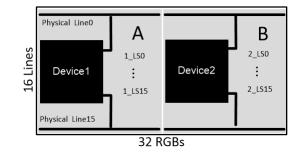

### 8.3.1 Independent and Stackable Mode

The TLC6984 can operate in two different modes: independent or stackable. In independent mode, a single TLC6984 can drive a 16 × 16 RGB LED matrix, while in stackable mode, up to four TLC6984s can be stacked together, which means the line switches of one device can be shared to the others. Stacking three TLC6984s can drive a 48 × 48 RGB LED matrix while stacking four TLC6984s can drive a 64 × 64 RGB matrix. The mode can be configured by the MOD\_SIZE (see FC2 for more details).

### 8.3.1.1 Independent Mode

$\boxtimes$  8-1 shows an implementation of a 16 × 32 RGB LED matrix using two TLC6984s in independent mode. Each device is responsible for its own 16 ×16 RGB LED matrix which means that all the data for section A is stored in device 1 and the data for section B is stored in device 2.

☑ 8-1. Two Devices in Independent Mode

The unused line must be assigned to the last several lines of the device. For example, if there are only 14 scanning lines, then the two unused lines must be assigned to 1\_LS14 and 1\_LS15.

#### 8.3.1.2 Stackable Mode

表 8-1 shows operating the TLC6984 in stackable mode.

|       | 20 U U      |                |                    |

|-------|-------------|----------------|--------------------|

| Mode  | Matrix Size | Register Value | Scan Sequence      |

| Mode1 | 16 × 32     | 000b           | D1, D2 independent |

| Mode2 | 32 × 32     | 001b           | D1->D2             |

| Mode3 | 48 × 48     | 010b           | D1->D2->D3         |

| Mode4 | 48 × 48     | 011b           | D1->D3->D2         |

| Mode5 | 48 × 64     | 100b           | D1->D2->D3         |

| Mode6 | 48 × 64     | 101b           | D1->D3->D2         |

| Mode7 | 64 × 64     | 110b           | D1->D2->D3->D4     |

| Mode8 | 64 × 64     | 111b           | D1->D4->D2->D3     |

#### 表 8-1. Stackable Mode

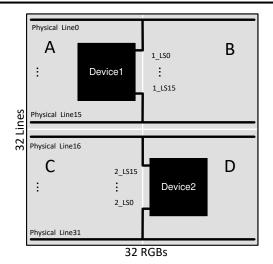

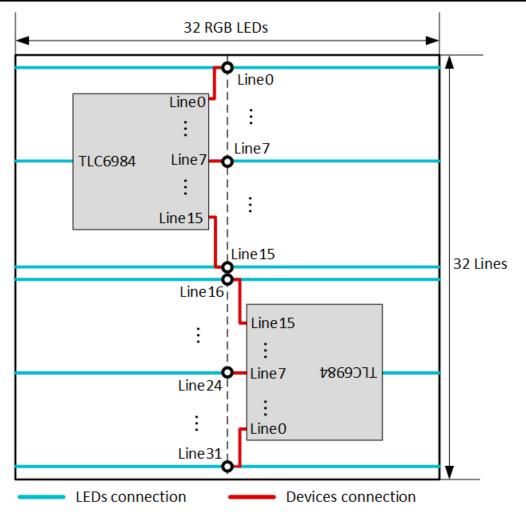

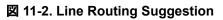

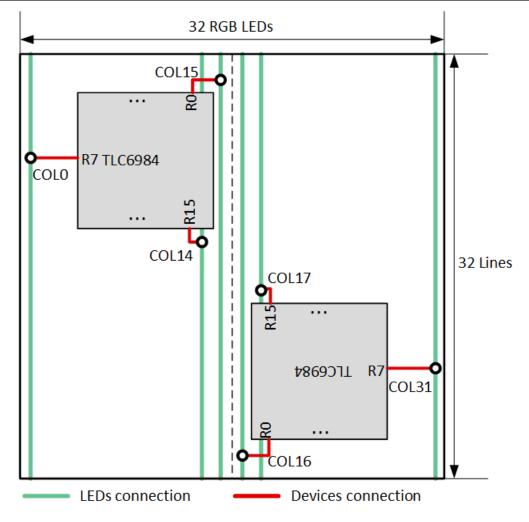

$\boxtimes$  8-2 shows that device 2 must be rotated 180° relative to device 1. This action allows the position of line switches to be near the center column of the LED matrix for better routing. For device 1, the lines are connected sequentially (line switch 0 connected to scan line 1). However on device 2, it is connected in reverse order, with the 16<sup>th</sup> scan line is connected to line switch 15 and the 32<sup>th</sup> scan line is connected to line switch 0.

$\boxtimes$  8-2 shows the connection between two TLC6984 devices in stackable mode driving a 32 × 32 RGB LED pixels. The MOD\_SIZE must be configured to 001b. Device1 supplies 16 line switches for the first 16 scan line, and device 2 supplies 16 line switches for scan line 17-32. The data for matrix sections A and C are stored in device 1, while matrix sections B and D data are stored in device 2.

To make sure the scanning sequence is still from 1<sup>st</sup> line to 32<sup>nd</sup> line, the scan line switching order of the second device must be reversed, This configuration can be completed by the SCAN\_REV (see FC4 for more details).

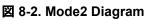

# 🛛 8-3. Mode3 and Mode4 Diagram

## 🛛 8-4. Mode5 and Mode6 Diagram

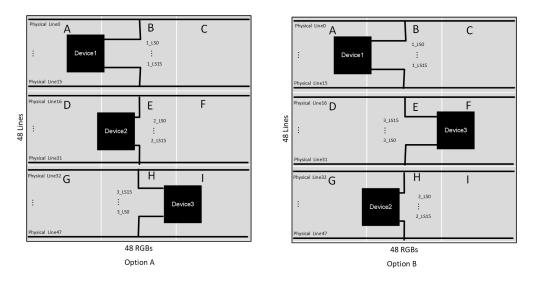

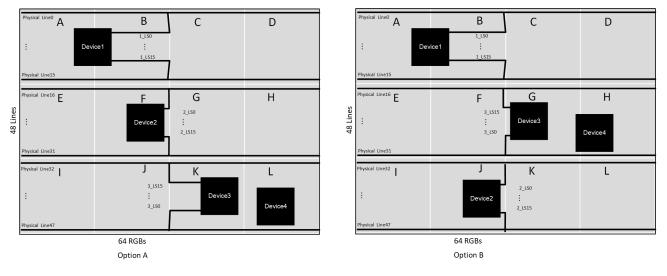

### 図 8-5. Mode7 and Mode8 Diagram

When two TLC6984 devices are used in stackable mode, if there are unused line switches, these unused line switches must be the last line switches of the first or the second device. For example, if there are only 30 scanning lines, and if,

SCAN\_REV = '0'b, the unused line switches can be either of below,

- 1\_LS14, 1\_LS15

- 2\_LS14, 2\_LS15

SCAN\_REV = '1'b, the unused line switches can be either of below,

- 1 LS14, 1 LS15

- 2\_LS1, 2\_LS0

If the unused line switches are 1\_LS14, 1\_LS15, the FC6-FC13 registers must be configured. If the unused line switches are 2\_LS14, 2\_LS15 when SCAN\_REV = '0' or 2\_LS1, 2\_LS0 when SCAN\_REV = '1', there is no need to configure FC6-FC13 registers.

### 8.3.2 Current Setting

### 8.3.2.1 Brightness Control (BC) Function

The TLC6984 device is able to adjust the output current of all constant-current outputs simultaneously. This function is called global brightness control (BC). The global BC for all outputs is programmed with a 3-bit register, thus all output currents can be adjusted in 8 steps for a given current-programming resistor,  $R_{IREF}$ . When the 3-bit BC register changes, the gain of output current, GAIN<sub>BC</sub> changes as  $\frac{1}{5}$  8-2 below.

#### 表 8-2. Current Gain Versus BC Code

| BC Register (BC) | Current Gain (GAIN <sub>BC</sub> ) |

|------------------|------------------------------------|

| 000b             | 24.17                              |

| 001b             | 30.57                              |

| 010b             | 49.49                              |

| 011b (default)   | 86.61                              |

| 100b             | 103.94                             |

| 101b             | 129.92                             |

| 110b             | 148.48                             |

| 111b             | 173.23                             |

The maximum output current per channel,  $I_{OUTSET}$ , is determined by resistor  $R_{IREF}$ , and the GAIN<sub>BC</sub>. The voltage on IREF is typically 0.8 V. Use  $\neq 1$  to calculate  $R_{IREF}$ . For noise immunity purpose, suggest  $R_{IREF} < 40 \text{ k}\Omega$ .

$$R_{IREF}(k\Omega) = \frac{V_{IREF}(V)}{I_{IREF}(mA)} = \frac{V_{IREF}(V)}{I_{OUTSET}(mA)} \times GAIN_{(BC)}$$

(1)

#### 8.3.2.2 Color Brightness Control (CC) Function

The TLC6984 device is able to adjust the output current of each of the three color groups R0-R15, G0-G15, and B0-B15 separately. This function is called color brightness control (CC). For each color, it has 8-bit data register, CC\_R, CC\_G, or CC\_B. Thus, all color group output currents can be adjusted in 256 steps from 0% to 100% of the maximum output current,  $I_{OUTSET}$ . Use  $\neq 2$  to calculate the output current of each color,  $I_{OUT R (or G or B)}$ .

$$I_{OUT\_R(or\ G\ or\ B)} = I_{OUTSET} \times \frac{1 + CC\_R(or\ CC\_G\ or\ CC\_B)}{256}$$

(2)

Table  $\frac{1}{8}$  8-3 shows the CC data versus the constant-current against I<sub>OUTSET</sub>.

| CC Register (CC_R or CC_G or CC_B) | Ratio of I <sub>OU</sub> | ITSET  |

|------------------------------------|--------------------------|--------|

| 0000 0000ь                         | 1/256                    | 0.39%  |

| 0000 0001b                         | 2/256                    | 0.78%  |

|                                    |                          |        |

| 0111 1111b (default)               | 128/256                  | 50%    |

|                                    |                          |        |

| 1111 1110b                         | 255/256                  | 99.61% |

| 1111 1111b                         | 256/256                  | 100%   |

#### 表 8-3. CC Data vs Current Ratio

#### 8.3.2.3 Choosing BC/CC for a Different Application

BC is mainly used for global brightness adjustment to adapt to ambient brightness, such as between day and night, indoor and outdoor.

- Suggested BC is 3h or 4h, which is in the middle of the range, allowing flexible changes in brightness up and down.

- If the current of one color group (usually R LEDs) is close to the output maximum current (10 mA or 20 mA), to prevent the constant output current from exceeding the upper limit in case a larger BC code is input accidentally, choose the maximum BC value, 7h.

- If the current of one color group (usually B LEDs) is close to the output minimum current (0.2 mA), to prevent the constant output current from exceeding the lower limit in case a lower BC code is input accidentally, choose the minimum BC code, 0h.

CC can be used to fine tune the brightness in 256 steps. This action is suitable for white balance adjustment between RGB color group. To get a pure white color, the general requirement for the luminous intensity ratio of R, G, B LED is 5:3:2. Depending on the characteristics of the LED (Electro-Optical conversion efficiency), the current ratio of R, G, B LED is much different from this ratio. Usually, the Red LED needs the largest current. Choose 255d (the maximum value) CC code for the color group that needs the largest initial current, then choose proper CC code for the other two color groups according to the current ratio requirement of the LED used.

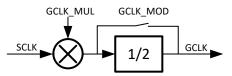

#### 8.3.3 Frequency Multiplier

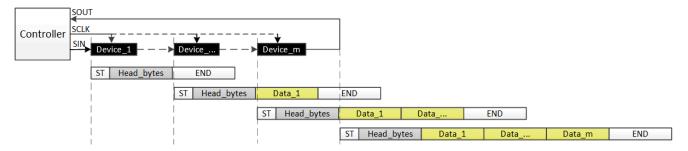

The TLC6984 has an internal frequency multiplier to generate the GCLK by SCLK. The GCLK frequency can be configured by FREQ\_MOD (See FC0 for more details) and FREQ\_MUL (see FC0 for more details) from 40 MHz to 160 MHz. As  $\boxtimes$  8-6 shows, if the GCLK frequency is not higher than 80 MHz, the GCLK\_MOD is set to 0 to disable the bypass switch (enable the ½ divider), while the GCLK frequency is higher than 80 MHz, the GCLK\_MOD is set to 1 to enable the bypass switch (disable the ½ divider).

図 8-6. Frequency Multiplier Block Diagram

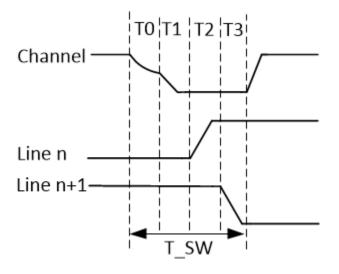

#### 8.3.4 Line Transitioning Sequence

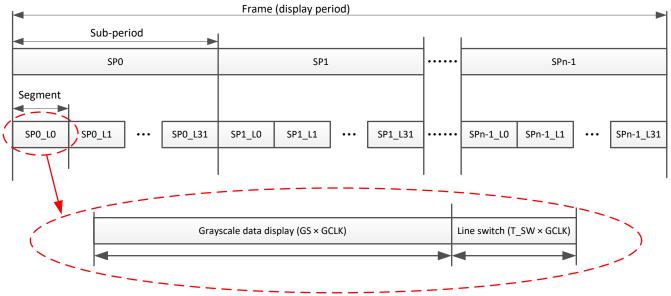

The TLC6984 defines a timing sequence of scan line transition, shown as  $\boxtimes$  8-7. T\_SW is the total transitioning time. T\_SW is broken up into four intervals: T0 is the time interval between the end of PWM time in current segment and the beginning of channel pre-discharge, T1 is the time interval between the beginning of the channel pre-discharge and the beginning of current line OFF, T2 is the time interval that the beginning of current line OFF and the beginning of next line ON, T3 is the time interval of the beginning of next line ON and the beginning of PWM time in next segment.

**1** 8-7. Line Transitioning Sequence

The line switch time T\_SW equals to T0 + T1 + T2 + T3. T\_SW can be configured by the LINE\_SWT (see FC1 register bit 40-37 in FC1).

表 8-4 is the relation between LINE\_SWT bits and the line switch time (GCLK numbers) with different internal GCLK frequency.

|              |                 |                            | 表 8-4. Line Sv            | witch Time                 |                            |                             |

|--------------|-----------------|----------------------------|---------------------------|----------------------------|----------------------------|-----------------------------|

| LINE_SW<br>T | GCLK<br>Numbers | T_SW (us, 40-<br>MHZ GCLK) | T_SW (us, 60-MHZ<br>GCLK) | T_SW (us, 100-MHZ<br>GCLK) | T_SW (us, 120-MHZ<br>GCLK) | T_SW (us, 160-<br>MHZ GCLK) |

| 0000b        | 45              | 1.125                      | 0.7515                    | 0.45                       | 0.3735                     | 0.2835                      |

| 0001b        | 60              | 1.5                        | 1.002                     | 0.6                        | 0.498                      | 0.378                       |

| 0010b        | 90              | 2.25                       | 1.503                     | 0.9                        | 0.747                      | 0.567                       |

| 0011b        | 120             | 3                          | 2.004                     | 1.2                        | 0.996                      | 0.756                       |

| 0100b        | 150             | 3.75                       | 2.505                     | 1.5                        | 1.245                      | 0.945                       |

| 0101b        | 180             | 4.5                        | 3.006                     | 1.8                        | 1.494                      | 1.134                       |

| 0110b        | 210             | 5.25                       | 3.507                     | 2.1                        | 1.743                      | 1.323                       |

| 0111b        | 240             | 6                          | 4.008                     | 2.4                        | 1.992                      | 1.512                       |

| 1000b        | 270             | 6.75                       | 4.509                     | 2.7                        | 2.241                      | 1.701                       |

| 1001b        | 300             | 7.5                        | 5.01                      | 3                          | 2.49                       | 1.89                        |

| 1010b        | 330             | 8.25                       | 5.511                     | 3.3                        | 2.739                      | 2.079                       |

| 1011b        | 360             | 9                          | 6.012                     | 3.6                        | 2.988                      | 2.268                       |

| 1100b        | 390             | 9.75                       | 6.513                     | 3.9                        | 3.237                      | 2.457                       |

| 1101b        | 420             | 10.5                       | 7.014                     | 4.2                        | 3.486                      | 2.646                       |

| 1110b        | 450             | 11.25                      | 7.515                     | 4.5                        | 3.735                      | 2.835                       |

| 1111b        | 480             | 12                         | 8.016                     | 4.8                        | 3.984                      | 3.024                       |

### 8.3.5 Protections and Diagnostics

### 8.3.5.1 Thermal Shutdown Protection

The thermal shutdown (TSD) function turns off all IC constant-current outputs when the junction temperature ( $T_J$ ) exceeds 170°C (typical). The function resumes normal operation when  $T_J$  falls below 155°C (typical).

### 8.3.5.2 IREF Resistor Short Protection

The IREF resistor short protection (ISP) function prevents unwanted large currents from flowing through the constant-current output when the IREF resistor is shorted accidently. The TLC6984 device turns off all output channels when the IREF pin voltage is lower than 0.19 V (typical). When the IREF pin voltage goes higher than 0.325 V (typical), the TLC6984 device resumes normal operation.

### 8.3.5.3 LED Open Load Detection and Removal

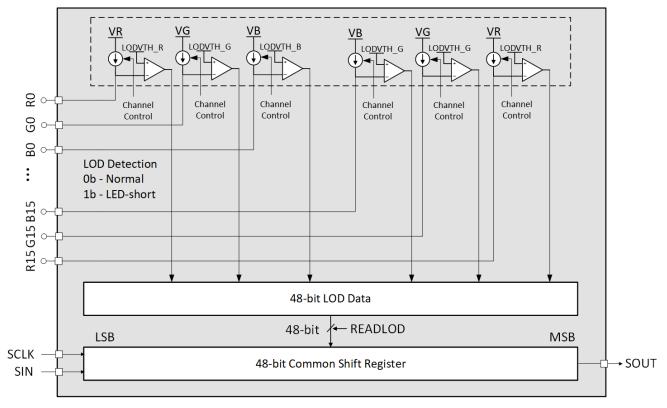

#### 8.3.5.3.1 LED Open Detection

The LED open detection (LOD) function detects faults caused by an open circuit in any LED, or a short from OUTn to VLED with low impedance. This function was realized by comparing the OUTn voltage to the LOD detection threshold voltage level set by LODVTH\_R/LODVTH\_G/LODVTH\_B (See FC3 for more details). If the OUTn voltage is higher than the programmed voltage, the corresponding output LOD bit is set to 1 to indicate an open LED. Otherwise, the output of that LOD bit is 0. LOD data output by the detection circuit are valid only during the OUTn turning on period.

図 8-8 shows the equivalent circuit of LED open detection.

### 図 8-8. LED Open Detection Circuit

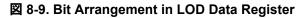

The LED open detection function records the position of the open LED, which contains the scan line number and relevant channel number. The scan line order is stored LOD\_LINE\_WARN register (see FC16, FC17 for more details), and the channel number is latched into the internal 48-bit LOD data register (see FC20 for more details) at the end of each segment.  $\boxtimes$  8-9 shows the bit arrangement of the LOD data register.

| OD Data Re<br>LSB |           |           |           |           |           |           |           |           |           |           |           |           |           |           |            |

|-------------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|------------|

| LOD Bit0          | LOD Bit1  | LOD Bit2  | LOD Bit3  | LOD Bit4  | LOD Bit5  | LOD Bit6  | LOD Bit7  | LOD Bit8  | LOD Bit9  | LOD Bit10 | LOD Bit11 | LOD Bit12 | LOD Bit13 | LOD Bit14 | LOD Bit15  |

| RO                | R1        | R2        | R3        | R4        | R5        | R6        | R7        | R8        | R9        | R10       | R11       | R12       | R13       | R14       | R15        |

| LOD Bit16         | LOD Bit17 | LOD Bit18 | LOD Bit19 | LOD Bit20 | LOD Bit21 | LOD Bit22 | LOD Bit23 | LOD Bit24 | LOD Bit25 | LOD Bit26 | LOD Bit27 | LOD Bit28 | LOD Bit29 | LOD Bit30 | LOD Bit31  |

| G0                | G1        | G2        | G3        | G4        | G5        | G6        | G7        | G8        | G9        | G10       | G11       | G12       | G13       | G14       | G15<br>MSB |

| LOD Bit32         | LOD Bit33 | LOD Bit34 | LOD Bit35 | LOD Bit36 | LOD Bit37 | LOD Bit38 | LOD Bit39 | LOD Bit40 | LOD Bit41 | LOD Bit42 | LOD Bit43 | LOD Bit44 | LOD Bit45 | LOD Bit46 | LOD Bit47  |

| BO                | B1        | B2        | B3        | B4        | B5        | B6        | B7        | B8        | B9        | B10       | B11       | B12       | B13       | B14       | B15        |

#### 8.3.5.3.2 Read LED Open Information

The LOD readback function must be enabled before read LED open information. This function is enabled by LOD\_LSD\_RB (see FC3 for more details).

⊠ 8-10 shows the steps to read LED open information. Wait at least one sub-period time between Step2 and Step3 command.

### 図 8-10. Steps to Read LED Open Information

#### 8.3.5.3.3 LED Open Caterpillar Removal

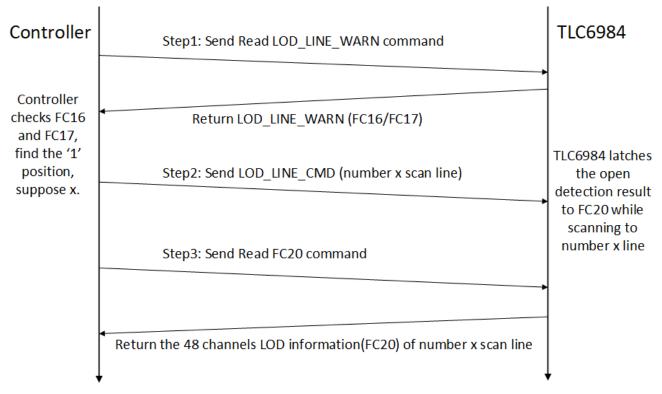

⊠ 8-11 shows the caterpillar issue caused by open LED. Suppose the LED0-1 is an open LED. When line0 is chosen and the OUT1 is turned on, the OUT1 voltage is forced to approach to VLED because of the broken path of the current source. However, the voltage of the un-chosen lines are below the Vclamp which is much lower than VLED, causing all LEDs which connect to the channel OUT1, light unwanted.

🛛 8-11. LED Open Caterpillar

The TLC6984 implements circuits that can eliminate the caterpillar issue caused by open LEDs. The LED open caterpillar removal function is configured by LOD\_RM\_EN (see FC0 for more details). When LOD\_RM\_EN is set to 1b, the caterpillar removal function is enabled. The corresponding channel OUTn is turned off when scanning to line with open LED, The caterpillar issue is eliminated until device resets or LOD\_RM\_EN is set to 0b.

The internal caterpillar elimination circuit can handle a maximum of three lines that have open LEDs fault condition. If there are open LEDs located in three or fewer lines, the TLC6984 is able to handle the open LEDs all in these lines. If there are open LEDs in more than three lines, the caterpillar issue is solved for the lines where the first three open LEDs were detected, but the open LEDs in the fourth and subsequent lines still cause the caterpillar issue.

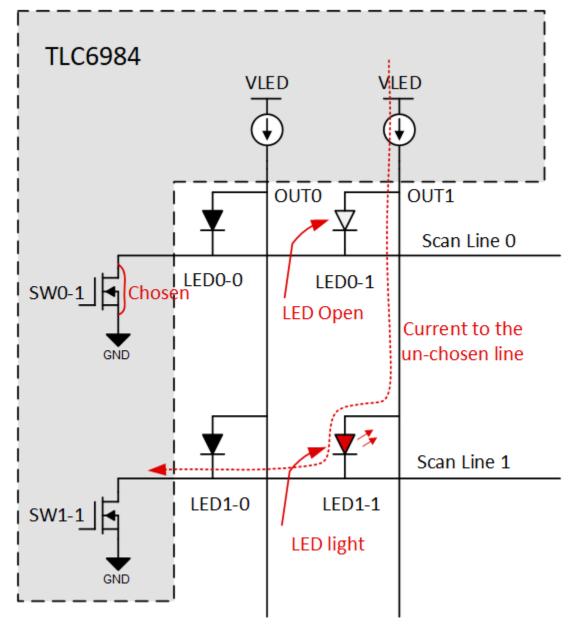

### 8.3.5.4 LED Short and Weak Short Circuitry Detection and Removal

### 8.3.5.4.1 LED Short and Weak Short Detection

The LED short detection (LSD) function detects faults caused by a short circuit in any LED. This function was realized by comparing the OUTn voltage to the LSD threshold voltage. If the OUTn voltage is lower than the

threshold voltage, the corresponding output LSD bit is set to 1 to indicate an short LED, otherwise, the output of that LSD bit is 0. LSD data output by the detection circuit are valid only during the OUTn turning on period.

LSD weak short can be detected by adjusting threshold voltage, which level is set by LSDVTH\_R/LSDVTH\_G/ LSDVTH\_B (See FC3 for more details).

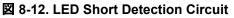

☑ 8-12 shows the equivalent circuit of LED short detection.

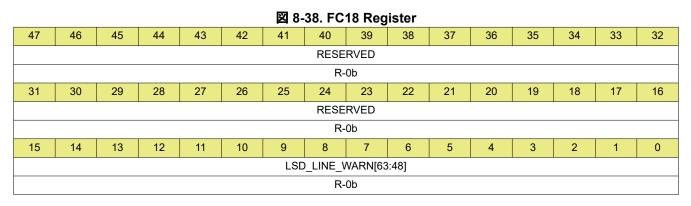

The LED short detection function records the position of the short LED, which contains the scan line order and relevant channel number. The scan line order is stored LSD\_LINE\_WARN register (see FC18 and FC19 for more details), and the channel number is latched into the internal 48-bit LSD data register (see FC21 for more details) at the end of each segment.  $\boxtimes$  8-13 shows the bit arrangement of the LSD data register.

| LSB       |           |           |           |           |           |           |           |           |           |           |           |           |           |           |           |

|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| LSD Bit0  | LSD Bit1  | LSD Bit2  | LSD Bit3  | LSD Bit4  | LSD Bit5  | LSD Bit6  | LSD Bit7  | LSD Bit8  | LSD Bit9  | LSD Bit10 | LSD Bit11 | LSD Bit12 | LSD Bit13 | LSD Bit14 | LSD Bit15 |

| RO        | R1        | R2        | R3        | R4        | R5        | R6        | R7        | R8        | R9        | R10       | R11       | R12       | R13       | R14       | R15       |

|           |           |           |           |           |           |           |           |           |           |           |           |           |           |           |           |

| LSD Bit16 | LSD Bit17 | LSD Bit18 | LSD Bit19 | LSD Bit20 | LSD Bit21 | LSD Bit22 | LSD Bit23 | LSD Bit24 | LSD Bit25 | LSD Bit26 | LSD Bit27 | LSD Bit28 | LSD Bit29 | LSD Bit30 | LSD Bit31 |

| G0        | G1        | G2        | G3        | G4        | G5        | G6        | G7        | G8        | G9        | G10       | G11       | G12       | G13       | G14       | G15       |

|           |           |           |           |           |           |           |           |           |           |           |           |           |           |           | MSB       |

| LSD Bit32 | LSD Bit33 | LSD Bit34 | LSD Bit35 | LSD Bit36 | LSD Bit37 | LSD Bit38 | LSD Bit39 | LSD Bit40 | LSD Bit41 | LSD Bit42 | LSD Bit43 | LSD Bit44 | LSD Bit45 | LSD Bit46 | LSD Bit47 |

| BO        | B1        | B2        | B3        | B4        | B5        | B6        | B7        | B8        | B9        | B10       | B11       | B12       | B13       | B14       | B15       |

### **2**8-13. Bit Arrangement in the LSD Data Register

#### 8.3.5.4.2 Read LED Short Information

The LSD readback function must be enabled before reading LED Short information. This function is enabled by LOD\_LSD\_RB (see FC3 for more details).

⊠ 8-14 shows the steps to read LED Short information. Wait at least one sub-period time between Step2 and Step3 command.

### **図** 8-14. Steps to Read LED Short Information

#### 8.3.5.4.3 LSD Caterpillar Removal

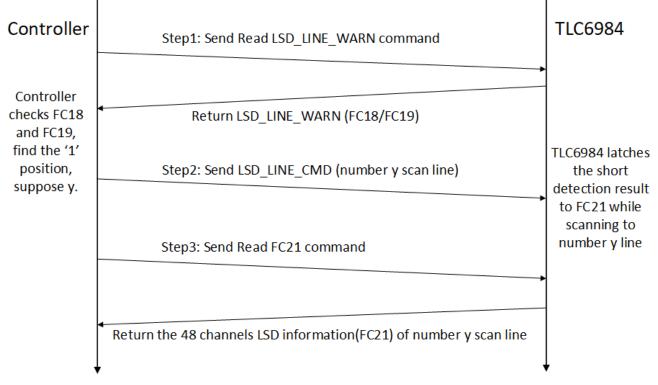

⊠ 8-15 shows the LSD caterpillar issue caused by short LED. Suppose the LED0-1 is a short LED. When it scans to the line1 and the OUT1 is turned off, the OUT1 voltage is the same with scan line0 voltage because of the short path of the LED0-1. At this time, there is a current path from the line0 to the GND through the LED1-1 and SW1-1, which causes LED1-1 light unwanted.

The TLC6984 device implements internal circuits that can eliminate the caterpillar issue by short LEDs. As is shown in  $\boxtimes$  8-15, the LED short caterpillar is caused by the voltage of the Vclamp on the line. So it can be solved by adjusting the LSD\_RM\_EN (see FC3 for more details) to let the voltage drop of the LED1-1 be smaller than LED forward voltage.

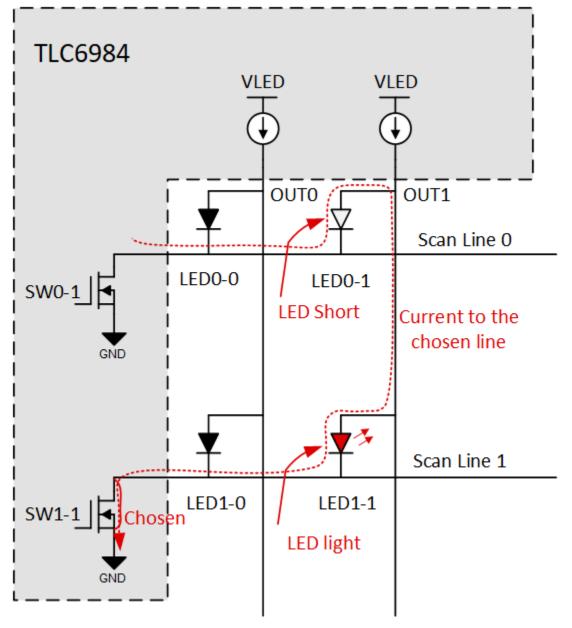

### 8.4 Device Functional Modes

The device functional modes are shown in  $\boxtimes$  8-16.

# 図 8-16. Functional Modes

- **Initialization:** the device enters into Initialization when Vcc goes down to UVLO voltage. In this mode, all the registers are reset. Entry can also be from any state.

- **Normal:** the device enters the normal mode when Vcc is higher than UVLO threshold. The display process is shown as below in normal mode.

- **Power saving:** the device automatically enters and gets out from the power save mode when it detects the condition PSin and PSout. In this mode, all channels turn off. PSin: after the device detects that the display data of the next frame all equal to zero, it enters to power save mode when the VSYNC comes. PSout: after the device detects that there is non-zero display data of the next frame, it gets out from power save mode immediately.

- IREF Resistor Short Protection: the device automatically enters and gets out from the IREF resistor short protection mode when it detects the condition ISPin and ISPout. In this mode, all channels turn off. ISPin: the device detects that the reference voltage is smaller than 0.195 V ISPout: the device detects that the reference voltage is larger than 0.325 V.

- **Thermal Shutdown:** the device automatically enters and gets out from the thermal shutdown mode when it detects the condition TSDin and TSDout. In this mode, all channels turn off. TSDin: the device detects that the junction temperature exceeds 170° C TSDout: the device detects that the junction temperature is below 155° C.

### 8.5 Continuous Clock Series Interface

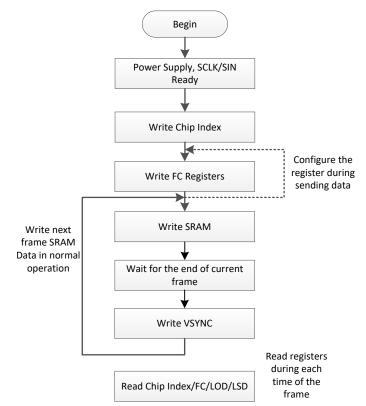

The continuous clock series interface (CCSI) provides access to the programmable functions and registers, SRAM data of the device. The interface contains two input digital pins. the pins are the serial data input (SIN) and serial clock (SCLK). Moreover, there is an another wire called serial data output (SOUT) as the output digital signal of the device. The SIN is set to HIGH when device is in idle status and the SCLK must be existent and continuous all the time considering as the clock source of internal Frequency Multiplier, the SOUT is used to transmit the data or read the data of internal registers.

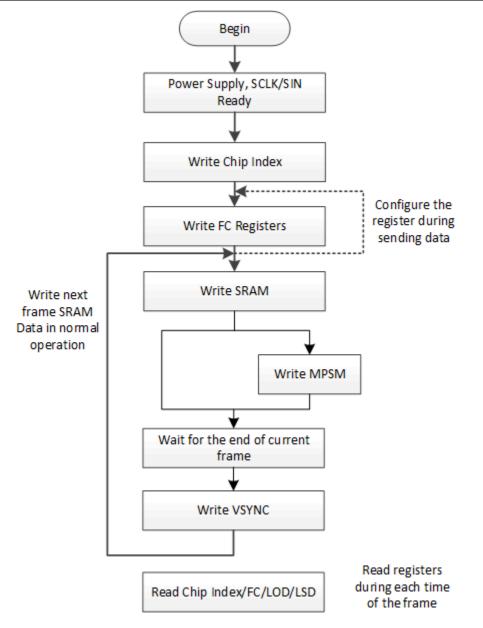

This protocol can support up to 32 devices cascaded in a data chain. The devices receive the chip index command after power up. The chip index command configures addresses of the devices from 0x00 up to 0x1F according to the sequence that receives the command. Then the controller can communicate with all the devices through the broadcast way or particular device through non-broadcast way.

The broadcast is mainly used to transmit function control commands. All the devices in a data chain receive the same data in this way. The non-broadcast is mainly used to transmit function control commands or display data, and each device receives its own data in this way. These two ways are distinguished by the command identification.

Dual-edge is designed to support more devices cascaded in a data chain.

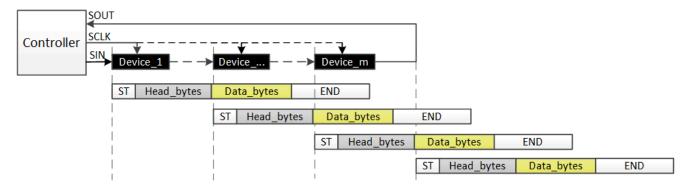

### 8.5.1 Data Validity

The data on DIN wire must be stable at rising and falling edges of the SCLK in dual-edge transmission.

### 8.5.2 CCSI Frame Format

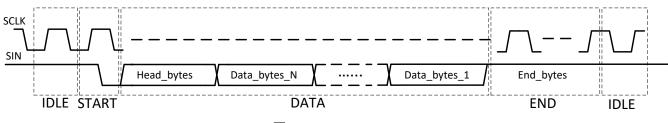

☑ 8-17 defines the format of the command and data transimission. There are four states in one frame.

- IDLE: SCLK is always existent and continuous, and DIN is always HIGH.

- **START:** DIN changes from HIGH to LOW after the IDLE states.

- DATA:

- Head\_bytes: command identifier that contains one 16-bit data and one check bit. It can be WRITE COMMAND ID or READ COMMAND ID (see Register Maps for more details).

- Data\_bytes\_N: The N<sup>th</sup> data-bytes, contains 3 × 17-bit data, each 17-bit data contains one 16-bit data and one check bit. N is the number of devices cascaded in a data chain.

- END: the device recognizes continuous 18-bit HIGH on DIN, then returns to IDLE state.

- CHECK BIT: the check bit (17<sup>th</sup> bit) value is the NOT of 16<sup>th</sup> bit value, to avoid continuous 18-bit HIGH (to distinguish with END).

## 🛛 8-17. CCSI Frame

The IDLE state is not the necessary, that means the START state of next frame can connect to the END state of current frame.

#### 8.5.3 Write Command

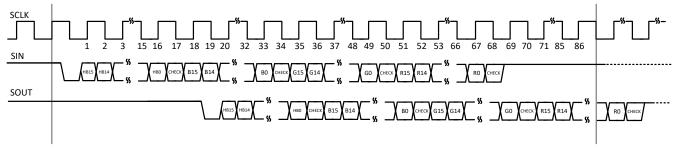

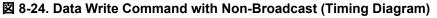

Take m devices cascaded in a data chain for example.

### 8.5.3.1 Chip Index Write Command

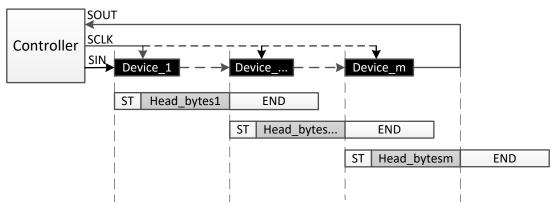

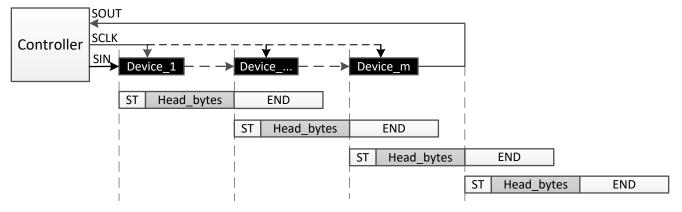

The chip index is used to set the identification of the device cascaded in a data chain. When the first device receives the chip index command Head\_bytes1, it sets the current address to 00h and meanwhile change the chip index command Head\_bytes2, then sends to the next device. When the device receives the Head\_bytes2, it sets the address to 01h and meanwhile changes the chip index command Head\_bytes3, then sends to the next device, likewise, all the cascaded devices get their unique identifications.

🛛 8-18. Chip Index Write Command

## 8.5.3.2 VSYNC Write Command

The VSYNC is used to sync the display of each frame for the devices in a cascaded chain. The VSYNC is a write-only command. The devices receive VSYNC command one time from the controller in each frame, and the VSYNC command must be active for all devices at the same time.

Because some devices receive the command earlier in the data chain, they must wait until the last device receives the command, then all the devices are active at that time. To realize such function, each device must know its delay time from receiving VSYNC command to enabling VSYNC. The device uses some register bits to restore the device number in a data chain. This number minuses the device identification, and the result is the delay time of the device.

Because the sync function has been done by the device, the controller must only send the VSYNC command to the first device in a data chain.

**図 8-19. VSYNC Write Command**

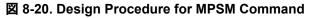

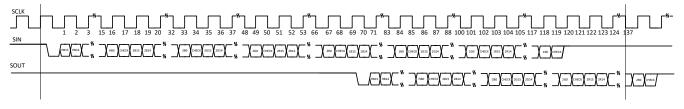

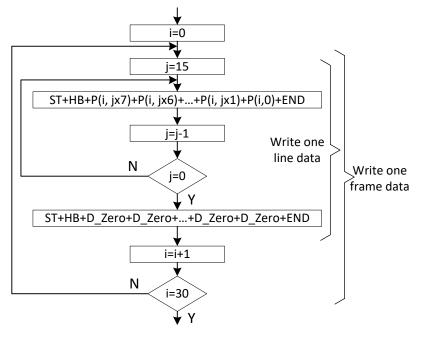

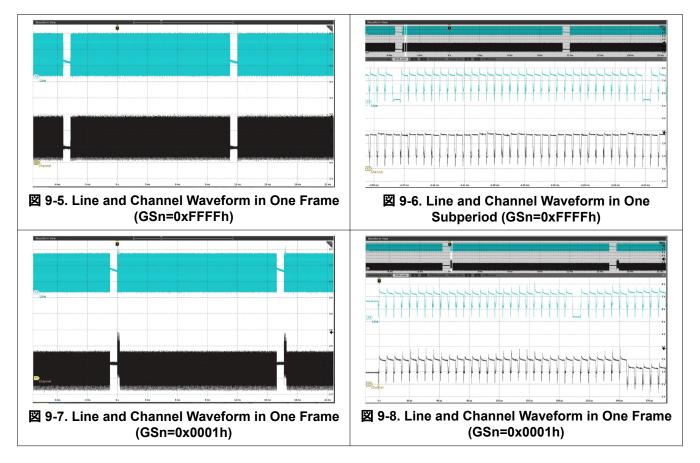

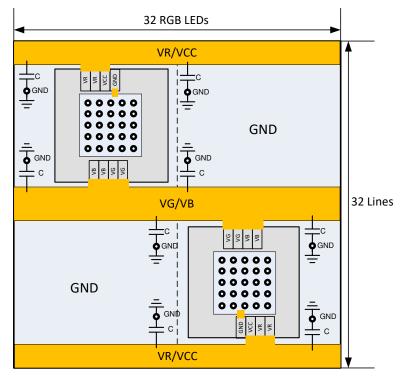

### 8.5.3.3 MPSM Write Command