TMUX582F-SEP JAJSO44A - JUNE 2023 - REVISED JULY 2024

# TMUX582F-SEP 宇宙用強化プラスチックに封止した可変フォルト スレッシ ョルド付き、±60V 保護、ラッチアップ耐性、8:1マルチプレクサ

# 1 特長

- 放射線耐性を強化

- シングル イベント ラッチアップ (SEL) 耐性:125℃で 43MeV-cm2/mg まで

- 30krad(Si) まで ELDRS フリー

- すべてのウェハーロットについて、20krad(Si)までの 吸収線量 (TID) RLAT

- 30krad(Si) まで吸収線量 (TID) 特性を評価済み

- 宇宙向け強化プラスチック

- 電源電圧範囲:8V~22V または ±5V~±16.5V

- 電源オフおよび過電圧保護を内蔵1

- ソースと電源間、またはドレイン間で最大 85V の過 電圧耐性

- 最大 ±60V の過電圧および電源オフ

- 最大 ±60V のコールドスペアに対応

- 障害スレッショルド (Vfp および Vfn) を 5V から電 源に調整可能

- 障害が発生したチャネルを示す割り込みフラグフィ

- 障害が発生していないチャネルは低リーク電流で 動作を維持

- ラッチアップ耐性構造

- 100pA の標準的なリーク電流、3.5pF の静電容量、 1% の Ron 平坦度で高精度を実現

- 動作温度範囲:-55℃~+125℃

- 管理されたベースライン

- 金 ワイヤ、NiPdAu リード仕上げ

- 単一のアセンブリ/テスト施設

- 単一の製造施設

- 長期にわたる製品ライフ サイクル

- 製品のトレーサビリティ

- モールドコンパウンドの改良による低いガス放出

- 小型で業界標準の TSSOP-20 パッケージ

# 2 アプリケーション

- 低軌道 (LEO) 衛星用途

- リモート インターフェイス ユニット (RIU)

- リモート テレメトリ ユニット (RTU)

- 宇宙のシステム監視

- ラッチアップおよび過電圧検出

- パワーアップ シーケンシング保護

- オンボードデータ処理用の衛星テレメトリおよびテレコ

• センサ データ アクイジション

# 3 概要

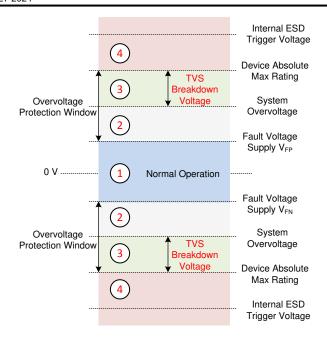

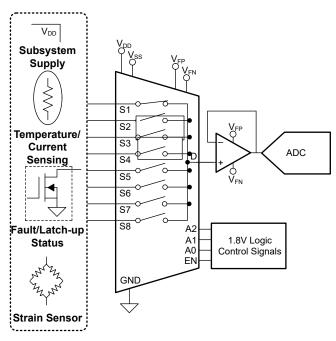

TMUX582F-SEP は、最新の8:1マルチプレクサで、シ ングルエンドと差動の両方の動作に適しています。このラ ッチアップ耐性デバイスは、最大 ±60V の堅牢な過電圧 保護を実現し、過酷な宇宙環境に最適です。さらに、この 保護機能は電源オン、電源オフ、フローティングの各電源 条件でも動作します。

過電圧または低電圧イベントなどの障害が発生すると、問 題のチャネルがオフになり、Sxピンは高インピーダンスに なります。この障害が発生しているチャネルを選択すると、 ドレイン (D) が超過したフォルト レール (Vfp または Vfn) にプルされます。障害が発生していない他のすべての Sx ピンは、引き続き正常に動作します。通常動作時、ソース (Sx) が Vfp または Vfn を超えない場合、スイッチは低リー ク、低静電容量、超フラットなオン抵抗で動作します。これ により、最小限の歪みで高性能のシグナル インテグリティ を実現できます。

TMUX582F-SEP は、システム監視から電源オン シーケ ンス保護、高精度のフロント エンド データ アクイジション に至るまで、ほぼすべてのアプリケーションに対応できる 柔軟性を備えた、障害保護機能搭載の CMOS マルチプ レクサです。

#### パッケージ情報

| 部品番号         | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |

|--------------|----------------------|--------------------------|

| TMUX582F-SEP | PW (TSSOP, 20)       | 6.5mm × 6.4mm            |

- 詳細については、セクション 12 を参照してください。

- パッケージ サイズ (長さ×幅) は公称値であり、該当する場合はピ ンも含まれます。

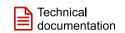

概略回路図

1 このマルチプレクサのアプリケーション シナリオは、通常の動作条件において最大電源電圧でバイアスが印加されることを想定しており、そのよう に照射されます。デバイスは、障害保護が正常であるかどうかを判定するために事後テストされます。詳細については、バイアス方式の放射線レ ポートを参照してください。

# **Table of Contents**

| 1 | 特長1                                            |

|---|------------------------------------------------|

| 2 | アプリケーション1                                      |

| 3 | 概要1                                            |

| 4 | Pin Configuration and Functions3               |

| 5 | Specifications5                                |

|   | 5.1 Absolute Maximum Ratings5                  |

|   | 5.2 ESD Ratings                                |

|   | 5.3 Recommended Operating Conditions5          |

|   | 5.4 Thermal Information6                       |

|   | 5.5 Electrical Characteristics (Global)6       |

|   | 5.6 Dual Supply: Electrical Characteristics    |

|   | 5.7 Single Supply: Electrical Characteristics9 |

|   | 5.8 Typical Characteristics11                  |

| 6 | Parameter Measurement Information14            |

|   | 6.1 On-Resistance                              |

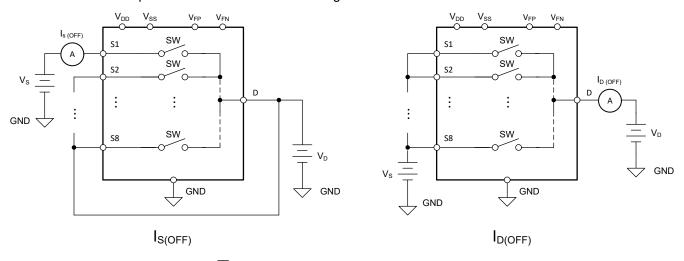

|   | 6.2 Off-Leakage Current14                      |

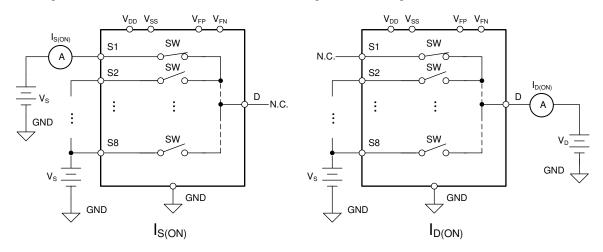

|   | 6.3 On-Leakage Current                         |

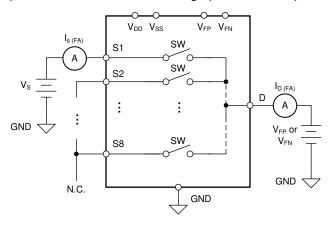

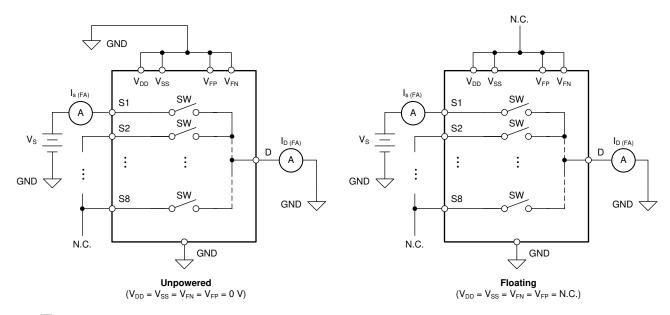

|   | 6.4 Input and Output Leakage Current Under     |

|   | Overvoltage Fault15                            |

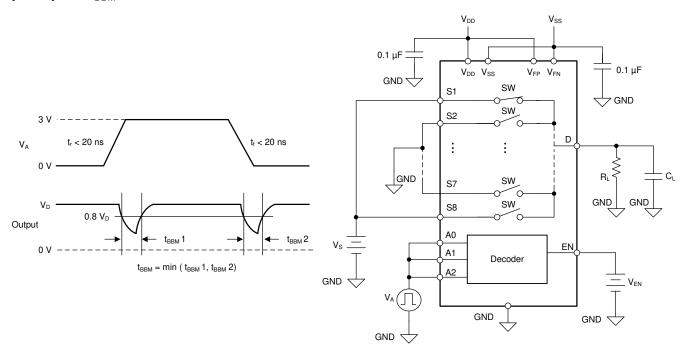

|   | 6.5 Break-Before-Make Delay16                  |

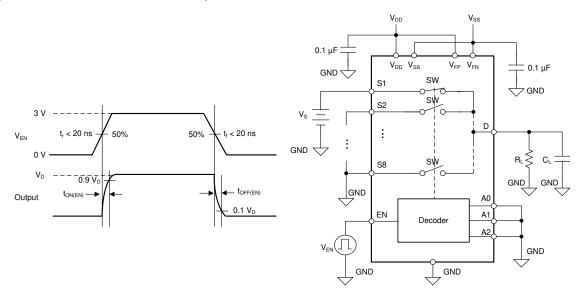

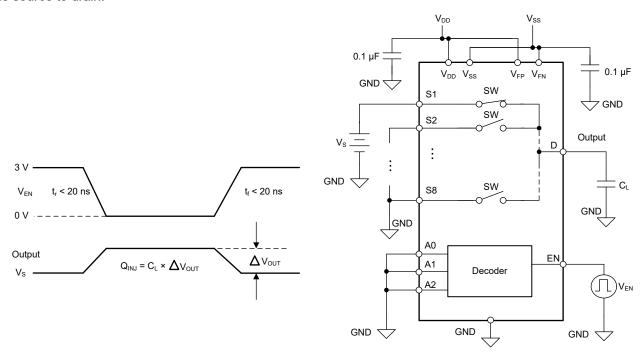

|   | 6.6 Enable Delay Time17                        |

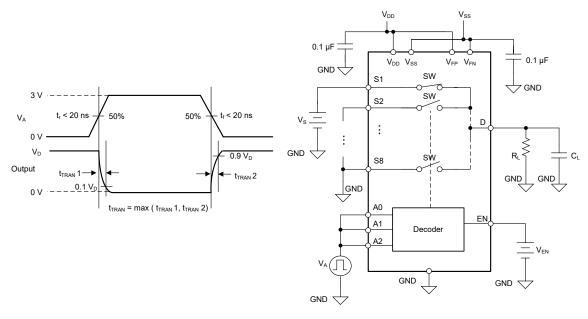

|   | 6.7 Transition Time                            |

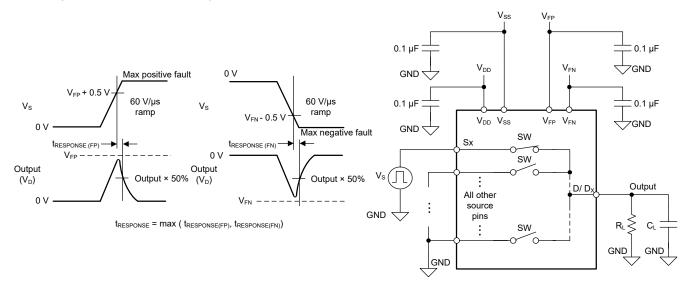

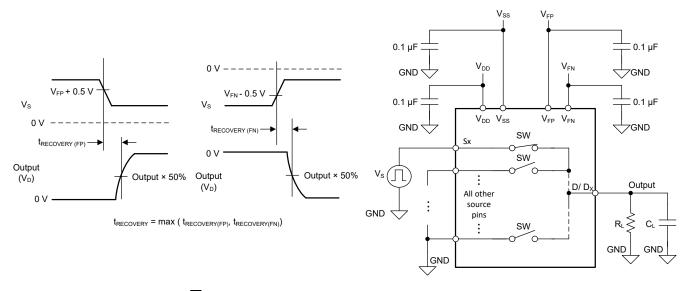

|   | 6.8 Fault Response Time18                      |

|   | 6.9 Fault Recovery Time18                      |

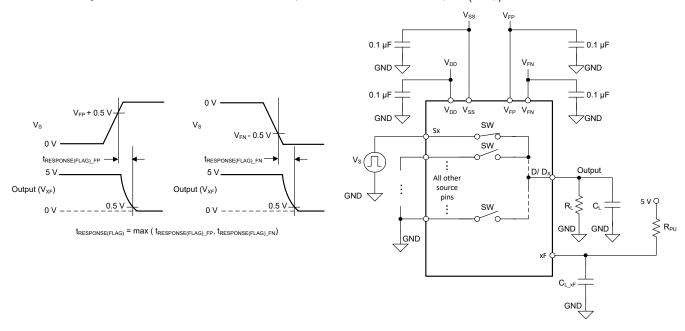

|   | 6.10 Fault Flag Response Time19                |

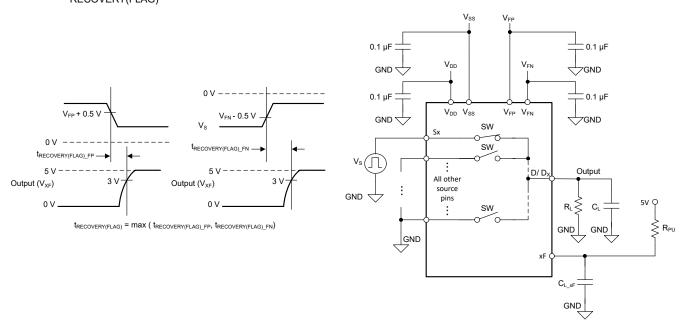

|   | 6.11 Fault Flag Recovery Time                  |

| 6. 12 Charge injection                  | ∠∪               |

|-----------------------------------------|------------------|

| 6.13 Off Isolation                      | 21               |

| 6.14 Crosstalk                          | 21               |

| 6.15 Bandwidth                          | 22               |

| 6.16 THD + Noise                        | 22               |

| 7 Truth Table                           |                  |

| 8 Detailed Description                  | 24               |

| 8.1 Functional Block Diagram            |                  |

| 8.2 Feature Description                 |                  |

| 8.3 Device Functional Modes             | <mark>29</mark>  |

| 9 Application and Implementation        | 30               |

| 9.1 Application Information             | 30               |

| 9.2 Typical Application                 | 30               |

| 9.3 Power Supply Recommendations        | 31               |

| 9.4 Layout                              |                  |

| 10 Device and Documentation Support     | 3 <mark>3</mark> |

| 10.1 Documentation Support              | <mark>33</mark>  |

| 10.2ドキュメントの更新通知を受け取る方法                  | 33               |

| 10.3 サポート・リソース                          | 33               |

| 10.4 Trademarks                         | 33               |

| 10.5 静電気放電に関する注意事項                      | 33               |

| 10.6 用語集                                | 33               |

| 11 Revision History                     | 33               |

| 12 Mechanical, Packaging, and Orderable |                  |

| Information                             | 33               |

|                                         |                  |

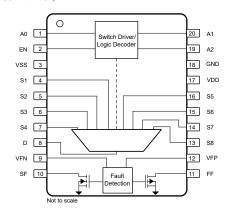

# 4 Pin Configuration and Functions

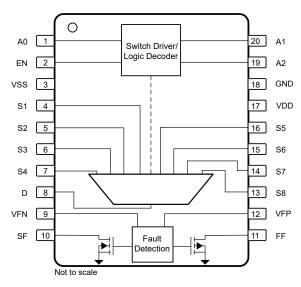

図 4-1. PW Package, 20-Pin TSSOP (Top View)

表 4-1. Pin Functions: TMUX582F-SEP

| F               | PIN | TYPE(1) | DECORPTION                                                                                                                                                                                                                                                                                                                                   |

|-----------------|-----|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME            | NO. | IYPE(") | DESCRIPTION                                                                                                                                                                                                                                                                                                                                  |

| A0              | 1   | ı       | Logic control input address 0 (A0). The pin has a weak internal pull-down. This pin can also be used together with the specific fault pin (SF) to indicate which input is under fault.                                                                                                                                                       |

| EN              | 2   | I       | Active high digital enable (EN) pin. The pin has a weak internal pull-down. The device is disabled and all switches become high impedance when the pin is low. When the pin is high, the Ax logic inputs determine individual switch states.                                                                                                 |

| V <sub>SS</sub> | 3   | Р       | Negative power supply. This pin is the most negative power-supply potential. In single-supply applications, this pin can be connected to ground. For reliable operation, connect a decoupling capacitor ranging from 0.1µF to 10µF between V <sub>SS</sub> and GND.                                                                          |

| S1              | 4   | I/O     | Overvoltage protected source pin 1. Can be an input or output.                                                                                                                                                                                                                                                                               |

| S2              | 5   | I/O     | Overvoltage protected source pin 2. Can be an input or output.                                                                                                                                                                                                                                                                               |

| S3              | 6   | I/O     | Overvoltage protected source pin 3. Can be an input or output.                                                                                                                                                                                                                                                                               |

| S4              | 7   | I/O     | Overvoltage protected source pin 4. Can be an input or output.                                                                                                                                                                                                                                                                               |

| D               | 8   | I/O     | Drain pin. Can be an input or output. The drain pin is not overvoltage protected and shall remain within the recommended operating range.                                                                                                                                                                                                    |

| V <sub>FN</sub> | 9   | Р       | Negative fault voltage supply that determines the overvoltage protection triggering threshold on the negative side. Connect to $V_{SS}$ if the triggering threshold is to be the same as the device's negative supply. For reliable operation, connect a decoupling capacitor ranging from $0.1\mu F$ to $10\mu F$ between $V_{FN}$ and GND. |

| SF              | 10  | 0       | Specific fault flag. This pin is an open drain output and is asserted low when overvoltage condition is detected on a specific pin, depending on the state of A0, A1, and A2, as shown in $\frac{1}{8}$ 7-1. Connect this pin to an external supply (1.8V to 5.5V) through a 1kΩ pull-up resistor.                                           |

| FF              | 11  | 0       | General fault flag. This pin is an open drain output and is asserted low when overvoltage condition is detected on any of the source (Sx) input pins. Connect this pin to an external supply (1.8V to 5.5V) through a $1k\Omega$ pull-up resistor.                                                                                           |

| $V_{FP}$        | 12  | Р       | Positive fault voltage supply that determines the overvoltage protection triggering threshold on the positive side. Connect to $V_{DD}$ if the triggering threshold is to be the same as the device's positive supply. For reliable operation, connect a decoupling capacitor ranging from $0.1\mu F$ to $10\mu F$ between $V_{FP}$ and GND. |

| S8              | 13  | I/O     | Overvoltage protected source pin 8. Can be an input or output.                                                                                                                                                                                                                                                                               |

| S7              | 14  | I/O     | Overvoltage protected source pin 7. Can be an input or output.                                                                                                                                                                                                                                                                               |

| S6              | 15  | I/O     | Overvoltage protected source pin 6. Can be an input or output.                                                                                                                                                                                                                                                                               |

| S5              | 16  | I/O     | Overvoltage protected source pin 5. Can be an input or output.                                                                                                                                                                                                                                                                               |

| V <sub>DD</sub> | 17  | Р       | Positive power supply. This pin is the most positive power-supply potential. For reliable operation, connect a decoupling capacitor ranging from 0.1µF to 10µF between V <sub>DD</sub> and GND.                                                                                                                                              |

| GND             | 18  | Р       | Ground (0V) reference                                                                                                                                                                                                                                                                                                                        |

| A2              | 19  | I       | Logic control input address 2 (A2). The pin has a weak internal pull-down. This pin can also be used together with the specific fault pin (SF) to indicate which input is under fault.                                                                                                                                                       |

# 表 4-1. Pin Functions: TMUX582F-SEP (続き)

| P<br>NAME | PIN           NAME         NO.           A1         20           I |  | DESCRIPTION                                                                                                                                                                            |

|-----------|--------------------------------------------------------------------|--|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1        | 20                                                                 |  | Logic control input address 1 (A1). The pin has a weak internal pull-down. This pin can also be used together with the specific fault pin (SF) to indicate which input is under fault. |

(1) I = input, O = output, I/O = input and output, P = power

Copyright © 2024 Texas Instruments Incorporated

English Data Sheet: SCDS460

4

Product Folder Links: TMUX582F-SEP

# **5 Specifications**

# 5.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                                         |                                                                 | MIN                                   | MAX                                   | UNIT |

|-----------------------------------------|-----------------------------------------------------------------|---------------------------------------|---------------------------------------|------|

| V <sub>DD</sub> to V <sub>SS</sub>      |                                                                 |                                       | 38                                    | V    |

| V <sub>DD</sub> to GND                  | Supply voltage                                                  | -0.3                                  | 28                                    | V    |

| V <sub>SS</sub> to GND                  |                                                                 | -18                                   | 0.3                                   | V    |

| V <sub>FP</sub> to GND                  | Positive fault clamping voltage                                 | -0.3                                  | V <sub>DD</sub> + 0.3                 | V    |

| V <sub>FN</sub> to GND                  | Negative fault clamping voltage                                 | V <sub>SS</sub> - 0.3                 | 0.3                                   | V    |

| V <sub>S</sub> to GND                   | Source input pin (Sx) voltage to GND                            | -65                                   | 65                                    | V    |

| V <sub>S</sub> to V <sub>DD</sub>       | Source input pin (Sx) voltage to V <sub>DD</sub>                | -90                                   |                                       | V    |

| V <sub>S</sub> to V <sub>SS</sub>       | Source input pin (Sx) voltage to V <sub>SS</sub>                |                                       | 90                                    | V    |

| $V_D$                                   | Drain pin (D or Dx) voltage                                     | V <sub>FN</sub> -0.7                  | V <sub>FP</sub> +0.7                  | V    |

| V <sub>SEL</sub> or V <sub>EN</sub>     | Logic control input pin voltage (EN, A0, A1, A2) <sup>(2)</sup> | GND -0.7                              | 48                                    | V    |

| V <sub>DIG_OUT</sub>                    | Digital output pin (SF, FF) voltage <sup>(2)</sup>              | GND -0.7                              | 6                                     | V    |

| I <sub>SEL</sub> or I <sub>EN</sub>     | Logic control input pin current (EN, A0, A1, A2) <sup>(2)</sup> | -30                                   | 30                                    | mA   |

| I <sub>DIG_OUT</sub>                    | Digital output pin (SF, FF) current <sup>(2)</sup>              | -10                                   | 10                                    | mA   |

| I <sub>S</sub> or I <sub>D (CONT)</sub> | Source or drain continuous current (Sx or D)                    | I <sub>DC</sub> ± 10 % <sup>(3)</sup> | I <sub>DC</sub> ± 10 % <sup>(3)</sup> | mA   |

| T <sub>stg</sub>                        | Storage temperature                                             | -65                                   | 150                                   | °C   |

| T <sub>A</sub>                          | Ambient temperature                                             | -55                                   | 150                                   | °C   |

| TJ                                      | Junction temperature                                            |                                       | 150                                   | °C   |

| P <sub>tot</sub> <sup>(4)</sup>         | Total power dissipation                                         |                                       | 800                                   | mW   |

<sup>(1)</sup> Operation outside the Absolute Maximum Rating may cause permanent device damage. Absolute Maximum Rating do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Condition. If used outside the Recommended Operating Condition but within the Absolute Maximum Rating, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

- (2) Stresses have to be kept at or below both voltage and current ratings at all time.

- (3) Refer to Recommended Operating Conditions for I<sub>DC</sub> ratings.

- (4) P<sub>tot</sub> derates linearly above T<sub>A</sub> = 70°C by 12.0 mW/°C

#### 5.2 ESD Ratings

|                    |           |                                                                                                          | VALUE | UNIT |

|--------------------|-----------|----------------------------------------------------------------------------------------------------------|-------|------|

| V                  |           | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>                                        | ±3500 | V    |

| V <sub>(ESD)</sub> | discharge | Charged device model (CDM), per JEDEC specification JESD22-C101 or ANSI/ESDA/JEDEC JS-002 <sup>(2)</sup> | ±750  | V    |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# **5.3 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)

|                                       |                                               | MIN             | NOM MAX         | UNIT |

|---------------------------------------|-----------------------------------------------|-----------------|-----------------|------|

| V <sub>DD</sub> – V <sub>SS</sub> (1) | Power supply voltage differential             | 8               | 33              | V    |

| $V_{DD}$                              | Positive power supply voltage                 | 5               | 22              | V    |

| V <sub>FP</sub>                       | Positive fault clamping voltage               | 3               | $V_{DD}$        | V    |

| V <sub>FN</sub>                       | Negative fault clamping voltage               | V <sub>SS</sub> | 0               | V    |

| Vs                                    | Source pin (Sx) voltage (non-fault condition) | $V_{FN}$        | V <sub>FP</sub> | V    |

| V <sub>S_FAULT</sub> (3)              | Source pin (Sx) voltage (fault condition)     | -60             | 60              | V    |

# 5.3 Recommended Operating Conditions (続き)

over operating free-air temperature range (unless otherwise noted)

|                                                  |                                                                                |                                                                                | MIN      | NOM MAX         | UNIT |

|--------------------------------------------------|--------------------------------------------------------------------------------|--------------------------------------------------------------------------------|----------|-----------------|------|

| V <sub>S</sub> to V <sub>DD</sub> <sup>(2)</sup> | Source pin (Sx) voltage to V <sub>DD</sub> or V <sub>D</sub> (fault condition) | Source pin (Sx) voltage to V <sub>DD</sub> or V <sub>D</sub> (fault condition) | -85      |                 | V    |

| V <sub>S</sub> to V <sub>SS</sub> <sup>(2)</sup> | Source pin (Sx) voltage to V <sub>SS</sub> or V <sub>D</sub> (fault condition) | Source pin (Sx) voltage to $V_{SS}$ or $V_D$ (fault condition)                 |          | 85              | 5 V  |

| V <sub>D</sub>                                   | Drain pin (D, Dx) voltage                                                      |                                                                                | $V_{FN}$ | V <sub>FI</sub> | V    |

| V <sub>SEL</sub> of V <sub>EN</sub>              | Logic control input pin voltage (EN, A0, A1, A2)                               | Logic control input pin voltage (EN, A0, A1, A2)                               |          | 22              | 2 V  |

| V <sub>DIG_OUT</sub>                             | Digital output pin (SF, FF) voltage                                            |                                                                                | 0        | 5.5             | 5 V  |

| T <sub>A</sub>                                   | Ambient temperature                                                            | Ambient temperature                                                            |          | 125             | °C   |

|                                                  |                                                                                | T <sub>A</sub> = 25°C                                                          |          | (               | mA   |

| IDC <sup>(3)</sup>                               | Continuous current through switch, TSSOP package                               | T <sub>A</sub> = 85°C                                                          |          | 6.5             | mA   |

|                                                  |                                                                                | T <sub>A</sub> = 150°C                                                         |          | ;               | mA   |

<sup>(1)</sup>

# **5.4 Thermal Information**

|                       | Junction-to-board thermal resistance         | TMUX582F-SEP |      |

|-----------------------|----------------------------------------------|--------------|------|

|                       |                                              | PW (TSSOP)   | UNIT |

|                       |                                              | 20 PINS      |      |

| R <sub>0JA</sub>      | Junction-to-ambient thermal resistance       | 84.3         | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 22.7         | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 37.3         | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 1.0          | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 36.7         | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

# 5.5 Electrical Characteristics (Global)

at T<sub>A</sub> = 25°C (unless otherwise noted)

|                       | PARAMETER                                                                          | TEST CONDITIONS                            | T <sub>A</sub>  | MIN TYP MA | X UNIT |

|-----------------------|------------------------------------------------------------------------------------|--------------------------------------------|-----------------|------------|--------|

| ANALOG SV             | VITCH                                                                              | ·                                          |                 | <u> </u>   | _      |

| V <sub>T</sub>        | Threshold voltage for fault detector                                               |                                            | -55°C to +125°C | 0.7        | V      |

| DIGITAL INP           | UT/ OUTPUT                                                                         |                                            |                 |            |        |

| V <sub>IH</sub>       | High-level input voltage                                                           | EN, Ax pins                                | -55°C to +125°C | 1.3        | 22 V   |

| V <sub>IL</sub>       | Low-level input voltage                                                            | EN, Ax pins                                | -55°C to +125°C | 0 0        | .8 V   |

| V <sub>OL(FLAG)</sub> | Low-level output voltage                                                           | FF and SF pins, I <sub>O</sub> = 5mA       | -55°C to +125°C | 0.1        | V      |

| POWER SUF             | PPLY                                                                               |                                            |                 | 1          | '      |

| V <sub>UVLO</sub>     | Undervoltage lockout (UVLO) threshold voltage (V <sub>DD</sub> – V <sub>SS</sub> ) | single supply configuration only           | -55°C to +125°C | 6          | V      |

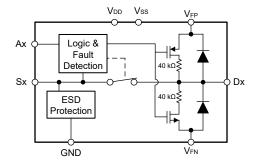

| R <sub>D(OVP)</sub>   | Drain resistance to fault rail durin                                               | g overvoltage event on selected source pin | 25°C            | 40         | kΩ     |

Product Folder Links: TMUX582F-SEP

資料に関するフィードバック (ご意見やお問い合わせ) を送信

Copyright © 2024 Texas Instruments Incorporated

$V_{DD}$  and  $V_{SS}$  can be any value as long as  $8V \le (V_{DD} - V_{SS}) \le 33V$ . Under a fault condition, the potential difference between source pin (Sx) and supply pins ( $V_{DD}$  and  $V_{SS}$ .) or source pin (Sx) and drain (2) pins (D, Dx) may not exceed 85V.

Fault supplies are tied to the primary supplies ( $V_{FP} = V_{DD}$ ,  $V_{FN} = V_{SS}$ )

# 5.6 Dual Supply: Electrical Characteristics

$V_{DD}$  = +15V ± 10%,  $V_{SS}$  = -15V ±10%, GND = 0V (unless otherwise noted) Typical at  $V_{DD}$  = +15V,  $V_{SS}$  = -15V,  $T_A$  = 25°C (unless otherwise noted)

|                                          | PARAMETER                                                        | TEST CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                             | T <sub>A</sub>                    | MIN  | TYP   | MAX | UNIT   |

|------------------------------------------|------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|------|-------|-----|--------|

| ANALOG SWIT                              | гсн                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                   |      |       |     |        |

|                                          |                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -55°C to +25°C                    |      | 180   |     |        |

| R <sub>ON</sub>                          | On-resistance                                                    | $V_S = -10V \text{ to } +10V, I_S = -1\text{mA}$                                                                                                                                                                                                                                                                                                                                                                                                            | -55°C to +125°C                   |      |       | 400 | Ω      |

|                                          | On-resistance mismatch between                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -55°C to +25°C                    |      | 2.5   |     | +      |

| $\Delta R_{ON}$                          | channels                                                         | $V_S = -10V \text{ to } +10V, I_S = -1\text{mA}$                                                                                                                                                                                                                                                                                                                                                                                                            | -55°C to +125°C                   |      |       | 13  | Ω      |

|                                          | +                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -55°C to +25°C                    |      | 1.5   | 10  |        |

| R <sub>FLAT</sub>                        | On-resistance flatness                                           | $V_S = -10V \text{ to } +10V, I_S = -1\text{mA}$                                                                                                                                                                                                                                                                                                                                                                                                            | -55°C to +125°C                   |      | 1.0   | 4   | Ω      |

| R                                        | On-resistance drift                                              | $V_S = 0V, I_S = -1mA$                                                                                                                                                                                                                                                                                                                                                                                                                                      | -55°C to +125°C                   |      | 1.2   | 7   | Ω/°C   |

| R <sub>ON_DRIFT</sub>                    | On-resistance unit                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -55°C to +25°C                    | -1   | 0.1   | 1   |        |

| I <sub>S(OFF)</sub>                      | Source off leakage current <sup>(1)</sup>                        | Switch state is off, $V_S = +10V/-10V$ , $V_D = -10V/ + 10V$ , $V_{DD} = 16.5V$ , $V_{SS} = -16.5V$                                                                                                                                                                                                                                                                                                                                                         | -55°C to +125°C                   | -4.5 | 0.1   | 4.5 | nΑ     |

|                                          |                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                   |      | 0.1   |     |        |

| I <sub>D(OFF)</sub>                      | Drain off leakage current <sup>(1)</sup>                         | Switch state is off, $V_S = +10V/-10V$ , $V_D = -10V/ + 10V$ , $V_{DD} = 16.5V$ , $V_{SS} = -16.5V$                                                                                                                                                                                                                                                                                                                                                         | -55°C to +25°C<br>-55°C to +125°C | -1   | 0.1   | 15  | nA     |

|                                          | _                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                   | -15  | 0.0   |     |        |

| I <sub>S(ON)</sub> , I <sub>,D(ON)</sub> | Channel on leakage current                                       | Switch state is on, $V_S$ = floating, $V_D$ = – 10V/ +10V, or $V_S$ = –10V/ +10V, $V_D$ =                                                                                                                                                                                                                                                                                                                                                                   | –55°C to +25°C                    | -1.5 | 0.3   | 1.5 | nA     |

| (C(V), ',D(C(V)                          |                                                                  | floating, $V_{DD} = 16.5V$ , $V_{SS} = -16.5V$                                                                                                                                                                                                                                                                                                                                                                                                              | –55°C to +125°C                   | -23  |       | 23  |        |

| FAULT CONDI                              | TION                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                   |      |       |     |        |

|                                          | Input leakage current                                            | $V_S = \pm 60V$ , GND = 0V, $V_{DD} = V_{FP} = 16.5V$ ,                                                                                                                                                                                                                                                                                                                                                                                                     |                                   |      | ±110  |     |        |

|                                          | during overvoltage                                               | $V_{SS} = V_{FN} = -16.5V$ $V_{S} = \pm 60V$ , GND = 0V, $V_{DD} = V_{SS} = V_{FP} = V_{FN} = 0V$ , $V_{EN} = V_{Ax} = 0V$ or floating                                                                                                                                                                                                                                                                                                                      |                                   |      |       |     |        |

|                                          | Input leakage current                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                   | ±135 |       |     |        |

| I <sub>S(FA)</sub>                       | during overvoltage with<br>grounded supplies                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                             | –55°C to +125°C                   |      |       |     | μΑ     |

|                                          | Input leakage current                                            | $V_S = \pm 60V$ , GND = 0V, $V_{DD} = V_{SS} = V_{FP} = V_{FN} = \text{floating}$ , $V_{EN} = V_{Ax} = 0V$ or floating                                                                                                                                                                                                                                                                                                                                      |                                   |      |       | ;   |        |

|                                          | during overvoltage with                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                   |      | ±135  |     |        |

|                                          | floating supplies                                                | 7 EN AX - 3                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                   |      |       |     |        |

|                                          | Output leakage current                                           | $\begin{split} &V_{S} = \pm 60 \text{V, GND} = 0 \text{V, } V_{DD} = V_{FP} = 16.5 \text{V,} \\ &V_{SS} = V_{FN} = -16.5 \text{V} \end{split}$ $V_{S} = \pm 60 \text{V, GND} = 0 \text{V, } V_{DD} = V_{SS} = V_{FP} = V_{FN} = 0 \text{V, } V_{EN} = V_{Ax} = 0 \text{V or floating} \end{split}$ $V_{S} = \pm 60 \text{V, GND} = 0 \text{V, } V_{DD} = V_{SS} = V_{FP} = V_{FN} = \text{floating, } V_{EN} = V_{Ax} = 0 \text{V or floating} \end{split}$ | –55°C to +25°C                    |      | ±10   |     | nA     |

|                                          | during overvoltage                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                             | –55°C to +125°C                   | -150 |       | 150 |        |

|                                          | Output leakage current during overvoltage with grounded supplies |                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -55°C to +25°C                    | -50  | ±1    | 50  |        |

| I <sub>D(FA)</sub>                       |                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -55°C to +125°C                   | -550 |       | 550 |        |

|                                          | Output leakage current                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -55°C to +25°C                    |      | ±3    |     |        |

|                                          | during overvoltage with floating supplies                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -55°C to +125°C                   |      | ±8    |     |        |

| DIGITAL INPUT                            |                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                   |      |       |     |        |

|                                          |                                                                  | V -V -V                                                                                                                                                                                                                                                                                                                                                                                                                                                     | –55°C to +125°C                   | -2.5 | +06   | 2.5 |        |

| l <sub>IH</sub>                          | High-level input current                                         | $V_{EN} = V_{Ax} = V_{DD}$                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                   |      | ± 0.6 |     | μA<br> |

| <sub>  </sub>                            | Low-level input current                                          | $V_{EN} = V_{Ax} = 0V$                                                                                                                                                                                                                                                                                                                                                                                                                                      | –55°C to +125°C                   | -1.5 | ± 0.6 | 1.5 | μA     |

| SWITCHING C                              | HARACTERISTICS                                                   | I                                                                                                                                                                                                                                                                                                                                                                                                                                                           | T                                 |      |       |     |        |

| t <sub>ON (EN)</sub>                     | Enable turn-on time                                              | $V_S = 10V$ ,                                                                                                                                                                                                                                                                                                                                                                                                                                               | -55°C to +25°C                    |      | 175   |     | ns     |

|                                          |                                                                  | $R_L = 4\kappa\Omega, C_L = 12pF$                                                                                                                                                                                                                                                                                                                                                                                                                           | -55°C to +125°C                   |      | 290   |     |        |

| t <sub>OFF (EN)</sub>                    | Enable turn-off time                                             | $V_{S} = 10V,$                                                                                                                                                                                                                                                                                                                                                                                                                                              | -55°C to +25°C                    |      | 350   |     | ns     |

| OIT (LIV)                                |                                                                  | $R_L = 4k\Omega$ , $C_L = 12pF$                                                                                                                                                                                                                                                                                                                                                                                                                             | –55°C to +125°C                   |      | 400   |     |        |

| t <sub>TRAN</sub>                        | Transition time                                                  | V <sub>S</sub> = 10V,                                                                                                                                                                                                                                                                                                                                                                                                                                       | –55°C to +25°C                    |      | 180   |     | ns     |

| TRAN                                     | Translation time                                                 | $R_L = 4k\Omega$ , $C_L = 12pF$                                                                                                                                                                                                                                                                                                                                                                                                                             | –55°C to +125°C                   |      | 250   |     |        |

| t <sub>BBM</sub>                         | Break-before-make time delay                                     | $V_S = 10V$ ,<br>$R_1 = 4k\Omega$ , $C_1 = 12pF$                                                                                                                                                                                                                                                                                                                                                                                                            | –55°C to +125°C                   |      | 120   |     | ns     |

| t <sub>RESPONSE</sub>                    | Fault response time                                              | $V_{FP} = 10V, V_{FN} = -10V,$ $R_L = 4k\Omega, C_L = 12pF$                                                                                                                                                                                                                                                                                                                                                                                                 | -55°C to +125°C                   |      | 300   |     | ns     |

| trecovery                                | Fault recovery time                                              | V <sub>FP</sub> = 10V, V <sub>FN</sub> = -10V,                                                                                                                                                                                                                                                                                                                                                                                                              | -55°C to +125°C                   |      | 1.5   |     | μs     |

|                                          | Coult flog recepts - time-                                       | $R_L = 4k\Omega$ , $C_L = 12pF$<br>$V_{FP} = 10V$ , $V_{FN} = -10V$ , $V_{PU} = 5V$ ,                                                                                                                                                                                                                                                                                                                                                                       | 25°C                              |      | 100   |     |        |

| <sup>t</sup> RESPONSE(FLAG)              | Fault flag response time                                         | $R_{PU} = 1k\Omega$ , $C_L = 12pF$                                                                                                                                                                                                                                                                                                                                                                                                                          | 25°C                              |      | 120   |     | ns     |

| t <sub>RECOVERY(FLAG)</sub>              | Fault flag recovery time                                         | $V_{FP} = 10V, V_{FN} = -10V, V_{PU} = 5V,$<br>$R_{PU} = 1k\Omega, C_L = 12pF$                                                                                                                                                                                                                                                                                                                                                                              | 25°C                              |      | 1     |     | μs     |

|                                          |                                                                  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1                                 |      |       |     |        |

# 5.6 Dual Supply: Electrical Characteristics (続き)

$V_{DD} = +15 V \pm 10\%, \ V_{SS} = -15 V \pm 10\%, \ GND = 0V \ (unless otherwise noted)$  Typical at  $V_{DD} = +15 V, \ V_{SS} = -15 V, \ T_A = 25^{\circ}C \ (unless otherwise noted)$

|                                         | PARAMETER                                     | TEST CONDITIONS                                                                                                                                                                                                                  | T <sub>A</sub>  | MIN TYP MA | X UNIT   |

|-----------------------------------------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------------|----------|

| Q <sub>INJ</sub>                        | Charge injection                              | $V_S = 0V$ , $C_L = 1$ nF, $R_S = 0$ $\Omega$                                                                                                                                                                                    | 25°C            | -15        | pC       |

| O <sub>ISO</sub>                        | Off-isolation                                 | $R_S = 50\Omega$ , $R_L = 50\Omega$ , $C_L = 5pF$ , $V_S = 200 \text{ mV}_{RMS}$ , $V_{BIAS} = 0V$ , $f = 1MHz$                                                                                                                  | 25°C            | -80        | dB       |

| X <sub>TALK</sub>                       | Intra-channel crosstalk                       | $R_S = 50\Omega$ , $R_L = 50\Omega$ , $C_L = 5pF$ ,<br>$V_S = 200 \text{ mV}_{RMS}$ , $V_{BIAS} = 0V$ , $f = 1MHz$                                                                                                               | 25°C            | -95        | dB       |

| BW                                      | –3 dB bandwidth                               | $R_S = 50\Omega$ , $R_L = 50\Omega$ , $C_L = 5pF$ , $V_S = 200 \text{ mV}_{RMS}$ , $V_{BIAS} = 0V$                                                                                                                               | 25°C            | 150        | MHz      |

| I <sub>LOSS</sub>                       | Insertion loss                                | $R_S = 50\Omega$ , $R_L = 50\Omega$ , $C_L = 5pF$ ,<br>$V_S = 200 \text{ mV}_{RMS}$ , $V_{BIAS} = 0V$ , $f = 1MHz$                                                                                                               | 25°C            | -9         | dB       |

| THD+N                                   | Total harmonic distortion plus noise          | $R_S = 40\Omega$ , $R_L = 10k\Omega$ , $V_S = 15V_{PP}$ , $V_{BIAS} = 0V$ , $f = 20Hz$ to $20kHz$                                                                                                                                | 25°C            | 0.0015     | %        |

| C <sub>S(OFF)</sub>                     | Input off-capacitance                         | $f = 1MHz, V_S = 0V$                                                                                                                                                                                                             | 25°C            | 3.5        | pF       |

| C <sub>D(OFF)</sub>                     | Output off-capacitance                        | $f = 1MHz, V_S = 0V$                                                                                                                                                                                                             | 25°C            | 28         | pF       |

| C <sub>S(ON)</sub> , C <sub>D(ON)</sub> | Input/Output on-capacitance                   | $f = 1MHz, V_S = 0V$                                                                                                                                                                                                             | 25°C            | 30         | pF       |

| POWER SUPPL                             | _Y                                            |                                                                                                                                                                                                                                  | 1               |            |          |

|                                         |                                               | $V_{DD} = V_{FP} = 16.5V$ , $V_{SS} = V_{FN} = -16.5V$ ,                                                                                                                                                                         | 25°C            | 0.25       |          |

| I <sub>DD</sub>                         | V <sub>DD</sub> supply current                | $V_{Ax}$ = 0V, 5V, or $V_{DD}$ , $V_{EN}$ = 5V or $V_{DD}$ , $V_{S}$ = 0V                                                                                                                                                        | -55°C to +125°C | C          | .6 mA    |

|                                         |                                               | $V_{DD} = V_{FP} = 16.5V$ , $V_{SS} = V_{FN} = -16.5V$ ,                                                                                                                                                                         | 25°C            | 0.15       |          |

| I <sub>SS</sub>                         | V <sub>SS</sub> supply current                | $V_{Ax}$ = 0V, 5V, or $V_{DD}$ , $V_{EN}$ = 5V or $V_{DD}$ , $V_{S}$ = 0V                                                                                                                                                        | -55°C to +125°C | C          | .5 mA    |

| I <sub>GND</sub>                        | GND current                                   | $\begin{array}{l} V_{DD} = V_{FP} = 16.5V,  V_{SS} = V_{FN} =  -16.5V, \\ V_{AX} = 0V,  5V,  or  V_{DD},  V_{EN} = 5V  or  V_{DD},  V_{S} \\ = 0V \end{array}$                                                                   | 25°C            | 0.075      | mA       |

| I <sub>FP</sub>                         | V <sub>FP</sub> supply current                | $\begin{array}{l} V_{DD} = V_{FP} = 16.5V,  V_{SS} = V_{FN} =  -16.5V, \\ V_{Ax} = 0V,  5V,  or  V_{DD},  V_{EN} = 5V  or  V_{DD},  V_{S} \\ = 0V \end{array}$                                                                   | 25°C            | 10         | μА       |

| I <sub>FN</sub>                         | V <sub>FN</sub> supply current                | $\begin{array}{l} V_{DD} = V_{FP} = 16.5V,  V_{SS} = V_{FN} =  -16.5V, \\ V_{Ax} = 0V,  5V,  \text{or}   V_{DD},  V_{EN} = 5V   \text{or}   V_{DD},  V_{S} \\ = 0V \end{array}$                                                  | 25°C            | 10         | μА       |

|                                         |                                               | $V_S = \pm 60V$ , $V_{DD} = V_{FP} = 16.5V$ , $V_{SS} = V_{FN}$                                                                                                                                                                  | 25°C            | 0.25       |          |

| $I_{DD(FA)}$                            | V <sub>DD</sub> supply current under fault    | = $-16.5V$ , $V_{Ax} = 0V$ , $5V$ , or $V_{DD}$ , $V_{EN} = 5V$ or $V_{DD}$                                                                                                                                                      | _55°C to +125°C | 1.:        | mA<br>25 |

|                                         |                                               | $V_S = \pm 60V$ , $V_{DD} = V_{FP} = 16.5V$ , $V_{SS} = V_{FN}$                                                                                                                                                                  | 25°C            | 0.15       |          |

| I <sub>SS(FA)</sub>                     | V <sub>SS</sub> supply current under fault    | = $-16.5V$ , $V_{Ax} = 0V$ , $5V$ , or $V_{DD}$ , $V_{EN} = 5V$ or $V_{DD}$                                                                                                                                                      | -55°C to +125°C | 0.         | 75 mA    |

| I <sub>GND(FA)</sub>                    | GND current under fault                       | $\begin{aligned} &V_S = \pm \ 60V, \ V_{DD} = V_{FP} = 16.5V, \ V_{SS} = V_{FN} \\ &= -16.5V, \ V_{Ax} = 0V, \ 5V, \ or \ V_{DD}, \ V_{EN} = 5V \\ ∨ \ V_{DD} \end{aligned}$                                                     | 25°C            | 0.2        | mA       |

| I <sub>FP(FA)</sub>                     | V <sub>FP</sub> supply current under fault    | $\begin{aligned} &V_S = \pm  60\text{V, } V_{DD} = V_{FP} = 16.5\text{V, } V_{SS} = V_{FN} \\ &=  -16.5\text{V, } V_{Ax} =  0\text{V, } 5\text{V, } \text{ or } V_{DD},  V_{EN} = 5\text{V} \\ &\text{or } V_{DD} \end{aligned}$ | 25°C            | 20         | μА       |

| I <sub>FN(FA)</sub>                     | V <sub>FN</sub> supply current under fault    | $\begin{aligned} &V_S = \pm  60\text{V, } V_{DD} = V_{FP} = 16.5\text{V, } V_{SS} = V_{FN} \\ &= -16.5\text{V, } V_{Ax} = 0\text{V, } 5\text{V, } \text{ or } V_{DD}, V_{EN} = 5\text{V} \\ &\text{or } V_{DD} \end{aligned}$    | 25°C            | 20         | μА       |

| Inn/pioas: 5)                           | V <sub>DD</sub> supply current (disable mode) | $V_{DD} = V_{FP} = 16.5V, V_{SS} = V_{FN} = -16.5V,$                                                                                                                                                                             | 25°C            | 0.15       | mA.      |

| IDD(DISABLE)                            | ADD and bis content (disable illoge)          | $V_{Ax} = 0V$ , 5V, or $V_{DD}$ , $V_{EN} = 0V$ , $V_{S} = 0V$                                                                                                                                                                   | -55°C to +125°C | C          | .6       |

| SS(DISABLE)                             | V <sub>SS</sub> supply current (disable mode) | $V_{DD} = V_{FP} = 16.5V$ , $V_{SS} = V_{FN} = -16.5V$ ,                                                                                                                                                                         | 25°C            | 0.1        | mA       |

| ISS(DISABLE)                            | 133 Supply Culterit (disable mode)            | $V_{Ax} = 0V$ , 5V, or $V_{DD}$ , $V_{EN} = 0V$ , $V_{S} = 0V$                                                                                                                                                                   | –55°C to +125°C | 0          | .5       |

<sup>(1)</sup> When  $V_S$  is positive,  $V_D$  is negative, and vice versa.

Copyright © 2024 Texas Instruments Incorporated

8

Product Folder Links: TMUX582F-SEP

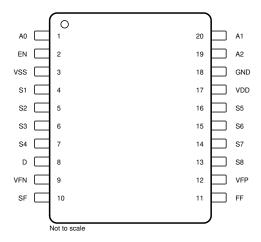

# 5.7 Single Supply: Electrical Characteristics

$V_{DD}$  = +12V ± 10%,  $V_{SS}$  = 0V, GND = 0V (unless otherwise noted) Typical at  $V_{DD}$  = +12V,  $V_{SS}$  = 0V,  $T_A$  = 25°C (unless otherwise noted)

|                                          | $_{0}$ = +12V, V <sub>SS</sub> = 0V, T <sub>A</sub> = 25°<br>PARAMETER | TEST CONDITIONS                                                                                                | T <sub>A</sub>  | MIN  | TYP   | MAX | UNIT       |

|------------------------------------------|------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|-----------------|------|-------|-----|------------|

| ANALOG SWIT                              | СН                                                                     |                                                                                                                |                 |      |       |     |            |

|                                          |                                                                        |                                                                                                                | -55°C to +25°C  |      | 180   |     |            |

| R <sub>ON</sub>                          | On-resistance                                                          | $V_{\rm S} = 0V \text{ to } 7.8V, I_{\rm S} = -1\text{mA}$                                                     | -55°C to +125°C |      |       | 400 | Ω          |

|                                          | On-resistance mismatch between                                         |                                                                                                                | -55°C to +25°C  |      | 2.5   |     |            |

| ΔR <sub>ON</sub> channels                |                                                                        | $V_S = 0V \text{ to } 7.8V, I_S = -1\text{mA}$                                                                 | -55°C to +125°C |      |       | 13  | Ω          |

| R <sub>FLAT</sub>                        | On-resistance flatness                                                 | V <sub>S</sub> = 0V to 7.8V, I <sub>S</sub> = -1mA                                                             | -55°C to +25°C  |      | 7     |     | Ω          |

| R <sub>FLAT</sub>                        | On-resistance flatness                                                 | $V_S = 0V \text{ to } 7.8V, I_S = -1\text{mA}$                                                                 | –55°C to +125°C |      |       | 80  | Ω          |

| TLAI                                     | On resistance manage                                                   | 13 01 10 1101,13 111111                                                                                        | -55°C to +25°C  |      | 1.5   |     |            |

| R <sub>FLAT</sub>                        | On-resistance flatness                                                 | $V_S = 1V \text{ to } 7.8V, I_S = -1\text{mA}$                                                                 | -55°C to +125°C |      |       | 8   | Ω          |

| R <sub>ON DRIFT</sub>                    | On-resistance drift                                                    | V <sub>S</sub> = 6V, I <sub>S</sub> = -1mA                                                                     | -55°C to +125°C |      | 1.2   |     | Ω/°C       |

| · ·ON_DRIFT                              |                                                                        |                                                                                                                | -55°C to +25°C  | -1   | 0.1   | 1   |            |

| I <sub>S(OFF)</sub>                      | Source off leakage current <sup>(1)</sup>                              | Switch state is off, $V_S = 1V/10V$ , $V_D = 10V/10V$ , $V_{DD} = 13.2V$                                       | -55°C to +125°C | -4.5 | 0.1   | 4.5 | nΑ         |

|                                          |                                                                        |                                                                                                                | -55°C to +25°C  | -1   | 0.1   | 1   |            |

| $I_{D(OFF)}$                             | Drain off leakage current <sup>(1)</sup>                               | Switch state is off, $V_S = 1V/10V$ , $V_D = 10V/10V$ , $V_{DD} = 13.2V$                                       | -55°C to +125°C | -15  | 0.1   | 15  | nA         |

|                                          |                                                                        |                                                                                                                | -55°C to +25°C  | -1.5 | 0.3   | 1.5 |            |

| I <sub>S(ON)</sub> , I <sub>,D(ON)</sub> | Channel on leakage current                                             | Switch state is on, $V_S$ = floating, $V_D$ = 1V/<br>10V, $V_{DD}$ = 13.2                                      | -55°C to +25°C  |      | 0.3   | 23  | nΑ         |

|                                          |                                                                        | 100, 100 - 10.2                                                                                                | -55°C to +125°C | -23  |       | 23  |            |

| FAULT CONDITI                            | T                                                                      | V                                                                                                              | T               |      |       |     |            |

| I <sub>S(FA)</sub>                       | Input leakage current during overvoltage                               | $V_S = \pm 60V$ , GND = 0V, $V_{DD} = V_{FP} = 13.2V$ , $V_{SS} = V_{FN} = 0V$                                 |                 |      | ±145  |     |            |

|                                          | Input leakage current<br>during overvoltage with<br>grounded supplies  | $V_S = \pm 60V$ , GND = 0V, $V_{DD} = V_{SS} = V_{FP} = V_{FN} = 0V$ , $V_{EN} = V_{Ax} = 0V$ or floating      | -55°C to +125°C | ±135 |       |     | μ <b>A</b> |

|                                          | Input leakage current during overvoltage with floating supplies        | $V_S = \pm 60V$ , GND = 0V, $V_{DD} = V_{SS} = V_{FP} = V_{FN}$ = floating, $V_{EN} = V_{Ax} = 0V$ or floating |                 |      |       |     |            |

|                                          | Output leakage current                                                 | $V_S = \pm 60V$ , GND = 0V, $V_{DD} = V_{FP} = 13.2V$ ,                                                        | -55°C to +25°C  |      | ±10   |     |            |

|                                          | during overvoltage                                                     | V <sub>SS</sub> = V <sub>FN</sub> = 0V                                                                         | -55°C to +125°C | -100 |       | 100 | nΔ         |

|                                          | Output leakage current                                                 | V = 1 COV CND = 0V V = V = V =                                                                                 | -55°C to +25°C  | -50  | ±1    | 50  |            |

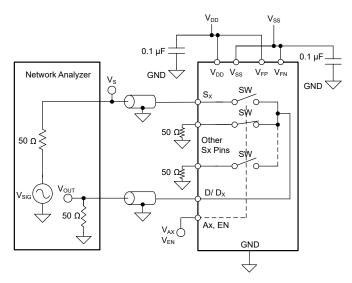

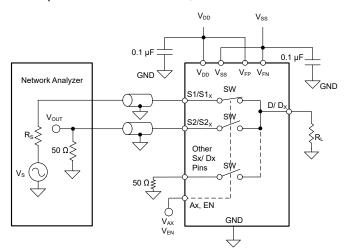

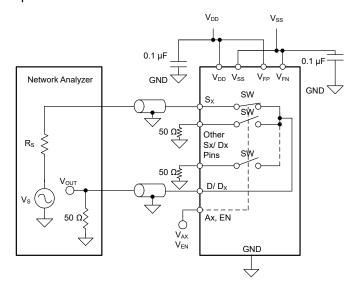

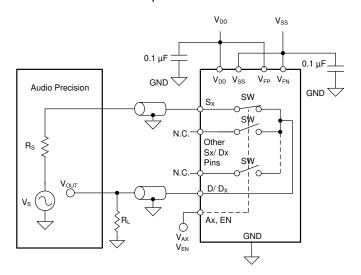

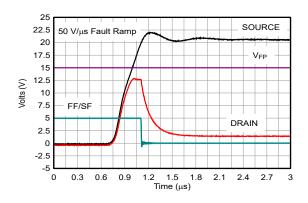

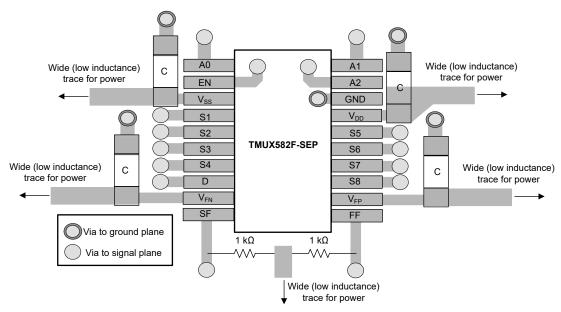

| $I_{D(FA)}$                              | during overvoltage with grounded supplies                              | $V_S = \pm 60V$ , GND = 0V, $V_{DD} = V_{SS} = V_{FP} = V_{FN} = 0V$ , $V_{EN} = V_{Ax} = 0V$ or floating      | –55°C to +125°C | -550 |       | 550 |            |