# TPS6287x-Q1 2.7V~6V 入力、15A、20A、25A、および 30A、車載用高速過渡同 期整流式降圧コンバータ、I<sup>2</sup>C インターフェイス付き

# 1 特長

- ・ 車載アプリケーション向けに AEC-Q100 認証済み - デバイス温度グレード 1:-40℃~125℃ T<sub>Δ</sub>

- 接合部温度範囲:-40℃~150℃

- 機能安全対応 - 機能安全システムの設計に役立つ資料を利用可 能

- 入力電圧範囲:2.7V~6V

- ピン互換性のあるデバイスファミリ:15A、20A、25A、 30A

- 3つの選択可能な出力電圧範囲:0.4V~1.675V

- 0.4V~0.71875V (1.25mV 刻み)

- 0.4V~1.0375V (2.5mV 刻み)

- 0.4V~1.675V (5mV 刻み)

- 出力電圧精度:±0.8%

- 内部電力 MOSFET:2.6mΩ、1.5mΩ

- 可変ソフトスタート

- 外部補償

- VSEL ピンを介してスタートアップ出力電圧を選択可 能

- FSEL ピンを介して 1.5MHz、2.25MHz、2.5MHz、 3MHz のスイッチング周波数を選択可能

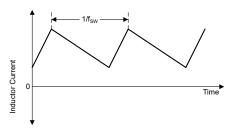

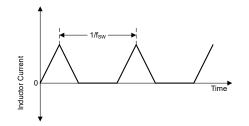

- 強制 PWM またはパワー セーブ モード動作

- 外部抵抗または I<sup>2</sup>C によるスタートアップ出力電圧の 選択

- I<sup>2</sup>C 互換インターフェイス:最高 3.4MHz

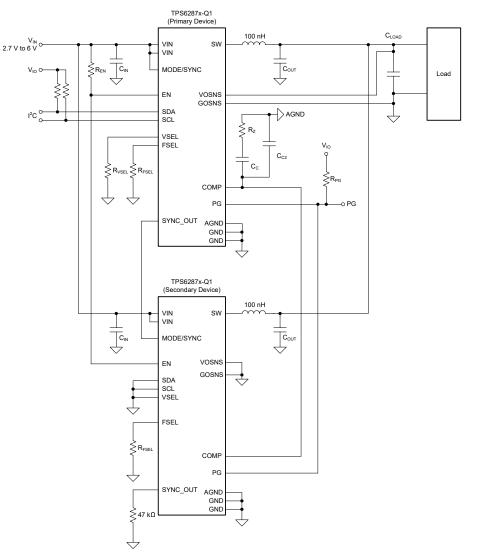

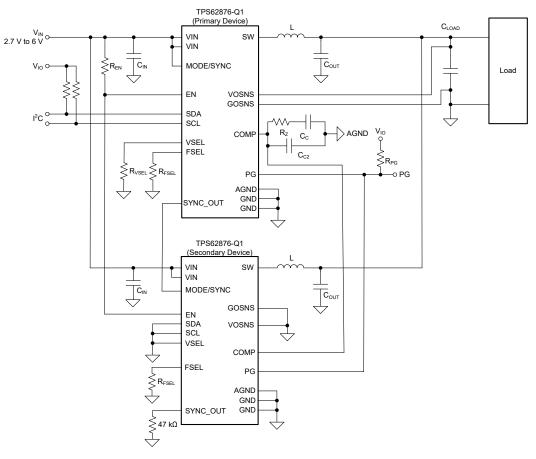

- オプションのスタック動作により、出力電流能力を向上

- 差動リモート センス

- サーマル事前警告およびサーマルシャットダウン

- 出力放電

- オプションのスペクトラム拡散クロック供給機能を内蔵

- ウィンドウ コンパレータによるパワー グッド出力

# 2 アプリケーション

- ADAS カメラ、ADAS センサ フュージョン

- サラウンド ビュー ECU

- ハイブリッドおよび再構成可能クラスタ

- ヘッドユニット、テレマティクス制御ユニット

# 3 概要

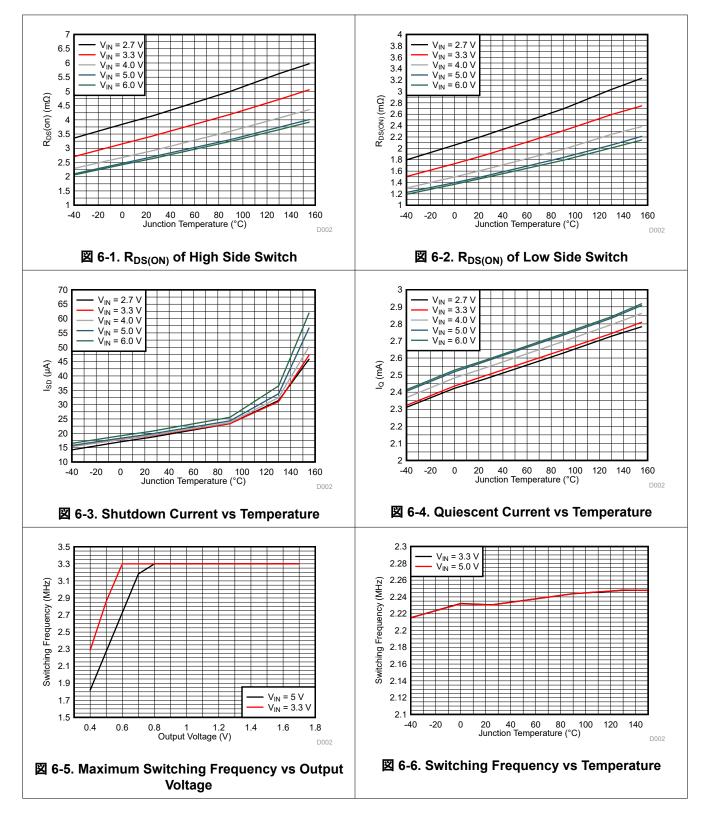

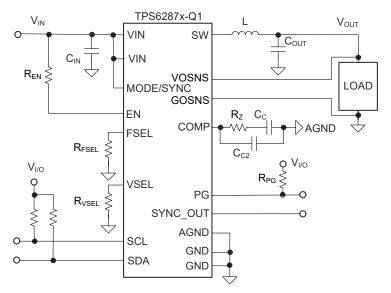

TPS62874-Q1、TPS62875-Q1、TPS62876-Q1、および TPS62877-Q1 TPS6287B10-Q1、TPS6287B15-Q1、 TPS6287B20、および TPS6287B30 は、I<sup>2</sup>C インターフ ェイスおよび差動リモート センスを搭載したピン互換、 15A、20A、25A、30A 同期整流式降圧 DC/DC コンバー

タのファミリです。すべてのデバイスは、高い効率と使いや すさを特長としています。低抵抗の電源スイッチにより、高 い周囲温度でも最大 30A の出力電流を供給できます。こ れらのデバイスをスタック モードで動作させることで、大き な出力電流を供給することや、消費電力を複数のデバイ スに分散することが可能です。

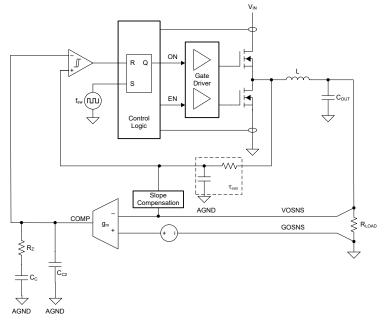

TPS6287x-Q1 ファミリは、固定周波数動作での高速過渡 応答を組み合わせた拡張 DCS 制御方式を実装していま す。デバイスは、最大効率を達成するパワー セーブ モー ド、または最高の過渡性能と最小の出力電圧リップルを実 現する強制 PWM モードで動作できます。

オプションのリモート センシング機能により、ポイント オブ ロードでの電圧レギュレーションが最大化され、デバイスは 出力電圧範囲全体にわたって±0.8%のDC 電圧精度を 達成します。

スイッチング周波数は FSEL ピンを介して選択可能であ り、1.5MHz、2.25MHz、2.5MHz、3MHz のいずれかに設 定する、または同じ周波数範囲の外部クロックに同期させ ることができます。

I<sup>2</sup>C 互換インターフェイスを使うと、各種の制御、監視、警 告機能(電圧の監視、温度に関連する警告など)を実現 できます。出力電圧は、負荷の消費電力を性能ニーズに 合わせて迅速に調整できます。デフォルトの起動電圧は、 VSELピンを介して抵抗により選択できます。

|                     | 製品情報 |                      |

|---------------------|------|----------------------|

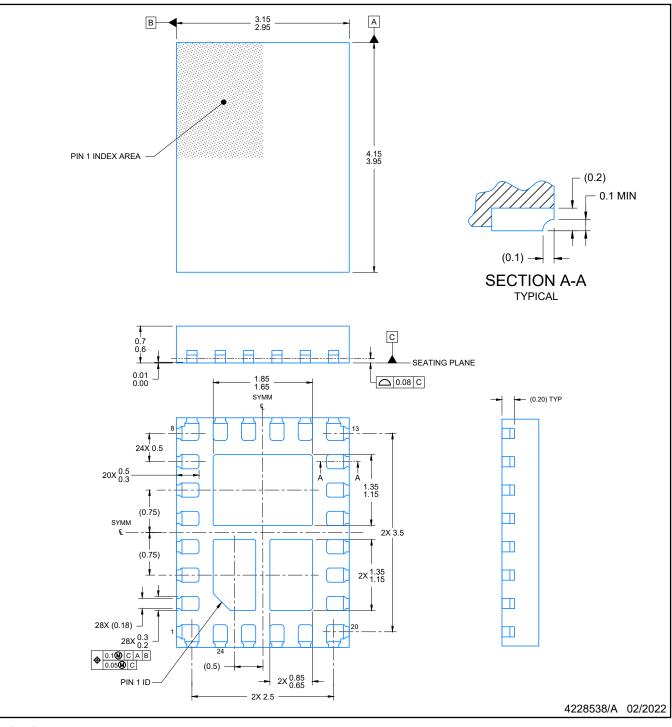

| 部品番号 <sup>(2)</sup> | 電流定格 | パッケージ <sup>(1)</sup> |

| TPS62874-Q1         | 15A  |                      |

| TPS62875-Q1         | 20A  | RZV (WQFN、24)        |

| TPS62876-Q1         | 25A  | 4.05mm × 3.05mm      |

| TPS62877-Q1         | 30A  |                      |

- 詳細については、セクション 13 を参照してください。 (1)

- デバイスのオプションの表を参照してください。 (2)

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳)を使用していることがあり、TI では翻訳の正確性および妥当 か

性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

# **Table of Contents**

| 1 特長                                                  | 1              |

|-------------------------------------------------------|----------------|

| 2アプリケーション                                             |                |

| 3 概要                                                  |                |

| 4 Device Options                                      | 3              |

| 5 Pin Configuration and Functions                     | 4              |

| 6 Specifications                                      | 6              |

| 6.1 Absolute Maximum Ratings                          | 6              |

| 6.2 ESD Ratings - Q100                                | 6              |

| 6.3 Recommended Operating Conditions                  | <mark>6</mark> |

| 6.4 Thermal Information                               | 7              |

| 6.5 Electrical Characteristics                        | 7              |

| 6.6 I <sup>2</sup> C Interface Timing Characteristics |                |

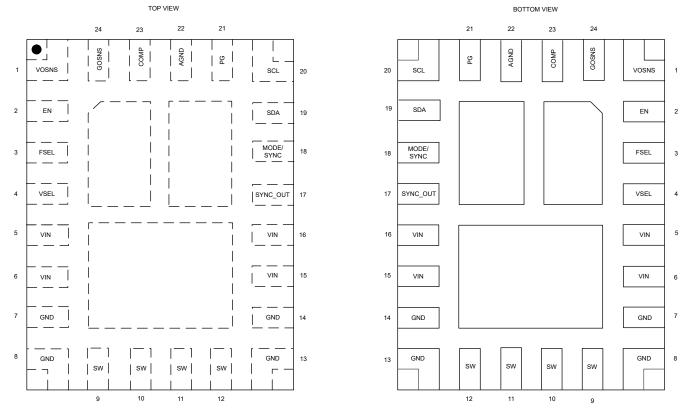

| 6.7 Typical Characteristics                           |                |

| 7 Parameter Measurement Information                   |                |

| 8 Detailed Description                                | 15             |

| 8.1 Overview                                          | 15             |

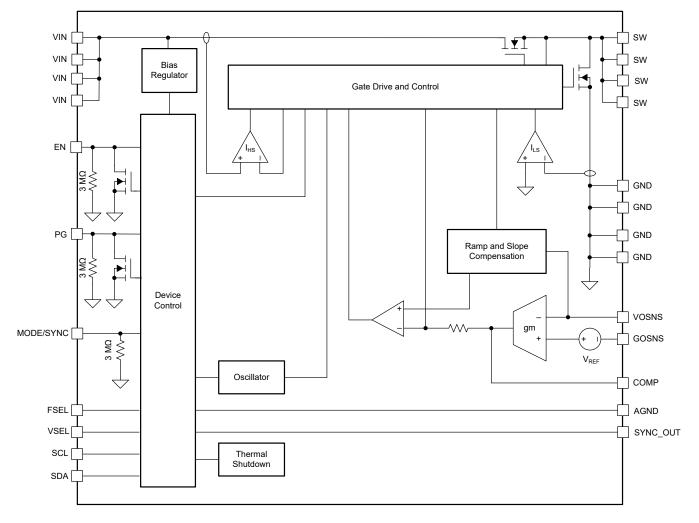

| 8.2 Functional Block Diagram                          | 15             |

| 8.3 Feature Description                               | 16             |

| 8.4 Device Functional Modes                           |                |

| 8.5 Programming                                       |                |

| 9 Device Registers                                    | 37             |

| 10 Application and Implementation                 | 43               |

|---------------------------------------------------|------------------|

| 10.1 Application Information                      | . 43             |

| 10.2 Typical Application                          |                  |

| 10.3 Typical Application Using Two TPS62876-Q1 in |                  |

| a Stacked Configuration                           | 52               |

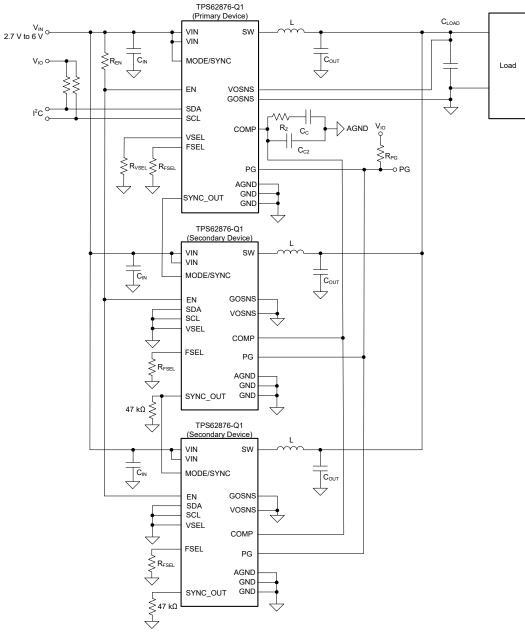

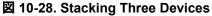

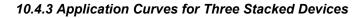

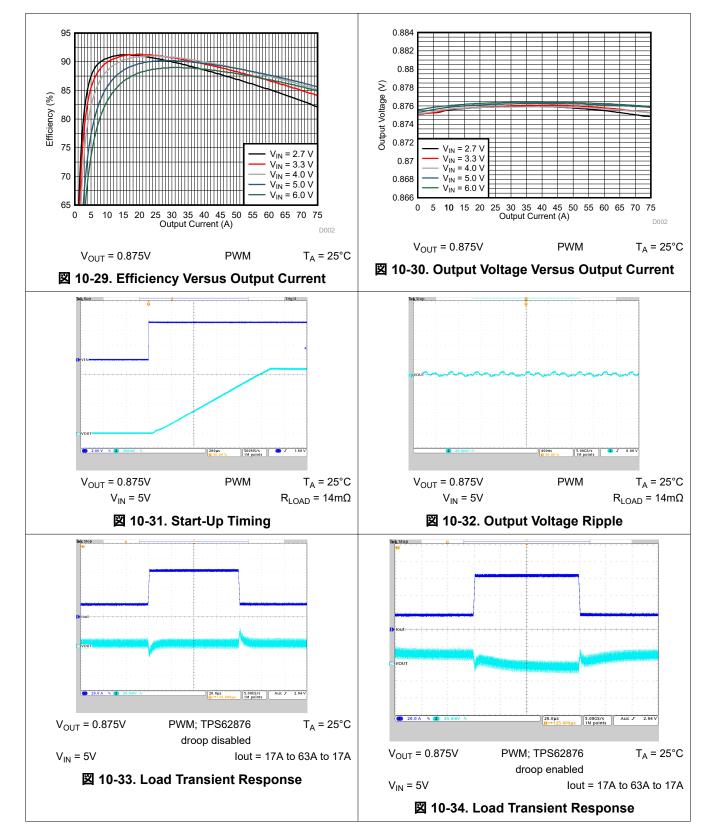

| 10.4 Typical Application Using Three TPS62876-Q1  |                  |

| in a Stacked Configuration                        | 57               |

| 10.5 Best Design Practices                        | <mark>61</mark>  |

| 10.6 Power Supply Recommendations                 | <mark>6</mark> 1 |

| 10.7 Layout                                       |                  |

| 11 Device and Documentation Support               | <mark>6</mark> 4 |

| 11.1 Documentation Support                        | 64               |

| 11.2ドキュメントの更新通知を受け取る方法                            | 64               |

| 11.3 サポート・リソース                                    | 64               |

| 11.4 Trademarks                                   |                  |

| 11.5 静電気放電に関する注意事項                                | 64               |

| 11.6 用語集                                          | 64               |

| 12 Revision History                               |                  |

| 13 Mechanical, Packaging, and Orderable           |                  |

| Information                                       | 66               |

|                                                   |                  |

# **4 Device Options**

| DEVICE NUMBER                     | OUTPUT<br>CURRENT | VSEL SETTING FOR START-UP<br>VOLTAGE AND I2C ADDRESS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | SSC | DEFAULT<br>DROOP | TRANS.<br>NONSYNC<br>MODE | SOFT-<br>START<br>TIME |

|-----------------------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------------|---------------------------|------------------------|

| TPS62874QWRZVRQ1                  | 15A               | VSEL with 6 2kO to GND: 0 80V 0x44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Off | Off              | Off                       |                        |

| TPS62875QWRZVRQ1                  | 20A               | VSEL shorted to GND: 0.75V, 0x45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Off | Off              | Off                       |                        |

| TPS62876QWRZVRQ1                  | 25A               | VSEL shorted to VIN: 0.875V, 0x46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Off | Off              | Off                       |                        |

| TPS62877QWRZVRQ1                  | 30A               | VSEL with 47kΩ to VIN: 0.58V, 0x47<br>VSEL with 6.2kΩ to GND: 0.8V, 0x44<br>VSEL shorted to GND: 0.8V, 0x45<br>VSEL shorted to VIN: 0.875V, 0x46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     | Off              | Off                       |                        |

| TPS62874B1QWRZVRQ1                | 15A               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Off | On               | On                        |                        |

| TPS62875B1QWRZVRQ1                | 20A               | VOLTAGE AND 12C ADDRESSSSCVSEL with 6.2kΩ to GND: 0.80V, 0x44<br>VSEL shorted to GND: 0.75V, 0x45<br>VSEL shorted to VIN: 0.875V, 0x46<br>VSEL with 47kΩ to VIN: 0.58V, 0x47OffVSEL with 6.2kΩ to GND: 0.8V, 0x44<br>VSEL shorted to GND: 0.8V, 0x44<br>VSEL shorted to GND: 0.8V, 0x44<br>VSEL shorted to GND: 0.8V, 0x45<br>VSEL shorted to VIN: 0.875V, 0x46<br>VSEL with 47kΩ to VIN: 0.875V, 0x46<br>VSEL shorted to GND: 0.85V, 0x44<br>VSEL shorted to GND: 0.75V, 0x45<br>VSEL shorted to GND: 0.75V, 0x46<br>VSEL shorted to VIN: 0.875V, 0x46<br>VSEL shorted to VIN: 0.875V, 0x46<br>VSEL shorted to GND: 0.73V, 0x44<br>VSEL shorted to GND: 0.73V, 0x44<br>VSEL shorted to GND: 0.75V, 0x45<br>VSEL shorted to VIN: 0.8V, 0x47OffVSEL with 6.2kΩ to GND: 0.73V, 0x44<br>VSEL shorted to GND: 0.75V, 0x45<br>VSEL shorted to VIN: 0.8V, 0x47OnVSEL with 6.2kΩ to GND: 0.75V, 0x45<br>VSEL shorted to VIN: 0.8V, 0x47OnVSEL with 6.2kΩ to GND: 0.75V, 0x45<br>VSEL shorted to VIN: 0.8V, 0x47OnVSEL with 6.2kΩ to GND: 0.75V, 0x45<br>VSEL shorted to VIN: 0.8V, 0x47OffVSEL with 6.2kΩ to GND: 0.75V, 0x45<br>VSEL shorted to VIN: 0.8V, 0x47OffVSEL with 6.2kΩ to GND: 0.75V, 0x45<br>VSEL shorted to VIN: 0.8V, 0x47OffVSEL with 6.2kΩ to GND: 0.75V, 0x45<br>VSEL shorted to VIN: 0.75V, 0x46<br> | Off | On               | On                        |                        |

| TPS62876B1QWRZVRQ1                | 25A               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Off | On               | On                        |                        |

| TPS62877B1QWRZVRQ1                | 30A               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Off | On               | On                        |                        |

| TPS62875B2QWRZVRQ1                | 20A               | VSEL shorted to GND: 0.75V, 0x45<br>VSEL shorted to VIN: 0.875V, 0x46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Off | On               | On                        |                        |

| TPS62875B3QWRZVRQ1                | 20A               | VSEL shorted to GND: 0.75V, 0x45<br>VSEL shorted to VIN: 0.8V, 0x46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | On  | On               | On                        | 1ms                    |

| TPS62876B3QWRZVRQ1                | 25A               | VSEL with $6.2k\Omega$ to GND: $0.845V$ , $0x44$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | On  | On               | On                        |                        |

| TPS62877B3QWRZVRQ1 <sup>(1)</sup> | 30A               | VSEL shorted to VIN: 0.8V, 0x46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | On  | On               | On                        |                        |

| TPS62874B4QWRZVRQ1                | 15A               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Off | On               | On                        |                        |

| TPS62875B4QWRZVRQ1                | 20A               | VSEL shorted to VIN: 0.765V, 0x46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Off | On               | On                        |                        |

| TPS62875B5QWRZVRQ1                | 20A               | VSEL shorted to VIN: 0.765V, 0x46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Off | On               | On                        |                        |

(1) Preview information (not Production Data)

3

# **5** Pin Configuration and Functions

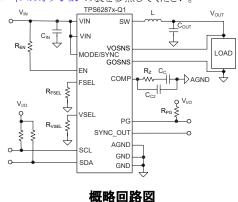

# 図 5-1. RZV Package 24 Pin WQFN

#### 表 5-1. Pin Functions

| Р               |       |     | PIN                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  | DESCRIPTION |

|-----------------|-------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|-------------|

| NO.             | NAME  |     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |             |

| 1               | VOSNS | I   | Output voltage sense (differential output voltage sensing).                                                                                                                                                                                                                                                                                                                                                                                            |  |             |

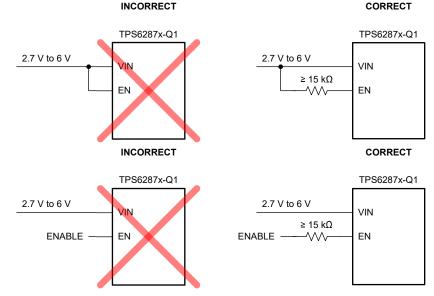

| 2               | EN    | I   | This pin is the enable pin of the device. Connect to this pin using a series resistor of at least $15k\Omega$ . A logic low level on this pin disables the device, and a logic high level on the pin enables the device. Do not leave this pin unconnected. For stacked operation interconnect EN pins of all stacked devices with a resistor to the supply voltage or a GPIO of a processor. See <i>Stacked Operation</i> for a detailed description. |  |             |

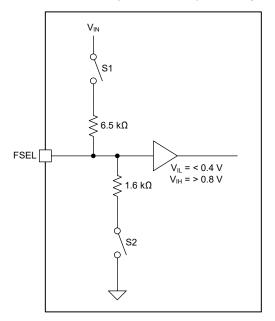

| 3               | FSEL  | I   | Frequency select pin. A resistor or a short circuit to GND or $V_{IN}$ determines the switching frequency if not externally synchronized. See $\forall 2 2 \Rightarrow 8.3.6$ for the frequency options.                                                                                                                                                                                                                                               |  |             |

| 4               | VSEL  | I   | Start-up output voltage set pin. A resistor or short circuit to GND or $V_{\text{IN}}$ defines the selected output voltage.                                                                                                                                                                                                                                                                                                                            |  |             |

| 5, 6, 15, 16    | VIN   | Р   | Power supply input. Connect the input capacitor as close as possible between pin VIN and GND.                                                                                                                                                                                                                                                                                                                                                          |  |             |

| 7, 8,<br>13, 14 | GND   | GND | Ground pin                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |             |

| 9, 10, 11, 12   | SW    | 0   | This is the switch pin of the converter and is connected to the internal Power MOSFETs.                                                                                                                                                                                                                                                                                                                                                                |  |             |

4 資料に関するフィードバック(ご意見やお問い合わせ)を送信

Copyright © 2024 Texas Instruments Incorporated

Product Folder Links: TPS62874-Q1 TPS62875-Q1 TPS62876-Q1 TPS62877-Q1

# 表 5-1. Pin Functions (続き)

| PIN                     |           | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

|-------------------------|-----------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NO.                     | NAME      | TIPE                | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| 17                      | SYNCOUT   | 0                   | Internal clock output pin for synchronization in stacked mode. Leave this pin floating for single device operation. Connect this pin to the MODE/SYNC pin of the successing device in the daisy-chain in stacked operation. Do not use this pin to connect to a non-TPS6287x-Q1 device. During start-up, this pin is used to identify if a device must operate as a secondary converter in stacked operation. Connect a 47k $\Omega$ resistor from this pin to GND to define a secondary converter in stacked operation. See <i>Stacked Operation</i> for a detailed description. |  |  |

| 18                      | MODE/SYNC | I                   | The device runs in Power-Save mode when this pin is pulled low. If the pin is pulled high, the device runs in Forced-PWM mode. Do not leave this pin unconnected. The mode pin can also be used to synchronize the device to an external clock.                                                                                                                                                                                                                                                                                                                                   |  |  |

| 19                      | SDA       | I/O                 | I <sup>2</sup> C serial data pin. Do not leave this pin floating. Connect a pullup to logic high level.<br>Connect to GND for secondary devices in stacked operation.                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| 20                      | SCL       | I/O                 | I <sup>2</sup> C serial clock pin. Do not leave this pin floating. Connect a pullup resistor to a logic high level.<br>Connect to GND for secondary devices in stacked operation.                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

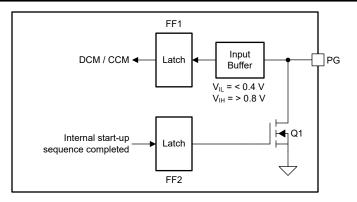

| 21                      | PG        | I/O                 | Open drain power good output. Low impedance when not "power good", high impedance<br>when "power good". This pin can be left open or be tied to GND when not used in single<br>device operation.<br>In stacked operation interconnect the PG pins of all stacked devices. Only the PG pin of the<br>primary converter in stacked operation is an open drain output. For devices that are defined<br>as secondary converters in stacked mode the pin is an input pin. See <i>Stacked Operation</i> for<br>a detailed description.                                                  |  |  |

| 22                      | AGND      | GND                 | Analog Ground. Connect to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| 23                      | COMP      | _                   | Device compensation input. A resistor and capacitor from this pin to AGND define the compensation of the control loop.<br>In stacked operation connect the COMP pins of all stacked devices together and connect a resistor and capacitor between the common COMP node and AGND.                                                                                                                                                                                                                                                                                                  |  |  |

| 24                      | GOSNS     | I                   | Output ground sense (differential output voltage sensing)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

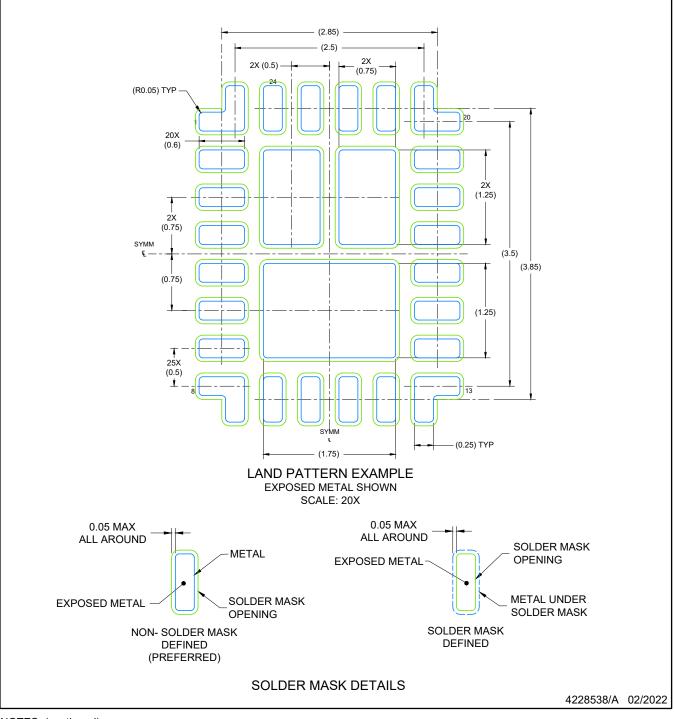

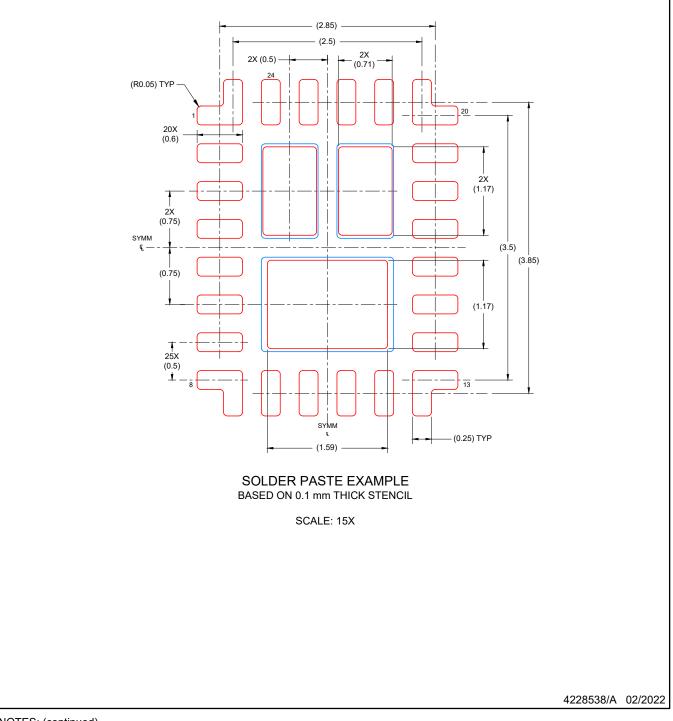

| Exposed<br>Thermal Pads |           | _                   | The thermal pads must be soldered to GND to achieve an appropriate thermal resistance and for mechanical stability.                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

(1) I = input, O = output, P = power, GND = ground

# **6** Specifications

# 6.1 Absolute Maximum Ratings

over operating temperature range (unless otherwise noted)<sup>(1)</sup>

|                        |                                          | MIN  | MAX                   | UNIT |

|------------------------|------------------------------------------|------|-----------------------|------|

| Voltage <sup>(2)</sup> | VIN <sup>(4)</sup>                       | -0.3 | 6.5                   | V    |

|                        | SW (DC)                                  | -0.3 | V <sub>IN</sub> + 0.3 | V    |

| Voltage <sup>(2)</sup> | COMP                                     | -0.3 | V <sub>IN</sub>       | V    |

|                        | SW (AC, less than 10ns) <sup>(3)</sup>   | -3   | 10                    | V    |

|                        | VOSNS                                    | -0.3 | 1.8                   | V    |

| Voltage <sup>(2)</sup> | SCL, SDA                                 | -0.3 | 5.5                   | V    |

| Voltage <sup>(2)</sup> | SYNC_OUT                                 | -0.3 | 2                     | V    |

| Voltage <sup>(2)</sup> | PG                                       | -0.3 | 6.5                   | V    |

| Voltage <sup>(2)</sup> | FSEL, VSEL, EN, MODE/SYNC <sup>(4)</sup> | -0.3 | 6.5                   | V    |

| Voltage <sup>(2)</sup> | GOSNS                                    | -0.3 | 0.3                   | V    |

| T <sub>stg</sub>       | Storage temperature                      | -65  | 150                   | °C   |

(1) Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

(2) All voltage values are with respect to the network ground terminal.

(3) While switching.

(4) The voltage at the pin can exceed the 6.5V absolute max condition for a short period of time, but must remain less than 8V. VIN at 8V for a 100ms duration is equivalent to approximately 8 hours of aging for the device at room temperature.

# 6.2 ESD Ratings - Q100

|                    |                            |                                                                                              | VALUE | UNIT |

|--------------------|----------------------------|----------------------------------------------------------------------------------------------|-------|------|

| V <sub>(ESD)</sub> | Electrostatic<br>discharge | Human body model (HBM), per AEC<br>Q100-002 <sup>(1)</sup><br>HBM ESD classification level 2 | ±2000 | V    |

| V <sub>(ESD)</sub> | Electrostatic<br>discharge | Charged device model (CDM) per AEC<br>Q100-011<br>CDM ESD classification level C5            | ±750  | V    |

(1) AEC Q100-002 indicates that HBM stressing must be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

# 6.3 Recommended Operating Conditions

Over operating temperature range (unless otherwise noted)

|                                          |                                                                    | MIN | NOM | MAX                                                      | UNIT |

|------------------------------------------|--------------------------------------------------------------------|-----|-----|----------------------------------------------------------|------|

| V <sub>IN</sub>                          | Input voltage range                                                | 2.7 |     | 6                                                        | V    |

| V <sub>OUT</sub>                         | Output voltage range                                               | 0.4 |     | .675 V or<br>(V <sub>IN</sub> – 1.5<br>V) <sup>(1)</sup> | V    |

| Voltage                                  | Nominal pull-up voltage on pins SDA and SCL                        | 1.2 |     | 5                                                        | V    |

| L                                        | Effective inductance for f <sub>SW</sub> = 1.5MHz                  | 100 | 150 | 200                                                      | nH   |

| L                                        | Effective inductance for $f_{SW}$ = 2.25MHz, 2.5MHz and 3MHz       | 40  | 100 | 200                                                      | nH   |

| C <sub>IN</sub>                          | Effective input capacitance per power input pin                    | 10  | 22  |                                                          | μF   |

| C <sub>OUT</sub>                         | Effective output capacitance                                       | 47  |     | (3)                                                      | μF   |

| C <sub>PAR</sub>                         | Parasitic capacitance on FSEL, VSEL pin                            |     |     | 100                                                      | pF   |

| C <sub>PAR</sub>                         | Parasitic capacitance on SYNC_OUT pin                              |     |     | 20                                                       | pF   |

| R <sub>EN</sub>                          | Pull-up resistance on EN pin                                       | 15  |     |                                                          | kΩ   |

| R <sub>VSEL</sub> ,<br>R <sub>FSEL</sub> | Resistance on VSEL, VSEL to GND if not directly tied to GND or VIN |     | 6.2 |                                                          | kΩ   |

6 資料に関するフィードバック(ご意見やお問い合わせ)を送信

Copyright © 2024 Texas Instruments Incorporated

Product Folder Links: TPS62874-Q1 TPS62875-Q1 TPS62876-Q1 TPS62877-Q1

# 6.3 Recommended Operating Conditions (続き)

Over operating temperature range (unless otherwise noted)

|                                          |                                                                    | MIN | NOM | MAX  | UNIT |

|------------------------------------------|--------------------------------------------------------------------|-----|-----|------|------|

| R <sub>VSEL</sub> ,<br>R <sub>FSEL</sub> | Resistance on VSEL, VSEL to VIN if not directly tied to GND or VIN |     | 47  |      | kΩ   |

| R <sub>VSEL</sub> ,<br>R <sub>FSEL</sub> | Resistor tolerance on VSEL, FSEL                                   |     |     | ± 2% |      |

| I <sub>SINK_PG</sub>                     | Sink current at PG pin                                             | 0   |     | 1    | mA   |

| TJ                                       | Operating junction temperature <sup>(2)</sup>                      | -40 |     | 150  | °C   |

(1) Whatever V<sub>OUT</sub> value is lower.

(2) Operating lifetime is derated at junction temperatures greater than 125°C.

(3) The maximum recommended output capacitance depends on the specific operating conditions of an application. Output capacitance values of up to a few millifarads are typically possible.

# 6.4 Thermal Information

|                       |                                                  | TPS6287x-Q1 | TPS6287x-Q1 |      |

|-----------------------|--------------------------------------------------|-------------|-------------|------|

|                       | C(top) Junction-to-case (top) thermal resistance | RZV (JEDEC) | RZV (EVM)   | UNIT |

|                       |                                                  | 24 PINS     | 24 PINS     |      |

| R <sub>0JA</sub>      | Junction-to-ambient thermal resistance           | 34.7        | 28          | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance        | 14.9        | -           | °C/W |

| R <sub>θJB</sub>      | Junction-to-board thermal resistance             | 6.5         | -           | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter       | 1.5         | -           | °C/W |

| Y <sub>JB</sub>       | Junction-to-board characterization parameter     | 6.5         | -           | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance     | 4.8         | -           | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application note.

# **6.5 Electrical Characteristics**

over operating junction temperature (T<sub>J</sub> = -40 °C to +150 °C) and V<sub>IN</sub> = 2.7 V to 6 V. Typical values at V<sub>IN</sub> = 5 V and T<sub>J</sub> = 25 °C (unless otherwise noted).

|                            | PARAMETER                                             | TEST CONDITIONS                                                        | MIN | TYP | MAX | UNIT |

|----------------------------|-------------------------------------------------------|------------------------------------------------------------------------|-----|-----|-----|------|

| SUPPLY                     |                                                       |                                                                        |     |     |     |      |

| l <sub>Q</sub>             | Quiescent current                                     | EN = High, I <sub>OUT</sub> = 0mA, device not<br>switching; MODE = Low |     | 2.1 | 3.8 | mA   |

| I <sub>SD</sub>            | Shutdown current                                      | EN = Low, $V_{(SW)}$ = 0 V, max value at T <sub>J</sub> = 125°C        |     | 18  | 450 | μA   |

| V <sub>IT+</sub><br>(UVLO) | Positive-going UVLO threshold voltage (VIN)           |                                                                        | 2.5 | 2.6 | 2.7 | V    |

| V <sub>IT-(UVLO)</sub>     | Negative-going UVLO threshold voltage (VIN)           |                                                                        | 2.4 | 2.5 | 2.6 | V    |

| V <sub>hys(UVLO</sub> )    | UVLO hysteresis voltage (VIN)                         |                                                                        | 80  |     |     | mV   |

| V <sub>IT+</sub><br>(ovlo) | Positive-going OVLO threshold voltage (VIN)           |                                                                        | 6.1 | 6.3 | 6.5 | V    |

| V <sub>IT-(OVLO)</sub>     | Negative-going OVLO threshold voltage (VIN)           |                                                                        | 6.0 | 6.2 | 6.4 | V    |

| V <sub>hys(OVLO</sub><br>) | OVLO hysteresis voltage (VIN)                         |                                                                        | 80  |     |     | mV   |

| V <sub>IT-(POR)</sub>      | Negative-going power-on reset threshold voltage (VIN) |                                                                        | 1.4 |     |     | V    |

| т                          | Thermal shutdown threshold temperature                | T <sub>J</sub> rising                                                  |     | 170 |     | °C   |

| T <sub>SD</sub>            | Thermal shutdown hysteresis                           |                                                                        |     | 20  |     | °C   |

Copyright © 2024 Texas Instruments Incorporated

資料に関するフィードバック(ご意見やお問い合わせ)を送信 7

# 6.5 Electrical Characteristics (続き)

over operating junction temperature (T<sub>J</sub> = -40 °C to +150 °C) and V<sub>IN</sub> = 2.7 V to 6 V. Typical values at V<sub>IN</sub> = 5 V and T<sub>J</sub> = 25 °C (unless otherwise noted).

|                      | PARAMETER                                                      | TEST CONDITIONS                                                                        | MIN  | TYP  | MAX  | UNIT |

|----------------------|----------------------------------------------------------------|----------------------------------------------------------------------------------------|------|------|------|------|

| т                    | Thermal warning threshold temperature                          | T <sub>J</sub> rising                                                                  |      | 150  |      | °C   |

| Τ <sub>W</sub>       | Thermal warning hysteresis                                     |                                                                                        |      | 20   |      | °C   |

| CONTRO               | DL and INTERFACE                                               |                                                                                        | 1    |      |      |      |

| V <sub>IT+</sub>     | Positive-going input threshold voltage (EN)                    |                                                                                        | 0.97 | 1.0  | 1.03 | V    |

| V <sub>IT-</sub>     | Negative-going input threshold voltage (EN)                    |                                                                                        | 0.87 | 0.9  | 0.93 | V    |

| V <sub>hys</sub>     | Hysteresis voltage (EN)                                        |                                                                                        | 95   |      |      | mV   |

| R <sub>(EN)</sub>    | Input resistance to GND (EN)                                   | Only active during start-up in stacked operation.                                      | 1.4  | 1.8  | 3    | kΩ   |

| I <sub>IH</sub>      | High-level input current (EN)                                  | V <sub>IH</sub> = V <sub>IN</sub> , internal pulldown resistor<br>disabled             |      |      | 3    | μA   |

| IL                   | Low-level input current (EN)                                   | V <sub>IL</sub> = 0V, internal pulldown resistor disabled                              | -200 |      |      | nA   |

| V <sub>IH</sub>      | High-level input voltage (MODE/SYNC, VSEL, FSEL, SYNC_OUT, PG) |                                                                                        | 0.8  |      |      | V    |

| V <sub>IH</sub>      | High-level input voltage (SDA, SCL)                            |                                                                                        | 0.95 |      |      | V    |

| V <sub>IL</sub>      | Low-level input voltage (MODE/SYNC, VSEL, FSEL, SYNC_OUT, PG)  |                                                                                        |      |      | 0.4  | V    |

| VIL                  | Low-level input voltage (SDA, SCL)                             |                                                                                        |      |      | 0.5  | V    |

| R <sub>IN</sub>      | Input resistance to GND on pins MODE/<br>SYNC, EN and PG       |                                                                                        | 2    | 3    | 4    | MΩ   |

| V <sub>OL</sub>      | Low-level output voltage (SDA)                                 | I <sub>OL</sub> = 9mA                                                                  |      |      | 0.4  | V    |

| V <sub>OL</sub>      | Low-level output voltage (SDA)                                 | I <sub>OL</sub> = 5mA                                                                  |      |      | 0.2  | V    |

| LKG                  | Input leakage current into SDA, SCL                            | V <sub>OH</sub> = 3.3V                                                                 |      |      | 200  | nA   |

| IIL                  | Low-level input current (MODE/SYNC)                            | V <sub>IL</sub> = 0V                                                                   | -100 |      | 100  | nA   |

| Ін                   | High-level input current (MODE/SYNC)                           | V <sub>IH</sub> = V <sub>IN</sub>                                                      |      |      | 3    | μA   |

| IIL                  | Low-level input current (SYNC_OUT)                             | V <sub>IL</sub> = 0V                                                                   | -230 |      |      | nA   |

| Ін                   | High-level input current (SYNC_OUT)                            | V <sub>IH</sub> = 2V                                                                   |      |      | 110  | nA   |

| V <sub>OL</sub>      | Low-level output voltage (SYNC_OUT)                            | I <sub>OL</sub> = 1mA                                                                  |      |      | 0.3  | V    |

| V <sub>OH</sub>      | High-level output voltage (SYNC_OUT)                           | I <sub>OH</sub> = 0.1mA                                                                | 1.3  |      | 2.1  | V    |

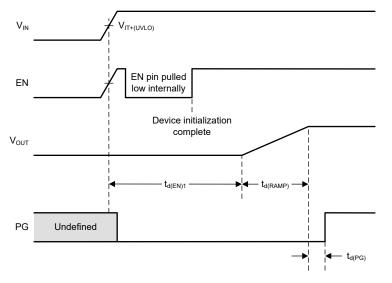

| t <sub>d(EN)1</sub>  | Enable delay time when EN tied to $V_{IN}$                     | Measured from when EN goes high to when device starts switching, $SR_{VIN} = 1V/\mu s$ |      | 200  | 600  | μs   |

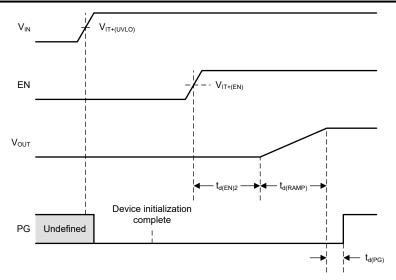

| t <sub>d(EN)2</sub>  | Enable delay time when V <sub>IN</sub> already applied         | Measured from when EN goes high to when device starts switching                        |      | 40   | 100  | μs   |

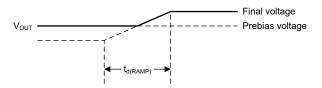

|                      | Output voltage ramp time for<br>CONTROL2[1:0] = 00             |                                                                                        | 0.35 | 0.5  | 0.65 | ms   |

| td/_                 | Output voltage ramp time for<br>CONTROL2[1:0] = 01             | Measured from when device starts                                                       | 0.54 | 0.77 | 1.0  | ms   |

| td( <sub>Ramp)</sub> | Output voltage ramp time for<br>CONTROL2[1:0] = 10, default    | switching to rising edge of PG                                                         | 0.7  | 1    | 1.3  | ms   |

|                      | Output voltage ramp time for<br>CONTROL2[1:0] = 11             |                                                                                        | 1.4  | 2    | 2.6  | ms   |

| f <sub>(SYNC)</sub>  | Synchronization clock frequency range (MODE/SYNC)              | f <sub>(SW)nom</sub> = 1.5MHz, D <sub>(MODE/SYNC)</sub> = 45%55%                       | 1.2  |      | 1.8  | MHz  |

|                      | Synchronization clock frequency range (MODE/SYNC)              | f <sub>(SW)nom</sub> = 2.25MHz, D <sub>(MODE/SYNC)</sub> = 45%55%                      | 1.8  |      | 2.7  | MHz  |

8 資料に関するフィードバック(ご意見やお問い合わせ)を送信

Copyright © 2024 Texas Instruments Incorporated

Product Folder Links: TPS62874-Q1 TPS62875-Q1 TPS62876-Q1 TPS62877-Q1

# 6.5 Electrical Characteristics (続き)

over operating junction temperature (T<sub>J</sub> = -40 °C to +150 °C) and V<sub>IN</sub> = 2.7 V to 6 V. Typical values at V<sub>IN</sub> = 5 V and T<sub>J</sub> = 25 °C (unless otherwise noted).

|                                          | PARAMETER                                                              | TEST CONDITIONS                                                                      | MIN   | TYP   | MAX  | UNIT |

|------------------------------------------|------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-------|-------|------|------|

|                                          | Synchronization clock frequency range (MODE/SYNC)                      | f <sub>(SW)nom</sub> = 2.5MHz, D <sub>(MODE/SYNC)</sub> =<br>45%55%                  | 2     |       | 3.0  | MHz  |

| f <sub>(SYNC)</sub>                      | Synchronization clock frequency range (MODE/SYNC)                      | f <sub>(SW)nom</sub> = 3MHz, D <sub>(MODE/SYNC)</sub> =<br>45%55%                    | 2.4   |       | 3.3  | MHz  |

| D <sub>(MODE/</sub><br><sub>SYNC</sub> ) | Duty cycle of synchronization clock<br>frequency (MODE/SYNC)           |                                                                                      | 45    |       | 55   | %    |

|                                          | Phase shift at SYNC_OUT with reference to internal CLK or external CLK | CONTROL2:SYNCH_OUT_PHASE = 0b0                                                       |       | 120   |      | ٥    |

|                                          | Phase shift at SYNC_OUT with reference to internal CLK or external CLK | CONTROL2:SYNCH_OUT_PHASE = 0b1                                                       |       | 180   |      | o    |

|                                          | Time to lock to external frequency                                     |                                                                                      |       | 50    |      | μs   |

|                                          | Resistance on FSEL, VSEL to GND if not tied to GND directly            |                                                                                      |       | 6.2   |      | kΩ   |

|                                          | Resistance on FSEL, VSEL to VIN if not tied to VIN directly            |                                                                                      |       | 47    |      | kΩ   |

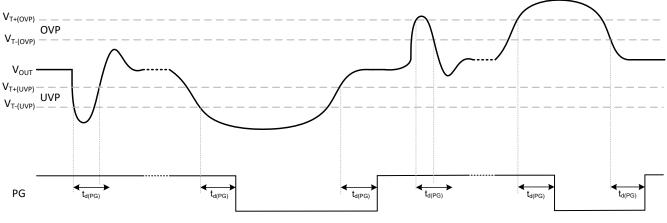

| V <sub>T+(UVP)</sub>                     | Positive-going power good threshold voltage (output undervoltage)      |                                                                                      | 94    | 96    | 98   | %    |

| V <sub>T-(UVP)</sub>                     | Negative-going power good threshold voltage (output undervoltage)      |                                                                                      | 92    | 94    | 96   | %    |

| V <sub>T+(OVP)</sub>                     | Positive-going power good threshold voltage (output overvoltage)       |                                                                                      | 104   | 106   | 108  | %    |

| V <sub>T-(OVP)</sub>                     | Negative-going power good threshold voltage (output overvoltage)       |                                                                                      | 102   | 104   | 106  | %    |

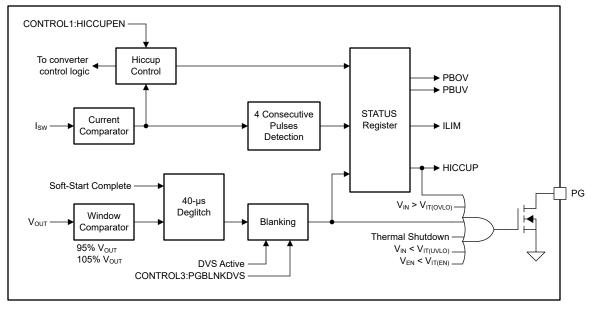

| V <sub>OL</sub>                          | Low-level output voltage (PG)                                          | I <sub>OL</sub> = 1mA                                                                |       | 0.012 | 0.3  | V    |

| I <sub>OH</sub>                          | High-level output current (PG)                                         | V <sub>OH</sub> = 5V                                                                 |       |       | 3    | μA   |

| I <sub>IH</sub>                          | High-level input current (PG)                                          | Device configured as secondary device in stacked operation                           |       |       | 3    | μA   |

| IIL                                      | Low-level input current (PG)                                           | Device configured as secondary device in stacked operation                           | -1    |       |      | μA   |

| t <sub>d(PG)</sub>                       | Deglitch time (PG)                                                     | High-to-low or low-to-high transition on the PG pin                                  | 34    | 40    | 46   | μs   |

| OUTPUT                                   |                                                                        |                                                                                      |       |       |      |      |

| ΔV <sub>OUT</sub>                        | Output voltage accuracy                                                | $V_{IN} \ge V_{OUT} + 1.6V$ , droop compensation disabled                            | -0.8  |       | 0.8  | %    |

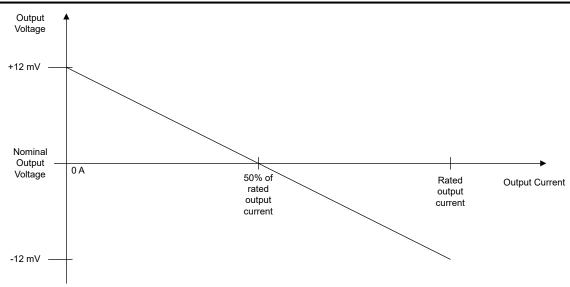

| ΔV <sub>OUT</sub>                        | Output voltage change from no current to rated current                 | droop compensation enabled                                                           |       | ±12   |      | mV   |

|                                          | Accuracy of droop compensation voltage;<br>TPS62874-Q1                 | device in forced PWM mode                                                            | -3.75 |       | 3.75 | mV   |

|                                          | Accuracy of droop compensation voltage;<br>TPS62875-Q1                 | device in forced PWM mode                                                            | -3.5  |       | 3.5  | mV   |

|                                          | Accuracy of droop compensation voltage;<br>TPS62876-Q1 and TPS62877-Q1 | device in forced PWM mode                                                            | -3    |       | 3    | mV   |

|                                          | Line regulation                                                        | I <sub>OUT</sub> = 15A, V <sub>IN</sub> ≥ V <sub>OUT</sub> + 1.6V                    |       | 0.02  |      | %/V  |

| I <sub>IB</sub>                          | Input bias current (GOSNS)                                             | EN = High; $V_{(GOSNS)}$ = -100mV to 100mV                                           | -60   |       | 3    | μA   |

| I <sub>IB</sub>                          | Input bias current (VOSNS)                                             | V <sub>(VOSNS)</sub> = 1.675 V, V <sub>IN</sub> = 6V, droop<br>compensation disabled | -5.5  |       | 5.5  | μA   |

| I <sub>IB</sub>                          | Input bias current (VOSNS)                                             | V <sub>(VOSNS)</sub> = 1.675V, V <sub>IN</sub> = 6V, droop<br>compensation enabled   | -13.2 |       | 13.2 | μA   |

| V <sub>ICR</sub>                         | Input common-mode range (GOSNS)                                        |                                                                                      | -100  |       | 100  | mV   |

Copyright © 2024 Texas Instruments Incorporated

資料に関するフィードバック(ご意見やお問い合わせ)を送信 9

# 6.5 Electrical Characteristics (続き)

over operating junction temperature (T<sub>J</sub> = -40 °C to +150 °C) and V<sub>IN</sub> = 2.7 V to 6 V. Typical values at V<sub>IN</sub> = 5 V and T<sub>J</sub> = 25 °C (unless otherwise noted).

| PARAMETER              |                                                                | TEST CONDITIONS                                                     | MIN                  | TYP      | MAX                | X UNIT |

|------------------------|----------------------------------------------------------------|---------------------------------------------------------------------|----------------------|----------|--------------------|--------|

| R <sub>DIS</sub>       | Output discharge resistance                                    | V <sub>OUT</sub> ≤ 1V                                               |                      | 2.7      | 9.2                | Ω      |

|                        |                                                                | f <sub>SW</sub> = 1.5MHz, PWM operation                             | 1.35                 | 1.5      | 1.65               | MHz    |

| c                      |                                                                | f <sub>SW</sub> = 2.25MHz, PWM operation                            | 2.025                | 2.25     | 2.475              | MHz    |

| f <sub>SW</sub>        | Switching frequency (SW)                                       | f <sub>SW</sub> = 2.5MHz, PWM operation                             | 2.25                 | 2.5      | 2.75               | MHz    |

|                        |                                                                | f <sub>SW</sub> = 3MHz, PWM operation                               | 2.7                  | 3        | 3.3                | MHz    |

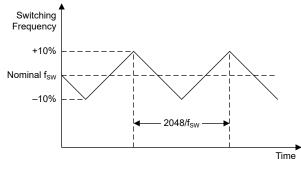

| f <sub>SSC</sub>       | Modulation frequency                                           |                                                                     | -                    | fsw/2048 |                    | kHz    |

| ∆f <sub>SW</sub>       | Switching frequency variation during spread spectrum operation |                                                                     | f <sub>SW</sub> –10% | f        | <sub>SW</sub> +10% |        |

| gm                     | Transconductance of OTA on COMP pin                            |                                                                     |                      | 1.5      |                    | mS     |

| г                      | Emulated current time constant                                 |                                                                     | 11.87                | 12.5     | 13.2               | μs     |

| R <sub>DS(ON)</sub>    | High-side FET static on-resistance                             | V <sub>IN</sub> = 3.3V                                              |                      | 3.4      | 6.4                | mΩ     |

| R <sub>DS(ON)</sub>    | Low-side FET static on-resistance                              | V <sub>IN</sub> = 3.3V                                              |                      | 1.9      | 3.6                | mΩ     |

| I <sub>(SW)(off)</sub> | SW pin current when HS-FET and LS-<br>FET are off              | V <sub>IN</sub> = 6V; V <sub>(SW)</sub> = 0V, T <sub>J</sub> = 25°C | -1.5                 |          | 0.1                | μA     |

|                        | SW pin current when HS-FET and LS-<br>FET are off              | V <sub>IN</sub> = 6V; V <sub>(SW)</sub> = 6V, T <sub>J</sub> = 25°C | 60                   |          | 130                | μA     |

|                        | SW pin current when HS-FET and LS-<br>FET are off              | V <sub>(SW)</sub> = 0.4V, current into SW pin                       |                      | 11       | 3000               | μA     |

| ILIM                   | High-side FET forward switch current limit, DC                 | TPS62874-Q1                                                         | 19                   | 22.5     | 26                 | А      |

| ILIM                   | High-side FET forward switch current limit, DC                 | TPS62875-Q1                                                         | 24                   | 28.5     | 32                 | А      |

| ILIM                   | High-side FET forward switch current limit, DC                 | TPS62876-Q1                                                         | 29                   | 34       | 39                 | А      |

| ILIM                   | High-side FET forward switch current limit, DC                 | TPS62877-Q1                                                         | 34                   | 39       | 44                 | А      |

| ILIM                   | Low-side FET forward switch current limit, DC                  | TPS62874-Q1                                                         | 15                   | 20       | 24                 | А      |

| LIM                    | Low-side FET forward switch current limit, DC                  | TPS62875-Q1                                                         | 20                   | 24.5     | 29                 | А      |

| ILIM                   | Low-side FET forward switch current limit, DC                  | TPS62876-Q1                                                         | 24.5                 | 29       | 33                 | А      |

| LIM                    | Low-side FET forward switch current limit, DC                  | TPS62877-Q1                                                         | 29.5                 | 33.5     | 38                 | А      |

| ILIM                   | Low-side FET negative current limit, DC                        |                                                                     |                      | -10      |                    | А      |

| t <sub>on, min</sub>   | Minimum on-time of HS FET                                      | V <sub>IN</sub> = 3.3V                                              |                      | 45       | 53                 | ns     |

| on, min                | Minimum on-time of HS FET                                      | V <sub>IN</sub> = 5V                                                |                      | 35       | 44                 | ns     |

| t <sub>off, min</sub>  | Minimum off-time of HS FET                                     | V <sub>IN</sub> = 5V                                                |                      | 70       | 100                | ns     |

|                        | Maximum duty cycle of power stage                              | for TPS62877-Q1 only                                                |                      | 45       |                    | %      |

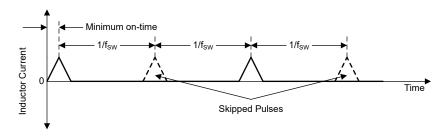

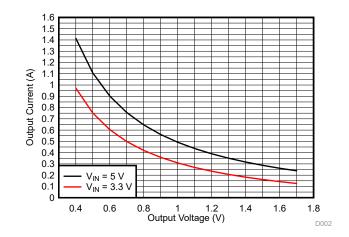

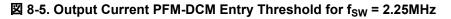

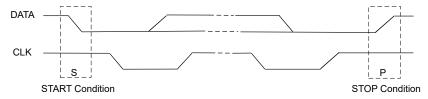

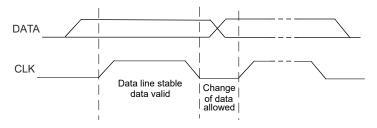

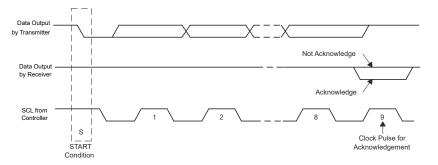

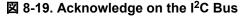

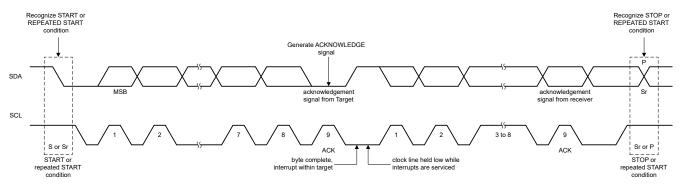

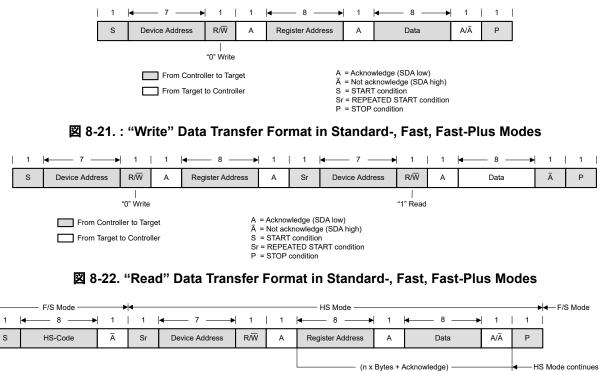

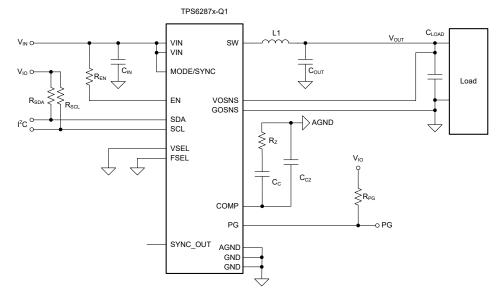

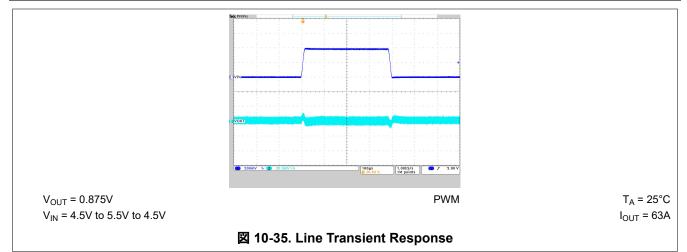

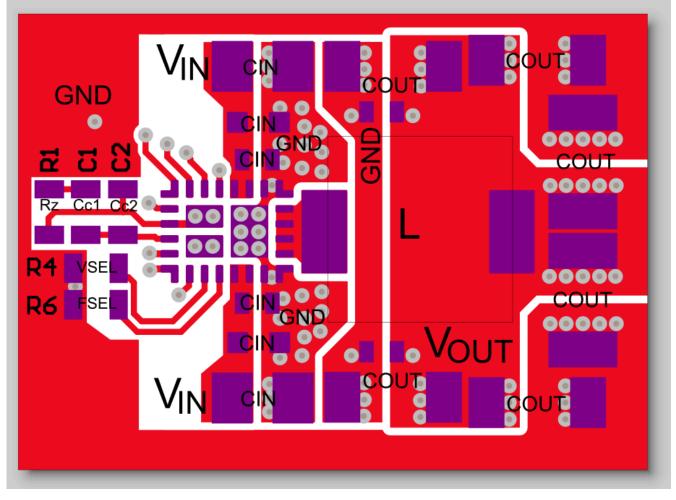

# 6.6 I<sup>2</sup>C Interface Timing Characteristics