Technical documentation

Support & training

UCC25800-Q1, UCC25800B-Q1

JAJSLJ6C – NOVEMBER 2020 – REVISED AUGUST 2023

# UCC25800-Q1 絶縁型バイアス電源向け、超低 EMI トランス・ドライバ

# 1 特長

TEXAS

- 高効率ハーフブリッジ・トランス・ドライバ

- 低い巻線間容量により極めて低い EMI

- トランスの小型化および低コスト化

- 周波数をプログラム可能:0.1MHz~1.2MHz

広い入力電圧範囲:9V~34V

- 34V 入力で 9W

INSTRUMENTS

- 24V 入力で 6W

- 15V 入力で 4W

- 最大デッドタイム・プログラミングによる自動デ ッドタイム調整

- 外部クロック同期により低ノイズ

- 堅牢な保護機能

- 低電圧誤動作防止 (UVLO)

- プログラム可能な過電流保護 (OCP)

- 入力過電圧保護 (OVP)

- 過熱保護 (TSD)

- 内蔵ソフトスタートにより突入電流を低減

- 外部ディセーブル機能とフォルト・コード出力

- 車載アプリケーション用に AEC-Q100 認定取得済み:

- 温度グレード1:-40℃~+125℃、T<sub>A</sub>

- 機能安全対応

機能安全システムの設計に役立つ資料を利用可

能

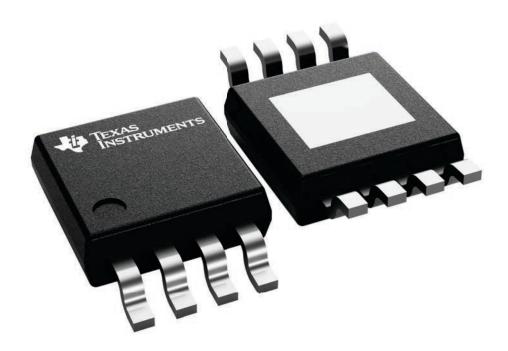

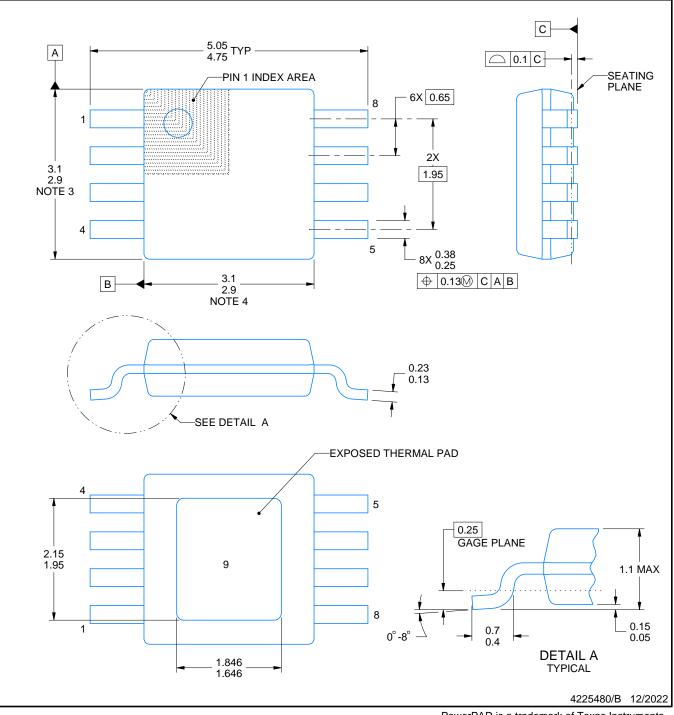

- サーマル・パッド付き 8 ピン DGN パッケージ

2 アプリケーション

- 車載用トラクション・インバータおよびモータ制御

- 車載用オンボード充電器 (OBC)

- ・ 車載用 DC/DC コンバータ

- EV 充電ステーション、 DC 高速充電ステーション

- ・ UPS およびソーラー・インバータ

- 産業用モーター、エレベータ、エスカレータ

- GaN、IGBT、SiC ゲート・トランス・ドライバの バイアス電源

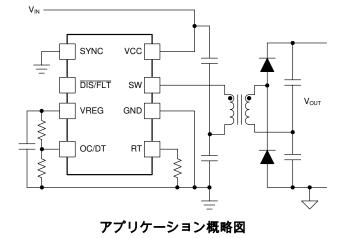

#### 3 概要

UCC25800-Q1は、スイッチング電力段、制御回路、 保護回路を統合した 超低 EMI トランス・ドライバで あり、絶縁型バイアス電源の設計を簡素化します。こ の設計では、漏れインダクタンスの大きい変圧器を使 っても、1次側から2次側への寄生容量をかなり小さ くできます。この低容量トランスの設計では、バイア ス・トランスを通過する同相モード電流注入が大幅に 低下します。このため、このトランス・ドライバは、 高速スイッチング・デバイスにより発生する EMI ノ イズを最小限に抑えることができ、さまざまな車載ア プリケーションの絶縁型バイアス電源向けの理想的な ソリューションとなります。ソフト・スイッチング機 能は、EMI ノイズをさらに低減します。

このトランス・ドライバの周波数は、100kHz~ 1.2MHz の範囲でプログラム可能です。この高いスイ ッチング周波数により、変圧器のサイズとフットプリ ント、およびバイアス電源の全体的なコストが削減さ れます。内蔵の SYNC 機能を使ってシステム・バイ アス電源を外部クロック信号と同期させると、システ ム・レベルのノイズをさらに低減できます。

デッドタイムは、導通損失を最小化するように自動的 に調整されるので、設計を簡素化できます。プログラ ム可能な最大デッドタイムにより、出力段の設計の柔 軟性が確保されています。

このトランス・ドライバは、低抵抗のスイッチング電 力段を内蔵しているので、24V入力で6W、34V入力 で最大 9W の設計を実現できます。固定入力電圧の 場合、開ループ制御は、負荷が 10% を上回ったとき でも出力レギュレーションを±5% に維持するのにも 役立ちます。

プログラム可能な過電流保護 (OCP) により、電源段 の設計の柔軟性を高め、変圧器のサイズを最小化でき ます。可変 OCP、入力 OVP、TSD、ピン障害からの 保護などの保護機能により、堅牢な動作が保証されま す。1.5msの固定ソフトスタート期間により、スター トアップ時およびフォルト回復時の突入電流を低減し ます。

また、このトランス・ドライバには、外部ディセーブ ル、およびフォルト・コード通知のための専用マルチ ファンクション・ピンもあります。バイアス電源が保 護モードになると、フォルト・コード通知機能により フォルト・コードが送信されます。

UCC25800-Q1 トランス・ドライバは、サーマル・パ ッド付き 8 ピン DGN パッケージで供給され、温度に 関する対応能力を強化しています。

製品情報

| 部品番号        | パッケージ <sup>(1)</sup> | 本体サイズ (公称)      |

|-------------|----------------------|-----------------|

| UCC25800-Q1 | HVSSOP (8)           | 3.00mm × 3.00mm |

(1) 利用可能なすべてのパッケージについては、データシートの 末尾にある注文情報を参照してください。

英語版の TI 製品についての情報を翻訳したこの資料は、製品の概要を確認する目的で便宜的に提供しているものです。該当する正式な英語版の最新情報 は、www.ti.com で閲覧でき、その内容が常に優先されます。TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計など の前には、必ず最新版の英語版をご参照くださいますようお願いいたします。

# **Table of Contents**

| 1 特長                                 | . 1 |

|--------------------------------------|-----|

| 2アプリケーション                            |     |

| 3 概要                                 | . 1 |

| 4 Revision History                   | . 3 |

| 5 Device Comparison Table            | 4   |

| 6 Pin Configuration and Functions    |     |

| 7 Specifications                     | . 6 |

| 7.1 Absolute Maximum Ratings         |     |

| 7.2 ESD Ratings                      | . 6 |

| 7.3 Recommended Operating Conditions | 6   |

| 7.4 Thermal Information              | 7   |

| 7.5 Electrical Characteristics       |     |

| 7.6 Typical Characteristics          | . 9 |

| 8 Detailed Description               | 11  |

| 8.1 Overview                         | 11  |

| 8.2 Functional Block Diagram         |     |

| 8.3 Feature Description              |     |

| 8.4 Device Functional Modes          | 25  |

| 9 Application and Implementation        | 27 |

|-----------------------------------------|----|

| 9.1 Application Information             | 27 |

| 9.2 Typical Application                 | 27 |

| 9.3 What to Do and What Not to Do       | 35 |

| 10 Power Supply Recommendations         | 36 |

| 11 Layout                               |    |

| 11.1 Layout Guidelines                  | 37 |

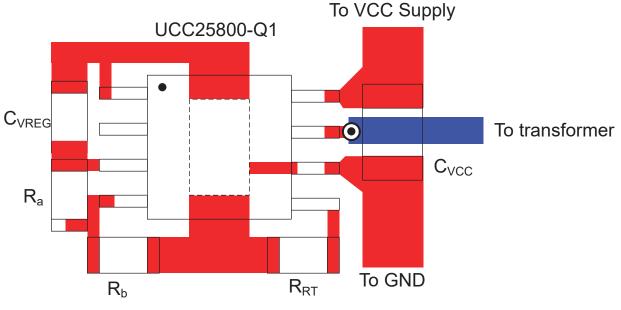

| 11.2 Layout Example                     | 37 |

| 12 Device and Documentation Support     |    |

| 12.1 Documentation Support              | 38 |

| 12.2 ドキュメントの更新通知を受け取る方法                 | 38 |

| 12.3 サポート・リソース                          | 38 |

| 12.4 Trademarks                         |    |

| 12.5 静電気放電に関する注意事項                      |    |

| 12.6 用語集                                | 38 |

| 13 Mechanical, Packaging, and Orderable |    |

| Information                             | 39 |

|                                         |    |

# **4 Revision History** 資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Changes from Revision B (November 2021) to Revision C (August 2023)                              | Page |

|--------------------------------------------------------------------------------------------------|------|

| <ul> <li>UCC25800B-Q1 デバイスの初版リリース</li> <li>Updated to include new device UCC25800B-Q1</li> </ul> |      |

| <ul> <li>Updated to include fault mode implications of new device UCC25800B-Q1</li> </ul>        |      |

| Changes from Revision A (July 2021) to Revision B (November 2021)                                | Page |

| <u> </u> | hanges nom kevision A (July 202 |                 |                 | 2021) i dy | - |

|----------|---------------------------------|-----------------|-----------------|------------|---|

| •        | データシートのステータスを「 <i>事</i>         | <i>前情報</i> 」から「 | <i>「量産データ</i> 」 | に変更        | 1 |

# **5 Device Comparison Table**

| Part Number  | OCP1<br>Protection |

|--------------|--------------------|

| UCC25800-Q1  | Enable             |

| UCC25800B-Q1 | Disable            |

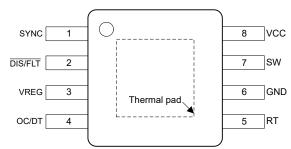

# **6** Pin Configuration and Functions

# 図 6-1. DGN Package, 8-Pin PDSO (Top View)

#### 表 6-1. Pin Functions

| PIN         |                                                                                                                                                                                                                                                                                                                                                 |     | DESCRIPTION                                                                                                                                                                                                     |  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME        | NO.                                                                                                                                                                                                                                                                                                                                             |     | DESCRIPTION                                                                                                                                                                                                     |  |

| DIS/FLT     | 2                                                                                                                                                                                                                                                                                                                                               | I/O | UCC25800-Q1 disable pin (active low) and fault code output pin.                                                                                                                                                 |  |

| GND         | 6                                                                                                                                                                                                                                                                                                                                               | G   | The GND pin is the return for all the control and power signals. The layout should separate the power and control signals.                                                                                      |  |

| OC/DT       | 4                                                                                                                                                                                                                                                                                                                                               | I   | Voltage on this pin sets the maximum dead-time between the internal switching power devices.<br>The Thevenin resistance on the pin is measured at start-up to set the OCP level.                                |  |

| RT          | 5                                                                                                                                                                                                                                                                                                                                               | _   | Switching frequency setting pin. Connect a resistor from RT pin to GND to set the converter witching frequency. The RT pin can be left open to operate the converter at the default 1.2-MHz witching frequency. |  |

| SW          | 7                                                                                                                                                                                                                                                                                                                                               | -   | The switch node of the integrated half-bridge. Connect this pin directly to the transformer.                                                                                                                    |  |

| SYNC        | 1                                                                                                                                                                                                                                                                                                                                               | I   | External clock input for frequency synchronization. The internal MOSFETs are switched synchronized with the rising edge of the SYNC signal, with half of the SYNC pin signal frequency.                         |  |

| VCC         | 8 The input for power and control of UCC25800-Q1. A good high-frequency by-pass capacitor between VCC and GND is needed to ensure high-efficiency, low-EMI design. Use the bypass capacitor layout to minimize the VCC-GND-bypass capacitor loop to reduce the stresses on internal power devices. Referring to セクション 11 for layout guidelines. |     | between VCC and GND is needed to ensure high-efficiency, low-EMI design. Use the bypass capacitor layout to minimize the VCC-GND-bypass capacitor loop to reduce the stresses on                                |  |

| VREG        | 3                                                                                                                                                                                                                                                                                                                                               | 0   | Internal regulated reference. Put a decoupling capacitor right across VREG pin and GND with shortest distance. The VREG pin can also be used as an external supply.                                             |  |

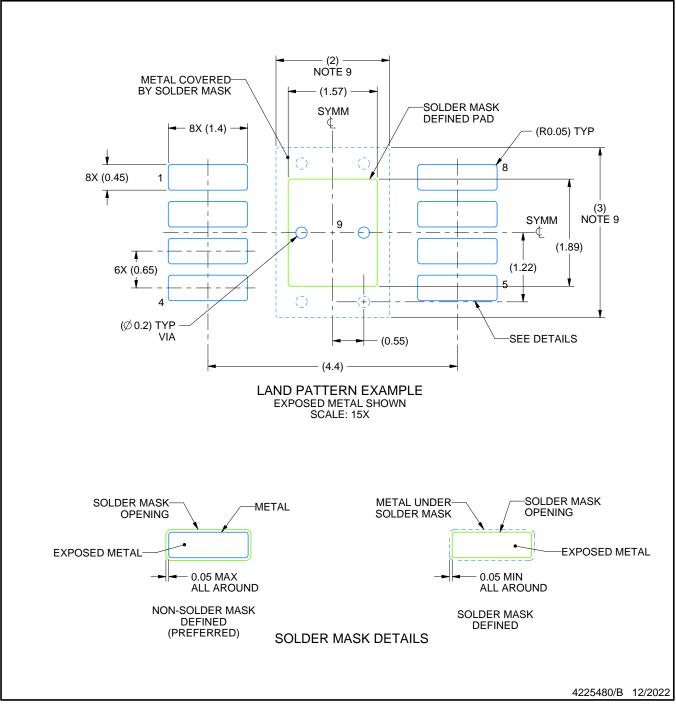

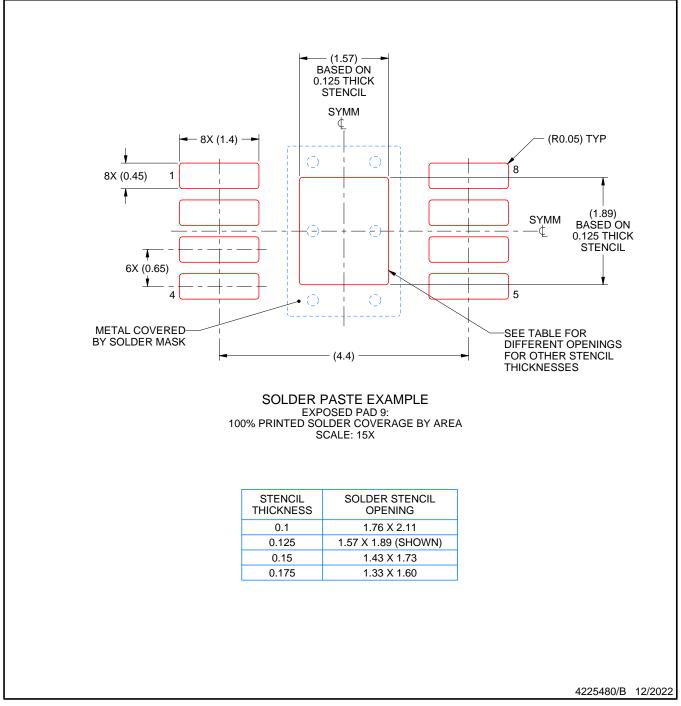

| Thermal Pad |                                                                                                                                                                                                                                                                                                                                                 | _   | Connect this pad to GND pin to provide thermal management for the device. Thermal vias are recommended if the design uses multilayer PCB.                                                                       |  |

(1) I = input, O = output, I/O = input or output, FB = feedback, G = ground, P = power

# 7 Specifications

# 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                   |                           | MIN                           | MAX                            | UNIT |

|-------------------|---------------------------|-------------------------------|--------------------------------|------|

| VCC               |                           | -0.3                          | 40                             | V    |

| VREG              |                           | -0.3                          | 5.5                            | V    |

| RT                |                           | -0.3                          | 5.5                            | V    |

| DIS/FLT           |                           | -0.3                          | 5.5                            | V    |

| SYNC              |                           | -0.3                          | 5.5                            | V    |

| OC/DT             |                           | -0.3                          | 5.5                            | V    |

|                   | Pin voltage               | -1                            | VCC + 1                        | V    |

|                   | Current transient (100ns) | -7                            | 7                              | А    |

| SW                | Voltage transient (50ns)  | higher of -5V or<br>(VCC-41V) | Lower of<br>(VCC+5V) or<br>41V | V    |

| I <sub>Qrms</sub> | MOSFET RMS current        |                               | 600                            | mA   |

| TJ                | Junction temperature      | -40                           | 150                            | °C   |

| T <sub>AMB</sub>  | Ambient temperature       | -40                           | 125                            | °C   |

| T <sub>stg</sub>  | Storage temperature       | -65                           | 150                            | °C   |

(1) Stresses beyond those listed under Absolute Maximum Rating may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Condition. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 7.2 ESD Ratings

|                    |                         |                                                                                          |                                        | VALUE | UNIT |

|--------------------|-------------------------|------------------------------------------------------------------------------------------|----------------------------------------|-------|------|

|                    |                         | Human body model (HBM), per AEC Q100-002 <sup>(1)</sup> ±HBM ESD classification level 2± |                                        | ±2000 | V    |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per<br>AEC Q100-011                                          | Corner pins (SYNC, OC/DT, RT, and VCC) | ±750  | V    |

|                    |                         | CDM ESD classification level C4B                                                         | Other pins                             | ±500  | V    |

(1) AEC Q100-002 indicates that HBM stressing must be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

# 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                      |                                      | MIN | NOM MAX | UNIT |

|----------------------|--------------------------------------|-----|---------|------|

| VCC                  | Supply voltage                       | 9   | 34      | V    |

| VREG                 | VREG current                         | 0   | 1       | mA   |

| C <sub>VREG</sub>    | VREG capacitor                       | 0.1 | 1       | μF   |

| R <sub>RT</sub>      | Switching frequency set pin resistor | 10  |         | kΩ   |

| C <sub>RT</sub>      | Capacitor on RT                      |     | 1000    | pF   |

| DIS/FLT              | Disable pin                          | 0   | VREG    | V    |

| OC/DT                | OCP/Dead Time setting pin            | 1   | 3.9     | V    |

| R <sub>OC/DT</sub>   | Thevenin resistance                  | 2.5 | 22.7    | kΩ   |

| C <sub>OC/DT</sub>   | Capacitor on OC/DT                   |     | 1000    | pF   |

| SYNC                 | External sync input voltage          | 0   | VREG    | V    |

| •                    | Minimum SYNC pulse width, high       | 150 |         | ns   |

| t <sub>SYNCmin</sub> | Minimum SYNC pulse width, low        | 150 |         | ns   |

over operating free-air temperature range (unless otherwise noted)

|                    |                                                   | MIN  | NOM MAX   | UNIT |

|--------------------|---------------------------------------------------|------|-----------|------|

| SW                 | Half bridge output pin                            | -0.6 | VCC + 0.6 | V    |

| f <sub>SW</sub>    | Switching frequency range                         | 100  | 1200      | kHz  |

| IQ <sub>RMS</sub>  | Internal MOSFET RMS current rating                |      | 500       | mA   |

| IQ <sub>Peak</sub> | Internal MOSFET peak current rating, steady state |      | 1         | А    |

# 7.4 Thermal Information

|                       |                                              | UCC25800-Q1  |      |

|-----------------------|----------------------------------------------|--------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | DGN (HVSSOP) | UNIT |

|                       |                                              | 8 PINS       |      |

| R <sub>OJA</sub>      | Junction-to-ambient thermal resistance       | 47.9         | °C/W |

| R <sub>OJC(top)</sub> | Junction-to-case (top) thermal resistance    | 59.1         | °C/W |

| R <sub>OJB</sub>      | Junction-to-board thermal resistance         | 18.4         | °C/W |

| ΨJT                   | Junction-to-top characterization parameter   | 1.6          | °C/W |

| Ψјв                   | Junction-to-board characterization parameter | 18.4         | °C/W |

| R <sub>OJC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 5.6          | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

#### 7.5 Electrical Characteristics

Unless otherwise stated:  $V_{VCC}$  = 15 V,  $R_{RT}$  = open,  $C_{VREG}$  = 470 nF, and -40 °C <T<sub>J</sub> =T<sub>A</sub> < 125 °C

|                      | PARAMETER                                                  | TEST CONDITIONS                                                                         | MIN  | TYP  | MAX  | UNIT |

|----------------------|------------------------------------------------------------|-----------------------------------------------------------------------------------------|------|------|------|------|

| SUPPLY VOLT          | AGE                                                        | · · · · · ·                                                                             |      |      |      |      |

| UVLO <sub>R</sub>    | VCC turn on threshold                                      | VCC rising                                                                              | 8    | 8.6  | 9    | V    |

| UVLO <sub>F</sub>    | VCC turn off threshold                                     | VCC falling                                                                             | 7.5  | 8    | 8.5  | V    |

| OV <sub>SD</sub>     | VCC overvoltage shutdown threshold                         | VCC rising                                                                              | 35   | 37   | 39   | V    |

| OV <sub>RS</sub>     | VCC overvoltage reset                                      | VCC falling                                                                             | 34   | 36   | 38   | V    |

| OV <sub>BLNK</sub>   | Overvoltage blanking time                                  | V <sub>VCC</sub> = 40 V                                                                 | 0.75 | 1.3  | 2    | μs   |

| SUPPLY CURR          | ENT                                                        | · · · · ·                                                                               |      |      | I    |      |

| IVCC <sub>UVLO</sub> | VCC current during UVLO                                    | V <sub>VCC</sub> = 7.5 V                                                                |      | 200  | 500  | μA   |

| IVCC <sub>RUN</sub>  | Input current, not including<br>FET current <sup>(3)</sup> | $f_{SW}$ = 1.2 MHz, $\overline{DIS/FLT}$ = 1, SW open,<br>$I_{VREG}$ = 0 mA, VCC = 12 V |      | 14   | 20   | mA   |

| IVCC <sub>DIS</sub>  | Supply current when disabled                               | No switching, $\overline{\text{DIS}/\text{FLT}} = 0$ , $I_{\text{VREG}} = 0$ mA         |      | 660  | 800  | μA   |

| VREG OUTPUT          | Г                                                          |                                                                                         |      |      |      |      |

| VREG                 | Internal regulated reference                               | I <sub>VREG</sub> = 0 mA, DIS/FLT = 0                                                   | 4.75 | 5    | 5.25 | V    |

| VREG <sub>LINE</sub> | Line Regulation                                            | $I_{VREG}$ = 0 mA, 9 V ≤ $V_{VCC}$ ≤ 34 V                                               |      |      | 10   | mV   |

| VREG <sub>LOAD</sub> | Load Regulation                                            | 0 mA ≤ I <sub>VREG</sub> ≤ 1 mA                                                         | -100 |      |      | mV   |

| VREG <sub>OK</sub>   | Threshold for VREG GOOD                                    | VREG rising                                                                             | 4.05 | 4.5  | 4.95 | V    |

| VREG <sub>LOW</sub>  | VREG fault threshold                                       | VREG falling                                                                            | 3.6  | 4    | 4.4  | V    |

| MOSFETs              | · · · ·                                                    | · · · ·                                                                                 |      |      | I    |      |

| DDCON                | On Basistanas                                              | PMOS I <sub>SW</sub> = -500 mA                                                          |      | 0.45 | 0.75 | Ω    |

| RDSON                | On Resistance                                              | NMOS I <sub>SW</sub> = +500 mA                                                          |      | 0.3  | 0.5  | Ω    |

| OSCILLATOR           |                                                            | 1                                                                                       |      |      |      |      |

|                         | PARAMETER                                                   | TEST CONDITIONS                                                       | MIN   | TYP | MAX   | UNIT |

|-------------------------|-------------------------------------------------------------|-----------------------------------------------------------------------|-------|-----|-------|------|

|                         |                                                             | V <sub>RT</sub> = 0.25 V                                              | 94    | 100 | 106   | kHz  |

| f <sub>SW</sub>         | SW switching frequency                                      | V <sub>RT</sub> = 2.5 V                                               | 0.94  | 1   | 1.06  | MHz  |

|                         |                                                             | Default switching frequency, RT open                                  | 1.128 | 1.2 | 1.272 | MHz  |

| f <sub>SWtol</sub>      | Tolerance                                                   | 10 kΩ $\leq$ R <sub>RT</sub> $\leq$ 100 kΩ                            | 94    |     | 106   | %    |

| Duty                    | Duty cycle                                                  | RT open                                                               | 49    | 50  | 51    | %    |

| RT <sub>SHORT</sub>     | Short circuit fault theshold                                |                                                                       | 130   | 150 | 170   | mV   |

| RT <sub>OPEN</sub>      | Open-circuit default f <sub>OSC</sub> threshold             |                                                                       | 2.9   | 3   | 3.1   | V    |

| SYNC                    | <u> </u>                                                    |                                                                       |       |     |       |      |

| SYNC <sub>RISNG</sub>   | SYNC rising threshold                                       | V <sub>SYNC</sub> rising                                              | 2.0   | 2.2 | 2.4   | V    |

| SYNC <sub>FALLING</sub> | SYNC falling threshold                                      | V <sub>SYNC</sub> falling                                             | 1.53  | 1.7 | 1.87  | V    |

| ADAPTIVE DEAL           | D-TIME                                                      |                                                                       |       |     |       |      |

| DT_HS <sub>TH</sub>     | High-side dead-time detection threshold with respect to VCC | SW rising                                                             | -1.2  | -1  | -0.8  | V    |

| DT_LS <sub>TH</sub>     | Low-side dead-time detection threshold                      | SW falling                                                            | 0.8   | 1   | 1.2   | V    |

| DT_HS <sub>DELAY</sub>  | High-side turn on delay                                     | From SW crossing DT_HS <sub>TH</sub> to HS turning on                 |       | 20  | 45    | ns   |

| DT_LS <sub>DELAY</sub>  | Low-side turn on delay                                      | From SW crossing $\text{DT}_{\text{LS}_{\text{TH}}}$ to LS turning on |       | 20  | 45    | ns   |

| PROGRAMMABI             | LE MAXIMUM DEAD-TIME                                        |                                                                       |       |     |       |      |

| OC/DT <sub>SHORT</sub>  | short threshold for OC/DT pin                               |                                                                       | 450   | 500 | 550   | mV   |

| OC/DT <sub>OPEN</sub>   | open threshold for OC/DT pin                                |                                                                       | 4.3   | 4.5 | 4.7   | V    |

| DT <sub>MAX</sub>       | Programmable maximum                                        | V <sub>OC/DT</sub> = 3.9 V                                            | 45    | 50  | 55    | ns   |

| DIMAX                   | dead-time                                                   | V <sub>OC/DT</sub> = 1.9 V                                            | 135   | 150 | 165   | ns   |

| OVER-CURREN             | T PROTECTION                                                |                                                                       |       |     |       |      |

| I <sub>OCP1max</sub>    | First level maximum OCP setting threshold                   | Low side only                                                         | 0.9   | 1   | 1.1   | А    |

| OCP1 <sub>TO</sub>      | OCP1 time out                                               | Peak current exceeds threshold time out to trigger OCP1 fault         | 1.9   | 2.1 | 2.3   | ms   |

| I <sub>OCP2max</sub>    | Second level maximum OCP threshold                          | Low side and high side                                                | 4.25  | 5   | 5.75  | А    |

| OCP2 <sub>FILTER</sub>  | OCP2 filter time                                            | Continuous over-current to trigger OCP2 fault, low side and high side | 80    | 100 | 120   | ns   |

| OVER-TEMPER/            | ATURE PROTECTION                                            |                                                                       |       |     |       |      |

| TSD                     | Thermal shutdown threshold                                  | $T_{\rm J} = T_{\rm A} ^{(1)}$                                        |       | 160 |       | °C   |

| T <sub>HYST</sub>       | Hysteresis                                                  | $T_{J} = T_{A}^{(1)}$                                                 |       | 20  |       | °C   |

| ENABLE_DISAB            |                                                             |                                                                       |       |     |       |      |

| EN <sub>TH</sub>        | Enable threshold                                            | DIS/FLT rising                                                        | 2     | 2.2 | 2.4   | V    |

| DIS <sub>TH</sub>       | Disable threshold                                           | DIS/FLT falling                                                       | 1.53  | 1.7 | 1.87  | V    |

| I <sub>pd_DIS</sub>     | Internal pull down disable current                          | V <sub>DIS/FLT</sub> = 5 V                                            | 650   | 750 | 850   | μA   |

| RESTARTDEL              | Restart delay after fault <sup>(2)</sup>                    |                                                                       |       | 100 |       | ms   |

Specified by design. No production tested. (1)

Specified by bench characterization. No production tested.

(2) (3) This current includes the SW pin parasitic capaticor charge and discharge current. When operating with LLC, soft switching removes the capacitor charge and discharge current. Actual current is smaller.

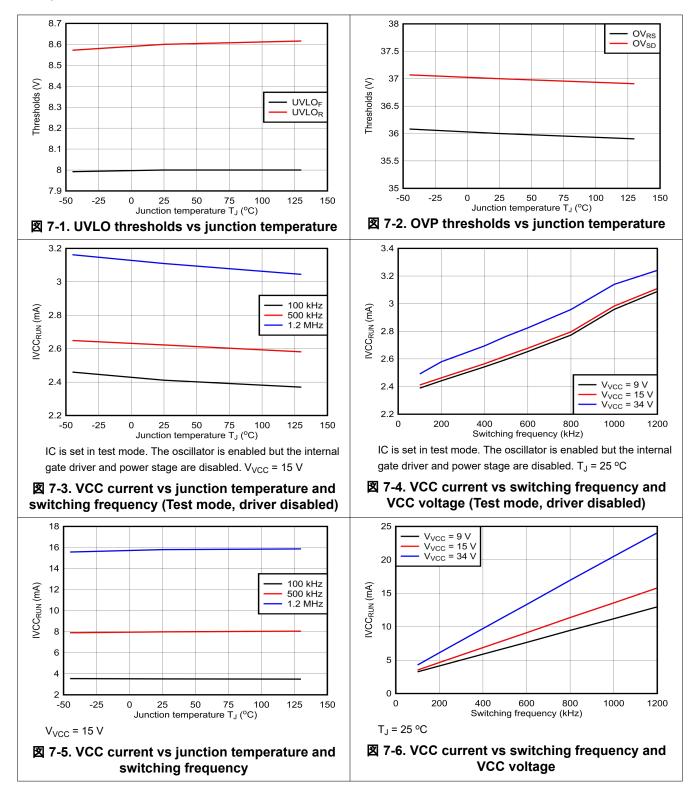

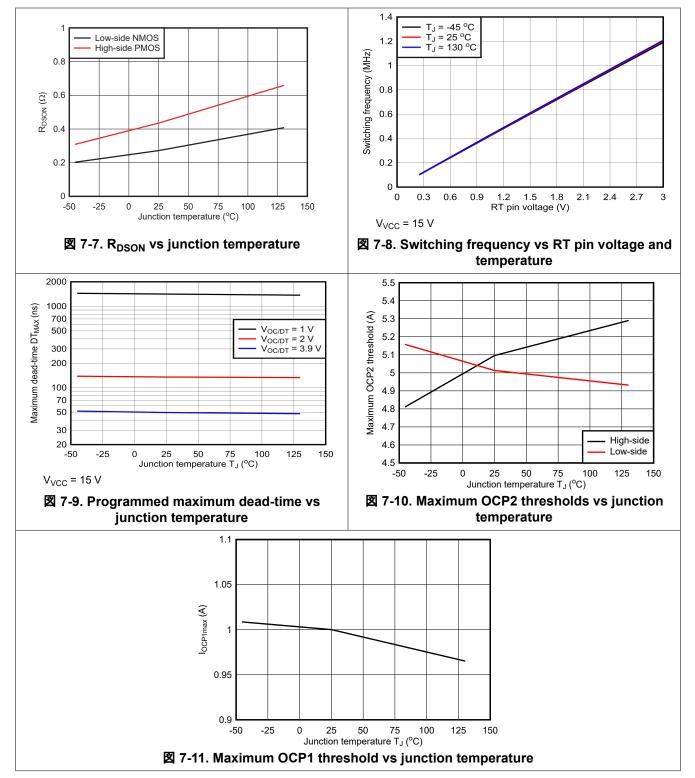

# 7.6 Typical Characteristics

# 8 Detailed Description

#### 8.1 Overview

Modern high-voltage, high-power-inverter, and motor-drive applications require floating bias supply voltages to power at least the high-side totem-pole switches, where source (and gate) voltages move up and down with the inverter switch-node. The traditional way of providing small amounts of isolated bias power has been to use a flyback converter. Often a single flyback converter with multiple outputs can generate the required rails for all the switches. However, issues with reliability, redundancy, shock and vibration testing, noise immunity and particularly EMI and common mode current have led to a trend away from the flyback topology and centralized architecture toward distributed open-loop approaches. The open-loop approaches such as 50% duty cycle push-pull, open-loop half bridge or full bridge without an output inductor are deployed while the flyback converter or *flybuck* (an isolated buck converter) continue to be used by some designs to provide regulated outputs despite the larger common-mode capacitance (transformer primary-side to secondary-side parasitic capacitance). With the adoption of SiC and GaN devices, the inverter power stage switches at a much higher dv/dt. This behavior causes much larger common-mode current injection through the isolated bias transformers and drives the needs for a bias supply design with minimum parasitic capacitance. The need to further reduce the primary-to-secondary capacitance without suffering performance degradation has led some designs to deploy resonant topologies such as the LLC. As the leakage inductance in an LLC is a component of the power train, the topology can enable a higher leakage inductance transformer to be used with an associated reduction in the parasitic primary-secondary capacitance. The UCC25800-Q1 transformer driver is a small, simple controller enabling this topology to be deployed with low component count, integrated protection features, high switching frequency, high parameter tolerance and robust operation. An 8-pin DGN package with thermal pad is used to provide up to 6-W power handling capability with 24-V input.

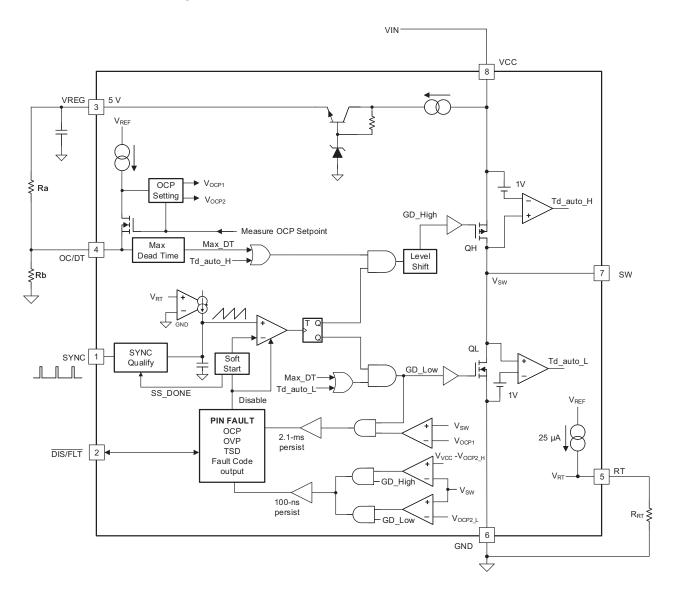

# 8.2 Functional Block Diagram

#### 8.3 Feature Description

UCC25800-Q1 is an 8-pin open-loop half-bridge transformer driver that integrates all the control and power devices. It converts a fixed input voltage to an isolated voltage source through an isolation transformer. The relationship between the output voltage and input voltage is fixed, which is determined by the transformer turnsratio and the rectification method. The open-loop control, together with the LLC resonant converter operation, makes the solution more robust, smaller size, higher efficiency, as well as lower EMI and common mode noise. The transformer driver requires a minimum of external components while providing design flexibility and robust protection features. The 1.2-MHz maximum switching frequency reduces the transformer size and cost, making it easier to pass the shock and vibration test in the automotive applications. The fault code output allows the designer to identify the protection mode, during the development stage, as well as during normal operation. This makes the development process much easier. It also enables the system controller to make intelligent decisions when bias supply faults happen.

#### 8.3.1 Power Management

The VCC pin powers the UCC25800-Q1 transformer driver. When the VCC pin voltage is below the UVLO rising threshold (UVLO<sub>R</sub>), the VREG pin 5-V regulator is disabled (VREG = 0 V). After the VCC pin voltage exceeds UVLO<sub>R</sub>, the 5-V regulator is enabled and VREG pin rises, while the DIS/FLT pin is internally pulled low through an internal 750- $\mu$ A current source, (DIS/FLT = 0 V). When the VREG exceeds 4.5 V (VREG<sub>OK</sub>), the DIS/FLT pin is released. If the DIS/FLT pin is not pulled low externally, it rises to VREG pin voltage level via an internal 100-k $\Omega$  pull up resistor. When DIS/FLT pin voltage exceeds the rising enable threshold (EN<sub>TH</sub>), the internal regulators and references are turned on and the transformer driver reads the Thevenin resistance on the OC/DT pin to set the overcurrent protection (OCP) thresholds. After this process completes, the faults are checked and if they are all cleared, the oscillator is enabled and the power stage starts switching. The time to complete this process is approximately 500 µs.

If a fault is detected, the transformer driver activates the internal pull-down current source on the DIS/FLT pin, the power stage stops switching, and the device outputs the fault code.

The rise time of the DIS/FLT pin depends on the external loading on the pin. An external pull-up can be added to the pin if there is concern over noise immunity. The values are specified in  $\pm 22 \approx 8.3.6$ .

When the VCC pin voltage is above the UVLO<sub>R</sub> threshold and  $\overline{\text{DIS/FLT}}$  pin is pulled low externally the transformer driver remains disabled with IVCC<sub>DIS</sub> = 660 µA.

If after a completed power-up sequence, VCC falls below the UVLO falling threshold (UVLO<sub>F</sub>), the power stage switching is immediately stopped. The VREG pin voltage regulator is disabled making the VREG pin voltage fall.

The VCC pin current is a combination of the IC bias current and the power stage current. It is important to have a low ESL bypass capacitor to minimize the current loop among this capacitor and VCC, GND pins. Refer to  $\frac{1}{2}$   $\frac{1}{2}$   $\frac{1}{2}$  11 for details.

#### 8.3.2 Oscillator

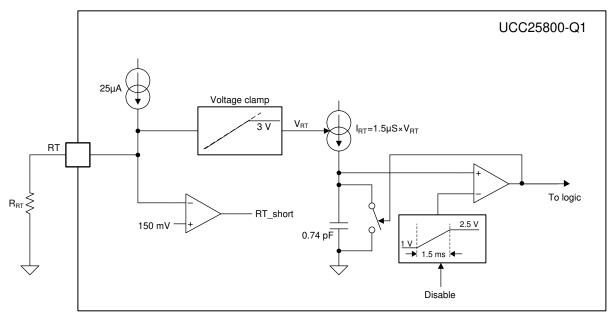

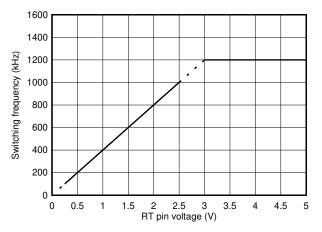

The internal oscillator of the UCC25800-Q1 transformer driver sets the switching frequency of the power stage. It operates at a 50% duty cycle. The voltage on the RT pin sets the oscillator frequency. A 25- $\mu$ A current source flows out of the pin so that the switching frequency can be set by connecting a resistor to GND. 🛛 8-1 shows the internal oscillator.

Use  $\pm$  1 to calculate the RT pin resitance for a required switching frequency.

(1)

$$f_{SW} = R_{RT} \times 10 \frac{Hz}{\Omega}$$

If the RT pin is left open, or an RT pin resistor value results in an RT pin voltage at  $RT_{OPEN}$  threshold or above, the power stage operates with the default switching frequency of 1.2 MHz. If the RT pin voltage is below 150 mV, the transformer driver considers the RT pin shorted to ground and declares a fault. The programmable voltage range on the RT pin is 250 mV to 2.5 V. The relationship between the power stage switching frequency and the RT-pin voltage is shown in 🛛 8-2.

図 8-2. Relationship between switching frequency and RT-pin voltage

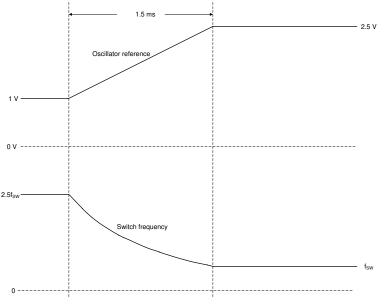

To avoid the excessive current stress during the start-up process, the transformer driver integrates a soft-start function. The oscillator starts by ramping the oscillator reference from 1 V to 2.5 V, which results in the switching frequency reducing from 2.5 times of the set frequency to the set frequency. Because the current source in the oscillator remains the same while the reference changes, the switching cycle decays linearly. The soft-start time is fixed internally at 1.5 ms. This long soft-start time limits the inrush current when charging large output capacitors. The soft-start is enabled during the start-up and fault recovery process.  $\boxtimes$  8-3 shows the switching frequency variation during the start-up time.

図 8-3. Switching frequency during soft start time

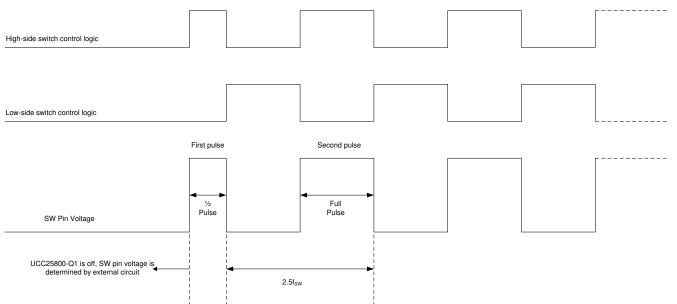

During the soft-start sequence, the first pulse from the oscillator is a half of the second pulse width (25% of the period at the starting switching frequency) and followed immediately by 50% duty cycle pulses. This process

ensures the LLC transformer magnetizing current is symmetrical from the first pulse to minimize ringing in the system. The high-side switch is always turned on at the first pulse to avoid uncertainty of the circuit operation.

#### 図 8-4. SW pin voltage and control logic at the first switching cycle (dead-time is not shown)

#### 8.3.3 External Synchronization

An external signal connected to the SYNC pin synchronizes the switching frequency of the UCC25800-Q1 transformer driver.

In the external synchronization mode, the switching frequency of the SW pin is half of the SYNC pin signal frequency. Given that, to ensure the output voltage remains within the normal operation range, the half of the frequency of external synchronization signal needs to be between 15% and 30% (nominal) above the programmed switching frequency with a tolerance of 5% or less, as described in  $\vec{x}$  2. A minimum high and low pulse width of 150 ns is required. The SYNC pin logic is compatible with TTL and CMOS levels for the design simplicity. It is recommended to use 50% duty cycle signal.

$$1.15 \times f_{SW} < \frac{1}{2} \times f_{SYNC} < 1.3 \times f_{SW}$$

<sup>(2)</sup>

where

- f<sub>SW</sub> is the RT pin programmed SW-pin switching frequency

- f<sub>SYNC</sub> is the SYNC pin signal frequency

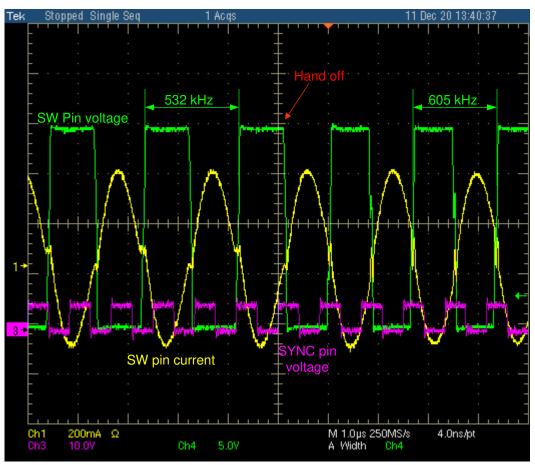

The transformer driver ignores the external synchronization signal during the 1.5-ms soft-start time. The switching frequency during the soft-start time is based on the RT pin voltage as described in  $\pm 22 \approx 8.3.2$ . After the soft-start period ends, if an external synchronization signal is present and its frequency and pulse width are within the specified range, the switch node is driven by the SYNC pin signal. The transformer driver also integrates a hand-off algorithm so that when the switching frequency transitions from internal oscillator to the external synchronization signal, the disturbance is minimal and transformer saturation is avoided.

The hand-off algorithm first confirms that the external synchronization signal is within the range. If the frequency is not within the acceptable range, the hand-off doesn't happen. If the frequency is within the acceptable range, the hand-off algorithm begins to search for the optimal transition point and locks the switching frequency with the external SYNC signal. After the frequency is locked, the hand-off algorithm stops monitoring the SYNC pin frequency. It is important to ensure external synchronization source has a stable frequency. There is an internal watchdog timer to prevent the external frequency from falling below the set frequency (the watchdog time does not monitor if the SYNC pin frequency goes above the range). If the SYNC pin frequency drops below the

Copyright © 2023 Texas Instruments Incorporated

set frequency, the transformer driver loses synchronization and the converter operates with the set frequency determined by RT pin voltage.

The 🛛 8-5 shows an oscilloscope screen capture for the controller transition from internal oscillator to the external synchronization signal. The smooth transition can be observed and the SW pin current sees minimal disturbance.

図 8-5. Transition from internal oscillator to external synchronization

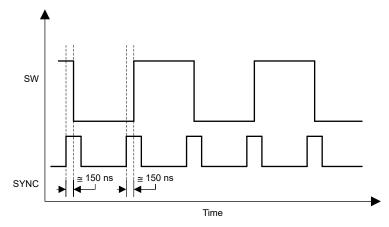

The internal MOSFET gate drives are toggled on each SYNC pin voltage rising edge, so the switch-node frequency is equal to half of the SYNC pin signal frequency, as shown in  $\boxtimes$  8-6. Due to the internal filter delays, the SW pin switching edge is not aligned with the SYNC pin switching edge. There is a delay of approximately 150 ns.

図 8-6. External SYNC signal drives switching frequency

#### 8.3.4 Dead-Time

A dead-time is needed between the turn off of one switch and the turn on of the other switch to avoid shoot through. This also allows the switch-node voltage to transition to the opposite rail voltage, which reduces switching loss and EMI noise.

#### 8.3.4.1 Adaptive Dead-time

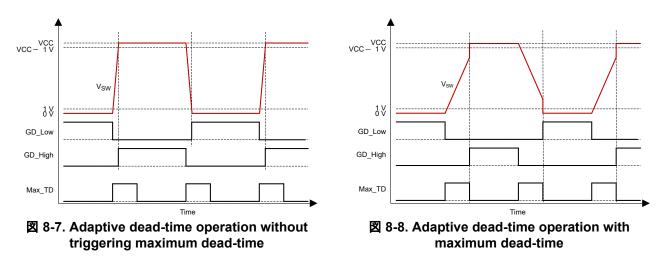

The UCC25800-Q1 transformer driver automatically detects the dead-time after the switch-node voltage slews to within 1 V of the opposite rail. This slewing of the node is driven by the current flowing through the SW pin into the resonant tank at the end of the each MOSFET on-time. There must be sufficient current flowing through the SW pin at the end of the on-time to drive the SW pin voltage to the opposite rail. The voltage on the OC/DT pin programs the maximum dead-time. Even if the SW pin voltage crossing the threshold is not detected within the maximum programmed dead-time, the internal MOSFET switches on when the maximum programmed dead-time expires. 🖾 8-7 and 🖾 8-8 demonstrate the two adaptive dead-time operation conditions.

#### 8.3.4.2 Maximum Programmable Dead-time

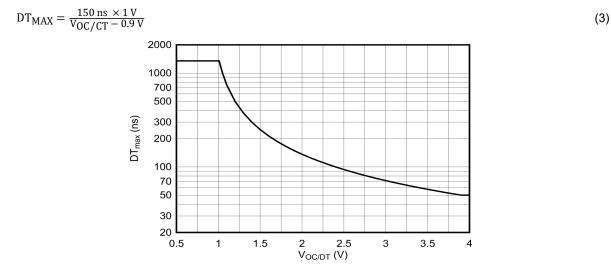

During operation, the voltage on the OC/DT pin sets a maximum duration of the dead-time. If the adaptive dead-time has not triggered the turn-on of the internal MOSFET within this time, it switches on when the maximum dead-time expires. The relationship between the OC/DT pin voltage and this maximum programmable dead-time is shown in 🛛 8-9 and given by  $\pm$  3. The UCC25800-Q1 transformer driver also limits the maximum dead-time to be 1/8 of the switching cycle. Therefore, the programmed maximum dead-time is the lower value of these two.

図 8-9. Maximum dead time vs. OC/DT pin voltage

When the OC/DT pin voltage falls below 0.5 V, the transformer driver triggers the pin-short protection and it shuts down. When the OC/DT pin voltage is between 0.5 V to 3.95 V, the maximum dead-time is set by  $\vec{x}$  3 with a clamped maximum value of 1.35 µs and a clamped minimum value of 50 ns. When the OC/DT pin voltage is between 3.95 V and 4.5 V, it triggers the DT-out-of-range fault and the transformer driver shuts down. When the OC/DT pin voltage is above 4.5 V, the transformer driver shuts down due to the OC/DT open pin fault protection.

#### 8.3.5 Protections

UCC25800-Q1 transformer driver provides a full set of protection functions to improve the system level reliability, meeting automotive design requirements. The protection functions include programmable two-level over current protection (OCP), input undervoltage protection (UVLO), input over-voltage protection (OVP), and over-temperature protection (TSD). This design considers possible pin fault conditions such as pin open and pin short.. Extra protection mechanisms are also integrated inside the design.

# 8.3.5.1 Overcurrent Protection

The UCC25800-Q1 transformer driver has two levels of overcurrent protection (OCP).

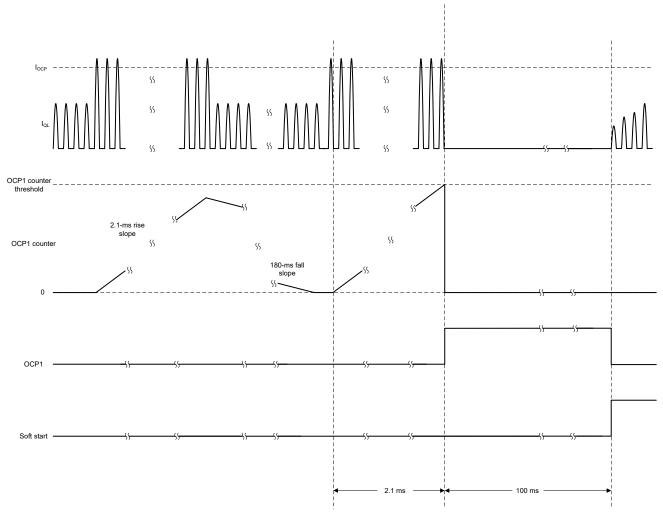

- The first level (OCP1) triggers if the current through the low-side MOSFET exceeds programmed threshold I<sub>OCP</sub> during its on-time in each switching cycle for 2.1 ms. Refer to OCP Threshold Setting for OCP1 threshold programming details.

- OCP1 detection is based on only the low-side MOSFET current, when the SW pin current flows into the SW pin

- The second level (OCP2) triggers if the current in either the high-side or low-side MOSFET exceeds 5 ×  $I_{OCP}$  for 100 ns.

- The OCP2 threshold is set significantly above OCP1 threshold to allow the unit to cope with heavy load surges for a short duration, or during the start-up to charge the large output capacitor. If OCP2 is exceeded, it indicates that there is a serious fault in the system. OCP2 tracks OCP1 so that events like output overload can still trip OCP2, even if the current limit is set well below the maximum current limit of the transformer driver.

- During soft-start

- The OCP1 is disabled

- The OCP2 threshold is fixed at its maximum value of 5 A

- After soft-start

- OCP1 is enabled, with the threshold I<sub>OCP</sub> equal to the programmed value

- OCP2 threshold becomes 5 times of the programmed I<sub>OCP</sub> level.

- The OCP1 overcurrent timer is implemented as an up-down counter to ensure that the repetitive short over-current events as well as a sustained 2.1-ms over current trigger the OCP.

- OCP1 overcurrent timer counts up if the SW current crosses I<sub>OCP</sub> for longer than 100 ns in each switching cycle

- OCP1 overcurrent timer counts down if the SW current does not cross I<sub>OCP</sub> for longer than 100 ns in the entire switching cycle

- The internal counter for OCP1 overcurrent timer counts up in 2.1 ms from 0 to the trip threshold and counts down in 180 ms from the trip threshold down to 0.

- OCP2 detection has an analog filter which filters out pulses of less than 100 ns.

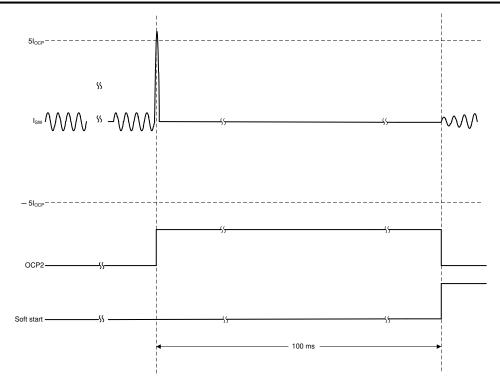

The transformer driver imposes a restart time of 100 ms before restarting from overcurrent protection to maintain the RMS current in the transformer driver below its limit. The OCP behaviors are illustrated in  $\boxtimes$  8-10 and  $\boxtimes$  8-11.

図 8-10. OCP1 protection and recovery behavior

図 8-11. OCP2 protection and recovery behavior

#### 8.3.5.1.1 OCP Threshold Setting

The UCC25800-Q1 transformer driver can support 6-W output power with 24-V input. For designs with lower power levels, the overcurrent protection (OCP) threshold can be adjusted accordingly to limit the maximum output power to improve the system reliability.

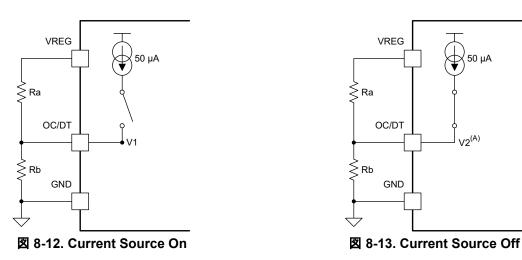

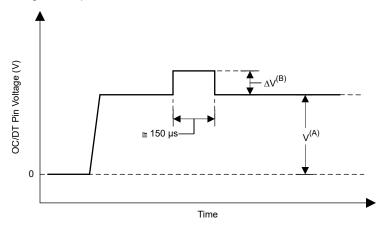

The OCP threshold setting shares the same pin as the maximum dead-time programming through OC/DT pin. During the transformer driver start-up sequence (after its VREG pin settles down to its final value) an internal 50-µA current source flowing out of OC/DT pin is turned on and off. The voltage on the OC/DT pin is measured at the current source on and off conditions. The measured voltage difference is used to set the OCP threshold. After the OCP setting is determined, the current source is turned off, so that the voltage on the OC/DT pin can be used for the maximum dead-time setting.

(5)

According to the Thevenin theorem, the measured voltage difference is the current source multiplied by the Thevenin resistance on the voltage divider on OC/DT pin. The OCP settings using different Thevenin resistance are summarized in  $\frac{1}{5}$  8-1. The Thevenin resistance can be calculated using  $\frac{1}{5}$  5.

$$Rth = \frac{Ra \times Rb}{Ra + Rb}$$

|                                       |                          | 1                        |                          | 193                       |                           |                        |

|---------------------------------------|--------------------------|--------------------------|--------------------------|---------------------------|---------------------------|------------------------|

|                                       | OCP1_1                   | OCP1_2                   | OCP1_3                   | OCP1_4                    | OCP1_5                    | OCP1_6                 |

| R <sub>th</sub>                       | 22.25 kΩ ~ 23.15<br>kΩ   | 16.4 kΩ ~ 17 kΩ          | 11.7 kΩ ~ 12.1 kΩ        | 7.95 kΩ ~ 8.25 kΩ         | 4.9 kΩ ~ 5.1 kΩ           | 2.45 kΩ ~ 2.55 kΩ      |

| OCP1 threshold<br>(I <sub>OCP</sub> ) | 1/6 I <sub>OCP1max</sub> | 1/3 I <sub>OCP1max</sub> | 1/2 I <sub>OCP1max</sub> | 2/3 I <sub>OCP1max</sub>  | 5/6 I <sub>OCP1max</sub>  | I <sub>OCP1max</sub>   |

| OCP2 threshold<br>during soft-start   | 5 A                      | 5 A                      | 5 A                      | 5 A                       | 5 A                       | 5 A                    |

| OCP2 threshold<br>after soft-start    | 5/6 I <sub>OCP1max</sub> | 5/3 I <sub>OCP1max</sub> | 5/2 I <sub>OCP1max</sub> | 10/3 I <sub>OCP1max</sub> | 25/6 I <sub>OCP1max</sub> | 5 I <sub>OCP1max</sub> |

表 8-1. OCP Settings

To ensure accurate reading of the Thevenin resistance, the time constant of Rth and any capacitance connected to the OC/DT pin should not be greater than 20  $\mu$ s. For this reason, the maximum recommended capacitance on the pin is 1 nF. It is not required to add capacitance to the pin.

The OC/DT pin voltage during start-up is illustrated in 🛛 8-14.

図 8-14. OC/DT pin voltage during start-up

| Α. | $V = VREG \times \frac{Rb}{Ra + Rb}$ | (6) |

|----|--------------------------------------|-----|

| В. | $\Delta V = 50 \ \mu A \times Rth$   | (7) |

#### 8.3.5.1.2 Output Power Capability

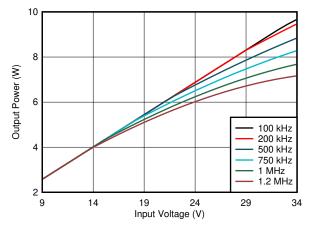

⊠ 8-15 shows the output power capability of the UCC25800-Q1 transformer driver at different input voltages and switching frequencies with its highest OCP set-point ( $I_{OCP} = I_{OCP1max} = 1$  A), based on an input-output efficiency of 90%. There are two limiting factors on the power handling capability of the transformer driver; the OCP1 threshold and the thermal stress.

OCP1 serves as an over-power limit rather than over current protection since it has a 2.1-ms timer. Given its maximum value is 1 A and considering the sinusoidal current shaped, transformer driver limits its maximum output power proportionally to the input voltage. In  $\mathbb{X}$  8-15, the 100-kHz line is approximately the OCP1 limit.

The thermal limitation is to prevent the junction temperature of the transformer driver from becoming too high. Assuming its loss is only the IC bias consumption and the MOSFET conduction loss, at 125°C ambient

Copyright © 2023 Texas Instruments Incorporated

temperature and 90% efficiency, the maximum output power creates the loss to make the junction temperature reach 150°C.  $\boxtimes$  8-15 shows that with higher the switching frequency, the IC power consumption increases and the maximum power capability decreases.

The power handling capability can be increased by increasing the input voltage or lowering the switching frequency, but it cannot exceed the OCP1 limit.

図 8-15. Power rating curves

# 8.3.5.2 Input Overvoltage Protection (OVP)

Due to the lack of feedback, UCC25800-Q1 transformer driver includes input overvoltage protection to prevent the output voltage from becoming too high, in case its input voltage becomes too high. If the VCC pin voltage exceeds the overvoltage set-point of  $OV_{SD}$  for overvoltage blanking time ( $OV_{BLNK}$ , 1.3 µs typical), the input overvoltage protection is triggered. When the input overvoltage protection is triggered, the fault mode is activated, stops the switching, and discharges the DIS/FLT pin and disables the transformer driver. Before restarting from an OVP fault, the input voltage must be below the OVP recovery threshold  $OV_{RS}$ . The transformer driver attempts to restart after 100 ms as described in  $\pm 2 \ge 3 \times 8.4.5$ .

The overvoltage protection threshold is a fixed value and cannot be programmed.

#### 8.3.5.3 Over-Temperature Protection (TSD)

Over-temperature protection is required, primarily to stop the internal MOSFETs from failing in either high ambient temperature operation conditions or due to self-heating from high switching current. An over-temperature condition occurs when the junction temperature goes above the TSD threshold of 160°C (typical). In this case, the fault mode is activated, the switching stops, discharging the  $\overline{\text{DIS/FLT}}$  pin and disabling the UCC25800-Q1 transformer driver. Before restarting from a TSD fault, the junction temperature must be below the overtemperature protection recover threshold (TSD-T<sub>HYST</sub>). Over-temperature protection parameters are specified by design.

#### 8.3.5.4 Pin-Fault Protections

表 8-2 below shows the UCC25800-Q1 transformer driver response to open and short circuits on the pins. For example, the SYNC function operates on the rising edge of the SYNC pin. Hence if the pin is open or short the only impact is the loss of synchronization functionality. The transformer driver continues to operate as normal at the switching frequency programmed by the RT pin.

| PIN     | OPEN                                           | SHORT TO GND                                   |

|---------|------------------------------------------------|------------------------------------------------|

| SYNC    | Normal operation with the programmed frequency | Normal operation with the programmed frequency |

| DIS/FLT | Normal operation                               | OFF                                            |

| VREG    | OFF (VREG open protection)                     | OFF                                            |

| OC/DT   | Fault (OC/DT open protection)                  | Fault (OC/DT short protection)                 |

#### 表 8-2. Pin Open and Short Response

#### 表 8-2. Pin Open and Short Response (continued)

| PIN | OPEN                      | SHORT TO GND                |

|-----|---------------------------|-----------------------------|

| RT  | f <sub>SW</sub> = 1.2 MHz | Fault (RT short protection) |

| GND | Unknown                   | -                           |

| SW  | V <sub>OUT</sub> = 0      | Fault (OCP) / 🗙             |

| VCC | OFF                       | OFF                         |

#### 表 8-3. Pin-to-Pin Shorts Responses

|         |                    |                   |                        |                         |               | -                 |                     |    |

|---------|--------------------|-------------------|------------------------|-------------------------|---------------|-------------------|---------------------|----|

| 123     | SYNC               | DIS/FLT           | VREG                   | OC/DT                   | VCC           | SW                | GND                 | RT |

| SYNC    | -                  |                   |                        |                         |               |                   |                     |    |

| DIS/FLT | - / OFF            | _                 |                        |                         |               |                   |                     |    |

| VREG    | No SYNC            | Always<br>enabled | -                      |                         |               |                   |                     |    |

| OC/DT   | – / OC/DT<br>Fault | Indeterminate     | Fault (OC/<br>DT_OPEN) | -                       |               |                   |                     |    |

| VCC     | ×                  | ×                 | ×                      | ×                       | _             |                   |                     |    |

| SW      | ×                  | OCP Fault / 🗙     | ×                      | Fault / 🗙               | Fault / 🗙     | -                 |                     |    |

| GND     | No SYNC            | OFF               | OFF                    | Fault (OC/<br>DT_SHORT) | IC not biased | Fault (OCP)/<br>★ | -                   |    |

| RT      | Indeterminate      | Indeterminate     | Fault<br>(RT_OPEN)     | Indeterminate           | ×             | ×                 | Fault<br>(RT_SHORT) | -  |

1. **X** indicates that the transformer driver will or may become damaged.

- 2. indicates no effect on the circuit operation.

- 3. *Indeterminate* indicates the IC behavior is unpredictable

#### 8.3.5.5 VREG Pin Protection

The VREG pin is an internal linear regulator output and the bias pin for most of the internal circuits. It is important to ensure a good regulated voltage on VREG pin. A low ESL decoupling capacitor is recommended between VREG to GND. The layout should follow the Layout Guidelines.

VREG pin is equipped with two sets of protection functions to prevent the pin from being left open or over loaded from external circuit.

When VREG pin is left open, since there is no decoupling capacitor, the internal linear regulator becomes unstable. The UCC25800-Q1 transformer driver detects this condition, stops the operation, shuts down the internal linear regulator, and enters the latch-off mode. VCC must be recycled to clear this protection.

To prevent VREG pin from being over-loaded, the VREG pin has its own over-current protection. During start-up, when VREG pin voltage is below 1 V, the VREG pin current is limited to 15-mA, to protect the IC from short or over-load conditions. When the VREG pin voltage rises above 1 V, the VREG pin current limit increases to 40 mA for a fast start-up. When the voltage crosses the VREG<sub>OK</sub> value, the VREG pin current limit returns to 15 mA. Because the VREG pin provides current for both internal circuit and external circuit, it is recommended to maintain the VREF pin external load to a value less than 1 mA. When the external VREG-pin current is between 1 mA and 15 mA, excessive VREG pin current can cause the VREG pin voltage to drop. During normal operation, if the VREG pin is over loaded and its voltage drops below the VREG<sub>low</sub> threshold, the transformer driver shuts down the linear regulator and enters latch-off mode. VCC must be recycled to clear this protection.

#### 8.3.6 DIS/FLT Pin operation

The DIS/FLT pin is an input/output pin. It can be

- Externally driven to enable or disable the transformer driver

- Read as a status flag telling whether the transformer driver is in fault mode or not and specifically what fault it is

- Left floating to enable the transformer driver by default

Internally the pin is tied high through a 100-k $\Omega$  pullup resistor from VREG. This pullup resistor activates only after the VREG pin is high. If the UCC25800-Q1 transformer driver enters the fault mode, the DIS/FLT pin is pulled low internally via a 750- $\mu$ A current source. When the pin is low, switching is inhibited.

The  $\overline{\text{DIS/FLT}}$  internal pulldown current source is activated during the power-up sequence once the VCC voltage exceeds the UVLO rising threshold. After the VREG voltage has risen above the VREG<sub>OK</sub> threshold, the pulldown current source is released and the  $\overline{\text{DIS/FLT}}$  pin rises (unless it is externally pulled down). When the  $\overline{\text{DIS/FLT}}$  pin voltage exceeds the EN<sub>TH</sub> threshold, the transformer driver is enabled. When  $\overline{\text{DIS/FLT}}$  pin falls below the  $\overline{\text{DIS/FLT}}$  the transformer driver is disabled. When the transformer driver is disabled its power consumption is reduced to  $\overline{\text{IVCC}}_{\text{DIS}}$ .

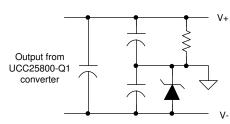

If there is concern about noise coupling to the  $\overline{\text{DIS/FLT}}$  pin it can be pulled up with an external resistor to an external rail or to VREG. In order to read the pin as a status flag, the external resistor value must be high enough that the 750-µA current source can pull the pin below the threshold level of the device reading the pin. It is recommended that the value for an external pullup resistor to 5 V is 10 k $\Omega$  and the value for an external pullup resistor to 3.3 V is 4.7 k $\Omega$  in order for the pin to be read as a fault output.

図 8-16. External Pullup for 3.3-V Supply

図 8-17. External Pullup for 5-V Supply

If the DIS/FLT pin functionality is not required, it can be left floating or tied to VREG to allow the transformer driver to operate normally.

#### 8.3.6.1 FAULT Codes

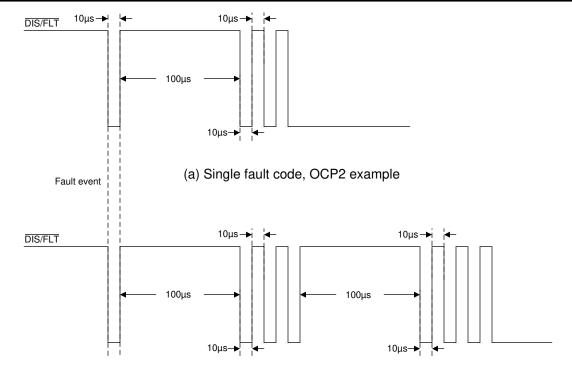

When the UCC25800-Q1 transformer driver enters fault mode, it outputs a train of pulses to indicate which faults have occurred through the  $\overline{\text{DIS/FLT}}$  pin. The pulse train consists of a number 50% duty cycle pulses at 50 kHz, (that is, 10-µs wide pulses), where the number of pulses indicates the fault listed in  $\frac{1}{8}$  8-4. The pulse train is created through controlling the internal 750-µA pull-down current source, together with the 100-k $\Omega$  pull-up resistor.

| NO. OF<br>PULSES | FAULT                                  |

|------------------|----------------------------------------|

| 1                | OCP1                                   |

| 2                | OCP2                                   |

| 3                | Input overvoltage protection           |

| 4                | Over temperature protection            |

| 5                | DT out of range                        |

| 6                | OC/DT open                             |

| 7                | OC/DT short                            |

| 8                | RT short                               |

| 9                | OTP (one-time-programmable bit ) error |

#### 表 8-4. Fault codes

The pulse train starts 10  $\mu$ s after the fault has been asserted. Transmission of the fault code begins with a 100- $\mu$ s wide high pulse. If more than one fault is detected, the codes are transmitted successively based on the order in  $\frac{1}{8}$  8-4, separated by a 100- $\mu$ s wide high pulse, as shown below in  $\boxed{2}$  8-18.

(b) Multiple fault codes, OCP2 and input over-voltage example

#### 🗷 8-18. Fault code diagram

#### 8.4 Device Functional Modes

Depending on the operating condition, the UCC25800-Q1 transformer driver can operate in different modes, including UVLO, soft-start, normal operation, disabled and the fault modes.

#### 8.4.1 UVLO Mode

When the input voltage on VCC is less than the transformer driver UVLO threshold, the transformer driver is disabled. There is no switching on the SW pin and VREG is off.

#### 8.4.2 Soft-start Mode

After the VCC voltage is above the UVLO threshold, all the faults are cleared, and  $\overline{\text{DIS/FLT}}$  is released, the converter operates in the soft-start mode. During the soft-start period, the switching frequency gradually decreases to reduce the current stress. The soft-start period duration is 1.5 ms. The UCC25800-Q1 transformer driver always operates in soft-start mode during startup or after fault recovery. Refer to  $\pm 22 \approx 8.3.2$  for more details of soft-start mode.

#### 8.4.3 Normal Operation Mode

Most of the cases, the UCC25800-Q1 transformer driver operates in the normal operation mode. The switching frequency is fixed, determined by eithert he RT pin voltage or external synchronization signal.

#### 8.4.4 Disabled Mode

When the  $\overline{\text{DIS/FLT}}$  pin is pulled low externally, the UCC25800-Q1 transformer driver enters disabled mode. In this mode, the VREG pin is regulated while the SW pin remains off. The VCC current consumption reduces to the disable current IVCC<sub>DIS</sub>.

#### 8.4.5 Fault Modes

Occasionally, different fault conditions occur and the UCC25800-Q1 transformer driver protects the system from more severe damage by entering the following fault modes.

Copyright © 2023 Texas Instruments Incorporated

| FAULT                  | DESCRIPTION                                                                                                                                                                                                                                                                                     |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Overcurrent (OCP1)     | OCP1 occurs when the current in the internal low-side MOSFET during the low-side MOSFET on time exceeds $I_{OCP}$ for 2.1 ms. UCC25800B-Q1 disables the OCP1 fault action.                                                                                                                      |

| Overcurrent (OCP2)     | OCP2 occurs when the current in either MOSFET exceeds five times of the I <sub>OCP</sub> for more than 100 ns. UCC25800B-Q1 keeps the same OCP2 setting and fault action as UCC25800-Q1.                                                                                                        |

| Over temperature (TSD) | Over temperature protection (TSD) occurs when the junction temperature goes above TSD threshold.                                                                                                                                                                                                |

| Input overvoltage      | Input overvoltage protection occurs when VCC voltage is above the overvoltage shut-down ( $OV_{SD}$ ) threshold for more than 1.3 $\mu$ s.                                                                                                                                                      |

| OC/DT open             | OC/DT open protection occurs if the OC/DT pin exceeds 4.5 V after the OCP check has been completed.                                                                                                                                                                                             |

| OC/DT short            | OC/DT short protection occurs if the OC/DT pin falls below 500 mV.                                                                                                                                                                                                                              |

| OC/DT out of range     | OC/DT out-of-range protection occurs when the OC/DT pin voltage is between 3.95 V and 4.5 V during the OCP programming check.                                                                                                                                                                   |

| RT short               | RT short protection occurs when RT pin is below 150 mV.                                                                                                                                                                                                                                         |

| OTP error              | OTP error fault occurs when, during the OTP reading at start-up, the OTP sanity check fails. In case of OTP error fault, only OTP error fault code is transmitted while all other faults are ignored. The OTP error fault can be cleared only with a power cycle that forces a new OTP reading. |

#### 表 8-5. Fault Mode Summary

When any fault occurs the switching is immediately (after individual detection delays) stopped. The DIS/FLT pin is internally pulled down. After the fault codes are transmitted, the transformer driver current consumption is reduced to IVCC<sub>DIS</sub>. The VREG regulator remains enabled and the RT pin remains at its programmed level.

When the transformer driver enters fault mode it pulses the pull-down current on the  $\overline{\text{DIS/FLT}}$  pin on and off to output a fault code and signal which fault has been triggered as explained in  $\pm 22 \pm 8.3.6.1$ .

After a delay time of 100 ms, the  $\overline{\text{DIS/FLT}}$  pin is released and, if it is not pulled low externally. When it crosses the EN<sub>TH</sub>, the transformer driver is enabled, the power up sequence occurs and the switching can start again. Before starting switching, the faults are checked again. If the protection that caused the fault condition still presents, or a new protection is triggered, the switching is not started and a new fault condition is asserted; fault codes are transmitted again. And the transformer driver current consumption is reduced to IVCC<sub>DIS</sub>. This fault and power-up sequence is automatically cycled until all the faults are cleared.

# **9** Application and Implementation

注

以下のアプリケーション情報は、TIの製品仕様に含まれるものではなく、TI ではその正確性または 完全性を保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断して いただくことになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確 認する必要があります。

# 9.1 Application Information

The isolated bias supply is required in many applications, such as the gate driver bias for the traction inverters, on board chargers in electrical vehicles. It is also used in other sensing and control circuits in the electrical vehicles to minimize the noise or provide safety isolation. The open-loop LLC converter based on the UCC25800-Q1 transformer driver provides a reliable solution for these applications. It uses the open-loop control to improve the noise immunity. The LLC topology is able to operate at a higher switching frequency with soft switching, achieve high efficiency and low EMI, reducing the transformer size. Furthermore, the LLC topology is able to absorb the transformer leakage inductance as part of the resonant circuit. This absorption allows the transformer to have extremely low primary side to secondary side parasitic capacitance, which reduces the system level common-mode noise. The LLC topology also helps to simplify the transformer construction and reduces the transformer cost.

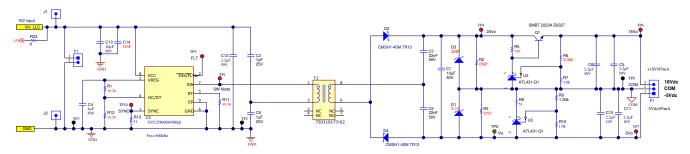

#### 9.2 Typical Application

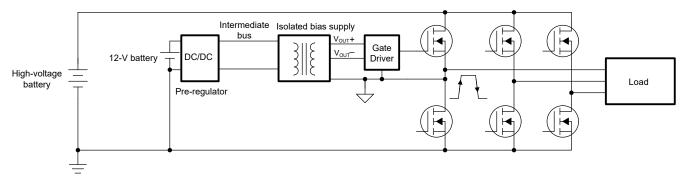

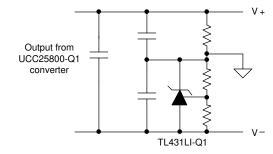

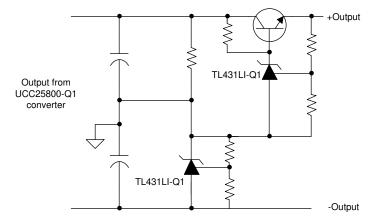

In the automotive traction inverters or on-board chargers, a regulated bus voltage is often generated from the 12-V battery and then processed by the isolated bias supplies to provide the gate driver bias power for the inverter switches, as shown in  $\boxtimes$  9-1. The isolated bias supply can be used to bias the high-side drivers or low-side drivers, to provide the isolation for function, safety, or noise immunity.

#### 図 9-1. Gate driver bias supply example for automotive traction inverter

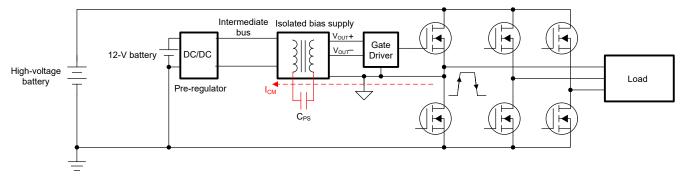

When the isolated based bias supply used in the inverter applications, especially for the high side switches, the high dv/dt on the inverter switch-node can couple through the bias supply transformer and causes extra EMI noise, as demonstrated in  $\boxtimes$  9-2.

図 9-2. Noise coupling path from inverter power stage to isolated bias supply

Given the high dv/dt is caused by the inverter power stage, to minimize this noise coupling, it is desired to minimize the transformer primary side to secondary side parasitic capacitor (inter-winding capacitor)  $C_{PS}$ . Popular topologies, such as Flyback or Push-pull, require the minimum leakage inductance to improve the efficiency, reduce the voltage and current stress, as well as minimize the noise created by the converter. In turn, this type of transformers suffer from larger inter-winding capacitance. When they are used in the gate driver bias supply applications, the high dv/dt from the inverter power stage could be coupled through the transformer inter-winding capacitor to the low-voltage side. This creates a much severe EMI noise issue. Instead, the LLC topology utilizes the transformer leakage inductance as its resonant component, allowing the converter to use a transformer with larger leakage inductance but much smaller inter-winding capacitance. This results in less system EMI noise challenges.

# 9.2.1 LLC Converter Operation Principle

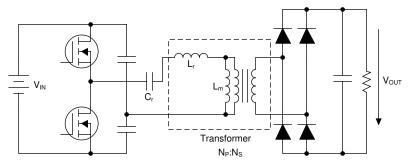

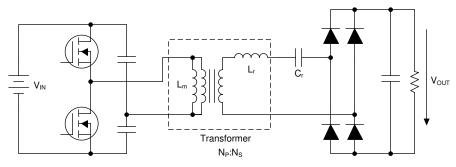

Different than the traditional PWM converters, LLC converters adjust the output voltage through varying the switching frequency. It is often called a PFM (pulse frequency modulation) converter. As shown in  $\boxtimes$  9-3, the LLC converter has three resonant elements, the resonant inductor (L<sub>r</sub>), the magnetizing inductor (L<sub>m</sub>), and the resonant capacitor (C<sub>r</sub>). In the isolated bias supply design, the transformer leakage inductor, and the magnetizing inductor can be used as part of the resonant circuit. In this case, the only external resonant component is the resonant capacitor.

図 9-3. LLC Converter

At the resonant switching frequency (series resonant frequency of  $L_r$  and  $C_r$ ), the impedance of the resonant tank ( $L_r$  and  $C_r$ ) is equal to zero. The input and output voltage are virtually connected together through the transformer. Therefore, the gain of the converter is equal to the transformer turns ratio, as shown in  $\vec{x}$  8.

$$\frac{V_{OUT}}{V_{IN}} = \frac{1}{2} \frac{N_S}{N_P}$$

(8)

In this equation, the  $\frac{1}{2}$  comes from the half-bridge architecture that the transformer primary side only sees half of the input voltage.

UCC25800-Q1 transformer driver controls the LLC converter to operate at a fixed switching frequency very close to the resonant frequency, to create an output voltage proportional to the input voltage, through a transformer

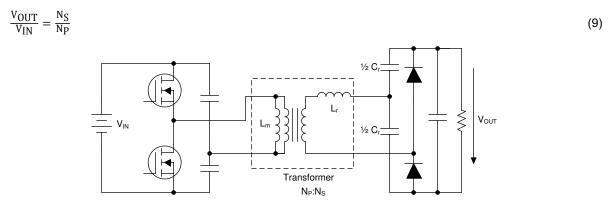

turns-ratio. Depending on the location of the resonant capacitor, the LLC converter can be configured as primary-side resonant (as shown in  $\boxtimes$  9-3), or secondary-side resonant (as shown in  $\boxtimes$  9-4). When the resonant capacitor is moved to the secondary side, the magnetizing inductor no longer affects the converter gain. Therefore, the converter is less sensitive to the switching frequency and resonant component tolerances. The secondary-side resonant is more suitable for the open-loop LLC converter and it is a preferred configuration for transformer driver.

図 9-4. Secondary side resonant LLC converter

Furthermore, the secondary-side full-wave rectifier can be replaced with a voltage-doubler rectifier. Together with splitting the resonant capacitor into two, as shown in  $\boxtimes$  9-5, the converter configuration becomes simpler and fewer diodes are used. In this case, the transformer primary side sees half of the input voltage and the transformer secondary side sees half of the output voltage. The converter voltage gain becomes purely the transformer turns-ratio, as shown in  $\vec{x}$  9.

図 9-5. Secondary side resonant LLC converter with voltage doubler rectifier

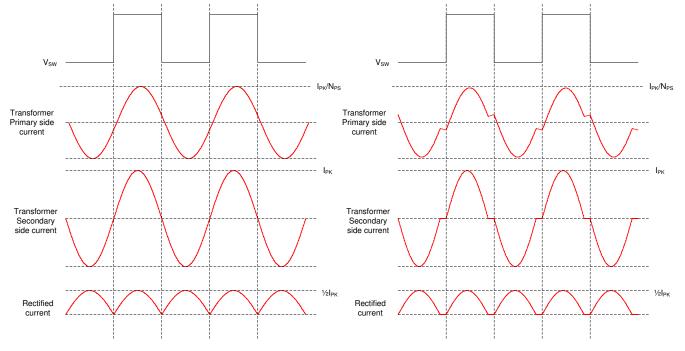

The LLC operation waveforms are shown in 29-6, when switching frequency is equal to the resonant frequency or below the resonant frequency.

(a) Switching frequency equal to resonant frequency

(b) Switching frequency below resonant frequency

#### 図 9-6. LLC converter operation waveforms

#### 9.2.2 Design Requirements

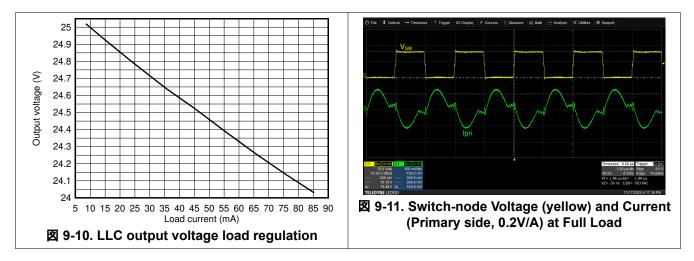

A 2-W traction inverter gate driver bias supply design demonstrates the design process based on the UCC25800-Q1 transformer driver.

| PARAMETER                                | TEST CONDITIONS                                   | MIN   | NOM   | MAX   | UNIT |

|------------------------------------------|---------------------------------------------------|-------|-------|-------|------|

| Input Characteristics                    |                                                   | L     |       |       | -    |

| V <sub>IN</sub> , Input voltage, DC      |                                                   |       | 15    |       | V    |

| Output Characteristics                   |                                                   | L.    | I     |       |      |

| V <sub>OUT1</sub> , set point, DC        |                                                   | 17.93 | 18.10 | 18.27 | V    |

| I <sub>OUT1</sub> , output current range |                                                   | 0     |       | 85    | mA   |

| V <sub>OUT1</sub> , regulation           | $I_{OUT1} = I_{OUT2}$ , 0 to full load            | -1.0  |       | 1.0   | %    |

| V <sub>OUT2</sub> , set point            |                                                   | -5.02 | -4.98 | -4.94 | V    |

| I <sub>OUT1</sub> , output current range |                                                   | -85   |       | 0     | mA   |

| V <sub>OUT2</sub> , regulation           | $I_{OUT1} = I_{OUT2}$ , 0 to full load            | -1.0  |       | 1.0   | %    |

| V <sub>OUT1</sub> , peak to peak ripple  | I <sub>OUT1</sub> = I <sub>OUT2</sub> , full load |       | 50    |       | mV   |

| V <sub>OUT2</sub> , peak to peak ripple  | I <sub>OUT1</sub> = I <sub>OUT2</sub> , full load |       | 35    |       | mV   |

| System Characteristics                   |                                                   | L     | •     |       |      |