order

Now

## **TPS7A78**

Reference

Design

JAJSH18A - MARCH 2019 - REVISED SEPTEMBER 2019

# TPS7A78 120mA スマート AC/DC リニア電圧レギュレータ

Technical

Documents

# 1 特長

- 18V<sub>AC RMS</sub> 以上の非絶縁型電源ソリューション

最高 75% の効率

- スタンバイ時消費電力:15mW (標準値)

- リニア・ソリューションの 1/4 のサイズのライン電圧 降下コンデンサ

- 固定出力電圧で提供

- 1.3V ~ 5V (50mV 刻み)

- 電源障害検出

- パワー・グッド表示

- 精度:1%(標準値)

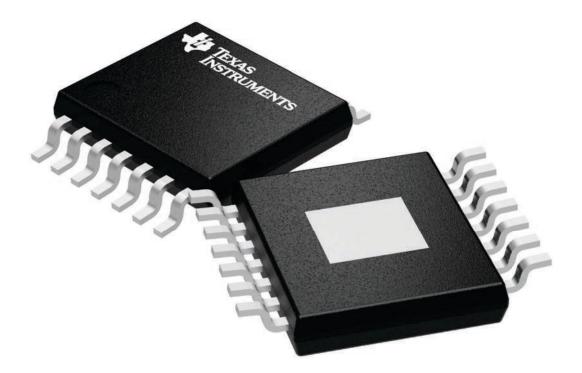

- パッケージ

5mm × 6.5mm の HTSSOP-14 (PWP)

# 2 アプリケーション

- キー・パネル

- ガレージのドア・システム

- 小型家電製品

- 電気メータ

- 煙感知器と熱感知器

- サーモスタット

# 3 概要

**TPS7A78** は、使いやすい非磁気的 AC/DC 変換方式に より、電源の総合効率とスタンバイ時電力を改善します。 **TPS7A78** は、コンデンサ電圧降下アーキテクチャを使用 して AC 電源電圧を降圧してから、整流された電圧をアク ティブにクランプします。次に、この整流された電圧をアプ リケーション固有の動作電圧まで下げてレギュレートしま す。本デバイスの独自のアーキテクチャを使用すると、スタ ンバイ時の電力をわずか数十ミリワットに低減できます。 **TPS7A78** のスイッチト・キャパシタ段は、整流された入力 電圧を4分の1 に降圧し出力電流を入力電流の4倍に 増やすことで、電力損失を減らします。これは、 $P_{IN} \cong P_{OUT}$ および  $V_{IN} \cong V_{OUT} \times 4$ で与えられます。従来型のコンデン サ電圧降下 (キャップドロップ) 段と比較して、この降圧方 式では入力電流が減少するため、必要なコンデンサの値 を最小化できます。

**TPS7A78** は外付け磁気部品を必要としないため、磁気 に対する耐タンパー性を備えた電源を必要とする電力 メータ用途に適しています。この特長により、磁気シールド のコストを最小化しながら IEC 61000-4-8 に簡単に準拠 できます。

製品情報<sup>(1)</sup>

| 型番      | パッケージ       | 本体サイズ(公称)       |

|---------|-------------|-----------------|

| TPS7A78 | HTSSOP (14) | 5.00mm × 6.50mm |

|         |             |                 |

(1) 利用可能なすべてのパッケージについては、このデータシートの末 尾にある注文情報を参照してください。

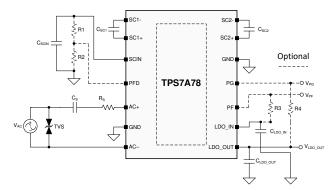

#### フルブリッジ構成の標準的な回路図

# 目次

| 1 | 特長   | ;1                               |

|---|------|----------------------------------|

| 2 | アプ   | リケーション1                          |

| 3 | 概要   |                                  |

| 4 | 改訂   | '履歴2                             |

| 5 | 概要   | 〔(続き)3                           |

| 6 | Pin  | Configuration and Functions 4    |

| 7 | Spe  | cifications5                     |

|   | 7.1  | Absolute Maximum Ratings 5       |

|   | 7.2  | ESD Ratings5                     |

|   | 7.3  | Recommended Operating Conditions |

|   | 7.4  | Thermal Information 6            |

|   | 7.5  | Electrical Characteristics7      |

|   | 7.6  | Timing Requirements 7            |

|   | 7.7  | Typical Characteristics 8        |

| 8 | Deta | ailed Description 11             |

|   | 8.1  | Overview 11                      |

|   | 8.2  | Functional Block Diagram 11      |

|   | 8.3  | Feature Description 12           |

|   |      |                                  |

|    | 8.4  | Device Functional Modes     | . 15 |

|----|------|-----------------------------|------|

| 9  | Арр  | lication and Implementation | 16   |

|    | 9.1  | Application Information     | . 16 |

|    | 9.2  | Typical Application         | . 24 |

| 10 | Pow  | ver Supply Recommendations  | 30   |

| 11 | Lay  | out                         | 30   |

|    | 11.1 | Layout Guidelines           | . 30 |

|    | 11.2 | Layout Example              | . 30 |

| 12 | デバ   | イスおよびドキュメントのサポート            | 31   |

|    | 12.1 | デバイス・サポート                   |      |

|    | 12.2 | ドキュメントのサポート                 | . 31 |

|    | 12.3 | ドキュメントの更新通知を受け取る方法          | . 31 |

|    | 12.4 | コミュニティ・リソース                 | . 31 |

|    | 12.5 | 商標                          | . 31 |

|    | 12.6 | 静電気放電に関する注意事項               | . 32 |

|    | 12.7 |                             |      |

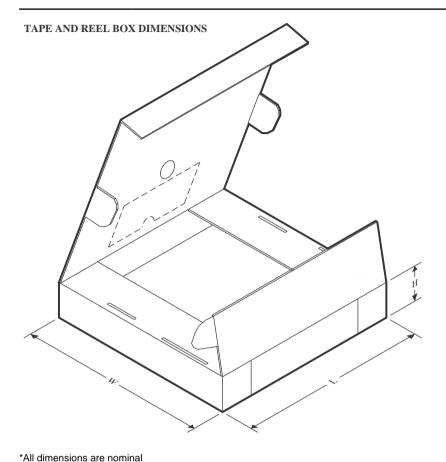

| 13 | メカニ  | ニカル、パッケージ、および注文情報           | 32   |

|    |      |                             |      |

# 4 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

#### 2019年3月発行のものから更新

| • | デバイスのステータスを APL から量産データに 変更 | 1 |

|---|-----------------------------|---|

www.tij.co.jp

Page

# 5 概要(続き)

また、TPS7A78 は、電源障害に対して早期アラートを発行し電源が完全に失われる前にシャットダウンできるユーザ・プロ グラマブルな電源障害検出スレッショルドも備えています。マイクロコントローラのシーケンシングまたはリセット用にパワー・ グッド・インジケータ (PG) も備えています。

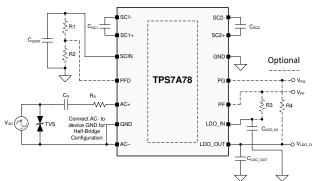

TPS7A78 は、14 ピンの HTSSOP (PWP) パッケージで供給されます。

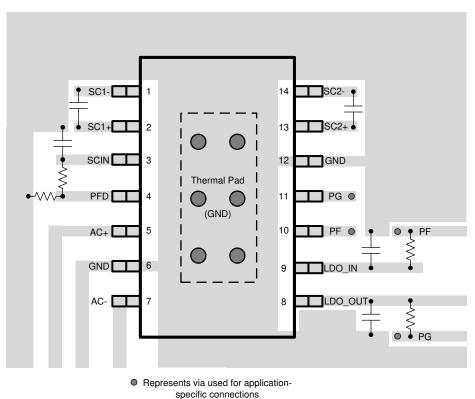

# 6 Pin Configuration and Functions

#### **Pin Functions**

|     | PIN TVET |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|-----|----------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NO. | NAME     | TYPE   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| 1   | SC1-     | _      | Negative terminal of the switched-capacitor, voltage-reduction stage pin. Connect a minimum 1- $\mu$ F, X5R (or better) dielectric, 16-V-rated capacitor between this pin and the SC1+ pin. Place the capacitor as close to the device as possible; see the <i>Recommended Operating Conditions</i> table for details.                                                                                                                                                                 |  |  |  |

| 2   | SC1+     | _      | Positive terminal of the switched-capacitor, voltage-reduction stage pin. Connect a minimum 1- $\mu$ F, X5R (or better) dielectric, 16-V-rated capacitor between this pin and the SC1– pin. Place the capacitor as close to the device as possible; see the <i>Recommended Operating Conditions</i> table for details.                                                                                                                                                                 |  |  |  |

| 3   | SCIN     | _      | Rectified DC-voltage pin. Place the capacitor as close to the device as possible; see the <i>Device Functional Modes</i> section for the dual-input power-supply capability and the <i>Calculating the Bulk Capacitor</i> section for the proper capacitor calculation.                                                                                                                                                                                                                |  |  |  |

| 4   | PFD      | Input  | Power-failure detect pin. An analog voltage input compares the reference voltage to a resistor-<br>divided $V_{SCIN}$ voltage to detect a $V_{AC}$ power-failure; see the <i>Recommended Operating Conditions</i><br>table and the <i>Calculating the PFD Pin Resistor Dividers for Power-Fail Detection</i> section for<br>details.                                                                                                                                                   |  |  |  |

| 5   | AC+      | Power  | AC-supply line or neutral input to the device after the capacitive-drop (cap-drop) capacitor and surge resistor. Either this pin or the AC– pin must have the cap-drop capacitor and surge resistor in series with the line. See the <i>Full-Bridge (FB) and Half-Bridge (HB) Configurations</i> section for details.                                                                                                                                                                  |  |  |  |

| 6   | GND      | Ground | Ground pin. All device ground pins must be referenced to the same ground. Connect this pin to the thermal pad at the bottom of the device; see the <i>Layout</i> section for details.                                                                                                                                                                                                                                                                                                  |  |  |  |

| 7   | AC-      | Power  | AC-supply line or neutral input to the device pin after the cap-drop capacitor and surge resistor. Either this pin or the AC+ pin must have the cap-drop capacitor and surge resistor in series with the line. See the <i>Full-Bridge (FB) and Half-Bridge (HB) Configurations</i> section for details.                                                                                                                                                                                |  |  |  |

| 8   | LDO_OUT  | Output | Regulated DC output pin. Connect a minimum 0.68-µF, X5R (or better) dielectric capacitor between this pin and the device GND pins. Place the capacitor as close to the device as possible; see the <i>Recommended Operating Conditions</i> table for the maximum capacitor value.                                                                                                                                                                                                      |  |  |  |

| 9   | LDO_IN   |        | Charge-pump output pin. Connect a minimum $0.68$ -µF, X5R (or better) dielectric capacitor between this pin and the device GND pins. This pin is internally driven and must not be driven externally. For optimal performance, connect a capacitor that is 10x the value of C <sub>LDO_OUT</sub> placed as close to the device as possible. See the <i>Recommended Operating Conditions</i> table for the maximum capacitor value.                                                     |  |  |  |

| 10  | PF       | Output | Power-fail indicator pin. An open-drain indicator signal indicates if the $V_{AC}$ supply has failed.<br>Pullup this pin through an external resistor to $V_{LDO_{\_IN}}$ or to a DC-rail that shares the same GND as the device. The PF pin goes low when $V_{PFD}$ is less than the $V_{IT(PFD,FALLING)}$ threshold, as specified in the <i>Electrical Characteristics</i> table. See the <i>Recommended Operating Conditions</i> table for proper selection of the pullup resistor. |  |  |  |

#### **Pin Functions (continued)**

| PIN                                                                                         |                                                                                                                                                                                                      | ТҮРЕ                                                                                                                                                                                                                                                                                                                     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO.                                                                                         | NAME                                                                                                                                                                                                 | TTPE                                                                                                                                                                                                                                                                                                                     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 11                                                                                          | PG                                                                                                                                                                                                   | Output                                                                                                                                                                                                                                                                                                                   | Power-good indication pin. An open-drain indicator signal indicates if the $V_{LDO\_OUT}$ surpassed the $V_{IT(PG,RISING)}$ threshold, as specified in the <i>Electrical Characteristics</i> table. Pullup this pin through an external resistor to $V_{LDO\_OUT}$ or to a DC rail that shares the same GND as the device. See the <i>Recommended Operating Conditions</i> table for proper selection of the pullup resistor. |

| 12                                                                                          | GND                                                                                                                                                                                                  | Ground                                                                                                                                                                                                                                                                                                                   | Ground pin. All device ground pins must be referenced to the same ground. Connect this pin to the thermal pad at the bottom of the device; see the <i>Layout</i> section for details.                                                                                                                                                                                                                                         |

| 13                                                                                          | 13 SC2+ — µF, X5R (or a better) dielectric, 10-V-rated capacitor between this pin and the SC2- pin. P the capacitor as close to the device as possible; see the <i>Recommended Operating Conditi</i> |                                                                                                                                                                                                                                                                                                                          | Positive terminal of the switched-capacitor, voltage-reduction stage pin. Connect a minimum 1- $\mu$ F, X5R (or a better) dielectric, 10-V-rated capacitor between this pin and the SC2– pin. Place the capacitor as close to the device as possible; see the <i>Recommended Operating Conditions</i> table for details.                                                                                                      |

| μF, X5R (or a better) dielectric, 10-V-rated capacitor between this pin and the SC2+ pin. F |                                                                                                                                                                                                      | Negative terminal of the switched-capacitor, voltage-reduction stage pin. Connect a minimum 1- $\mu$ F, X5R (or a better) dielectric, 10-V-rated capacitor between this pin and the SC2+ pin. Place the capacitor as close to the device as possible; see the <i>Recommended Operating Conditions</i> table for details. |                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Thermal pad —                                                                               |                                                                                                                                                                                                      | —                                                                                                                                                                                                                                                                                                                        | Exposed pad of the package. Connect this pad to device ground pins. Connect the thermal pad to a large-area ground plane for best thermal performance.                                                                                                                                                                                                                                                                        |

# 7 Specifications

## 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)(2)</sup>

|             |                                                                  | MIN                               | MAX | UNIT |

|-------------|------------------------------------------------------------------|-----------------------------------|-----|------|

|             | AC+, AC- (V <sub>AC</sub> supply mode only)                      | -1.5                              | 30  |      |

|             | SCIN (V <sub>AC</sub> supply mode only, internally driven)       | -1.5                              | 30  |      |

| ) (altaria  | SCIN (DC supply mode only, voltage directly applied on SCIN pin) | - 0.3                             | 24  | V    |

| Voltage     | LDO_OUT                                                          | - 0.3                             | 5.5 | v    |

|             | PF, PG                                                           | - 0.3                             | 6   |      |

|             | PFD                                                              | -0.3                              | 3   |      |

|             | LDO_OUT pin reverse current <sup>(3)</sup>                       |                                   | 6   |      |

| Current     | Maximum output                                                   | Maximum output Internally limited |     | mA   |

|             | I <sub>PF</sub> , I <sub>PG</sub>                                |                                   | 5   |      |

| Temperature | Storage, T <sub>STG</sub>                                        | - 65                              | 150 | °C   |

(1) Stresses beyond those listed under Absolute Maximum Rating may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Condition. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltages are with respect to the device GND pins (not Earth GND); see the *Full Bridge (FB) and Half Bridge (HB) Configurations* section for details.

(3) Exceeding the maximum reverse current into the LDO\_OUT pin can cause damage to the device; see the *Reverse Current* section for details.

# 7.2 ESD Ratings

|         |                                            |                                                                                          | VALUE | UNIT |

|---------|--------------------------------------------|------------------------------------------------------------------------------------------|-------|------|

| N       | Flastrastatia disebarga                    | Human body model (HBM), per<br>ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>           | ±2000 | V    |

| v (ESD) | V <sub>(ESD)</sub> Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins <sup>(2)</sup> | ±1000 | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                 |                                                                                                      | MIN               | NOM | MAX                | UNIT              |

|---------------------------------|------------------------------------------------------------------------------------------------------|-------------------|-----|--------------------|-------------------|

| V <sub>AC</sub> <sup>(2)</sup>  | Connected via $C_8^{(3)}$ and $R_8^{(3)(4)}$ on either AC+ or AC-                                    | 18 <sup>(5)</sup> |     |                    | V <sub>RMS</sub>  |

| f <sub>AC</sub>                 | Line frequency                                                                                       |                   | 50  | 20,000             | Hz                |

| I <sub>SURGE</sub>              | Peak transient current into or out of either the AC+ or AC– pins (during hot plug for $\leq$ 100 µs) |                   |     | 2.5                | А                 |

| I <sub>SHUNT</sub>              | AC current during shunt event on either AC+ or AC- pins                                              |                   |     | 200                | mA <sub>RMS</sub> |

| V <sub>SCIN</sub>               | DC supply mode, voltage applied to the SCIN pin for devices with $V_{LDO\_OUT} \leq 3.4~V$           | 17 <sup>(6)</sup> |     | 23                 | V                 |

| C <sub>SCIN</sub>               | Bulk capacitor for V <sub>AC</sub> supply mode                                                       | 22                |     |                    |                   |

| C <sub>SCIN</sub>               | Bulk capacitor for DC-supply mode                                                                    | 1.0               |     |                    | μF                |

| C <sub>SC1</sub>                | Switched-capacitor stage 1                                                                           | 1                 |     | 4.7 <sup>(7)</sup> | μF                |

| C <sub>SC2</sub>                | Switched-capacitor stage 2                                                                           | 1                 |     | 4.7 <sup>(7)</sup> | μF                |

| $C_{LDO_IN}$                    | LDO_IN capacitor                                                                                     | 0.68              | 10  | 1000               | μF                |

| C <sub>LDO_OUT</sub>            | LDO_OUT capacitor                                                                                    | 0.68              | 1   | 100                | μF                |

| R <sub>1</sub>                  | PFD top resistor divider                                                                             | 0                 |     | 200                | kΩ                |

| R <sub>3</sub> & R <sub>4</sub> | Power-good and power-fail pullup resistors                                                           | 10                |     | 100                | kΩ                |

| I <sub>OUT</sub>                | Output current                                                                                       | 0                 |     | 120                | mA                |

| TJ                              | Operating junction temperature                                                                       | -40               |     | 125                | °C                |

(1) All voltages are with respect to the device GND pins (not Earth GND); see the *Full Bridge (FB) and Half Bridge (HB) Configurations* section for details.

(2) Theoretically there is no upper limit to the V<sub>AC</sub> supply voltage because this voltage is dropped across the C<sub>S</sub> capacitor; see the *Calculating the Cap-Drop Capacitor* section for details.

(3) The voltage ratings for the cap-drop capacitor C<sub>S</sub> and the surge resistor R<sub>S</sub> must be able to handle the peak V<sub>AC</sub> supply voltage; see the *Typical Application* section for details.

(4) The surge resistor R<sub>S</sub> is required to limit the inrush current into or out off either AC+ or AC- pins during hot-plug or surge current events; see the Calculating the Surge Resistor section for details.

(5) Only available for devices with  $\leq$  3.3-V output voltage options.

(6) DC-supply mode is also availabe for 3.6-V devices but with a minmum required V<sub>SCIN</sub> supply voltage of 18 V.

(7) A 16 V or higher voltage rating is recommended for the C<sub>SC1</sub> capacitor, and a 10 V or higher voltage rating is recommeded for the C<sub>SC2</sub> capacitor.

## 7.4 Thermal Information

|                       |                                              | TPS7A78     |      |

|-----------------------|----------------------------------------------|-------------|------|

|                       | THERMAL METRIC <sup>(1)(2)</sup>             | PWP (TSSOP) | UNIT |

|                       |                                              | 14 PINS     |      |

| $R_{	hetaJA}$         | Junction-to-ambient thermal resistance       | 48.0        | °C/W |

| $R_{\theta JC(top)}$  | Junction-to-case (top) thermal resistance    | 44.0        | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 24.2        | °C/W |

| $\Psi_{\text{JT}}$    | Junction-to-top characterization parameter   | 1.6         | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 24.1        | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 7.2         | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

(2) Thermal metrics were modeled on a JEDEC Hi-K board in order to provide a standardized layout and measurement technique for comparison purposes. The An empirical analysis of the impact of board layout on LDO thermal performance application report goes into detail on how board layout impacts the thermal performance of linear regulators.

### 7.5 Electrical Characteristics

$V_{SCIN}^{(1)} = 4 (V_{LDO_OUT (nom)} + 0.6 V) + 1 V \text{ or } 17 V \text{ (whichever is greater), } C_{SCIN} = 10 \ \mu\text{F}, C_{S1} = 1.0 \ \mu\text{F}, C_{S2} = 2.2 \ \mu\text{F} \text{ , } C_{LDO_IN} = 10 \ \mu\text{F}, C_{LDO_OUT} = 1.0 \ \mu\text{F}, \text{ and } I_{OUT} = 1 \ \text{mA} \text{ (unless otherwise noted); typical values are at } T_J = 25^{\circ}\text{C}^{(2)}$

| PA                                 | ARAMETER                                      | TEST CONDITIONS                                                                                                                                                                                             | MIN   | TYP | MAX   | UNIT                  |

|------------------------------------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|-------|-----------------------|

| V <sub>UVLO_SCIN</sub>             | UVLO_SCIN threshold rising                    | $V_{SCIN}$ rising, $V_{LDO_OUT(nom)} \le 3.4 V$                                                                                                                                                             | 17    |     |       | V                     |

| V                                  | UVLO_LDO_IN threshold rising                  | V <sub>SCIN</sub> rising                                                                                                                                                                                    | 3.9   |     |       | V                     |

| VUVLO_LDO_IN                       | UVLO_LDO_IN threshold falling                 | V <sub>SCIN</sub> falling                                                                                                                                                                                   |       |     | 3.5   | V                     |

| $\Delta V_{LDO\_OUT(\Delta IOUT)}$ | Load regulation                               | $0 \text{ mA} \le I_{OUT} \le 120 \text{ mA}$                                                                                                                                                               |       |     | 0.21  | mV/mA                 |

| V <sub>LDO_OUT</sub>               | Output voltage accuracy                       | $V_{SCIN}^{(1)(3)} = 4 (V_{LDO_OUT (nom)} + 0.6 V) + 3 V, 0 mA \le I_{OUT} \le 120 mA$                                                                                                                      | -2    | 1   | 2     | %                     |

| I <sub>CL</sub>                    | Output current limit                          | $V_{LDO_OUT} = 0.9 \times V_{LDO_OUT(nom)}$                                                                                                                                                                 | 145   | 215 | 300   | mA                    |

| IDD_SCIN                           | SCIN pin quiescent<br>current                 | $V_{LDO_OUT(nom)}$ = 3.3 V, $I_{OUT}$ = 0 mA, no R <sub>3</sub> , R <sub>4</sub>                                                                                                                            |       | 280 |       | μA                    |

| V <sub>Ripple</sub>                | Output voltage ripple                         | $ \begin{array}{l} V_{AC} = 120 \; V, \; 60 \; Hz, \; FB, \; C_S = 1.0 \; \mu F, \; C_{SCIN} = 180 \\ \mu F, \; V_{LDO\_OUT(nom)} = 5 \; V, \; I_{OUT} = 10 \; mA, \\ scope \; BW = 10 \; MHz \end{array} $ |       | 3   |       | mV                    |

| VIT(PFD, RISING)                   | PFD pin rising threshold                      | $V_{PFD}$ rising, $R_4 = 100 \text{ k}\Omega$                                                                                                                                                               | 1.24  |     | 1.42  | V                     |

| VIT(PFD, FALLING)                  | PFD pin falling threshold                     | $V_{PFD}$ falling, $R_4 = 100 \text{ k}\Omega$                                                                                                                                                              | 1.17  |     | 1.25  | v                     |

| V <sub>HYS(PFD)</sub>              | PFD pin hysteresis                            |                                                                                                                                                                                                             |       | 110 |       | mV                    |

| VIT(PG,RISING)                     | PG pin rising threshold                       | $R_3 = 100 \text{ k}\Omega, \text{ V}_{\text{SCIN}} \text{ rising}$                                                                                                                                         | 90.16 | 92  | 93.84 |                       |

| VIT(PG,FALLING)                    | PG pin falling threshold                      | $R_3 = 100 \text{ k}\Omega$                                                                                                                                                                                 | 88.5  | 90  | 91.5  | %V <sub>LDO_OUT</sub> |

| V <sub>HYS(PG)</sub>               | PG pin hysteresis                             |                                                                                                                                                                                                             |       | 2   |       |                       |

| V <sub>OL(PF),(PG)</sub>           | PF and PG pins low-level ouput voltage        | I <sub>PF,PG</sub> = 500 μA                                                                                                                                                                                 |       |     | 0.2   | V                     |

| I <sub>LKG(PF),(PG)</sub>          | PF and PG pins open-<br>drain leakage current | V <sub>PF,PG</sub> = 5 V                                                                                                                                                                                    |       |     | 50    | nA                    |

| T <sub>SD(Shutdown)</sub>          | Thermal shutdown temperature                  | Shutdown, temperature increasing                                                                                                                                                                            |       | 162 |       | °C                    |

| T <sub>SD(Reset)</sub>             | Thermal shutdown reset temperature            | Reset, temperature decreasing                                                                                                                                                                               |       | 135 |       |                       |

For V<sub>LDO\_OUT</sub> > 4.4 V, V<sub>SCIN</sub> is limited to 24 V for testing purposes only.

Electrcial characterestic data tested in DC supply mode equivalent to V<sub>SCIN</sub> voltage under AC supply mode.

V<sub>SCIN</sub> ≥ 19 V.

#### 7.6 Timing Requirements

|                     |                                              | MIN | NOM | MAX | UNIT |

|---------------------|----------------------------------------------|-----|-----|-----|------|

| t <sub>PF(HL)</sub> | PF pin going from high to low                |     | 1   |     | μs   |

| t <sub>PG(LH)</sub> | PG pin going from low to high                |     | 1   |     | μs   |

| f <sub>SC</sub>     | Switched capacitor stage operating frequency |     | 200 |     | kHz  |

TEXAS INSTRUMENTS

TPS7A78 JAJSH18A – MARCH 2019 – REVISED SEPTEMBER 2019

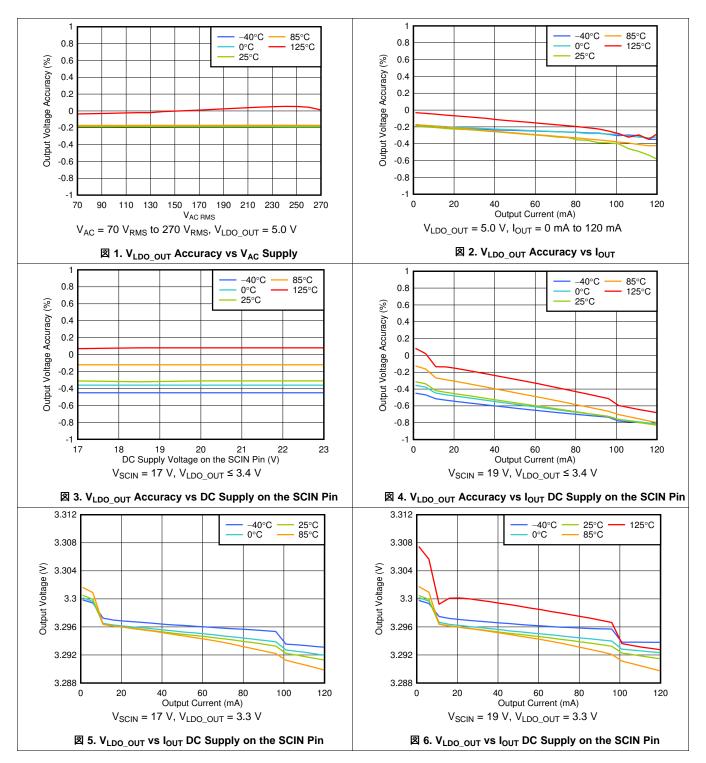

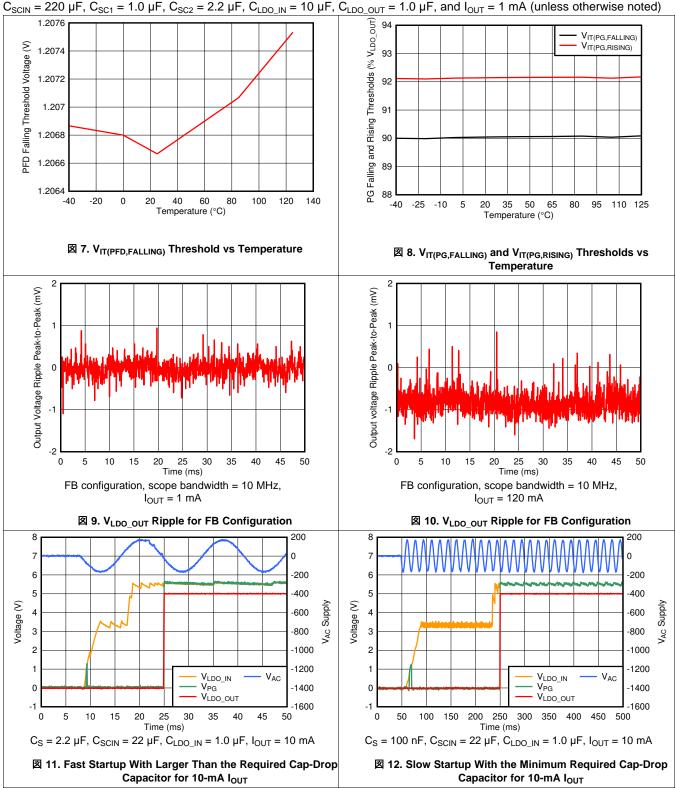

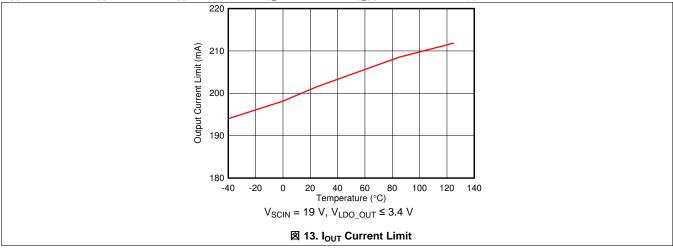

# 7.7 Typical Characteristics

at operating temperature  $T_J = 25^{\circ}$ C,  $V_{AC}$  supply = 120  $V_{RMS}$  per 60 Hz, full-bridge (FB) bridge configuration,  $C_S = 1.0 \ \mu$ F,  $C_{SCIN} = 220 \ \mu$ F,  $C_{SC1} = 1.0 \ \mu$ F,  $C_{SC2} = 2.2 \ \mu$ F,  $C_{LDO_{IN}} = 10 \ \mu$ F,  $C_{LDO_{OUT}} = 1.0 \ \mu$ F, and  $I_{OUT} = 1 \ m$ A (unless otherwise noted)

## **Typical Characteristics (continued)**

at operating temperature  $T_J = 25^{\circ}$ C,  $V_{AC}$  supply = 120  $V_{RMS}$  per 60 Hz, full-bridge (FB) bridge configuration,  $C_S = 1.0 \ \mu$ F,  $C_{SCIN} = 220 \ \mu$ F,  $C_{SC1} = 1.0 \ \mu$ F,  $C_{SC2} = 2.2 \ \mu$ F,  $C_{LDO_{-IN}} = 10 \ \mu$ F,  $C_{LDO_{OUT}} = 1.0 \ \mu$ F, and  $I_{OUT} = 1 \ m$ A (unless otherwise noted)

# **Typical Characteristics (continued)**

at operating temperature  $T_J = 25^{\circ}$ C,  $V_{AC}$  supply = 120  $V_{RMS}$  per 60 Hz, full-bridge (FB) bridge configuration,  $C_S = 1.0 \ \mu$ F,  $C_{SCIN} = 220 \ \mu$ F,  $C_{SC1} = 1.0 \ \mu$ F,  $C_{SC2} = 2.2 \ \mu$ F,  $C_{LDO_{IN}} = 10 \ \mu$ F,  $C_{LDO_{OUT}} = 1.0 \ \mu$ F, and  $I_{OUT} = 1 \ m$ A (unless otherwise noted)

# 8 Detailed Description

### 8.1 Overview

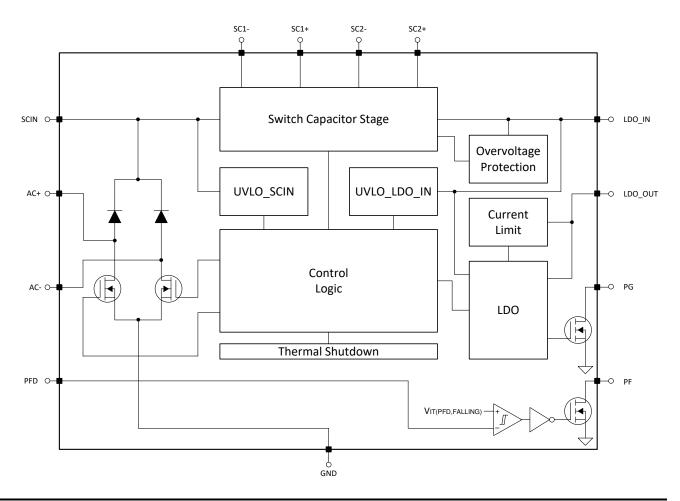

The TPS7A78 features an internally controlled, active bridge rectifier that can be configured either as full bridge (FB) or a half bridge (HB), a 4:1 switched-capacitor stage (charge pump), an internally controlled low-dropout (LDO) linear-voltage regulator, as well as current-limit, thermal-shutdown, programmable power-fail detection, and power-good detection.

The TPS7A78 is a non-isolated, smart linear-voltage regulator that uses an external high-voltage, capacitor-drop (cap-drop) capacitor ( $C_S$ ) and an internally controlled, active bridge-rectifier to create a regulated DC output voltage. The device incorporates a switched-capacitor charge pump stage that transforms the voltage and current characteristics of the rectifier stage to the voltage and current needs of the LDO stage, providing a 4-times reduction in input power for a given load power. This feature also reduces the size of the required  $C_S$  by a factor of 4. The external surge resistor  $R_S$  is used to limit the inrush-current to the device. Unlike typical AC-to-DC power solutions, the TPS7A78 does not require external magnetic components, thus making the device an excellent choice for electricity-metering applications by improving tamper resistance. This unique design allows the TPS7A78 to reduce standby power to approximately 15 mW for light-load applications while maintaining high efficiency.

For applications with output voltages of 3.6 V or less, the TPS7A78 can be powered from a DC supply connected directly to the SCIN pin. This supply mode can provide DC-only operation or DC-powered backup in case of AC supply failure. When a DC supply is used to power the device, the internally controlled dropout voltage regulation is affected as explained in the *Dropout Voltage Regulation* section. The AC+ and AC- pins must be grounded when only a DC power source is used.

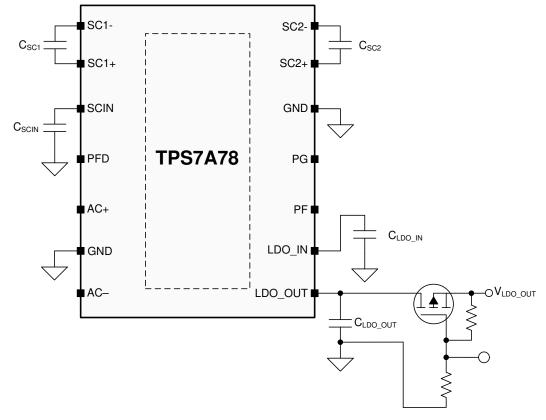

# 8.2 Functional Block Diagram

TEXAS INSTRUMENTS

#### 8.3 Feature Description

#### 8.3.1 Active Bridge Control

The TPS7A78 has an internally controlled, actively clamped, full-bridge rectifier between the AC+ and AC- pins that requires one of these pins to be connected in series with the high-voltage capacitor  $C_S$  and the surge resistor  $R_S$ . The active clamp for the bridge is designed to stabilize the rectified DC voltage at the SCIN pin to optimize performance given the LDO output voltage. The clamp circulates any excess AC charging current from the cap-drop capacitor  $C_S$  and surge resistor  $R_S$  through the AC+ or the AC- pins to the GND pins when the SCIN pin voltage surpasses its UVLO\_SCIN rising threshold during startup. The clamp maintains the SCIN pin voltage higher than this threshold to support the targeted output voltage. This excess AC charging current is also referred to as the shunt current,  $I_{SHUNT}$ ; see the *Standby Power and Output Efficiency* section for details on the shunt current.

A DC supply can also be used to provide power directly to the SCIN pin, which completely bypasses the bridge active-clamp circuit; see 表 1 for details on the DC supply mode.

#### 8.3.2 Full-Bridge (FB) and Half-Bridge (HB) Configurations

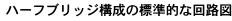

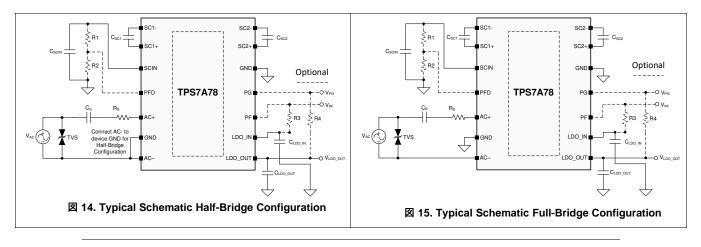

The TPS7A78 can be configured to operate either in full-bridge (FB) or half-bridge (HB) configurations. HB configuration ties the AC input pin without the series  $C_S$  and  $R_S$  components to the device GND pins. See  $\boxed{2}$  14 and  $\boxed{2}$  15 for the HB and FB configurations.

注

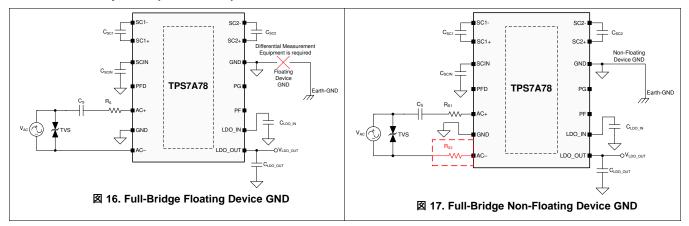

When FB configuration is used, do not tie the device GNDs to earth GND neither schematically nor accidentally via an earth-grounded oscilloscope or measurement equipment because the device GNDs and earth GND are at different voltage potentials. Doing so and can cause damage to the device and external equipment. Tying the device GND pins to earth GND when FB configuration is used is only acceptable if a second surge resistor  $R_S$  is used on the AC input pin side without the series  $C_S$  and first  $R_S$ , as illustrated in 🛛 16 with floating device GND pins and 🔅 17 with non-floating (earth grounded) device GND pins.

### Feature Description (continued)

#### 8.3.3 4:1 Switched-Capacitor Voltage Reduction

The TPS7A78 uses a switched-capacitor charge pump to reduce the rectified DC voltage at the SCIN pin by four times, providing the LDO block with an input voltage above its dropout voltage that is then regulated to the target output voltage. The DC voltage at the SCIN pin can be provided either by the active clamp for the bridge rectifying the input  $V_{AC}$  supply or by a direct DC supply connection to the SCIN pin.

### 8.3.4 Undervoltage Lockout Circuits (V<sub>UVLO SCIN</sub>) and (V<sub>UVLO LDO IN</sub>)

The TPS7A78 incorporates two undervoltage lockout (UVLO) circuits; the UVLO\_SCIN circuit and the UVLO\_LDO\_IN circuit. UVLO\_SCIN is used to make sure that the active clamp for the bridge has charged the  $C_{SCIN}$  capacitor to a voltage level that surpasses the UVLO\_SCIN rising threshold to start the switched-capacitor stage. The UVLO\_SCIN rising threshold voltage is a function of the LDO output voltage,  $V_{LDO_OUT(nom)}$ , as indicated in the *Electrical Characteristics* table.

The UVLO\_LDO\_IN circuit is used to ensure that the switched-capacitor stage has charged the  $C_{LDO_IN}$  capacitor to a voltage level that surpasses the UVLO\_LDO\_IN rising threshold to enable the LDO circuit to begin regulation at the specified LDO output voltage. See the *Startup Behavior* section for details.

# 注 The LDO\_IN pin must not be driven externally and must not be used as a supply rail to an external load.

#### 8.3.5 Dropout Voltage Regulation

This LDO functional block follows the conventional definition of dropout voltage ( $V_{DO}$ ) between  $V_{LDO_{IN}}$  and  $V_{LDO_{OUT}}$ . However, the supply mode can have an effect on the dropout voltage.

When the AC input is used as the supply, a fixed dropout ( $V_{DO}$ ) of 600 mV (typical) between  $V_{LDO\_IN}$  and  $V_{LDO\_OUT}$  is maintained for output voltages between 5.0 V and 3.4 V. For output voltages below 3.4 V, the  $V_{LDO\_IN}$  voltage is maintained at 4.0 V regardless of the output voltage.

A DC supply via the SCIN pin can only be used for output voltages of 3.6 V or less. Under a load condition approaching maximum output current and at high ambient temperature, the LDO can be driven into dropout; see the *Switched-Capacitor Stage Output Impedance* section for details.

#### 8.3.6 Current Limit

The LDO block has an internal current-limit circuit that protects the output during overcurrent events or shortcircuit faults. The current-limit circuit limits the output current to  $(I_{CL})$ , as specified in the *Electrical Characteristics* table.

Copyright © 2019, Texas Instruments Incorporated

#### Feature Description (continued)

When in current limit, the output voltage cannot be regulated and the device heats up because of the increase in power dissipation. When in current limit, the LDO pass transistor dissipates power equal to  $V_{DO} \times I_{CL}$ , where  $V_{DO}$  is equal in the worst case to  $V_{LDO_{IN}}$ . The heat generated when operating at current limit, in conjunction with the ambient temperature, can trigger the internal thermal shutdown. During thermal shutdown, both  $V_{LDO_{OUT}}$  and the switched-capacitor stage are shut down to prevent further heating; see the *Load Transient* section for more details.

#### 8.3.7 Programmable Power-Fail Detection

The TPS7A78 can monitor the rectified DC voltage at the SCIN pin to provide the application with an early warning via the power-fail (PF) pin if the main power fails. An external resistor-divider network connected to the VSCIN pin provides the input to the power-fail detect (PFD) analog input pin to monitor for an AC line supply failure. When the AC supply falls below its minimum level programmed by the resistor divider  $R_1$  and  $R_2$ , as illustrated in  $\boxtimes$  14 and in  $\boxtimes$  15, the PF output is pulled low. If this feature is not used, omit  $R_1$  and  $R_2$  and connect PFD and PF pins to the device GND pins reference.

#### 注

The PFD pin can also be used to monitor another DC rail within the application to provide an early warning via the PF pin. However, this DC rail must share the same GND reference with the TPS7A78 GND and the absolute maximum voltage of the PF pin must not be exceeded.

#### 8.3.8 Power-Good (PG) Detection

The power-good (PG) circuit monitors the  $V_{LDO_OUT}$  voltage to indicate the status of the LDO output voltage. PG is pulled low until  $V_{LDO_OUT}$  reaches its proper regulate voltage level, then PG is released and allowed to be pulled high. If  $V_{LDO_OUT}$  falls below the  $V_{IT(PG_FALLING)}$  threshold, PG is asserted low to indicate the LDO output voltage is not in regulation. PG pin low assertion can happen during an overcurrent event or a short-circuit fault.

PG can be used to release the reset pin of a microcontroller. The PG pin must be pulled up to a DC rail such as  $V_{LDO OUT}$ .

Use the recommended pullup resistor value specified in the *Electrical Characteristics* table for the PG pin. The functionality of the power-good detection pin has no effect on the internal control logic other than to indicate the state of the output voltage. If this function is not used, connect the PG pin to the device GND pins reference.

注

An external DC rail can also be used to pull up the PG pin signal via a pullup resistor only when the external DC rail shares the same reference GND with the TPS7A78 GND and the absolute maximum voltage of the PG pin is not exceeded.

## 8.3.9 Thermal Shutdown

A thermal shutdown protection circuit is included to disable  $V_{LDO_OUT}$  and to stop the switched-capacitor stage from switching when the junction temperature  $T_J$  of the pass-transistor rises to  $T_{SD(SHUTDOWN)}$ . Thermal shutdown hysteresis assures that the device resets, resumes normal operation, and that  $V_{LDO_OUT}$  turns back on when  $T_J$  falls to  $T_{SD(RESET)}$ . Based on the thermal time constant of the die and the device startup time, the device output can cycle on and off until power dissipation is reduced and the junction temperature remains below  $T_{SD(RESET)}$ .

For reliable operation, limit the junction temperature to the maximum listed in the *Recommended Operating Conditions* table. Operating above this maximum temperature causes the device to exceed its operational specifications. Although the internal protection circuitry is designed to protect against thermal overload conditions, this circuitry is not intended to replace proper heat sinking. Continuously running the device into thermal shutdown or above the maximum recommended junction temperature reduces long-term reliability.

## 8.4 Device Functional Modes

The unique features of the TPS7A78, along with its dual-input power-supply capability, enables the device to be used in a vast array applications. 表 1 gives a general overview of the conditions that lead to different modes of operation, given that the requirements in the *Typical Application* section are met.

| OPERATING                    | PARAMETER                                                                                                                                                                               |                                                                                 |                                             |  |  |  |  |  |  |  |  |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|---------------------------------------------|--|--|--|--|--|--|--|--|

| MODE                         | DEVICE POWER-SUPPLY                                                                                                                                                                     | Ι <sub>ουτ</sub>                                                                | TJ                                          |  |  |  |  |  |  |  |  |

| Normal operation             | $V_{AC}$ supply <sup>(1)</sup> / DC supply <sup>(2)</sup>                                                                                                                               | $I_{OUT} < I_{CL}$ used in the Calculating the Cap-Drop Capacitor $C_S$ section | T <sub>J</sub> < T <sub>SD (Shutdown)</sub> |  |  |  |  |  |  |  |  |

|                              | $C_S$ or $C_{SCIN}$ capacitors are not sufficient to support $I_{OUT}$ (V_{AC} supply)                                                                                                  | $I_{OUT} < I_{CL}$ used in the Calculating the Cap-Drop Capacitor $C_S$ section | $T_J < T_{SD (Shutdown)}$                   |  |  |  |  |  |  |  |  |

| Dropout mode <sup>(3)</sup>  | $\label{eq:V_SCIN} \begin{split} V_{SCIN} \leq V_{UVLO \ SCIN} \ rising \ threshold \ and \ V_{LDO \ IN} > V_{UVLO \ LDO \ IN} \\ rising \ threshold \ (DC \ supply)^{(4)} \end{split}$ | $I_{OUT} < I_{CL}$ used in the Calculating the Cap-Drop Capacitor $C_S$ section | T <sub>J</sub> < T <sub>SD (Shutdown)</sub> |  |  |  |  |  |  |  |  |

| Dischlad made <sup>(5)</sup> | $V_{LDO_{IN}} < V_{UVLO \ LDO_{IN}}$ falling threshold (V <sub>AC</sub> supply)                                                                                                         | Netopoliaskie                                                                   | т. т                                        |  |  |  |  |  |  |  |  |

| Disabled mode <sup>(5)</sup> | $V_{LDO_{IN}} < V_{UVLO \ LDO_{IN}}$ falling threshold (DC supply)                                                                                                                      | Not applicable                                                                  | $T_J > T_{SD}$ (Shutdown)                   |  |  |  |  |  |  |  |  |

#### 表 1. Device Functional Mode Comparison

(1) The device can function with the V<sub>AC</sub> supply down to 18 V<sub>RMS</sub>; see the *Typical Application* section for details.

(2) The DC supply applied on the SCIN primust be bounded by the V<sub>SCIN</sub> (MAX) > V<sub>SCIN</sub> > V<sub>UVLO\_SCIN</sub> (RISING) threshold as specified in the *Recommended Operating Conditions* and *Electrical Characteristics* tables.

(3) The device can be in dropout when powered by V<sub>AC</sub> or DC supplies; see the *Dropout Voltage Regulation* section for details.

(4) This condition applies after device has started up.

(5) Any true condition disables the device V<sub>LDO\_OUT</sub> and stops the switched-capacitor stage from switching; see the *Disabled Mode* section for details.

#### 8.4.1 Normal Operation

The device is mainly designed to be powered by the AC supply; however, a DC supply can also be used to power the TPS7A78. See the *Active Bridge Control* and *Application and Implementation* sections for proper operation.

#### 8.4.2 Dropout Mode

During dropout mode and when  $V_{LDO_OUT}$  tracks  $V_{LDO_IN}$ , the transient performance becomes significantly degraded because the pass-transistor is operating in the ohmic or triode region.

#### 8.4.3 Disabled Mode

There is no disable pin and disable mode simply means that the output,  $V_{LDO_OUT}$ , is turned off and the switched capacitor (see the 4:1 Switched-Capacitor Voltage Reduction section) is not switching. However, when  $V_{SCIN}$  is less than the  $V_{UVLO_SCIN}$  rising threshold and  $V_{LDO_IN}$  is greater than the  $V_{UVLO_LDO_IN}$  falling threshold, the internal blocks resume normal operation when either the AC or the DC supply is restored.

注

When the device is in disabled mode and powered by an AC supply, the bridge active control (see the *Active Bridge Control* section) continues to run until the AC supply powers off.

# 9 Application and Implementation

#### 注

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

## 9.1 Application Information

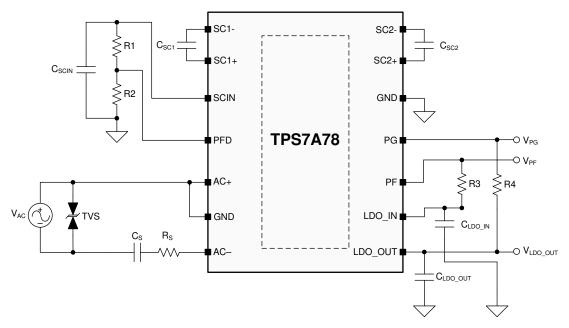

The TPS7A78 is a non-isolated smart AC/DC linear-voltage regulator capable of providing a maximum 120-mA load current; see  $\boxtimes$  14 and  $\boxtimes$  15 for the HB and FB configurations, respectively.

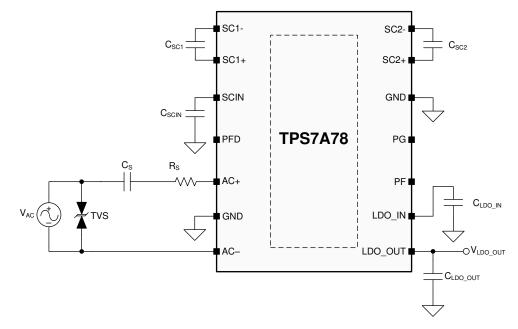

Being highly customizable, the TPS7A78 can be used in many low-power AC-to-DC or DC-to-DC applications, such as electricity meters, appliances, and thermostat controls. 🛛 18 shows an example configuration for a single-phase AC supply.

図 18. Implementation Example for the TPS7A78 Single-Phase AC Supply

## 9.1.1 Recommended Capacitor Types

The choice of capacitor types is flexible as long as the minimum derated capacitor values and capacitor voltage ratings are met.

Based on the system design requirements, TI recommends that greater than the minimum capacitor values and voltage ratings, as well as better than minimum-required dielectric materials for all device capacitors, be specified to ensure optimal performance. Chose the correct high-voltage, safety-rated cap-drop capacitor, C<sub>S</sub>, as required by the application. Regardless of the capacitor types selected, the effective capacitance varies with operating voltage, temperature, and time. Follow the manufacturer recommendations for component derating.

#### 9.1.2 Input and Output Capacitors Requirements

All the capacitors illustrated in  $\boxtimes$  14 or  $\boxtimes$  15 are required for proper operation. The value of C<sub>S</sub> required to support the application current is obtained from the *Calculating the Cap-Drop Capacitor C<sub>S</sub>* section. The chosen C<sub>S</sub> capacitor must tolerate the peak V<sub>AC</sub> supply voltage of the application and meet the required safety requirements.

## **Application Information (continued)**

Choosing an a larger value of the  $C_S$  capacitor than required has an adverse effect on the standby power consumption; however, capacitance reduction over long-term service is inevitable and must be considered when selecting the value of  $C_S$ . A ceramic capacitor can be used as  $C_S$  in designs for lower AC supply voltages, but the capacitor voltage rating must be appropriate to the application.

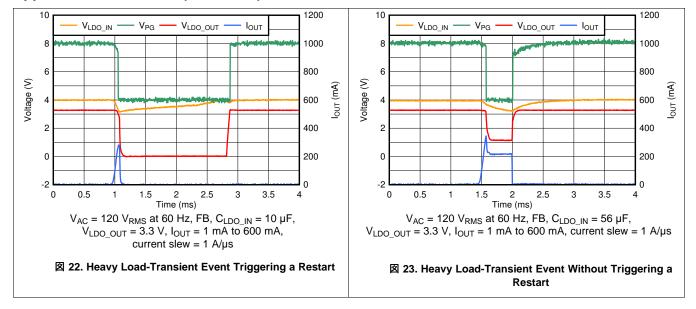

For switching capacitors  $C_{SC1}$  and  $C_{SC2}$ , select the minimum-required capacitor values and voltage ratings specified in the *Recommended Operating Conditions* table. Using too large of a capacitor for the switching capacitors is not recommended because a large capacitor lengthens the start-up time and load transient recovery time of the entire solution. Keep the switching capacitors as close to the device as possible to eliminate any unwanted trace inductance.

For the bulk capacitor  $C_{SCIN}$ , use the minimum required capacitor value obtained from the *Calculating the Bulk Capacitor*  $C_{SCIN}$  section and increase that value based on the expected capacitor degradation resulting from aging and operating conditions. Accounting for capacitor degradation is especially important if a relatively low life expectancy of the capacitor is expected when an electrolytic capacitor is used. If the application requires an extended hold-up time, the values of the  $C_{SCIN}$  or  $C_{LDO_{IN}}$  capacitors can be increased as long as the maximum capacitor values specified in the *Recommended Operating Conditions* table are not exceeded. Using a significantly larger values of  $C_{SCIN}$  or  $C_{LDO_{IN}}$  has an adverse effect on the startup time of the solution.

For the  $C_{LDO_OUT}$  capacitor, maintain a 10:1 ratio between  $C_{LDO_IN}$  and  $C_{LDO_OUT}$  for applications using the maximum load current. For lesser load currents, the minimum required  $C_{LDO_OUT}$  and  $C_{LDOU_IN}$  capacitors are sufficient. For optimum performance, place all capacitors as close as possible to the device.

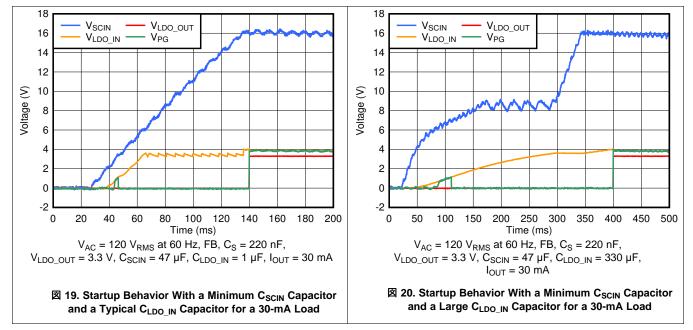

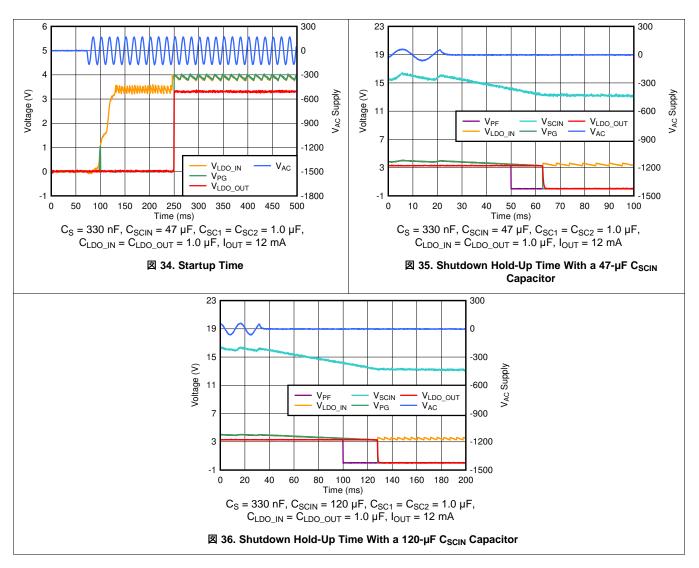

#### 9.1.3 Startup Behavior

The device startup time is dependent on the circuit topology (FB versus HB configuration), AC supply voltage and frequency, input capacitors values, and output voltage. The FB configuration has a faster startup time compared to the HB configuration. Having a larger than minimum  $C_S$  capacitor value shortens the startup time without exceeding the maximum  $I_{SHUNT}$  current specified in the *Recommended Operating Conditions* table. However, startup behavior depends on which  $C_{SCIN}$  and  $C_{LDO_{IN}}$  capacitor values are used. 🖾 19 illustrates the startup behavior with the minimum required  $C_{SCIN}$  capacitor and a typical  $C_{LDO_{IN}}$  capacitor to support 30 mA of load current with the FB configuration. 🖾 20 illustrates the startup behavior with the minimum required  $C_{SCIN}$  capacitor and a large  $C_{LDO_{IN}}$  capacitor in the same configuration.

Although the load current has no effect on startup time or startup behavior, the bulk capacitor  $C_{SCIN}$  and input capacitor  $C_{LDO_IN}$  have a significant effect on the time and behavior; see 219 and 220. For some applications, larger  $C_{SCIN}$  or  $C_{LDO_IN}$  capacitors are used to hold-up the output voltage on for a longer period of time after the input collapses.

## **Application Information (continued)**

#### 9.1.4 Load Transient

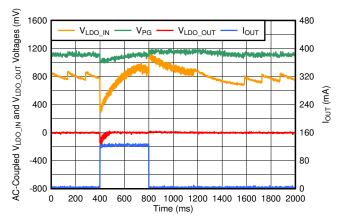

A load-transient event can trigger the internal overcharge protection circuit on the LDO\_IN pin. This condition prevents  $C_{LDO_IN}$  from overcharging when a heavy load is abruptly removed. The overvoltage protection circuit engages and prevents the switched capacitors from switching until the excess charge on  $C_{LDO_IN}$  is discharged into the load. This protection behavior occurs most often during heavy load-transient events on devices with higher output voltages. The value of the  $C_{LDO_IN}$  capacitor and the load current determine how long the overvoltage protection circuit remains engaged. 21 shows the overvoltage protection circuit behavior after the load is removed without tripping the PG signal.

#### 21. Overvoltage Protection Circuit Behavior for a 5.0-V Output Voltage Device During Load Transient

As illustrated in  $\boxtimes$  22, a load-transient event that exceeds the maximum output current can disable the output when the heavy load pulls down the V<sub>LDO\_IN</sub> voltage below the V<sub>UVLO\_LDO\_IN</sub> falling threshold. If the application is prone to heavy load-transient events as illustrated in  $\boxtimes$  22, increase the C<sub>LDO\_IN</sub> capacitor value as necessary. However, as illustrated in  $\boxtimes$  20, too large of a C<sub>LDO\_IN</sub> leads to a longer startup time.

## **Application Information (continued)**

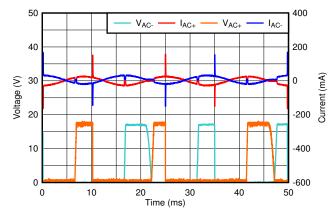

#### 9.1.5 Standby Power and Output Efficiency

The AC input current cannot be directly calculated because of the active bridge control; see the Active Bridge *Control* section. The AC input current through the AC+ and AC- pins is a combination of two current components, as shown in  $\boxtimes$  24: I<sub>SHUNT</sub> and I<sub>PEAK</sub>. The I<sub>SHUNT</sub> current component is identified by its wave profile because this component is the AC charging current supplied by the cap-drop capacitor C<sub>S</sub>. The I<sub>PEAK</sub> current component is identified by its instantaneous peak current profile.

式 1 calculates the shunt current  $I_{SHUNT}$ , and 式 2 calculates the peak current  $I_{PEAK}$ .

$$I_{SHUNT} = V_{AC (MAX)} / XC_S = V_{AC (MAX)} \times 2 \times \pi \times f \times C_S$$

$$I_{PEAK} = V_{SCIN} / R_S$$

(1)

(2)

$I_{PEAK} = V_{SCIN} / R_S$

$$V_{\text{SCIN}} = 4 \times (V_{\text{LDO}_{\text{OUT}(\text{nom})}} + 0.6 \text{ V})$$

where

- $V_{AC (MAX)}$  is the maximum  $V_{AC}$  supply RMS voltage

- $XC_S$  is the impedance of the standard  $C_S$  capacitor to be used in the application

- V<sub>SCIN</sub> is the rectified DC voltage on the SCIN pin

- $R_{\text{S}}$  is the standard  $R_{\text{S}}$  resistor to be used in the application

(3)

## **Application Information (continued)**

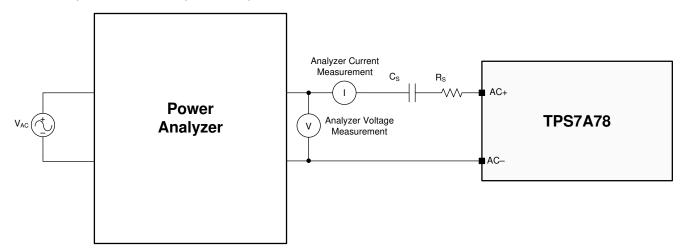

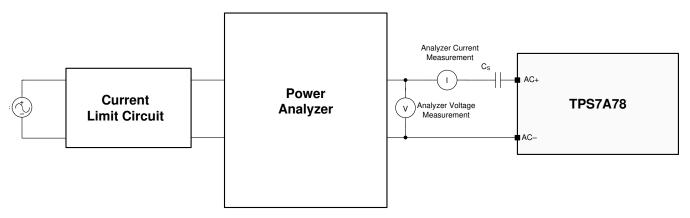

The frequency of the shunt activity is uncorrelated to the AC input frequency. Therefore, the standby power must be measured with a power analyzer. Fortunately, using a power analyzer is relatively simple and the measurement setup shown in  $\boxtimes$  25 and  $\boxtimes$  26 can be used to measure the standby power and the output efficiency.

If the application has an upstream current-limit circuit that limits any high-transient input currents, such as surge or hot-plug currents, the requirement for the surge resistor  $R_S$  can be relaxed. The input transient current-limit circuit allows the  $R_S$  resistor to be removed, thus significantly improving the standby power and output efficiency because no power loss is dissipated in  $R_S$ .

#### 25. Standby Power and Output Efficiency Measurement Setup

26. Standby Power and Output Efficiency Measurement Setup With an Upstream Current-Limit Circuit

### **Application Information (continued)**

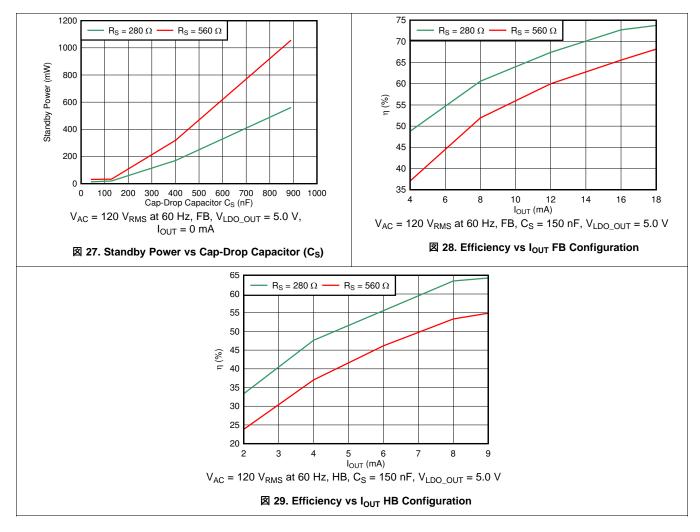

The standby power and output efficiency measurements shown in  $\boxtimes$  27 to  $\boxtimes$  29 were created with the measurement setup in  $\boxtimes$  25.

## 9.1.6 Reverse Current

Excessive reverse current can damage the TPS7A78. Reverse current flows through the intrinsic body diode of the pass-transistor instead of the normal conducting channel. At high magnitudes, this current flow degrades the long-term reliability of the device.

Conditions where reverse current can occur are:

- If the device has a large C<sub>LDO\_OUT</sub> and the input supply collapses with little or no load current

- The LDO\_OUT pin is biased when the input supply is not present

- The LDO\_OUT pin is biased above the voltage of the LDO\_IN pin

If reverse current flow is expected in the application, external protection is recommended to provide protect. Reverse current is not limited within the device, so external limiting is required, as illustrated in  $\boxtimes$  30 and  $\boxtimes$  31, if extended reverse-voltage operation is anticipated.

# **Application Information (continued)**

☑ 30. Example Circuit for Reverse Current Protection Using a Schottky Diode

図 31. Example Circuit for Reverse Current Protection Using a P-Channel FET

#### **Application Information (continued)**

#### 9.1.7 Switched-Capacitor Stage Output Impedance

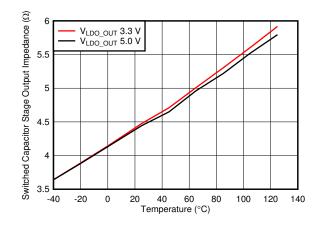

To ensure a low output impedance of the device switched-capacitor stage (charge pump), connect a 1- $\mu$ F X5R or a better dielectric capacitor in parallel with the bulk capacitor C<sub>SCIN</sub>. 2 32 shows the switched-capacitor stage output impedance versus temperature at the maximum output current of 120 mA. When a DC supply power source is used to power the device under heavy loading conditions close to the maximum current rating at high temperature, the load can run the LDO into dropout because of the degradation in the charge pump output impedance. To enhance performance with a DC supply, apply the DC supply voltage to the SCIN pin equal to 4 (VLDO\_OUT (nom) + 0.6 V) + 2 V to ensure optimal performance. See 2 5 and 2 6 for a 3.3-V output voltage example.

図 32. Switched-Capacitor Stage Output Impedance vs Temperature at a 120-mA Load Current

#### 9.1.8 Power Dissipation (P<sub>D</sub>)

To ensure proper thermal design, the printed circuit board (PCB) area around the TPS7A78 must include a minimal of heat-generating devices to avoid added thermal stress. The three internal sources that dissipate power are: the bridge rectifier conduction losses, the switched-capacitor stage, and the LDO. For devices with an output voltage greater 3.3 V, the maximum power dissipation under a maximum load current of 120 mA is estimated to be between 160 mW and 190 mW, assuming a nominal C<sub>S</sub> capacitor value for the given load current. For applications with less than a 3.3-V output , the power dissipated in the LDO is the dominant power and can be calculated using  $\vec{x}$  4 because the dropout voltage between V<sub>LDO\_IN</sub> and V<sub>LDO\_OUT</sub> can be as high as 2.7 V for the 1.3-V output option. See the *Dropout Voltage Regulation* section for details on dropout voltage.

$$\mathsf{P}_{\mathsf{D}_{\mathsf{L}}\mathsf{D}\mathsf{O}} = (\mathsf{V}_{\mathsf{L}\mathsf{D}\mathsf{O}_{\mathsf{I}}\mathsf{N}} - \mathsf{V}_{\mathsf{L}\mathsf{D}\mathsf{O}_{\mathsf{O}}\mathsf{O}\mathsf{U}\mathsf{T}}) \times \mathsf{I}_{\mathsf{O}\mathsf{U}\mathsf{T}}$$

The higher dropout for less than 2.0-V output voltage options may run the device into thermal limitations at the startup ramp for higher temperatures, especially with the large LDO\_OUT pin capacitor or when close to the maximum load. The thermal pad under the TPS7A78 must contain an array of filled vias that conduct heat to additional copper planes for increased heat dissipation. The amount of thermal dissipation determines the maximum allowable ambient temperature (T<sub>A</sub>) for the device. According to  $\exists$  5, power dissipation and junction temperature are determined by the junction-to-ambient thermal resistance (R<sub> $\theta$ JA</sub>) of the combined PCB and device package as well as the temperature of the ambient air (T<sub>A</sub>).

$$T_{J} = T_{A} + (R_{\theta JA} \times P_{D})$$

(5)

Thermal resistance ( $R_{\theta JA}$ ) is highly dependent on the heat-spreading capability built into the particular PCB design, and therefore varies according to the total copper area, copper weight, and location of the planes. The junction-to-ambient thermal resistance listed in the *Thermal Information* table is determined by the JEDEC standard PCB and copper-spreading area, and is used as a relative measure of package thermal performance, but not indicative of performance in any particular implementation.

(4)

## **Application Information (continued)**

#### 9.1.9 Estimating Junction Temperature

The JEDEC standard recommends the use of psi ( $\Psi$ ) thermal metrics to estimate the junction temperatures of the linear regulator when in circuit on a typical PCB board application. These metrics are not thermal resistance parameters and instead offer a practical and relative way to estimate junction temperature. These psi metrics are determined to be significantly independent of the copper area available for heat spreading. The *Thermal Information* table lists the primary thermal metrics, which are the junction-to-top characterization parameter ( $\psi_{JT}$ ) and junction-to-board characterization parameter ( $\psi_{JB}$ ). These parameters provide two methods for calculating the junction temperature ( $T_J$ ). As described in the *Semiconductor and IC Package Thermal Metrics* application report, use the junction temperature. As described in the *Semiconductor and IC Package Thermal Metrics* application *Metrics* application report, use the junction-to-board characterization parameter ( $\psi_{JT}$ ) with the temperature at the center-top of device package ( $T_T$ ) to calculate the junction-to-board characterization parameter ( $\psi_{JB}$ ) with the PCB surface temperature 1 mm from the device package ( $T_B$ ) to estimate the junction temperature.

$$T_{J} = T_{T} + \psi JT \times P_{D_{Total}}$$

where

- P<sub>D Total</sub> is the total dissipated power in the device

- $T_T$  is the temperature at the center-top of the device package

(6)

$T_J = T_B + \psi JB \times P_D$

where

T<sub>B</sub> is the PCB surface temperature measured 1 mm from the device package and centered on the package edge

(7)

For detailed information on the thermal metrics and how to use them, see the Semiconductor and IC Package Thermal Metrics application report.

## 9.2 Typical Application

This section demonstrates the design process for a typical application of the TPS7A78, including the calculation of the values of the external components required for proper operation. 🛛 33 shows an optimized electricity meter application using an HB configuration. For this design, the AC supply line voltage is referenced to the TPS7A78 GND pins to share the same GND as the system microcontroller.

#### 2 33. Example for a Single-Phase Electricity Meter Configuration

#### **Typical Application (continued)**

#### 9.2.1 Design Requirements

表 2 summarizes the design requirement for this example.

| PARAMETER                                | DESIGN REQUIREMENT                                                               |  |  |  |  |  |

|------------------------------------------|----------------------------------------------------------------------------------|--|--|--|--|--|

| V <sub>AC</sub> supply voltage           | 85 V <sub>AC RMS</sub> to 265 V <sub>AC RMS</sub>                                |  |  |  |  |  |

| V <sub>AC</sub> supply frequency         | 50 Hz (±3 Hz)                                                                    |  |  |  |  |  |

| Bridge configuration                     | HB, AC+ pin is tied to the device GND pins                                       |  |  |  |  |  |

| Device GND pins reference                | Floating device GND, AC supply line voltage is referenced to the device GND pins |  |  |  |  |  |

| Output voltage                           | 3.3 V                                                                            |  |  |  |  |  |

| Output current                           | 12 mA                                                                            |  |  |  |  |  |

| Electrical fast transient immunity (EFT) | (IEC 61000-4-4) level 2 (1 kV)                                                   |  |  |  |  |  |

#### 表 2. Design Parameters

#### 9.2.2 Detailed Design Procedure

This section discusses how to calculate the external components required for this design example.

## 9.2.2.1 Calculating the Cap-Drop Capacitor C<sub>S</sub>

Use  $\vec{x}$  8 to calculate the minimum required cap-drop capacitance needed to support the application current. For common application conditions,  $\bar{x}$  3 can be used to select the minimum standard cap-drop capacitor required to support the application current. However, neither  $\vec{x}$  8 nor  $\bar{x}$  3 account for capacitance derating under biasing voltage and operating temperature conditions. Follow the manufacturer recommendation and guidelines on capacitor derating and degradation to ensure the minimum-required capacitance needed for the application under various operating conditions. Do not use a load current less than 10 mA to calculate the C<sub>S</sub> capacitor because the device current is a larger fraction of the load current.  $\vec{x}$  8 and  $\bar{x}$  3 can also be used to calculate the value of C<sub>S</sub> depending on the application V<sub>AC (MIN)</sub> voltage and frequency and then use the highest value for the application.

$$C_{\rm S} = I_{\rm OUT} / (16 \times f \times [\sqrt{2} \times V_{\rm AC (MIN)} - 4 \times (V_{\rm LDO_OUT (nom)} + 0.6 \text{ V})])$$

where

- the C<sub>S</sub> value is the minimum cap-drop capacitance value in farads needed to support I<sub>OUT</sub>

- I<sub>OUT</sub> is the application nominal load current, but the application peak current must be considered if this current cannot be supported by the LDO output capacitor

- V<sub>LDO\_OUT</sub> is the targeted LDO output voltage

- V<sub>AC (MIN)</sub> is the minimum RMS V<sub>AC</sub> supply voltage

- *f* is the minimum V<sub>AC</sub> line frequency

(8)

| V <sub>AC (MIN)</sub> (f) | I <sub>OUT</sub> (mA) | C <sub>S</sub> FOR FB (nF) | C <sub>S</sub> FOR HB (nF) |  |  |

|---------------------------|-----------------------|----------------------------|----------------------------|--|--|

|                           | 10                    | 100                        | 220                        |  |  |

|                           | 30                    | 330                        | 470                        |  |  |

| 120 (60)                  | 60                    | 560                        | 1000                       |  |  |

|                           | 90                    | 820                        | 1500                       |  |  |

|                           | 120                   | 1000                       | 2200                       |  |  |

|                           | 10                    | 47                         | 100                        |  |  |

|                           | 30                    | 150                        | 330                        |  |  |

| 240 (50)                  | 60                    | 330                        | 560                        |  |  |

|                           | 90                    | 470                        | 820                        |  |  |

|                           | 120                   | 560                        | 1200                       |  |  |

| 表 3. The Minimum | Required | Cap-Drop | Capacitor C <sub>S</sub> |

|------------------|----------|----------|--------------------------|

|------------------|----------|----------|--------------------------|

The capacitance value of  $C_S$  from  $\pm 8$  is for the FB configuration. For the HB configuration, double the calculated capacitance value, then approximate the value up to the nearest standard capacitor value after taking capacitance degradation into account. Similarly, the capacitor value of  $C_S$  from  $\pm 3$  represents the minimum required capacitor value and is already approximated to the nearest standard value but capacitor degradation is not accounted for.

#### 9.2.2.1.1 C<sub>s</sub> Calculations for the Typical Design

式 8 yields a capacitance value of 153 nF, as given by 式 9, which results from the V<sub>AC (MIN)</sub> voltage and frequency of this application. This value is for the FB configuration. For the HB configuration, doubling the calculated capacitance value yields 306 nF, and approximate this value up to the nearest standard capacitor value, which yields a C<sub>S</sub> value of 330 nF.

$$C_{s} = (0.012) / (16 \times 47 \times [\sqrt{2} \times 85 - 4(3.3 + 0.6)]) = 153 \text{ nF}$$

(9)

As mentioned in the Calculating the Cap-Drop Capacitor  $C_S$  and Input and Output Capacitors Requirements sections, capacitance loss under long-term service is inevitable and must be considered in the design. Follow the manufacturer recommendations and guidelines for capacitor derating and degradation over time.

#### 9.2.2.2 Calculating the Surge Resistor R<sub>S</sub>

The device requires a surge resistor or resistors in series with the AC+ and or AC- pins, depending configuration; see the *Full-Bridge (FB) and Half-Bridge (HB) Configurations* section for details. The purpose of the surge resistor is to limit the hot-plug AC current into the AC+ and AC- pins when the AC supply voltage is applied.  $\pm$  10 calculates the value of the minimum surge resistor R<sub>S (MIN)</sub> required for the application.

$$R_{S (MIN)} = V_{AC (PEAK)} / I_{Surge (MAX)}$$

where

- $V_{AC (PEAK)}$  is the peak  $V_{AC}$  supply voltage for the application

- I<sub>Surge (MAX)</sub> is the maximum V<sub>AC</sub> current into or out of out the AC+ or AC− pins for a duration of ≤100 µs, as specified in the *Recommended Operating Conditions* table.

If the solution requires the use of a transient voltage surge suppressor (TVS) or a metal-oxide varistor (MOV), then use the maximum clamping voltage of the TVS or MOV instead of the peak  $V_{AC}$  voltage in  $\pm$  10. After calculating  $R_{S (MIN)}$ , select the next-higher standard resistor value.

#### 9.2.2.2.1 R<sub>s</sub> Calculations for the Typical Design

The peak AC supply voltage for this example is equal to 375 V ( $\sqrt{2} \times 265$ ) and the electrical fast transient immunity (EFT) requirement is given as 1 kV. Thus, a TVS with a maximum clamping voltage of 1000 V can be used.  $\vec{x}$  11 shows the calculated R<sub>S (MIN)</sub> value.

$$R_{S (MIN)} = 1000 / 2.5 = 400 \Omega$$

(11)