**TPS65994AD**

# TPS65994AD USB4 および代替モード対応ソース・パワー・スイッチ内蔵、テ ュアル・ポート USB Type-C® および USB PD コントローラ

## 1 特長

- USB-IF による PD3.0 認証済みデバイス

- 新しい USB PD 設計の認証には PD3.0 シリコン が必要

- TID#:3495

- PD2.0 vs. PD3.0 (英語) 記事

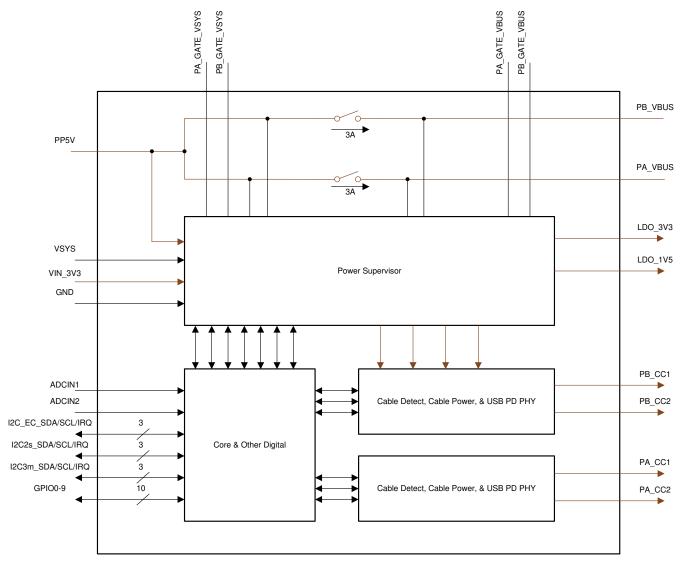

- TPS65994AD は、全体的に設定可能なデュアル・ポ ート USB4 および Thunderbolt 4 (TBT4) PD3.0 コン トローラ

- このデバイスは USB4 ホストおよびデバイス設計に 使用可能

- 産業用拡張温度範囲をサポート

- 各種アプリケーションに合わせて TPS65994AD を 簡単に構成するための GUI ツール

- DisplayPort ソース、Thunderbolt、およびユーザ 一が構成可能な代替モードをサポート

- より詳しいセレクション・ガイドと設計開始に必要な 情報については、www.tij.co.jp/usb-c と E2E ガイ ドをご覧ください。

- 完全に管理されたパワー・パスを内蔵:

- 2 つの 5V、3A、38mΩ ソース・スイッチを内蔵

- UL2367 認証番号:E169910

- IEC62368-1 認証番号:US-34737-M3-UL

- 堅牢なパワー・パス保護機能を内蔵

- ソース・パスの過電圧保護、低電圧保護、逆電流保 護、および可変電流制限機能を内蔵

- シンク・パスの過電圧保護、低電圧保護、逆電流保 護機能を内蔵

- USB Type-C® PD (Power Delivery) コントローラ

- 10 本の構成可能な GPIO

- USB PD 3.0 認証

- USB Type-C 仕様認証

- ケーブル接続および方向の検出

- VCONN スイッチを内蔵

- デッド・バッテリ Rd を内蔵

- 物理層およびポリシー・エンジン

- デッド・バッテリ・サポート用の 3.3V LDO 出力

- 3.3V または VBUS 電源からの電力供給

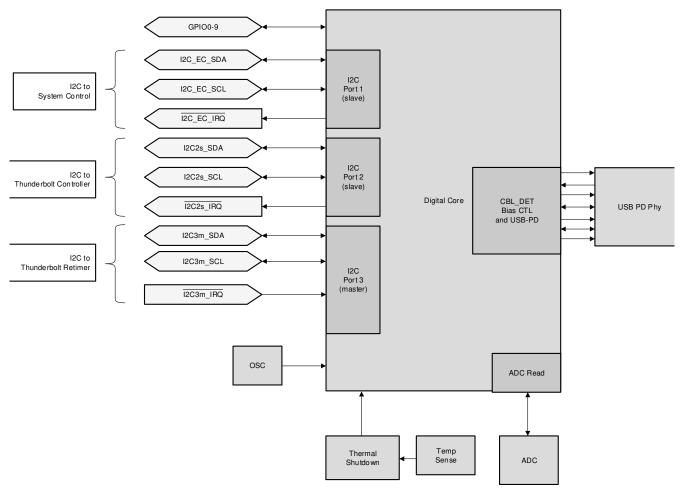

- 1 つの I2C プライマリ・ポート

- 2 つの I2C セカンダリ・ポート

# 2 アプリケーション

- PC およびノート PC

- 高耐久性 PC およびラップトップ

- シングル・ボード・コンピュータ

- ドッキング・ステーション

- フラット・パネル・モニタ

## 3 概要

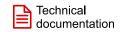

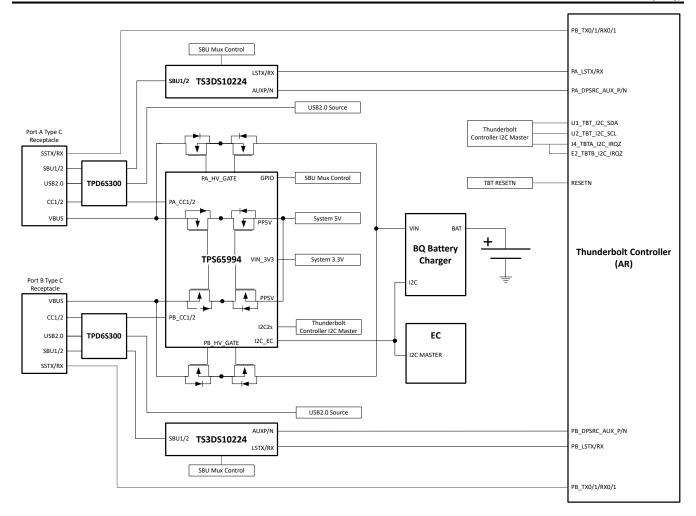

TPS65994AD は、PC およびノートPC アプリケーション 向けの高集積スタンドアロン・デュアル・ポート USB Type-C および PD (Power Delivery) コントローラです。 TPS65994AD は、完全に管理されたソース・パスと堅牢 な保護機能を統合することで包括的な USB-C PD ソリュ ーションを実現しています。 TPS65994AD このデバイス は、インテルと AMD の PC およびノート PC 最終製品リフ ァレンス・デザインに採用されています。このリファレンス・ デザインは、この種の設計において本 PD コントローラが システム・レベルで適切に機能することを保証しています。 これにより、システム設計の複雑さが大幅に緩和され、そ の結果、開発期間を大幅に短縮できます。

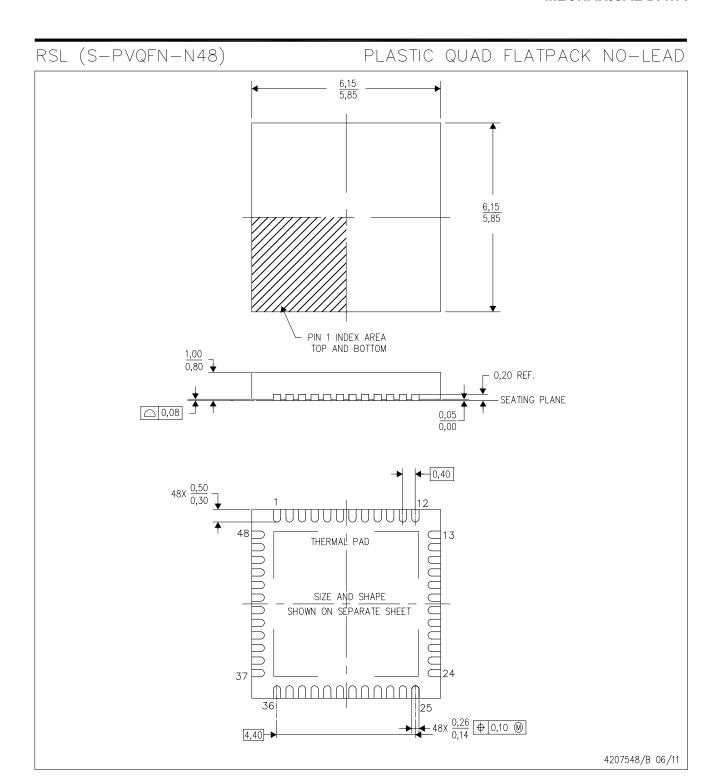

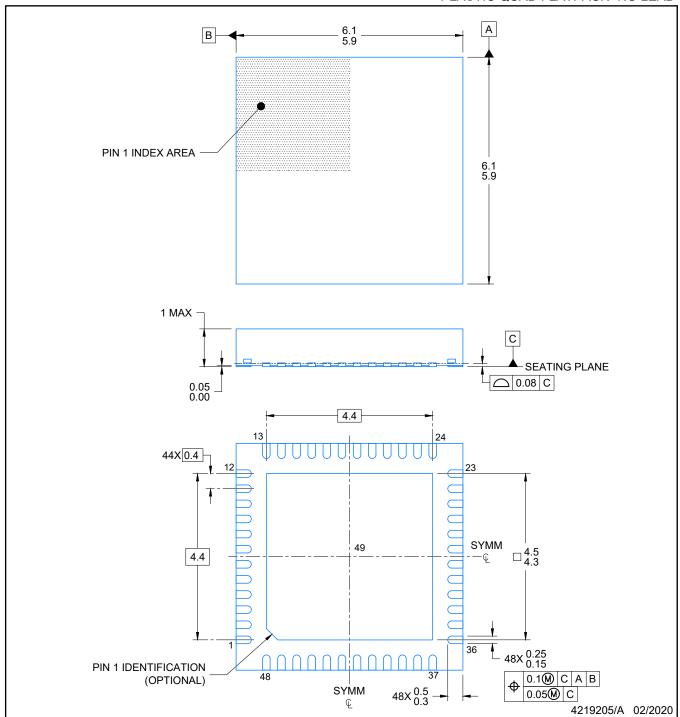

#### 製品情報

| 部品番号 <sup>(1)</sup> | パッケージ     | 本体サイズ (公称)    |

|---------------------|-----------|---------------|

| TPS65994AD          | QFN (RSL) | 6.0mm × 6.0mm |

利用可能なすべてのパッケージについては、このデータシートの 末尾にある注文情報を参照してください。

# **Table of Contents**

| <b>1 特長</b>                               | 1 | 8.2 Functional Block Diagram                | 19 |

|-------------------------------------------|---|---------------------------------------------|----|

| 2 アプリケーション                                | 1 | 8.3 Feature Description                     | 20 |

| 3 概要                                      |   | 8.4 Device Functional Modes                 | 40 |

| 4 Revision History                        |   | 9 Application and Implementation            | 42 |

| 5 Pin Configuration and Functions         |   | 9.1 Application Information                 |    |

| Specifications                            |   | 9.2 Typical Application                     |    |

| 6.1 Absolute Maximum Ratings              |   | 10 Power Supply Recommendations             |    |

| 6.2 ESD Ratings                           |   | 10.1 3.3-V Power                            |    |

| 6.3 Recommended Operating Conditions      |   | 10.2 1.5-V Power                            | 49 |

| 6.4 Recommended Capacitance               |   | 10.3 Recommended Supply Load Capacitance    | 49 |

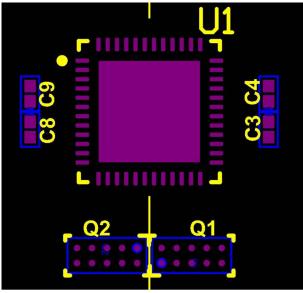

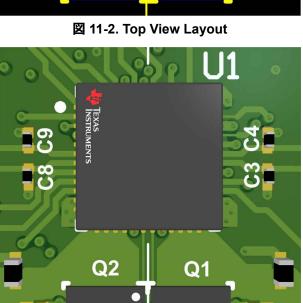

| 6.5 Thermal Information                   |   | 11 Layout                                   |    |

| 6.6 Power Supply Characteristics          |   | 11.1 Layout Guidelines                      |    |

| 6.7 Power Consumption                     |   | 11.2 Layout Example                         |    |

| 6.8 PP_5V Power Switch Characteristics    |   | 11.3 Component Placement                    |    |

| 6.9 PP_EXT Power Switch Characteristics   |   | 11.4 Routing PP_5V, VBUS, VIN_3V3, LDO_3V3, |    |

| 6.10 Power Path Supervisory               |   | LDO_1V5                                     | 52 |

| 6.11 CC Cable Detection Parameters        |   | 11.5 Routing CC and GPIO                    |    |

| 6.12 CC VCONN Parameters                  |   | 12 Device and Documentation Support         |    |

| 6.13 CC PHY Parameters                    |   | 12.1 Device Support                         |    |

| 6.14 Thermal Shutdown Characteristics     |   | 12.2 Documentation Support                  |    |

| 6.15 ADC Characteristics                  |   | 12.3 サポート・リソース                              |    |

| 6.16 Input/Output (I/O) Characteristics   |   | 12.4 Trademarks                             |    |

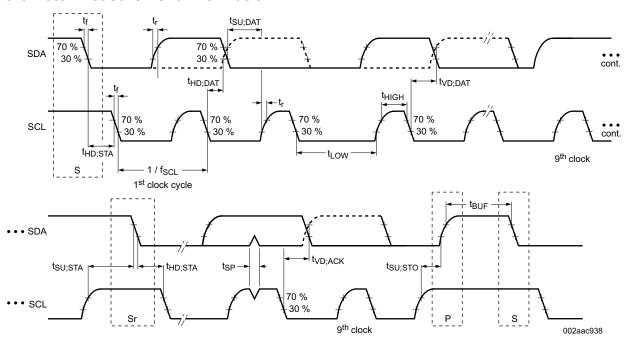

| 6.17 I2C Requirements and Characteristics |   | 12.5 Electrostatic Discharge Caution        |    |

| 6.18 Typical Characteristics              |   | 12.6 Glossary                               |    |

| 7 Parameter Measurement Information       |   | 13 Mechanical, Packaging, and Orderable     |    |

| B Detailed Description                    |   | Information                                 | 56 |

| 8.1 Overview                              |   | 13.1 Package Option Addendum                |    |

| 0.1 0.101.101                             |   | 3 -1                                        |    |

# **4 Revision History**

| C | Changes from Revision * (August 2020) to Revision A (July 2021) | Page |

|---|-----------------------------------------------------------------|------|

| • | 「 <i>特長</i> 」一覧を更新                                              | 1    |

|   | ドキュメントのタイトルを更新                                                  |      |

|   | 「アプリケーション」セクションを更新                                              |      |

|   | 「 <i>概要</i> 」セクションを更新                                           |      |

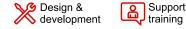

# **5 Pin Configuration and Functions**

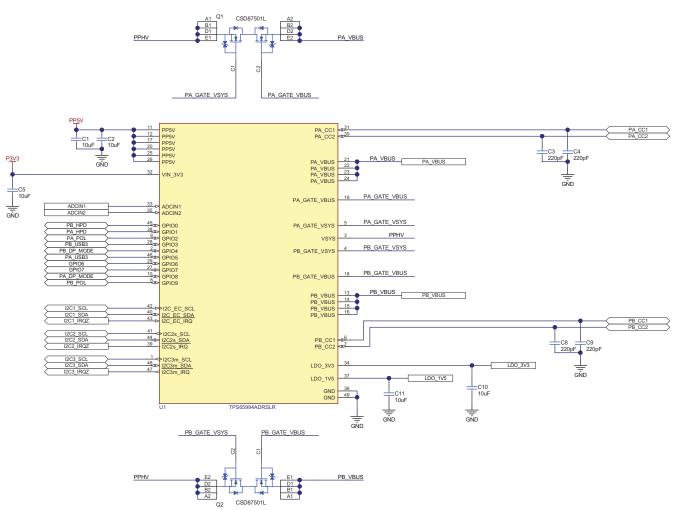

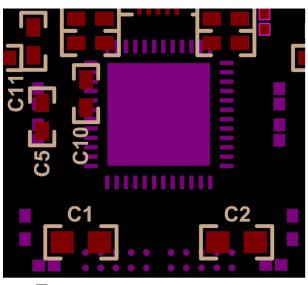

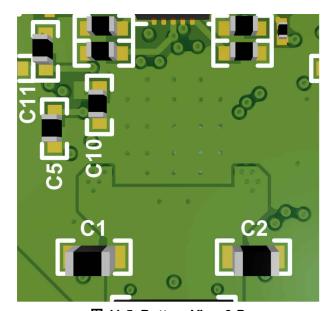

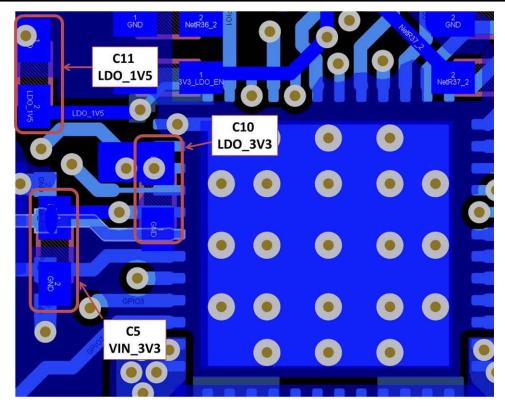

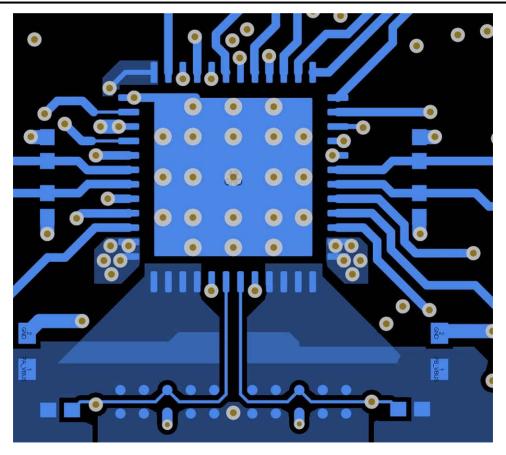

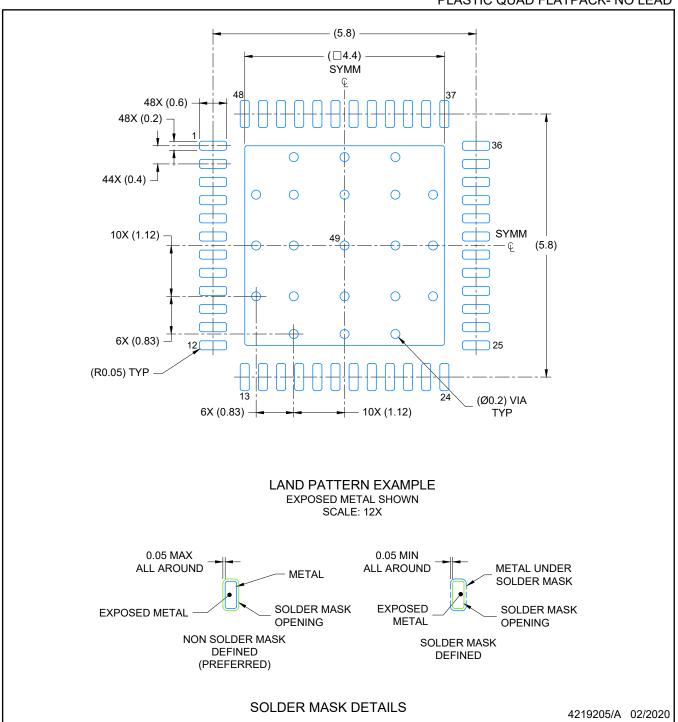

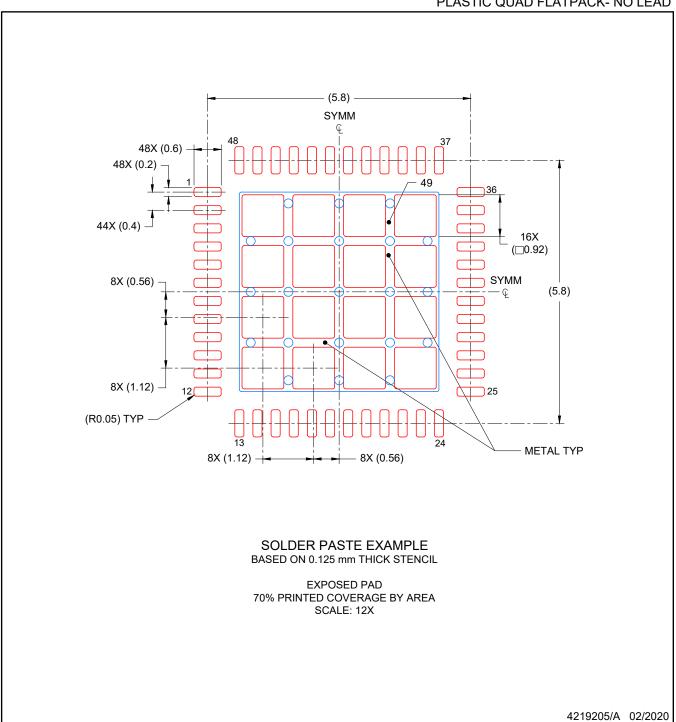

図 5-1. RSL Package 48-pin QFN Top View

表 5-1. Pin Functions

| PII    | N   | TYPE | RESET | Description                                                                                                            |  |

|--------|-----|------|-------|------------------------------------------------------------------------------------------------------------------------|--|

| NAME   | NO. | ITPE | KESEI | Description                                                                                                            |  |

| ADCIN1 | 33  | I    | Hi-Z  | Configuration input. Connect to a resistor divider to LDO_3V3.                                                         |  |

| ADCIN2 | 35  | I    | Hi-Z  | Configuration input. Connect to a resistor divider to LDO_3V3.                                                         |  |

| GND    | 36  | _    | _     | Ground. Connect to ground plane.                                                                                       |  |

| GPIO0  | 45  | I/O  | Hi-Z  | Z General purpose digital I/O. Tie to PP5V or ground when unused. May be used as DisplayPort HPD signal for Port B.    |  |

| GPIO1  | 38  | I/O  | Hi-Z  | Hi-Z General purpose digital I/O. Tie to PP5V or ground when unused. May be used as DisplayPort HPD signal for Port A. |  |

| GPIO2  | 9   | I/O  | Hi-Z  | General purpose digital I/O. Tie to PP5V or ground when unused.                                                        |  |

| GPIO3  | 28  | I/O  | Hi-Z  | General purpose digital I/O. Tie to PP5V or ground when unused.                                                        |  |

| GPIO4  | 2   | I/O  | Hi-Z  | General purpose digital I/O. May be used as an ADC input. Tie to PP5V or ground when unused.                           |  |

| GPIO5  | 46  | I/O  | Hi-Z  | General purpose digital I/O. May be used as an ADC input. Tie to PP5V or ground when unused.                           |  |

| GPIO6  | 29  | I/O  | Hi-Z  | General purpose digital I/O. Tie to PP5V or ground when unused.                                                        |  |

| GPIO7  | 27  | I/O  | Hi-Z  | General purpose digital I/O. Tie to PP5V or ground when unused.                                                        |  |

| GPIO8  | 10  | I/O  | Hi-Z  | General purpose digital I/O. Tie to PP5V or ground when unused.                                                        |  |

# 表 5-1. Pin Functions (continued)

| PIN          | ı                     |      |       | Functions (continued)                                                                                                                                                                         |

|--------------|-----------------------|------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME         | NO.                   | TYPE | RESET | Description                                                                                                                                                                                   |

| GPIO9        | 8                     | 0    | Hi-Z  | General purpose digital output. Tie to PP5V or ground when unused.                                                                                                                            |

| I2C_EC_SCL   | 42                    | I    | Hi-Z  | I2C slave serial clock input. Tie to pullup voltage through a resistor. May be grounded if unused. Connect to Embedded Controller (EC).                                                       |

| I2C_EC_SDA   | 40                    | I/O  | Hi-Z  | I2C slave serial data. Open-drain input/output. Tie to pullup voltage through a resistor. May be grounded if unused. Connect to Embedded Controller (EC).                                     |

| I2C_EC_IRQ   | 43                    | 0    | Hi-Z  | I2C slave interrupt. Active low. Connect to external voltage through a pull-up resistor. Connect to Embedded Controller (EC). This can be re-configured to GPIO10. May be grounded if unused. |

| I2C2s_SCL    | 41                    | I    | Hi-Z  | I2C slave serial clock input. Tie to pull-up voltage through a resistor. May be grounded if unused.                                                                                           |

| I2C2s_SDA    | 44                    | I/O  | Hi-Z  | I2C slave serial data. Open-drain input/output. Tie to pullup voltage through a resistor. May be grounded if unused.                                                                          |

| I2C2s_IRQ    | 39                    | 0    | Hi-Z  | I2C slave interrupt. Active low. Connect to external voltage through a pull-up resistor. Tie to PP5V or ground when unused. This can be re-configured to GPIO11.                              |

| I2C3m_SCL    | 1                     | 0    | Hi-Z  | I2C master serial clock. Open-drain output. Tie to pullup voltage through a resistor when used or unused.                                                                                     |

| I2C3m_SDA    | 48                    | I/O  | Hi-Z  | I2C master serial data. Open-drain input/output. Tie to pullup voltage through a resistor when used or unused.                                                                                |

| I2C3m_IRQ    | 47                    | I    | Hi-Z  | I2C master interrupt. Active low. Connect to external voltage through a pull-up resistor. Tie to PP5V or ground when unused. This can be re-configured to GPIO12.                             |

| LDO_1V5      | 37                    | 0    | _     | Output of the CORE LDO. Bypass with capacitance $C_{LDO\_1V5}$ to GND. This pin cannot source current to external circuits.                                                                   |

| LDO_3V3      | 34                    | 0    | _     | Output of supply switched from VIN_3V3 or VBUS LDO. Bypass with capacitance C <sub>LDO_3V3</sub> to GND.                                                                                      |

| PA_CC1       | 31                    | I/O  | Hi-Z  | I/O for USB Type-C and USB PD. Filter noise with recommended capacitor to GND ( $C_{Px\_CCy}$ ).                                                                                              |

| PA_CC2       | 30                    | I/O  | Hi-Z  | I/O for USB Type-C and USB PD. Filter noise with recommended capacitor to GND ( $C_{Px\_CCy}$ ).                                                                                              |

| PA_GATE_VSYS | 5                     | 0    | Hi-Z  | Connect to the PortA N-ch MOSFET that has source tied to VSYS.                                                                                                                                |

| PA_GATE_VBUS | 19                    | 0    | Hi-Z  | Connect to the N-ch MOSFET that has source tied to PA_VBUS.                                                                                                                                   |

| PA_VBUS      | 21,22,23,24           | I/O  | _     | 5-V to 20-V input or 5-V output from PP5V. Bypass with capacitance $C_{\text{VBUS}}$ to GND.                                                                                                  |

| PB_CC1       | 6                     | I/O  | Hi-Z  | I/O for USB Type-C and USB PD. Filter noise with recommended capacitor to GND ( $C_{Px\_CCy}$ ).                                                                                              |

| PB_CC2       | 7                     | I/O  | Hi-Z  | I/O for USB Type-C and USB PD. Filter noise with recommended capacitor to GND ( $C_{Px\_CCy}$ ).                                                                                              |

| PB_GATE_VSYS | 4                     | 0    | Hi-Z  | Connect to the Port B N-ch MOSFET that has source tied to VSYS.                                                                                                                               |

| PB_GATE_VBUS | 18                    | 0    | Hi-Z  | Connect to the N-ch MOSFET that has source tied to PB_VBUS.                                                                                                                                   |

| PB_VBUS      | 13,14,15,16           | I/O  | _     | 5-V to 20-V input or 5-V output from PP5V. Bypass with capacitance $C_{\text{VBUS}}$ to GND.                                                                                                  |

| PP5V         | 11,12,17,20,25,<br>26 | I    | _     | 5-V System Supply to VBUS, supply for Px_CCy pins as VCONN.                                                                                                                                   |

| VSYS         | 3                     | I    | _     | High-voltage sinking node in the system. It is used to implement reverse-<br>current-protection (RCP) for the external sinking paths controlled by<br>PA_GATE_VSYS and PB_GATE_VSYS.          |

| VIN_3V3      | 32                    | I    | _     | Supply for core circuitry and I/O. Bypass with capacitance C <sub>VIN_3V3</sub> to GND.                                                                                                       |

|              |                       |      |       |                                                                                                                                                                                               |

# **6 Specifications**

## 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

| -                                       |                                                                                                     | MIN                | MAX             | UNIT |  |

|-----------------------------------------|-----------------------------------------------------------------------------------------------------|--------------------|-----------------|------|--|

|                                         | PP5V                                                                                                | -0.3               | 6               |      |  |

|                                         | VIN_3V3                                                                                             | -0.3               | 4               | V    |  |

|                                         | ADCIN1, ADCIN2                                                                                      | -0.3               | 4               |      |  |

|                                         | VSYS, PA_VBUS, PB_VBUS (4)                                                                          | -0.3               | 28              |      |  |

| Input voltage range <sup>(2)</sup>      | PA_CC1, PA_CC2, PB_CC1, PB_CC2                                                                      | -0.5               | 6               |      |  |

|                                         | GPIO0-GPIO9, IZC_EC_IRQ, IZC2s_IRQ, IZC3m_IRQ                                                       | -0.3               | 6               | V    |  |

|                                         | I2C_EC_SDA, I2C_EC_SCL,I2C2s_SDA,<br>I2C2s_SCL, I2C3m_SDA, I2C3m_SCL                                | -0.3               | 4               |      |  |

| 2                                       | LDO_1V5 <sup>(3)</sup>                                                                              | -0.3               | 2               | .,   |  |

| Output voltage range <sup>(2)</sup>     | LDO_3V3 <sup>(3)</sup>                                                                              | -0.3               | 4               | V    |  |

| Output voltage range <sup>(2)</sup>     | PA_GATE_VBUS, PA_GATE_VSYS,<br>PB_GATE_VBUS, PB_GATE_VSYS (3)                                       | -0.3               | 40              | V    |  |

| V <sub>GS</sub>                         | V <sub>Px_GATE_VBUS</sub> - V <sub>Px_VBUS</sub> , V <sub>Px_GATE_SYS</sub> - V <sub>VSYS</sub>     | -0.5               | 12              | V    |  |

|                                         | Source or sink current PA_VBUS, PB_VBUS                                                             | internally limited |                 |      |  |

|                                         | Positive source current on PA_CC1, PA_CC2, PB_CC1, PB_CC2                                           |                    | 1               |      |  |

| Source current                          | Positive sink current on PA_CC1, PA_CC2, PB_CC1, PB_CC2 while VCONN switch is enabled               | 1                  |                 | Α    |  |

|                                         | GPIO0-GPIO9                                                                                         |                    | 0.005           |      |  |

|                                         | positive sink current for I2C_EC_SDA,<br>I2C_EC_SCL, I2C2s_SDA, I2C2s_SCL,<br>I2C3m_SDA, I2C3m_SCL, | inte               | ernally limited |      |  |

|                                         | positive source current for LDO_3V3, LDO_1V5                                                        | inte               | rnally limited  |      |  |

| T <sub>J</sub> Operating junction tempe | rature                                                                                              | -40                | 175             | °C   |  |

| T <sub>STG</sub> Storage temperature    |                                                                                                     | <b>–</b> 55        | 150             | °C   |  |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Rating may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- (2) All voltage values are with respect to network GND. Connect the GND pin directly to the GND plane of the board.

- (3) Do not apply voltage to these pins.

- (4) For Px\_VBUS a TVS with a break down voltage falling between the Recommended max and the Abs max value is recommended such as TVS2200. For Px\_VBUS a Schottky diode is recommended to ensure the MIN voltage is not violated.

## 6.2 ESD Ratings

|                    | PARAMETER TEST CONDITIONS |                                                                                               | VALUE | UNIT |

|--------------------|---------------------------|-----------------------------------------------------------------------------------------------|-------|------|

|                    |                           | Human body model (HBM), per ANSI/<br>ESDA/JEDEC JS-001, all pins <sup>(1)</sup>               | ±1000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge   | Charged device model (CDM), per<br>JEDEC specificationJESD22-C101, all<br>pins <sup>(2)</sup> | ±500  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## **6.3 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)(1)

|                 |                                |                                                                                              | MIN | MAX | UNIT |

|-----------------|--------------------------------|----------------------------------------------------------------------------------------------|-----|-----|------|

|                 |                                | VIN_3V3                                                                                      | 3.0 | 3.6 |      |

| VI              | Input voltage range (1)        | PP5V <sup>(2)</sup>                                                                          | 4.9 | 5.5 | V    |

|                 |                                | PA_VBUS, PB_VBUS (3)                                                                         | 4   | 22  |      |

| VI              | Input voltage range (1)        | VSYS                                                                                         | 0   | 22  | V    |

|                 |                                | I2Cx_SDA, I2Cx_SCL, ADCIN1,<br>ADCIN2                                                        | 0   | 3.6 |      |

| V <sub>IO</sub> | I/O voltage range (1)          | GPIOx, IZC_EC_IRQ, IZC2s_IRQ, IZC3m_IRQ                                                      | 0   | 5.5 | ٧    |

|                 |                                | PA_CC1, PA_CC2, PB_CC1,<br>PB_CC2                                                            | 0   | 5.5 |      |

|                 |                                | PA_VBUS, PB_VBUS                                                                             |     | 3   | А    |

| I <sub>O</sub>  | Output current (from PP5V)     | PA_CC1, PA_CC2, PB_CC1,<br>PB_CC2                                                            |     | 315 | mA   |

| Io              | Output current (from LDO_3V3)  | GPIOx                                                                                        |     | 1   | mA   |

| I <sub>O</sub>  | Output current (from VBUS LDO) | sum of current from LDO_3V3 and GPIO0-9.                                                     |     | 5   | mA   |

| T <sub>A</sub>  | Ambient enerating temperature  | I <sub>PP_5VX</sub> ≤ 1.5 A, I <sub>PP_5Vy</sub> ≤ 3.0 A,<br>I <sub>PP_CABLEX</sub> ≤ 315 mA | -40 | 105 | °C   |

|                 | Ambient operating temperature  | I <sub>PP_5Vx</sub> ≤ 3.0 A, I <sub>PP_CABLEx</sub> ≤ 315 mA                                 | -40 | 85  | C    |

| T <sub>J</sub>  | Operating junction temperature |                                                                                              | -40 | 125 | °C   |

- (1) All voltage values are with respect to network GND. All GND pins must be connected directly to the GND plane of the board.

- (2) Maximum current sourced from PP5V to PA\_VBUS or PB\_VBUS. Resistance from Px\_VBUS to Type-C connector less than or equal 30 mΩ. Short all PP5V bumps together.

- (3) All PA\_VBUS bumps should be shorted together. All PB\_VBUS bumps should be shorted together.

#### 6.4 Recommended Capacitance

over operating free-air temperature range (unless otherwise noted)

|                      | PARAMETER <sup>(1)</sup>                  | VOLTAGE RATING | MIN                | NOM | MAX | UNIT |

|----------------------|-------------------------------------------|----------------|--------------------|-----|-----|------|

| C <sub>VIN_3V3</sub> | Capacitance on VIN_3V3                    | 6.3 V          | 5                  | 10  |     | μF   |

| C <sub>LDO_3V3</sub> | Capacitance on LDO_3V3                    | 6.3 V          | 5                  | 10  | 25  | μF   |

| C <sub>LDO_1V5</sub> | Capacitance on LDO_1V5                    | 4 V            | 4.5                |     | 12  | μF   |

| C <sub>Px_VBUS</sub> | Capacitance on VBUS <sup>(4)</sup>        | 25 V           | 1                  | 4.7 | 10  | μF   |

| C <sub>PP5V</sub>    | Capacitance on PP5V                       | 10 V           | 120 <sup>(2)</sup> |     |     | μF   |

| C <sub>VSYS</sub>    | Capacitance on VSYS Sink from VBUS        | 25 V           |                    | 47  | 100 | μF   |

| C <sub>Px_CCy</sub>  | Capacitance on Px_CCy pins <sup>(3)</sup> | 6.3 V          | 200                | 320 | 480 | pF   |

- (1) Capacitance values do not include any derating factors. For example, if 5.0 μF is required and the external capacitor value reduces by 50% at the required operating voltage, then the required external capacitor value would be 10 μF.

- (2) This is a requirement from USB PD (cSrcBulkShared). Keep at least 10 µF tied directly to PP5V.

- (3) This includes all capacitance to the Type-C receptacle.

- (4) The device can be configured to quickly disable PP\_EXT upon certain events. When such a configuration is used, a capacitance on the higher side of this range is recommended.

# 6.5 Thermal Information

|                        |                                           | DEVICE    |      |

|------------------------|-------------------------------------------|-----------|------|

|                        | THERMAL METRIC                            | QFN (RSL) | UNIT |

|                        |                                           | 48 PINS   | 1    |

| $R_{\theta JA}$        | Junction-to-ambient thermal resistance    | 26.8      | °C/W |

| R <sub>θJC</sub> (top) | Junction-to-case (top) thermal resistance | 15.4      | °C/W |

Submit Document Feedback

# 6.5 Thermal Information (continued)

|                           |                                                      | DEVICE    |      |

|---------------------------|------------------------------------------------------|-----------|------|

| THE                       | RMAL METRIC                                          | QFN (RSL) | UNIT |

|                           |                                                      | 48 PINS   |      |

| $R_{\theta JB}$           | Junction-to-board thermal resistance                 | 8.5       | °C/W |

| ΨЈТ                       | Junction-to-top characterization parameter           | 0.2       | °C/W |

| ΨЈВ                       | Junction-to-board characterization parameter         | 8.5       | °C/W |

| R <sub>θJC</sub> (bottom) | Junction-to-case (bottom GND pad) thermal resistance | 1.8       | °C/W |

# **6.6 Power Supply Characteristics**

Operating under these conditions unless otherwise noted: 3.0 V  $\leq$  V<sub>VIN\_3V3</sub>  $\leq$  3.6 V

|                        | PARAMETER                                | TEST CONDITIONS                                                                                   | MIN  | TYP  | MAX  | UNIT |  |

|------------------------|------------------------------------------|---------------------------------------------------------------------------------------------------|------|------|------|------|--|

| VIN_3V3, Px_VBUS       |                                          |                                                                                                   |      |      |      |      |  |

|                        |                                          | rising, V <sub>Px_VBUS</sub> =0                                                                   | 2.56 | 2.66 | 2.76 |      |  |

| $V_{VIN3V3\_UVLO}$     | voltage required on VIN_3V3 for power on | falling, V <sub>Px_VBUS</sub> =0                                                                  | 2.44 | 2.54 | 2.64 | V    |  |

|                        | perior cir                               | hysteresis                                                                                        |      | 0.12 |      |      |  |

|                        |                                          | rising                                                                                            | 3.6  |      | 3.9  |      |  |

| V <sub>VBUS_UVLO</sub> | UVLO comparator for Px_VBUS              | falling                                                                                           | 3.5  |      | 3.8  | V    |  |

|                        |                                          | hysteresis                                                                                        |      | 0.1  |      |      |  |

| LDO_3V3, LDO_1V5       |                                          |                                                                                                   |      |      | '    |      |  |

| V <sub>LDO_3V3</sub>   | voltage on LDO_3V3                       | $V_{VIN\_3V3} = 0V$ , $I_{LDO\_3V3} \le 5$ mA, $V_{PA\_VBUS} \ge 3.9V$ or $V_{PB\_VBUS} \ge 3.9V$ | 2.7  | 3.4  | 3.6  | V    |  |

| R <sub>LDO_3V3</sub>   | Rdson of VIN_3V3 to LDO_3V3              | I <sub>LDO_3V3</sub> =50mA                                                                        |      |      | 1.5  | Ω    |  |

| V <sub>LDO_1V5</sub>   | Output voltage of LDO_1V5                | up to maximum internal loading condition.                                                         |      | 1.55 |      | V    |  |

# **6.7 Power Consumption**

Operating under these conditions unless otherwise noted: 3.0 V  $\leq$  V<sub>VIN\_3V3</sub>  $\leq$  3.6 V, no loading on GPIO pins

| PA                          | RAMETER                                                               | TEST CONDITIONS                                                                                             | MIN | TYP | MAX | UNIT |

|-----------------------------|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| I <sub>VIN_3V3,ActSrc</sub> | current into VIN_3V3                                                  | Active Source mode: V <sub>PP5V</sub> =5.0V, V <sub>VIN_3V3</sub> =3.3V                                     |     | 4.5 | 12  | mA   |

| I <sub>VIN_3V3,ActSnk</sub> | current into VIN_3V3                                                  | Active Sink mode: $22V \ge V_{PA\_VBUS} \ge 4.0V$ , $22V \ge V_{PB\_VBUS} \ge 4.0V$ , $V_{VIN\_3V3} = 3.3V$ |     | 4.8 | 12  | mA   |

| I <sub>VSYS</sub>           | current into VSYS                                                     |                                                                                                             |     | 10  |     | μA   |

| I <sub>VIN_3V3,IdlSrc</sub> | current into VIN_3V3                                                  | Idle Source mode: V <sub>PA_VBUS</sub> =5.0V, V <sub>PB_VBUS</sub> =5.0V, V <sub>VIN_3V3</sub> =3.3V        |     | 1.1 |     | mA   |

| I <sub>VIN_3V3,IdlSnk</sub> | current into VIN_3V3                                                  | Idle Sink mode: $22V \ge V_{PA\_VBUS} \ge 4.0V$ , $22V \ge V_{PB\_VBUS} \ge 4.0V$ , $V_{VIN\_3V3} = 3.3V$   |     | 1.1 |     | mA   |

| P <sub>MstbySnk</sub>       | Power drawn into PP5V<br>and VIN_3V3 in Modern<br>Standby Sink Mode   | Modern Standby Sink Mode: $V_{PP5V}$ = 5V, $V_{VIN\_3V3}$ =3.3V, $V_{PA\_VBUS}$ =5.0V, $V_{PB\_VBUS}$ =0V   |     | 3.7 |     | mW   |

| P <sub>MstbySrc</sub>       | Power drawn into PP5V<br>and VIN_3V3 in Modern<br>Standby Source Mode | Modern Standby Source Mode: $V_{PP5V}$ = 5V, $V_{VIN\_3V3}$ =3.3V, $I_{Px\_VBUS}$ =0                        |     | 4.5 |     | mW   |

| I <sub>VIN_3V3,Sleep</sub>  | current into VIN_3V3                                                  | Sleep mode: $V_{PA\_VBUS}$ =0V, $V_{PB\_VBUS}$ =0V, $V_{VIN\_3V3}$ =3.3V, $T_J$ $\leq$ 25 °C                |     | 67  |     | μΑ   |

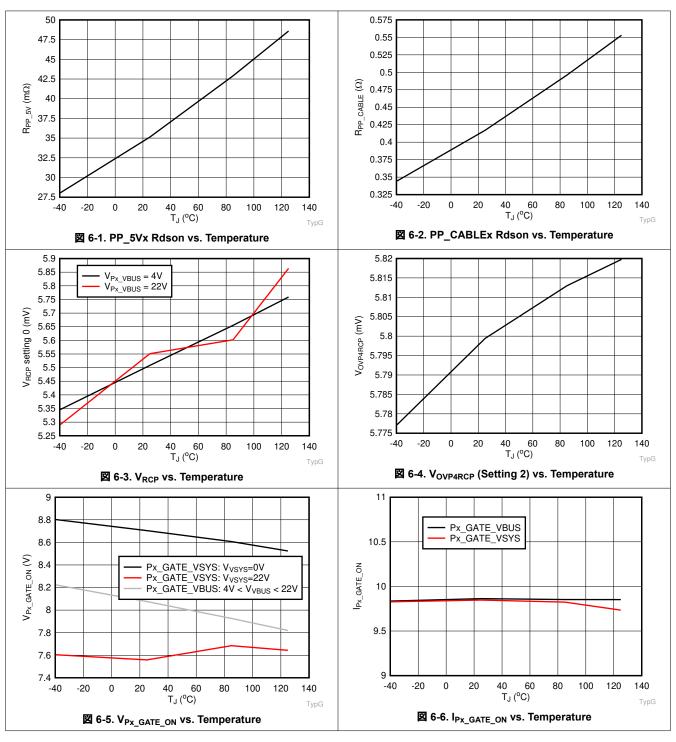

# 6.8 PP\_5V Power Switch Characteristics

Operating under these conditions unless otherwise noted:  $3.0 \text{ V} \le \text{V}_{\text{VIN}\_3\text{V}3} \le 3.6\text{V}$

|                         | PARAMETER                                                                                                                                                         | TEST CONDITIONS                                                                                                                                                                                                                                                                                             | MIN  | TYP  | MAX  | UNIT |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| D                       | Desistance from DD5V/45 Dv. VD1/6                                                                                                                                 | I <sub>LOAD</sub> = 3 A, T <sub>J</sub> ≤25°C                                                                                                                                                                                                                                                               |      | 37.7 | 41.5 | 0    |

| R <sub>PP_5V</sub>      | Resistance from PP5V to Px_VBUS                                                                                                                                   | I <sub>LOAD</sub> = 3 A, T <sub>J</sub> ≤125°C                                                                                                                                                                                                                                                              |      | 37.7 | 57   | mΩ   |

| I <sub>PP5V_REV</sub>   | Px_VBUS to PP5V leakage current                                                                                                                                   | V <sub>PP5V</sub> = 0V, V <sub>PX_VBUS</sub> = 5.5V, PP_5V disabled, T <sub>J</sub> ≤85°C, measure I <sub>PP5V</sub>                                                                                                                                                                                        |      | 0    | 3    | μΑ   |

| I <sub>PP5V_FWD</sub>   | PP5V to Px_VBUS leakage current                                                                                                                                   | V <sub>PP5V</sub> = 5.5V, V <sub>Px_VBUS</sub> =<br>0V, PP_5V disabled,<br>T <sub>J</sub> ≤85°C, measure I <sub>Px_VBUS</sub>                                                                                                                                                                               |      | 0    | 15   | μΑ   |

| I <sub>LIM5V</sub>      | Current limit setting                                                                                                                                             | Configure to setting 0                                                                                                                                                                                                                                                                                      | 1.15 |      | 1.36 | Α    |

| I <sub>LIM5V</sub>      | Current limit setting                                                                                                                                             | configure to setting 1                                                                                                                                                                                                                                                                                      | 1.61 |      | 1.90 | Α    |

| I <sub>LIM5V</sub>      | Current limit setting                                                                                                                                             | configure to setting 2                                                                                                                                                                                                                                                                                      | 2.3  |      | 2.70 | Α    |

| I <sub>LIM5V</sub>      | Current limit setting                                                                                                                                             | configure to setting 3                                                                                                                                                                                                                                                                                      | 3.04 |      | 3.58 | Α    |

| I <sub>LIM5V</sub>      | Current limit setting                                                                                                                                             | configure to setting 4                                                                                                                                                                                                                                                                                      | 3.22 |      | 3.78 | Α    |

| I <sub>Px_VBUS</sub>    | PP5V to Px_VBUS current sense accuracy                                                                                                                            | $3.0A \ge I_{P_{X\_VBUS}} \ge 1A,$<br>$V_{VIN\_3V3} = \overline{3.3V}$                                                                                                                                                                                                                                      | 2.8  | 3.4  | 4.1  | A/V  |

| V <sub>PP_5V_RCP</sub>  | RCP clears and PP_5Vx starts turning on when V <sub>PX_VBUS</sub> - V <sub>PP5V</sub> < V <sub>PP_5V_RCP</sub> . Measure V <sub>PX_VBUS</sub> - V <sub>PP5V</sub> |                                                                                                                                                                                                                                                                                                             | 10   | 15   | 20   | mV   |

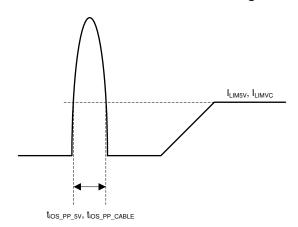

| t <sub>iOS_PP_5V</sub>  | response time to VBUS short circuit                                                                                                                               | Px_VBUS to GND through 10mΩ, C <sub>Px_VBUS</sub> =0                                                                                                                                                                                                                                                        |      | 1.15 |      | μs   |

| t <sub>PP_5V_ovp</sub>  | response time to V <sub>Px_VBUS</sub> > V <sub>OVP4RCP</sub>                                                                                                      | Enable PP_5Vx, ramp<br>V <sub>Px_VBUS</sub> from 4V to 20V at<br>100 V/ms                                                                                                                                                                                                                                   |      | 4.5  |      | μs   |

| t <sub>PP_5V_uvlo</sub> | response time to $V_{PP5V}$ < $V_{PP5V\_UVLO}$ , $PP\_VBUS$ is deemed off when $V_{Px\_VBUS}$ < 0.8V                                                              | R <sub>L</sub> = 100 Ω, no external capacitance on Px_VBUS                                                                                                                                                                                                                                                  |      | 4    |      | μs   |

| t <sub>PP_5V_rcp</sub>  | response time to V <sub>PP5V</sub> < V <sub>Px_VBUS</sub> +V <sub>PP_5V_RCP</sub>                                                                                 | V <sub>PP5V</sub> =5.5V,enable<br>PP_5Vx, ramp V <sub>Px_VBUS</sub><br>from 4V to 21.5V at 10 V/μs                                                                                                                                                                                                          |      | 0.7  |      | μs   |

| <sup>t</sup> FRS_on     | Time allowed to enable the pass FET in PP_5Vx with 3A current limit.                                                                                              | $\begin{aligned} & \text{Initial V}_{\text{Px\_VBUS}} = \text{0V, } 2\mu\text{F} \leq \\ & \text{C}_{\text{Px\_VBUS}} \leq 20\mu\text{F, } 0 \leq \\ & \text{I}_{\text{Px\_VBUS}} \leq 0.5 \text{ A, FET is} \\ & \text{deemed enabled when} \\ & \text{V}_{\text{Px\_VBUS}} > 4.75\text{V.} \end{aligned}$ |      | 54   | 150  | μs   |

| t <sub>ILIM</sub>       | Current clamping deglitch time                                                                                                                                    |                                                                                                                                                                                                                                                                                                             |      | 5    |      | ms   |

| t <sub>ON</sub>         | from enable signal to Px_VBUS at 90% of final value                                                                                                               | $R_L = 100\Omega, V_{PP5V} = 5V,$<br>$C_L = 0$                                                                                                                                                                                                                                                              | 2.6  | 3.5  | 4.4  | ms   |

| t <sub>OFF</sub>        | from disable signal to Px_VBUS at 10% of final value                                                                                                              | $R_L = 100\Omega, V_{PP5V} = 5V,$<br>$C_L = 0$                                                                                                                                                                                                                                                              | 0.30 | 0.45 | 0.6  | ms   |

| t <sub>RISE</sub>       | Px_VBUS from 10% to 90% of final value                                                                                                                            | $R_L = 100\Omega$ , $V_{PP5V} = 5V$ , $C_L=0$                                                                                                                                                                                                                                                               | 1.2  | 1.7  | 2.2  | ms   |

| t <sub>FALL</sub>       | Px_VBUS from 90% to 10% of initial value                                                                                                                          | $R_L = 100\Omega, V_{PP5V} = 5V,$<br>$C_L = 0$                                                                                                                                                                                                                                                              | 0.06 | 0.1  | 0.14 | ms   |

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

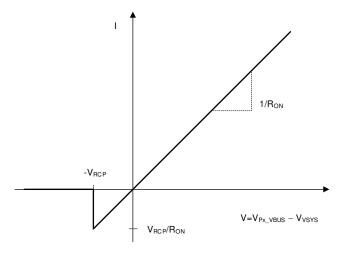

# 6.9 PP\_EXT Power Switch Characteristics

Operating under these conditions unless otherwise noted: 3.0 V  $\leq$  V<sub>VIN\_3V3</sub>  $\leq$  3.6 V

|                               | PARAMETER                                                                                                                       | TEST CONDITIONS                                                                                                                                                                                                   | MIN  | TYP | MAX  | UNIT  |

|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|-------|

| L                             | Cata driver coursing current                                                                                                    | $ 0 \le V_{Px\_GATE\_VSYS} - V_{VSYS} \le $ $ 6 \text{ V, } 0 \text{ V} \le V_{VSYS} \le 22 \text{ V, } $ $ V_{Px\_VBUS} > 4 \text{ V, measure } $ $ I_{Px\_GATE\_VSYS} $                                         | 8.5  | 10  | 11.5 | μΑ    |

| I <sub>Px_</sub> gate_on      | Gate driver sourcing current                                                                                                    | $\begin{array}{l} 0 \leq V_{PX\_GATE\_VBUS^-} \\ V_{PX\_VBUS} \leq 6 \text{ V, 4 V} \leq \\ V_{PX\_VBUS} \leq 22 \text{ V, measure} \\ I_{Px\_GATE\_VBUS} \end{array}$                                            | 8.5  | 10  | 11.5 | μА    |

| V <sub>Px_GATE_</sub> ON      | sourcing voltage (ON)                                                                                                           | $\label{eq:controller} \begin{split} 0 &\leq V_{VSYS} \leq 22 \text{ V,} \\ I_{Px\_GATE\_VSYS} &< 4  \mu\text{A,} \\ \text{measure } V_{Px\_GATE\_VSYS} &- \\ V_{VSYS}, V_{Px\_VBUS} &> 4 \text{ V.} \end{split}$ | 6    |     | 12   | V     |

|                               | sourcing voltage (ON)                                                                                                           | $ \begin{cases} 4 \text{ V} \leq \text{V}_{Px\_VBUS} \leq 22 \text{ V,} \\ I_{Px\_GATE\_VBUS} < 4  \mu\text{A,} \\ \text{measure } \text{V}_{Px\_GATE\_VBUS} - \\ \text{V}_{Px\_VBUS}. \end{cases} $              | 6    |     | 12   | V     |

|                               |                                                                                                                                 | setting 0, 4 V ≤ V <sub>Px_VBUS</sub> ≤ 22 V, V <sub>VIN_3V3</sub> ≤ 3.63 V                                                                                                                                       | 2    | 6   | 10   | mV    |

| V <sub>RCP</sub>              | comparator mode RCP threshold,                                                                                                  | setting 1, 4 V ≤ V <sub>Px_VBUS</sub> ≤ 22 V, V <sub>VIN_3V3</sub> ≤ 3.63 V                                                                                                                                       | 4    | 8   | 12   | mV    |

|                               | V <sub>VSYS</sub> - V <sub>Px_VBUS</sub> .                                                                                      | setting 2, 4 V ≤ V <sub>Px_VBUS</sub> ≤ 22 V, V <sub>VIN_3V3</sub> ≤ 3.63 V                                                                                                                                       | 6    | 10  | 14   | mV    |

|                               |                                                                                                                                 | setting 3, 4 V ≤ V <sub>Px_VBUS</sub> ≤ 22 V, V <sub>VIN_3V3</sub> ≤ 3.63 V                                                                                                                                       | 8    | 12  | 16   | mV    |

|                               |                                                                                                                                 | normal turnoff: $V_{VSYS} = 5V$ , $V_{Px\_GATE\_VSYS} = 6V$                                                                                                                                                       | 13   |     |      | μΑ    |

| I <sub>Px_GATE_OFF</sub>      | Sinking strength                                                                                                                | normal turnoff: $V_{Px\_VBUS} = 5V$ , $V_{Px\_GATE\_VBUS} = 6V$ , $V_{VSYS} = 5V$                                                                                                                                 | 13   |     |      | μА    |

|                               |                                                                                                                                 | fast turnoff: V <sub>VSYS</sub> = 5V,<br>V <sub>Px_GATE_VSYS</sub> =6V,                                                                                                                                           |      |     | 85   | Ω     |

| R <sub>Px_GATE_</sub> FSD     | Sinking strength                                                                                                                | fast turnoff: V <sub>PX_VBUS</sub> = 5V,<br>V <sub>PX_GATE_VBUS</sub> =6V, V <sub>VSYS</sub> =<br>5 V                                                                                                             |      |     | 85   | Ω     |

| R <sub>Px_GATE_OFF_UVLO</sub> | Sinking strength in UVLO (safety)                                                                                               | V <sub>VIN_3V3</sub> =0V,<br>V <sub>PX_VBUS</sub> =3.0V,<br>V <sub>PX_GATE_VSYS</sub> =0.1V                                                                                                                       |      |     | 1.5  | МΩ    |

|                               | soft start slew rate for Px_GATE_VSYS, setting 0                                                                                |                                                                                                                                                                                                                   | 0.35 |     | 0.47 |       |

| 00                            | soft start slew rate for Px_GATE_VSYS, setting 1                                                                                | $4 \text{ V} \leq \text{V}_{\text{PX\_VBUS}} \leq 22 \text{ V},$ $500 \text{pF} \leq \text{C}_{\text{PX\_GATE\_VSYS}} \leq 40 \text{ m}$                                                                          | 0.67 |     | 0.91 | Maria |

| SS                            | soft start slew rate for Px_GATE_VSYS, setting 2                                                                                | 16 nF, measure slope from<br>10% to 90% of final<br>Px_GATE_VSYS value,                                                                                                                                           | 1.33 |     | 1.83 | V/ms  |

|                               | soft start slew rate for Px_GATE_VSYS, setting 3                                                                                |                                                                                                                                                                                                                   | 2.88 |     | 3.90 |       |

| t <sub>Px_GATE_VBUS_OFF</sub> | Time allowed to disable the external FET via Px_GATE_VBUS in normal shutdown mode. <sup>(1)</sup>                               | V <sub>Px_VBUS</sub> =20V, Gate is off when V <sub>GS</sub> < 1 V                                                                                                                                                 |      | 260 |      | μs    |

| t <sub>Px_gate_vbus_ovp</sub> | Time allowed to disable the external FET via Px_GATE_VBUS in fast shutdown mode (V <sub>OVP4RCP</sub> exceeded). <sup>(1)</sup> | OVP: V <sub>OVP4RCP</sub> = setting<br>57, V <sub>Px_VBUS</sub> =20V initially,<br>then raised to 23V in 50ns,<br>Gate is off when V <sub>GS</sub> < 1 V                                                          |      | 3   |      | μs    |

# **6.9 PP\_EXT Power Switch Characteristics (continued)**

Operating under these conditions unless otherwise noted: 3.0 V  $\leq$  V<sub>VIN 3V3</sub>  $\leq$  3.6 V

| P                              | ARAMETER                                                                                                                    | TEST CONDITIONS                                                                                                                                    | MIN | TYP  | MAX | UNIT |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|------|

| t <sub>Px_GATE_</sub> vbus_rcp | Time allowed to disable the external FET via Px_GATE_VBUS in fast shutdown mode (V <sub>RCP</sub> exceeded). <sup>(1)</sup> | RCP: $V_{RCP}$ = setting 0,<br>$V_{PX\_VBUS}$ =5V, $V_{VSYS}$ =5V<br>initially, then raised to 5.5V<br>in 50ns, Gate is off when<br>$V_{GS}$ < 1 V |     | 1.2  |     | μs   |

| tpx_gate_vsys_off              | Time allowed to disable the external FET via Px_GATE_VSYS in normal shutdown mode <sup>(1)</sup>                            | V <sub>VSYS</sub> =20V, Gate is off when V <sub>GS</sub> < 1 V                                                                                     |     | 0.25 |     | ms   |

| t <sub>Px_GATE_VSYS_FSD</sub>  | Time allowed to disable the external FET via Px_GATE_VSYS in fast shutdown mode (OVP or FRS) <sup>(1)</sup>                 | V <sub>VSYS</sub> =V <sub>VBUS</sub> =20V initially,<br>then V <sub>VBUS</sub> raised to 23V in<br>50ns, Gate is off when<br>V <sub>GS</sub> < 1 V |     | 0.25 |     | μs   |

| t <sub>Px_GATE_VBUS_ON</sub>   | time to enable Px_GATE_VBUS (1)                                                                                             | measure time from when $V_{GS}$ =0V until $V_{GS}$ >3V                                                                                             |     | 0.25 |     | ms   |

<sup>(1)</sup> These values depend upon the characteristics of the external N-ch MOSFET. The typical values were measured when Px GATE VSYS and Px GATE VBUS were used to drive two CSD17571Q2 in common drain back-to-back configuration.

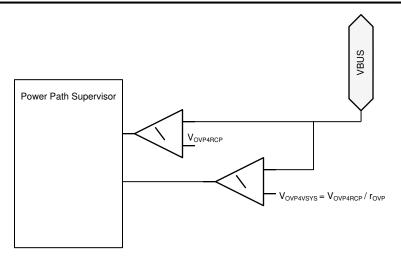

## 6.10 Power Path Supervisory

Operating under these conditions unless otherwise noted: 3.0 V ≤ V<sub>VIN 3V3</sub> ≤ 3.6 V

|                       | PARAMETER                                                                                            | TEST CONDITIONS                                                                 | MIN   | TYP   | MAX   | UNIT |

|-----------------------|------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-------|-------|-------|------|

| V <sub>OVP4RCP</sub>  | VBUS over voltage protection typical threshold for RCP programmable range (setting 0 to setting 63). | OVP detected when V <sub>Px_VBUS</sub> > V <sub>OVP4RCP</sub>                   | 5.25  |       | 22.9  | V    |

|                       | Tolernance of V <sub>OVP4RCP</sub> threshold                                                         |                                                                                 | -5    |       | 5     | %    |

| V <sub>OVPLSB</sub>   | VBUS over voltage protection range for RCP                                                           |                                                                                 |       | 280   |       | mV   |

| V <sub>OVP4RCPH</sub> | hysteresis                                                                                           |                                                                                 | 1.75  | 2     | 2.25  | %    |

|                       |                                                                                                      | setting 0                                                                       | 1     | 1     | 1     | V/V  |

|                       | Configurable ratio of OVP comparator                                                                 | setting 1                                                                       | 0.925 | 0.95  | 0.975 | V/V  |

| r <sub>OVP</sub>      | thresholds. $r_{OVP}^*V_{OVP4VSYS} = V_{OVP4RCP}$                                                    | setting 2                                                                       | 0.875 | 0.90  | 0.925 | V/V  |

|                       | 6414161                                                                                              | setting 3                                                                       | 0.85  | 0.875 | 0.9   | V/V  |

| V <sub>OVP4VSYS</sub> | VBUS over voltage protection range for VSYS protection                                               | OVP detected when r <sub>OVP</sub> *V <sub>PX_VBUS</sub> > V <sub>OVP4RCP</sub> | 5     |       | 27.5  | V    |

| V <sub>OVP4VSYS</sub> | hysteresis                                                                                           | VBUS falling, % of V <sub>OVP4VSYS</sub>                                        |       | 2     |       | %    |

|                       |                                                                                                      | rising                                                                          | 3.9   | 4.1   | 4.3   |      |

| $V_{PP5V\_UVLO}$      | Voltage required on PP5V                                                                             | falling                                                                         | 3.8   | 4.0   | 4.2   | V    |

| _                     |                                                                                                      | hysteresis                                                                      |       | 0.1   |       |      |

| I <sub>DSCH</sub>     | VBUS discharge current (1)                                                                           | V <sub>Px_VBUS</sub> = 22V, measure<br>I <sub>Px_VBUS</sub>                     | 4     |       | 13    | mA   |

<sup>(1)</sup> The discharge is enabled automatically when needed to meet USB specifications. It is not always enabled.

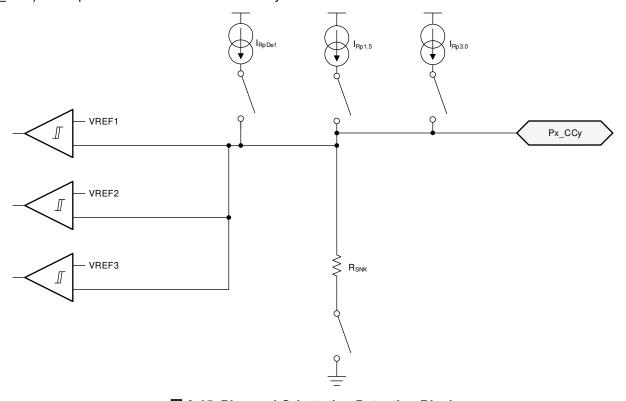

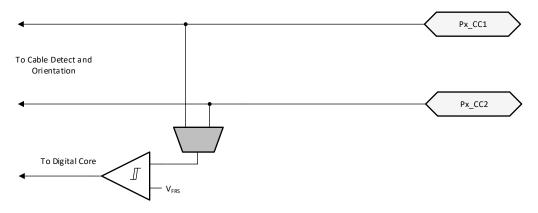

## **6.11 CC Cable Detection Parameters**

Operating under these conditions unless otherwise noted: 3.0 V  $\leq$  V<sub>VIN 3V3</sub>  $\leq$  3.6 V

| P                          | ARAMETER                                                         | TEST CONDITIONS                                                                          | MIN  | TYP | MAX | UNIT |  |

|----------------------------|------------------------------------------------------------------|------------------------------------------------------------------------------------------|------|-----|-----|------|--|

| Type-C Source (Rp pull-up) |                                                                  |                                                                                          |      |     |     |      |  |

| V <sub>OC_3.3</sub>        | Unattached Px_CCy open circuit voltage while Rp enabled, no load | $V_{LDO_{3V3}_{UVLO}} < V_{LDO_{3V3}} < 3.6 \text{ V},$<br>$R_{CC} = 47 \text{ k}\Omega$ | 1.85 |     |     | V    |  |

| V <sub>OC_5</sub>          | Attached Px_CCy open circuit voltage while Rp enabled, no load   | $V_{PP5V\_UVLO} < V_{PP5V} < 5.5 \text{ V}, R_{CC} = 47 \text{ k}\Omega$                 | 2.95 |     |     | V    |  |

Submit Document Feedback

## **6.11 CC Cable Detection Parameters (continued)**

Operating under these conditions unless otherwise noted: 3.0 V  $\leq$  V<sub>VIN 3V3</sub>  $\leq$  3.6 V

|                    | PARAMETER                                                              | TEST CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | MIN  | TYP  | MAX  | UNIT |

|--------------------|------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| L                  | Unattached reverse current on                                          | $\begin{split} &V_{Px\_CCy} = 5.5 \text{V},  V_{Px\_CCx} = 0 \text{V}, \\ &V_{LDO\_3V3\_UVLO} < V_{LDO\_3V3} < 3.6 \text{ V}, \\ &V_{PP5V} = 3.8 \text{ V},  \text{measure current} \\ &\text{into } Px\_CCy \end{split}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |      | 10   | ι.Λ  |

| Rev                | Px_CCy                                                                 | $\begin{array}{c} V_{Px\_CCy} = 5.5 \text{V, } V_{Px\_CCx} = 0 \text{V,} \\ V_{LDO\_3V3\_UVLO} < V_{LDO\_3V3} < 3.6 \text{ V,} \\ V_{PP5V} = 0, -10^{\circ}\text{C} \leq \text{T}_{J} \leq 85^{\circ}\text{C,} \\ \text{measure current into } Px\_CCy \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |      | 10   | μА   |

| I <sub>RpDef</sub> | current source - USB Default                                           | $0 < V_{Px\_CCy} < 1.0 \text{ V}$ , measure $I_{Px\_CCy}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 64   | 80   | 96   | μΑ   |

| Rp1.5              | current source - 1.5A                                                  | 4.75 V < V <sub>PP5V</sub> < 5.5 V, 0 < V <sub>PX_CCy</sub> < 1.5 V, measure I <sub>PX_CCy</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 166  | 180  | 194  | μA   |

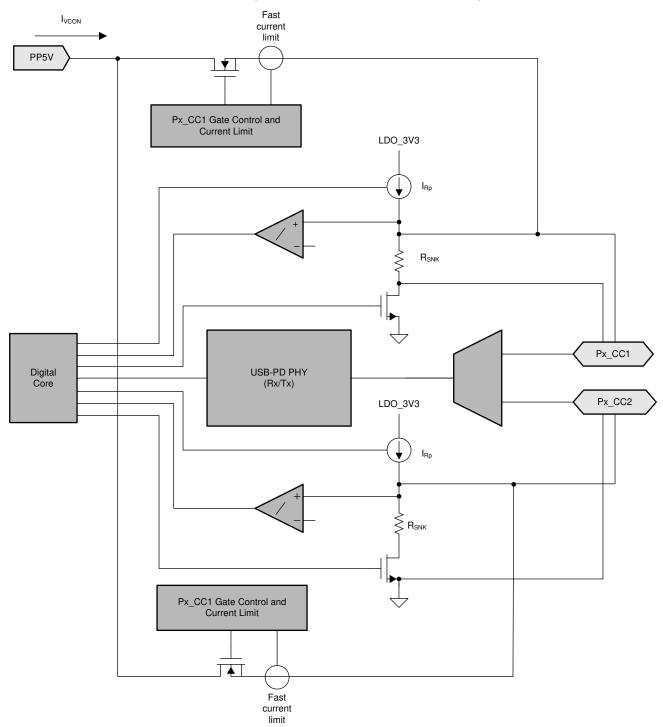

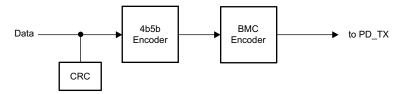

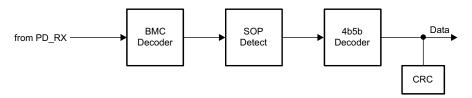

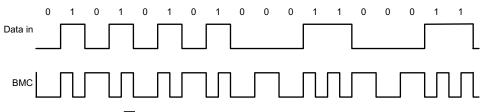

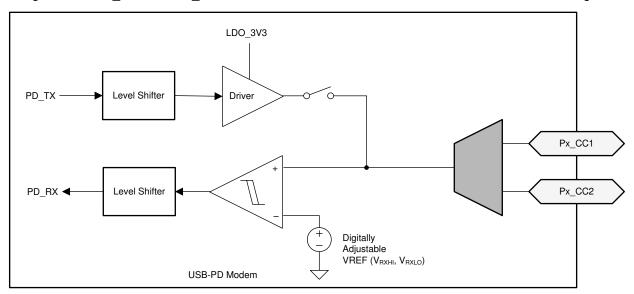

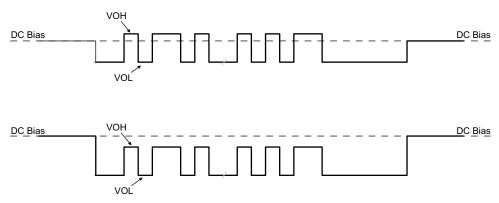

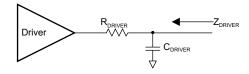

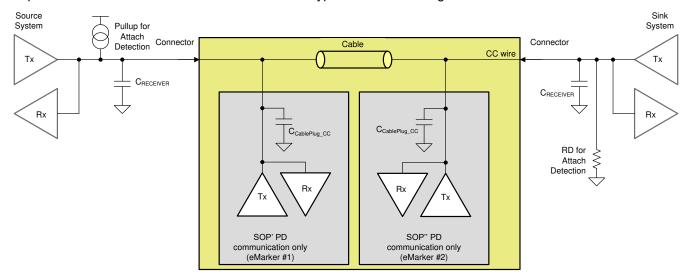

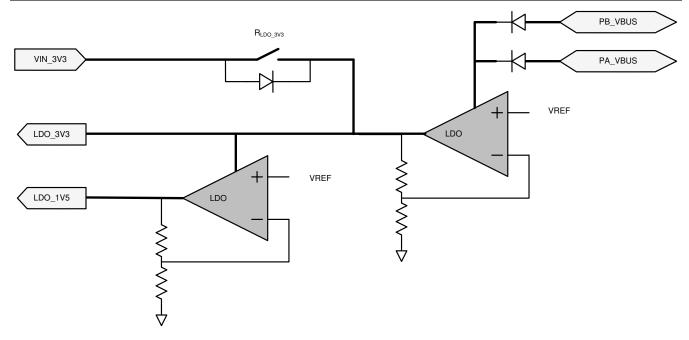

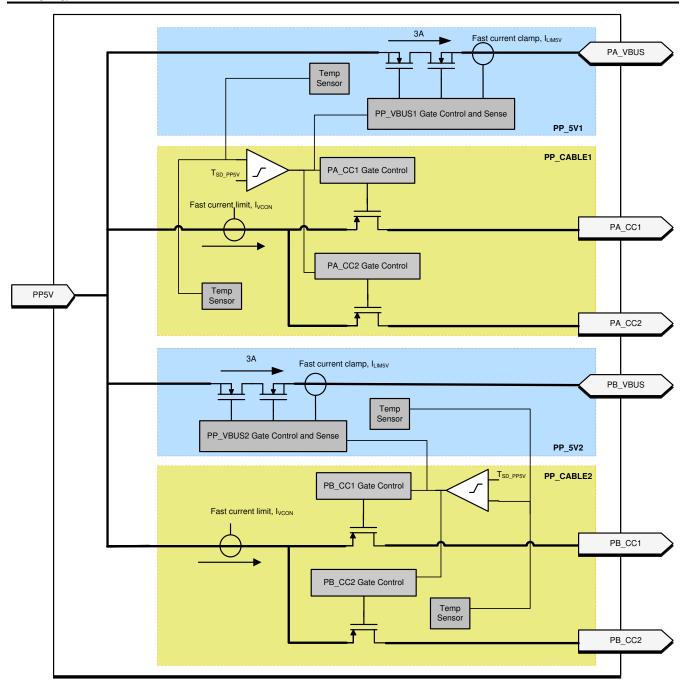

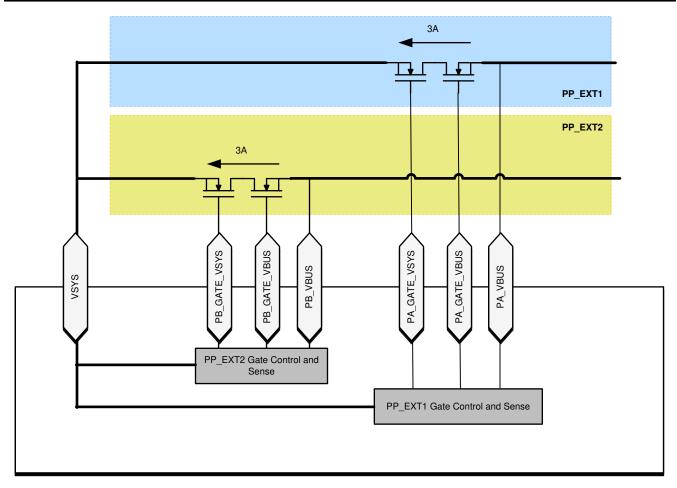

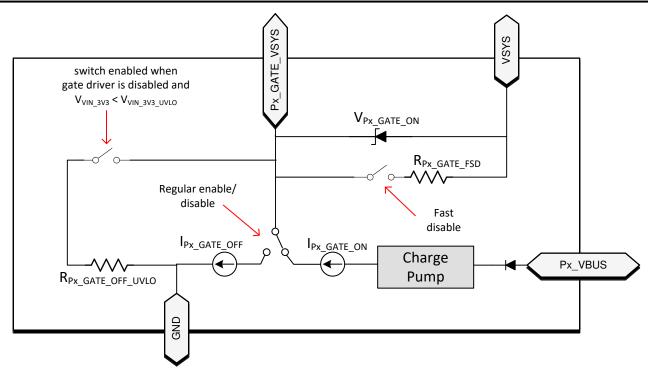

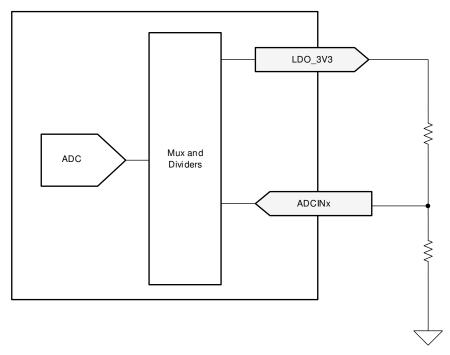

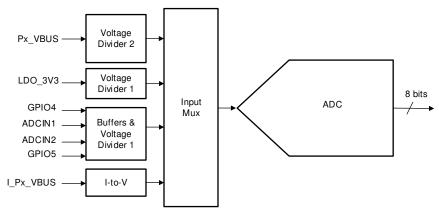

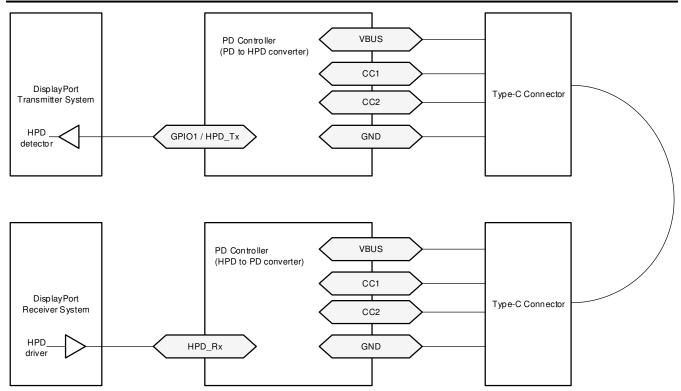

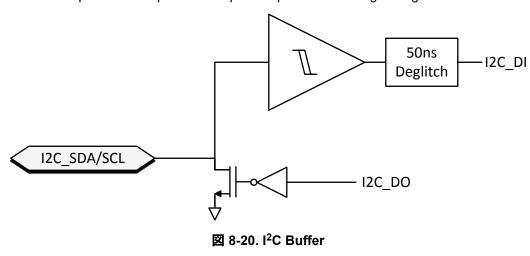

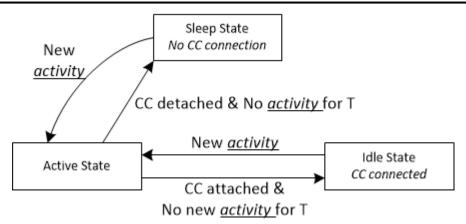

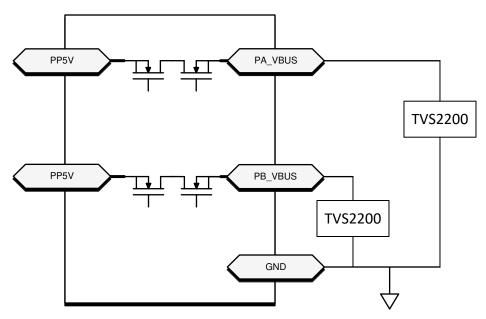

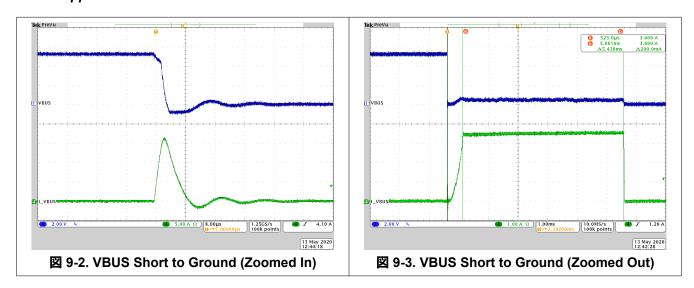

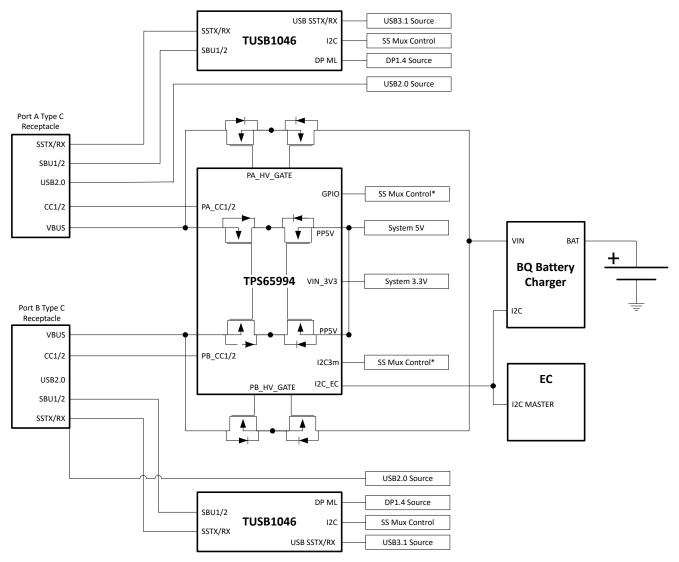

| Rp3.0              | current source - 3.0A                                                  | 4.75 V < V <sub>PP5V</sub> < 5.5 V, 0 < V <sub>Px_CCy</sub> < 2.45 V, measure I <sub>Px_CCy</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 304  | 330  | 356  | μΑ   |