Design Guide: TIDA-010945

# デジタル マルチメータ用の高精度シグナル チェーンのリファレンス デザイン

# TEXAS INSTRUMENTS

## 概要

このリファレンス デザインでは、DC 測定用の高性能シグナル チェーンの理論、設計、テストについて説明します。主なターゲット アプリケーションはデジタル マルチメータ (DMM) ですが、この設計はデータ アクイジション (DAQ) や状態監視など、他のアプリケーションにも適用できます。この設計は、高性能 24 ビット A/D コンバータ

ADS127L21 と、低ノイズのプログラマブル ゲイン アンプ PGA855 を使用して高い DC 精度を達成しており、標準 値

**±2.4ppm** の非直線性と、温度範囲全体での低ドリフトを実現しています。これらのデバイスは高度に統合されており、シグナル チェーンの設計全体を簡素化できます。

# 参照情報

TIDA-010945

デザイン フォルダ

ADS127L11

プロダクト フォルダ

ADS127L21

プロダクト フォルダ

PGA855

プロダクト フォルダ

REF7040

プロダクト フォルダ

テキサス・インスツルメンツの™ E2E サポート エキスパートにお問い合わせください。

# 特長

- ゲインを 0.125V/V~16V/V の範囲でプログラム可能

- 広い帯域幅:357kHz (Sinc3 フィルタ、最大速度)

- ADC 用の構成可能なデジタル フィルタ設定

- SNR 110dB (Sinc4 フィルタ) で、高速 ADC 入力ドライバやリファレンス バッファが不要

- 低いゲインドリフトと非線形性により、キャリブレーション後に高い DC 精度を実現

- フルスケール入力時:25℃ ±5℃ (キャリブレーション後)

- 推定標準値:TUE = ±6ppm、INL ±2.4ppm

- 推定最大値:TUE = ±32ppm、 INL ±12.2ppm

- 推定温度ドリフト(標準値)

- オフセットドリフト:350nV/°C

- ゲインドリフト: 1.5ppm/°C

- 1 ユニットで測定 (キャリブレーション後)

- TUE (総合未調整誤差):±9ppm

# アプリケーション

- デジタル マルチメータ (DMM)

- データ アクイジション (DAQ)

- コンディション監視

# 1システムの説明

この設計は入力ゲイン段を簡単に選択できるため、幅広い入力信号に対応できます。これは、複数の入力範囲を持つ DMM などのアプリケーションに便利有益です。ゲインの切り替えは比較的簡単なためです。

PGA855 は追加の ADC ドライバなしで ADS127L21 の入力を駆動でき、ADS127L21 は入力バッファとリファレンス バッファを内蔵しているため、外部アンプは不要です。高集積により、設計が大幅に簡略化され、スペースが節約されます。このシステムは、帯域幅とダイナミック レンジが広く、非線形性が小さいため、AC 精度と DC 精度が非常に優れています。

# 1.1 主なシステム仕様

# 主なシステム仕様

このリファレンス デザインの主なシステム仕様を、表 1-1 に示します。

## 表 1-1. 仕様

| パラメータ                 | 仕様                                                 |  |  |

|-----------------------|----------------------------------------------------|--|--|

| 入力信号範囲                | 0V~32.768V (0.125V/V ゲイン)                          |  |  |

| ゲイン オプション             | 0.125、0.25、0.5、1、2、4、8、16V/V                       |  |  |

| デジタル フィルタ オプション       | 広帯域、低レイテンシ、プログラマブルの IIR および FIR                    |  |  |

| 分解能                   | 24 ビット                                             |  |  |

| データレート                | 最大 512kSPS (広帯域フィルタ)<br>最大 1.365MSPS (低レイテンシ フィルタ) |  |  |

| SNR (1kHz、ゲイン = 1V/V) | 108dB (広帯域フィルタ)<br>110dB (低レイテンシ フィルタ)             |  |  |

| THD (1kHz、ゲイン = 1V/V) | -121.4dB (広帯域フィルタ)<br>-121.4 dB (低レイテンシ フィルタ)      |  |  |

| 帯域幅                   | 224kHz (広帯域フィルタ)<br>357kHz (低レイテンシ フィルタ)           |  |  |

| DC 精度の計算値             | オフセット誤差:±76μV<br>ゲイン誤差:±360ppm                     |  |  |

| 温度ドリフトの標準精度の計算値       | オフセットドリフト:350nV/℃<br>ゲインドリフト:1.1ppm/℃              |  |  |

www.ti.com/ja-jp システム概要

# 2 システム概要

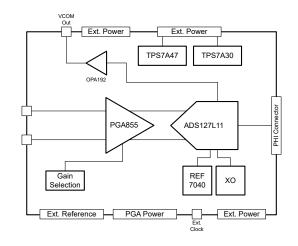

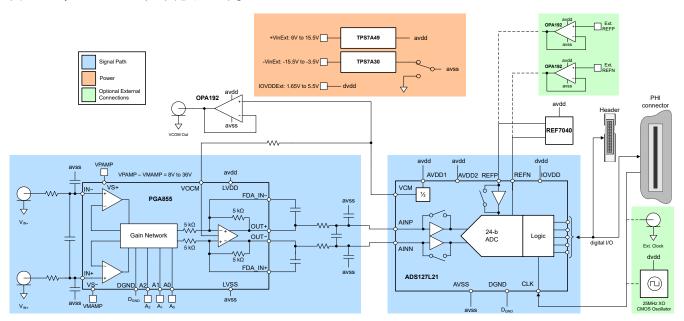

#### 2.1 ブロック図

図 2-1 に、システム ブロック図を示します。

図 2-1. システム ブロック図

# 2.2 設計の考慮事項

この設計は、高精度のホストインターフェイス (PHI) 基板と組み合わせて使用することを想定しており、ADS127L21 GUI と簡単に接続できます。PHI 基板は、テキサス・インスツルメンツのデルタ-シグマ ADC のいくつかについて、GUI とのインターフェイスに使用されるペリフェラルです。この基板は単独で注文できませんが、ADS127L11EVM-PDK または ADS127L21EVM-PDK を購入すると付属します。デフォルトでは、ADC の電源とクロックは PHI コントローラから供給されます。さらに、このリファレンス デザインにはオンボードの高精度 4.096V シリーズのリファレンスが含まれており、ADC のダイナミック レンジを最大化できます。ただし、システムの仕様に応じて、外部リファレンス、クロック、電源を選択することもできます。ADC への電力供給方法にかかわらず、PGA855 には外部から電力を供給する必要があります。さらに、PHI コントローラ基板を使用しない場合、基板のヘッダを使用して ADC からデジタル ラインにアクセスできます。

ADC には  $1x \ge 2x$  の 2 つの入力範囲があり、1x の範囲は  $VIN = \pm VREF$ 、2x の範囲は  $VIN = \pm 2 \times VREF$  で定義されます。1ファレンス電圧が 2.5V 以下の場合、2x の入力範囲では可能な範囲が 2 倍になります。2x の入力範囲を使用すると、2.5V のリファレンス電圧を使用しているとき一般に 5NR が 1dB 改善しますが、完全なダイナミック レンジを得るには、入力を 5V 電源レールに駆動する必要があります。可能な最高のダイナミック レンジを得る (標準で 50 のリファレンス電圧を使用します (ADC を高リファレンス電圧範囲モードにプログラムします)。

この設計は、PGA855 のゲイン設定のために、広い入力範囲に対応できます。基板への最大入力信号は、PGA855 の電源、PGA のゲイン設定、ADC での入力範囲の選択に依存します。PGA855 の推奨最大電源電圧は、36V ユニポーラまたは ±18V バイポーラです。たとえば、4.096V のリファレンス電圧を使用するなら合、PGA855 が ±18V 電源から電力を供給されるとき、システムのフルスケール範囲は ±0.256V (16V/V ゲイン) から ±32.768V (1/8V/V ゲイン) まで変化します。

# 2.3 主な使用製品

#### 2.3.1 ADS127L21

ADS127L21 は 24 ビットのデルタ-シグマ ( $\Delta\Sigma$ ) A/D コンバータ (ADC) で、プログラム可能なデジタル フィルタを備えており、データ レートは広帯域フィルタ使用時に最大 512kSPS、低レイテンシ フィルタ使用時に最大 1365kSPS です。本 デバイスは、低消費電力で優れた AC 性能と DC 精度を備えています。

プログラム可能な無限および有限インパルス応答 (IIR および FIR) デジタル フィルタにより、A 重み付け補償や周波数ノッチ フィルタなどのカスタムのフィルタ プロファイルを使用できます。 広帯域または低レイテンシのフィルタ オプションにより、AC 信号の性能または DC 信号のデータ スループットをすべて 1 つのデバイスで最適化します。

低ドリフトの変調器は、優れた DC 精度を備えており、小さい帯域内ノイズで AC 性能を向上しています。アーキテクチャは、消費電力に関する拡張性が高く、データレート、分解能、消費電力を最適化するために、4 つの速度モードがあります。信号およびリファレンス入力バッファは、ドライバの負荷を低減して精度を向上させます。

#### 2.3.2 PGA855

PGA855 は、完全差動出力を備えた高帯域幅のプログラマブル ゲイン計測アンプです。PGA855 は、3 本のデジタル ゲイン選択ピンを使用して、減衰ゲインが 0.125V/V から最大 16V/V までの、8 つのバイナリ ゲインを設定できます。出 力同相電圧は、VOCM ピンを使用して個別に設定できます。

PGA855 アーキテクチャは、高分解能、高精度の A/D コンバータ (ADC) の入力駆動用に最適化されています。出力段の電源は入力段から分離され、ADC またはダウンストリーム デバイスをオーバードライブの損傷から保護します。

スーパーベータ入力トランジスタを使用しているため、入力バイアス電流が非常に小さく、その結果として入力電流ノイズ密度が 0.3pA/√Hz と非常に小さいので、PGA855 は汎用性が高い選択肢として、事実上あらゆる種類のセンサに使用できます。PGA855 は、低ノイズの電流フィードバック フロントエンド アーキテクチャにより、高周波数でもゲイン平坦性が優れているので、高インピーダンスのセンサ読み出しデバイスとして優れています。入力ピンに保護回路が内蔵されており、電源電圧を最大±40V 上回る過電圧に対処できます。

#### 2.3.3 REF70

REF70 は、業界最小のノイズ (0.23ppm<sub>p-p</sub>)、非常に小さい温度ドリフト係数 (2ppm/°C)、高い精度 (±0.025%) を特長とする高精度シリーズ電圧リファレンスのファミリです。厳しい過渡要件を満たせるように、REF70 は高 PSRR、低ドロップアウト電圧、優れた負荷 / ライン レギュレーションを実現しています。この精度と機能の組み合わせは、高精度のリファレンスと、ADS8900B、ADS127Lx1、DAC11001A などの高精度、高分解能のデータ コンバータとを組み合わせて優れた信号チェーン性能を達成することが求められる、テストや測定などのアプリケーション向けに設計されています。

システム設計理論

# 3システム設計理論

フロント エンドは、デジタル マルチメータや多くのデータ アクイジション システムの重要なビルディング ブロックです。 デ ジタル マルチメータは、幅広い範囲の測定を行います。範囲ごとに個別のゲイン抵抗を持つスイッチング マトリクスは、特 にマルチチャネルデータアクイジションシステムの場合、多くのスペースを占有する可能性があります。

PGA855 のゲイン設定では広い入力範囲が可能で、3 つのデジタル信号で制御されるため、ゲインを簡単に切り替える ことができます。 DMM には 100mV、1V、10V、100V など複数の異なる入力範囲があり、1 つの入力段で複数の入力範 囲に対応できるので、設計を簡素化できます。 PGA855 のゲインは 3 本のデジタル ラインで制御されるため、マイコンや またはプロセッサを使用するとき、ゲイン段の切り替えが比較的簡単です。

アンプは、データコンバータの分解能を犠牲にせず、データコンバータのフルスケール範囲まで信号を正確にスケーリ ングできる必要があります。精度と正確さは、あらゆる DMM 設計に重要です。メーターの読み取り値は、実際の値に近 く、再現可能な必要があります。ほとんどの初期 DC 誤差は比較的簡単にキャリブレーションできますが、精度と正確性を 高めるには、非線形性、ドリフト、ノイズが低いことが必要です。

この設計に、高電圧入力用の追加の入力スケーリングを追加し、さらに入力保護を追加すると、アナログ フロントエンド シ グナルチェーンが完成します。

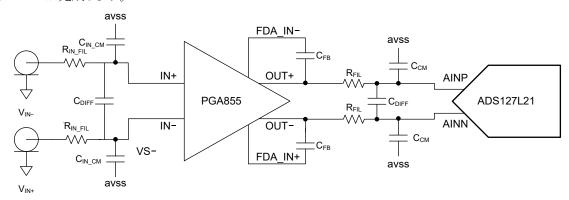

図 3-1, PGA および ADC 入力フィルタ

図 3-1 に示すように、PGA の入力に R-C-R 差動ローパス フィルタを配置するは、EMI/RFI 高周波数の固有ノイズを低 減できます。このフィルタは、帯域幅とアプリケーションの要件に応じてカスタマイズできます。同相コンデンサ C<sub>IN CM</sub> に 対して、差動コンデンサ C<sub>IN DIFF</sub> を 10:1 の比率で使用すると、優れた差動および同相ノイズ除去が得られます。また、 この比率は、フィルタコンデンサの許容誤差の変動や不一致の影響を受けにくくなる傾向があります。

帰還コンデンサ  $C_{FB}$  は、PGA855 出力段の内部  $5k\Omega$  帰還抵抗と並列に接続され (図 2-1 を参照)、追加のノイズ フィル タリングを実装しています。内部抵抗の絶対抵抗の変動は ±15% なので、ノイズ フィルタリングを実装するときはこの変動 を考慮する必要があります。この基板では、CFBが 25pFに設定され、標準的なf-3dBコーナー周波数である1MHzを 実現しています。この回路の推定最小 f-3dB コーナー周波数は、帰環抵抗の変動を考慮して、約 904kHz~1.119MHz の範囲です。ADS127Lx1の入力にあるフィルタは、ADCのサンプリングされた入力をフィルタ処理するため電荷を蓄積 します。電荷を蓄積することで、アンプの瞬間的な電荷要求が低減され、低い歪みとゲイン誤差が維持されます。電荷の 蓄積がないと、アンプのセトリングが不十分なために歪みやゲイン誤差が劣化することがあります。 ADC 入力のプリチャー ジ バッファは、入力電荷を大幅に低減し、ADC の入力インピーダンスを上昇させて、ゲイン誤差を低減します。

# 4 ハードウェア、ソフトウェア、テスト要件、テスト結果

# 4.1 ハードウェアの説明

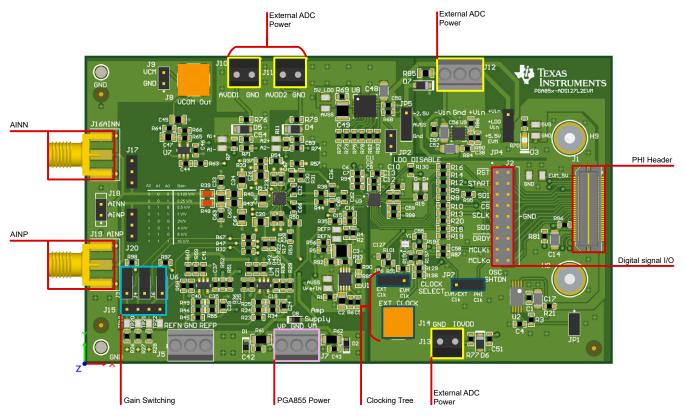

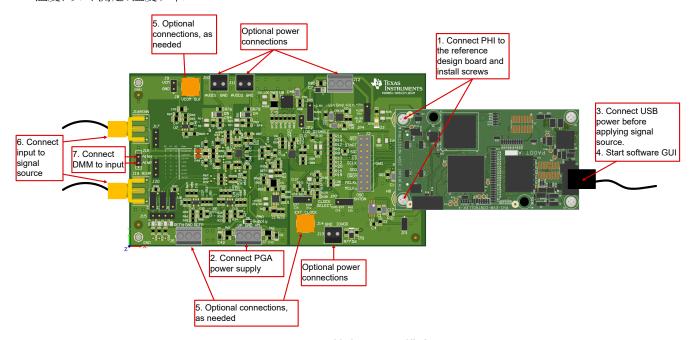

TIDA-010945 のハードウェアを、図 4-1 に示します。これは、さまざまな回路ブロック、コネクタ、インターフェイスを、システム ブロック図から示したものです。

図 4-1. 基板レイアウトとインターフェイス

## 4.1.1 基板インターフェイス

表 4-1. 基板のコネクタおよびヘッダ

| コネクタ            | 説明                                                   |  |  |

|-----------------|------------------------------------------------------|--|--|

| J1              | PHI に接続するための QSH コネクタ。接続前に基板に電力を供給するのがベスト プラクティスです   |  |  |

| J2              | SPI 信号ヘッダで、デバッグやプローブ、または別の基板への接続 (QSIがない場合) に使用されます  |  |  |

| J3、J4、J6        | PGA ゲイン制御に使用されます。表 4-2 を参照                           |  |  |

| J15             | ゲイン制御ピンのプローブに使用されます                                  |  |  |

| J16             | 負入力                                                  |  |  |

| J19             | 正入力                                                  |  |  |

| J18             | 複数の入力を互いに短絡する目的で使用されます                               |  |  |

| J17、J20         | 入力をグランドに短絡するために使用されます                                |  |  |

| J7              | PGA855 用の正および負の電源レール入力                               |  |  |

| J10、J11、J12、J13 | 外部から基板への電力供給に使用されます。詳細については、セクショ、<br>4.1.2 を参照してください |  |  |

| JP4、JP5         | オンボード LDO または外部電源の選択に使用されます                          |  |  |

| J5              | 外部リファレンスの接続に使用されます                                   |  |  |

| J9              | Vcm 信号用のテスト ポイント                                     |  |  |

## 表 4-1. 基板のコネクタおよびヘッダ (続き)

| コネクタ    | 説明                                |

|---------|-----------------------------------|

| J8      | ADC からの Vcm 信号を外部機器に接続するために使用されます |

| J14     | 外部クロック入力                          |

| JP6、JP7 | 基板クロックまたは外部クロックの選択に使用されます         |

| JP1     | EEPROM イネーブル                      |

| JP2     | LDO イネーブル                         |

PGA ゲインは、ゲイン制御ピンのジャンパを追加および削除して調整できます。

ゲイン (V/V) A0 (J3) A1 (J4) A2 (J9) 0.125 0 0 0 0.25 1 0 0 0.5 0 1 0 0 1 1 1 2 0 0 1 0 4 1 1 8 0 1 1 1 1 16 1

表 4-2. ゲイン設定

#### 4.1.2 電源

TIDA-010945 ハードウェアのデフォルト状態では、供給されるすべての ADC 電力は PHI コントローラからの USB 電力を使用して生成されます。 PGA のコネクタ J7 に、外部電源を接続する必要があります。 PGA855 には、単一電源 (8V~36V) またはデュアル電源 (±4V~±18V) を使用できます。電源の推奨事項と仕様の詳細については、『PGA855 低ノイズ、広帯域幅、完全差動出力、プログラマブル ゲインの計測アンプ』データシートを参照してください。この設計ボードには、36V のダイオード D1、D2、D3 が搭載されています。これにより、±18V のバイポーラ電源に加えて、非対称バイポーラ電源も、推奨動作条件内であるなら使用できます。

PHI が必要な電圧を供給しない場合は、外部電源接続を使用できます。たとえば、PHI はバイポーラ電圧を供給しないため、バイポーラ電源が必要な場合は、外部電源が不可欠必要です。AVDD と IOVDD に外部電源接続を使用するように、0Ω の抵抗接続 (R71、R74、R81) を変更します。J10 は AVDD1 への電力供給、J11 は AVDD2 への電力供給、J13 は IOVDD への電力供給に使用されます。詳細な仕様については、ADS127L21 データシートの推奨動作条件を参照してください。オプションとして、コネクタ J12 でオンボードの 5V および -2.5V レギュレータに電力を供給することもできます。この場合、-VinExt の許容電圧範囲は -15.5V < -VinExt < -3.5V で、+VinExt は 6V< +VinExt < 15.5V です。

PHI からの 5.5V 電圧は、低ノイズの TPS7A4700 LDO を使用して 5V に安定化されます。デフォルトでは、ジャンパ JP4 の位置 1-2 にシャントを配置すると、PHI から LDO  $\sim 5.5$ V の配線が行われます。(JP4) のシャントを 2-3 の位置 に移動して、J12 の外部電源から 5V LDO に電力を供給することもできます。5V LDO 出力は AVDD 接続に使用され、R72、R73、R75、R78、R82、R83 を使用して、さまざまな出力電圧に再プログラム可能です。追加の LDO があり、低ノイズの TPS7A3001 LDO を使用して、AVSS 用に -2.5V を生成します。この LDO は、J12 の外部電源からのみ電力を供給されます。デフォルトでは、AVSS は (JP5) 1-2 のシャントにより GND に接続されます。AVSS を -2.5V に設定する必要がある場合は、外部の負電源を J12 に接続し、(JP5) のシャントを位置 2-3 に移動します。

外部リファレンスは、コネクタ J5 を経由して基板に接続できます。基板上には、外部リファレンス用の適切なバッファと接続が存在しています。オンボードの電圧リファレンス (REF7040) を使用する場合、この機能は必要ありません。REF7040 は、『ADS127L21 512kSPS、プログラマブル フィルタ、24 ビット、広帯域デルタ-シグマ ADC』データシートの仕様を満たすのに十分です

この基板は REF7040 を使用して構成されしていますが、REF6241 など、テキサス・インスツルメンツの高精度シリーズ電 圧リファレンス カタログに掲載されている他の高精度リファレンスと簡単に交換できます。リファレンス電圧を交換するには、R89 と R93 ではなく R90 と R92 を実装する必要があります。これは、一部のリファレンスが完全にピン互換ではないためです。

#### 4.1.3 クロック ツリー

この基板は、3種類のクロック・オプションをサポートしています。

- PHI クロック (外部接続なし)

- ローカル クロック (外部接続なし)

- ユーザーから供給される外部クロック

ジャンパ (JP7) のデフォルト位置は 2-3 で、PHI デジタル コントローラ基板のクロックを ADS127L21 (U3) の CLK ピン に配線します。 PHI コントローラなしで基板を使用する場合は、ジャンパを 1-2 に移動して、ローカル クロックを ADS127L21 に直接配線できます。

ジャンパ (JP6) 2-3 は、基板ボード上でローカルの 32.768MHz 発振器 (Y1) を有効にします。これは、ADS127L21EVM-PDK-GUI ソフトウェアを使用するために必要なデフォルトの位置です。非アクティブな (JP6) 1-2 の場合、SMA コネクタ (J14) に外部クロックを供給できます。

ADS127L21EVMPDK-GUI ソフトウェアはデフォルトで 32.768MHz (Y1) 発振器を使用しますが、24MHz PHI クロック ソースを選択することもできます。ジャンパ JP6 を 1-2 の位置に配置すると、外部クロック ソースを使用できます。振幅が IOVDD (PHI 基板使用時に 2.5V) の CMOS 方形波信号を、ADS127L21 の規定範囲内の周波数で使用する必要があります。

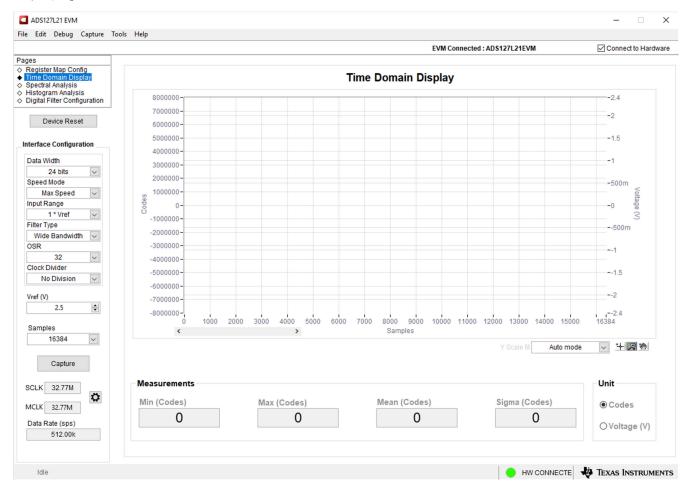

## 4.2 ソフトウェア要件

このリファレンス デザインは、専用のソフトウェアと組み合わせて使用することを意図しています。 図 **4-2** に示す ADS127L21 EVM-PDK-GUI。ソフトウェアの使用方法については、『ADS127L21EVM-PDK ユーザー ガイド』を参照してください。

図 4-2. ADS127L21 GUI

## 4.3 テスト構成

図 4-3 の基本的な設定を使用して、PCB を評価します。この基板は、PHI 基板を経由し、ADS127L21EVM-PDK-GUI ソフトウェアを実行する PCB に対して評価されます。GUI のデフォルトのリファレンス値は 2.5V で、これを 4.096V に更新する必要があります。

すべてのテストを実行するには、次のコンポーネントが必要です。

- リファレンス デザイン PCB

- PHI ボード

- ADS127L21 ソフトウェアを実行している PC

- ±15V 電源

- 低ノイズ DC 電源

- 6.5 桁デジタル マルチメータ

- 温度ドリフト測定:温度チャンバー

図 4-3. DC 精度テストの構成

図 4-3 に示すように、ハードウェアと電源を接続します。

ツイストペアまたは SMA コネクタを使用して、できるだけ短い接続で、高精度 DC ソースをシグナル チェーンの入力に接続します。これにより、シグナル チェーンに結合されるノイズの量が減少し、高精度の測定が可能になります。

シングルエンド信号をテストするには、ジャンパ J17 を使用して負入力 (AINN) を直接グランドに接続し、SMA コネクタ (J19) またはいずれかのピン コネクタ (J18 ピン 2 または J20 ピン 1) を使用して目的の信号を正入力 (AINP) に接続します。

## 4.4 テスト結果

ここでは、テスト結果の例を示します。 すべてのテスト結果は、以下の ADC 条件で測定されたものです。

| 設定     | 構成                 |  |  |

|--------|--------------------|--|--|

| 速度モード  | 高速                 |  |  |

| データレート | 11.72kSPS<br>Sinc4 |  |  |

| フィルタ   |                    |  |  |

| OSR    | 1024               |  |  |

| クロック構成 | PHI クロック (24MHz)   |  |  |

| 設定          | 構成             |  |  |

|-------------|----------------|--|--|

| 電圧リファレンスの範囲 | High リファレンスの範囲 |  |  |

| VCM 出力      | イネーブル          |  |  |

| リファレンス バッファ | イネーブル          |  |  |

| アナログ正入力バッファ | イネーブル          |  |  |

| アナログ負入力バッファ | イネーブル          |  |  |

| PGA 電源      | ± 15V          |  |  |

テストは ADS127L11 で、関連する GUI を使用して行われましたが、ADS127L11 の性能は ADS127L21 の性能とほぼ 同じです。すべてのテストはシングルエンド入力信号を使用します。

## 4.4.1 DC 精度テスト

ドリフトと非直線性は、DC 精度にとって重要な仕様です。ゲイン誤差やオフセット誤差のような初期誤差とは異なり、2点 または3点のキャリブレーションを使用して簡単に較正できないためです。このセクションでは、シグナル チェーンのゲイ ンとオフセットのドリフトと非直線性を測定して、シグナル チェーンのキャリブレーション後に達成される DC 精度を計算し ます。

ジャンパ J18 を使用して入力を互いに短絡し、オフセット誤差を測定します。 GUI を使用してデータをキャプチャし、図 4-4 と同様のグラフを生成します。入力が互いに短絡しているとき、出力はゼロなので、ゼロでないすべての出力がオフセ ット誤差です。 図 4-4 のヒストグラムを読み取ると、オフセット誤差は 27.7µV です。

図 4-4. オフセット測定 (G = 1、T<sub>A</sub> = 25℃)

J18 から短絡を取り除き、OV から ± フルスケールまでのデータを収集します。フルスケール範囲 (FSR) はリファレンスと ゲイン設定に依存し、次の式で計算できます。

資料に関するフィードバック(ご意見やお問い合わせ) を送信

$$FSR = \frac{2V_{ref}}{Gain} \tag{1}$$

PGA の入力範囲を逸脱しないよう注意してください。さまざまなゲイン設定に対してデータ収集を繰り返し、データを収集する前に温度チャンバーが正しい温度に安定することを確認します。フルスケール範囲の ±95% でデータを収集し、ゲイン誤差の計算を実行します。

温度ドリフトのデータを収集するには、複数の温度にわたって同じ試行を繰り返します。リファレンスの精度誤差を考慮するには、リファレンスの値を測定し、その結果を GUI の左側、「インターフェイス構成」の下に入力します。

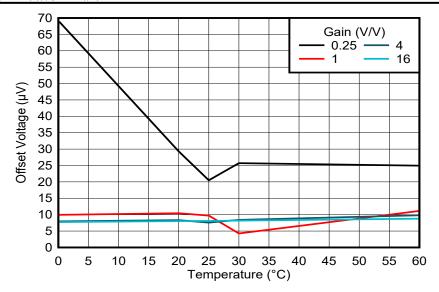

#### 4.4.2 ゲインおよびオフセット温度ドリフト

オフセットドリフトは、温度範囲全体にわたるオフセット電圧の変化です。シグナル チェーンのオフセットドリフトは、ボックス法を使用して収集されたオフセット データから計算できます。ボックス法は、式 2 に示すように、範囲全体にわたる最大オフセットと最小オフセットを取得し、オフセットを温度範囲で除算します。

Offset Drift

$$\left(\frac{\mu V}{^{\circ}C}\right) = 10^6 \times \frac{V_{OFSMAX} - V_{OFSMIN}}{T_{MAX} - T_{MIN}}$$

(2)

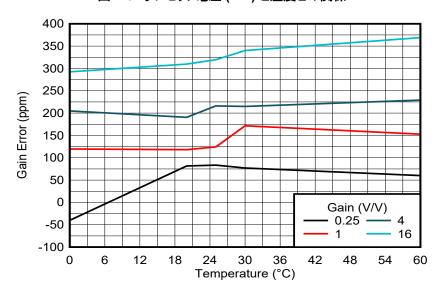

ゲイン誤差は、シグナル チェーンの実際のスロープと理想的なスロープとの差です。ゲイン誤差は、DC テスト電圧をフルスケール範囲の -95% と 95% で印加して測定します。誤差は、式 3 に示すように、DC テスト電圧 (理想的なスロープ) の変化を、ゲイン(G) でスケーリングし、ADC 出力電圧 (実際のスロープ) の変化から減算して計算されます。

Gain Error (ppm of FSR) =

$$10^6 \times \frac{\Delta V_{OUT} - G \Delta V_{IN}}{G \Delta V_{IN}}$$

(3)

ゲインドリフトは、ゲイン段全体にわたる最小および最大ゲイン誤差を使用して、再度ボックス方式を使用して求めることができます。

Gain Drift

$$\left(\frac{\text{ppm}}{^{\circ}\text{C}}\right) = 10^6 \times \frac{GE_{MAX} - GE_{MIN}}{T_{MAX} - T_{MIN}}$$

(4)

標準のゲインおよびオフセットドリフト誤差は、PGA855 および ADS127L21 データシートに記載されている標準値を加算して推定されます。最大誤差についても同様です。

ADS127L21 PGA855 + ADS127L21 **PGA855** PGA855 (MAX) PGA855 + (MAX) ADS127L21 の推 (TYP) ADS127L21 の推 (標準値) 定値 (標準値) 定值 (最大值) オフセットドリフト 0.3 0.05 0.35 1 0.2 1.2 (µV/°C) ゲイン ドリフト 1 0.5 1.5 2 1 3 (ppm/°C)

表 4-3. オフセットとゲイン ドリフトの推定値

20℃~30℃の範囲について、ドリフトから予測される誤差は約 ±3.5µV のオフセットと、±15ppm のゲイン誤差です。以下に示すのは、1 つのユニットから測定された温度範囲全体にわたるオフセットおよびゲイン誤差です。

図 4-5. オフセット電圧 (RTI) と温度との関係

図 4-6. ゲイン誤差と温度との関係

図 4-5 と図 4-6 から、式 2 と式 4 を使用して、ユニットの温度ドリフトを計算できます。

| ゲイン (V/V)         | 0.25 | 1    | 4    | 16   |

|-------------------|------|------|------|------|

| オフセットドリフト (μV/°C) | 0.81 | 0.11 | 0.04 | 0.02 |

| ゲイン ドリフト (ppm/℃)  | 2.06 | 0.89 | 0.64 | 1.28 |

#### 4.4.3 非線形性

オフセット誤差やゲイン誤差などの初期誤差は、2 点または 3 点のキャリブレーションで大幅に低減するか、完全に除去できます。ただし、非直線性は簡単にキャリブレーションできません。積分非直線性 (INL) は、特定の入力が与えられたとき、システムの実際の出力が最良の出力からどれだけ離れているかの測定値です。 INL は、システム のスロープとオフセット伝達関数から計算される直線に沿って、一連の DC テスト電圧を印加することで測定されます。 INL は、フルスケール入力範囲について、最良の出力と実際の出力との差の最大値です。 INL の計算では、最小 2 乗誤差の最適化法を使用して新しい直線を決定し、元のエンドポイント線の上下にある INL 誤差の 2 乗和平方根を最小化します。

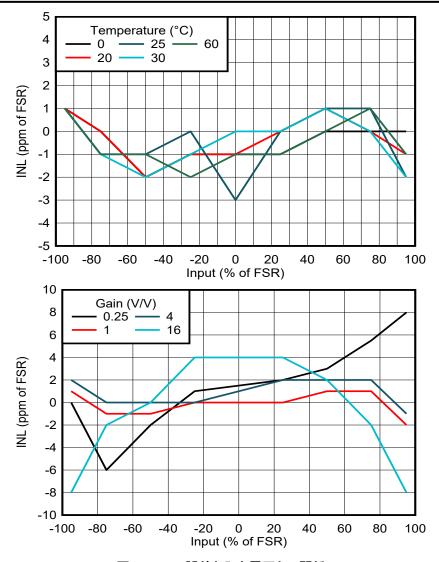

1 つのユニットについて、温度範囲 (1V/V 固定ゲイン) およびゲイン範囲 (25℃) にわたって測定された INL を、図 4-7 に示します。

図 4-7. INL 誤差と入力電圧との関係

ADS127L21 データシートに記載されている標準 INL は 0.4ppm で、0℃~70℃までの範囲で最大 1.8ppm です。 PGA855 の場合、記載されている標準 INL は 2ppm、最大値は 10ppm で、図 4-7 に示すように、1 つのユニットについて収集されたデータと一致しています。

# 4.4.4 SNR およびノイズ性能

設計のノイズ性能と SNR の詳細については、次のアプリケーション ノートを参照してください。 *完全差動のプログラマブ ル グイン アンプ PGA855 により高い SNR を実現*

# 5 設計とドキュメントのサポート

## 5.1 デザイン ファイル

#### 5.1.1 回路図

回路図をダウンロードするには、TIDA-010945 のデザイン ファイルを参照してください。

#### 5.1.2 BOM (部品表)

部品表 (BOM) をダウンロードするには、TIDA-010945 のデザイン ファイルを参照してください。

#### 5.2 ソフトウェア

ADS127L21 EVM ソフトウェア ユーザー イン このリファレンス デザインは、ADS127L21 EVM 専用の GUI と組み合わ せて使用することを意図しています ターフェイス

#### 5.3 ドキュメントのサポート

- 1. テキサス・インスツルメンツ、『ADS127L21 512kSPS、プログラマブル フィルタ、24 ビット、広帯域幅のデルタ-シグマ ADC 』データシート

- 2. テキサス・インスツルメンツ、『PGA855 低ノイズ、広帯域幅、完全差動出力、プログラマブル ゲインの計測アンプ 』デ ータシート

- 3. テキサス・インスツルメンツ、『ADS127L21EVM-PDK 評価基板 』ユーザー ガイド

# 5.4 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパ ートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要 な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕 様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツ ルメンツの使用条件を参照してください。

## 5.5 商標

テキサス・インスツルメンツの™ and テキサス・インスツルメンツ E2E™ are trademarks of Texas Instruments. すべての商標は、それぞれの所有者に帰属します。

資料に関するフィードバック(ご意見やお問い合わせ)を送信

# 6 著者について

MAGGIE LEE はテキサス・インスツルメンツのシステム エンジニアで、テストおよび測定アプリケーションのリファレンス デザイン開発を担当しています。氏は、カリフォルニア工科大学で電気工学の学士号 (B.S.) を取得しました。

このリファレンス デザインへのサポートについて、Keith Nicholas と Luis Chioye に感謝します。

# 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した テキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているテキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、テキサス・インスツルメンツの販売条件、または ti.com やかかる テキサス・インスツルメンツ製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2024, Texas Instruments Incorporated

# 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス・デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあら ゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TIの製品は、TIの販売条件、または ti.com やかかる TI 製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、TIはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2024, Texas Instruments Incorporated