# *LP5810 4-Channel RGBW LED Driver Register Map*

Technical Reference Manual

UTEXAS INSTRUMENTS

Literature Number: SNVU926 OCTOBER 2024

# Table of Contents

# TEXAS INSTRUMENTS

| Read This First                           | 5  |

|-------------------------------------------|----|

|                                           |    |

| About This Manual                         |    |

| Notational Conventions                    |    |

| Glossary                                  |    |

| Related Documentation                     |    |

| Support Resources                         |    |

| 1 Introduction/Feature Overview           |    |

| 1.1 Overview                              | 6  |

| 2 Register Maps                           | 7  |

| 2.1 Register Map Table                    | 8  |

| 2.2 Device_Enable Registers               | 14 |

| 2.3 Config Registers                      | 14 |

| 2.4 Command Registers                     | 20 |

| 2.5 LED_Enable Registers                  | 22 |

| 2.6 Fault_Clear Registers                 |    |

| 2.7 Reset Registers                       |    |

| 2.8 Manual DC Registers                   |    |

| 2.9 Manual_PWM Registers                  |    |

| 2.10 Autonomous DC Registers              |    |

| 2.11 LED 0 Autonomous Animation Registers |    |

| 2.12 LED_1_Autonomous_Animation Registers |    |

| 2.13 LED_2_Autonomous_Animation Registers |    |

| 2.14 LED_3_Autonomous_Animation Registers |    |

| 2.15 Flag Registers.                      |    |

| Revision History                          |    |

|                                           |    |

3

This page intentionally left blank.

Preface Read This First

# About This Manual

This Technical Reference Manual (TRM) details the register maps of LP5810.

The TRM should not be considered a substitute for the data sheet, rather a companion guide that should be used alongside the device-specific data sheet to understand the details to program the device. The primary purpose of the TRM is to abstract the programming registers of the device from the data manual. This allows the data sheet to outline the high-level features of the device without unnecessary information about register descriptions.

# **Notational Conventions**

This document uses the following conventions.

- Hexadecimal numbers can be shown with the suffix h or the prefix 0x. For example, the following number is 40 hexadecimal (decimal 64): 40h or 0x40.

- Registers in this document are shown in figures and described in tables.

- Each register figure shows a rectangle divided into fields that represent the fields of the register. Each field

is labeled with its bit name, its beginning and ending bit numbers above, and its read/write properties with

default reset value below. A legend explains the notation used for the properties.

- Reserved bits in a register figure can have one of multiple meanings:

- Not implemented on the device

- Reserved for future device expansion

- Reserved for TI testing

- · Reserved configurations of the device that are not supported

- Writing nondefault values to the Reserved bits could cause unexpected behavior and should be avoided.

# Glossary

TI Glossary This glossary lists and explains terms, acronyms, and definitions.

# **Related Documentation**

For a complete listing of related documentation and development-support tools, visit the Texas Instruments website at http://www.ti.com.

**SNVSCD0B** *LP5810 4-Channel RGBW LED Driver With Autonomous Control* describes the data sheet of the LP5810 device.

# Support Resources

TI E2E<sup>™</sup> support forums are an engineer's go-to source for fast, verified answers and design help — straight from the experts. Search existing answers or ask your own question to get the quick design help you need.

Linked content is provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

# Trademarks

TI E2E<sup>™</sup> is a trademark of Texas Instruments. All trademarks are the property of their respective owners.

5

# Chapter 1 Introduction/Feature Overview

# 1.1 Overview

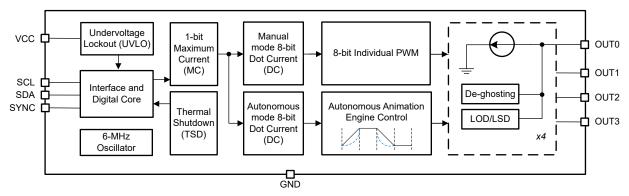

The LP5810 is a 4-Channel RGBW LED driver with autonomous animation engine control. The LP5810 has ultra-low operation current at active mode, consuming 0.4 mA when LED maximum current setting is 25.5 mA. If all LEDs are turned off, the device enters standby state to reduce power consumption with data retained. When 'chip\_enable' bit setting is 0, initial state is entered with minimum power consumption to save power.

The LP5810 supports both analog dimming and PWM dimming. In analog dimming, the output current of each LED can be adjusted with 256 steps. In PWM dimming, the integrated 8-bit configurable PWM generator enables smooth brightness dimming control. Optional exponential PWM dimming can be activated for individual LED to achieve a human-eye-friendly visual performance.

The LP5810 integrates autonomous animation engine, with no need for brightness control commands from controller. Each LED has an individual animation engine which can be configured through the related registers. The device can generate a 6 MHz clock signal, which synchronizes the lighting effects among multiple devices.

The LP5810 has 4 different material versions with different I2C chip address. Up to 4 LP581x devices can be connected to the same I2C bus and controlled individually.

Figure 1-1. Device Block Diagram

Chapter 2 Register Maps

# TEXAS INSTRUMENTS

This section shows the detailed register maps of LP5810.

| 2.1 Register Map Table                           | 8  |

|--------------------------------------------------|----|

| 2.2 Device_Enable Registers                      | 14 |

| 2.2 Device_Enable Registers                      | 14 |

| 2.4 Command Registers                            | 20 |

| 2.5 LED_Enable Registers                         | 22 |

| 2.6 Fault_Clear Registers                        | 23 |

| 2.6 Fault_Clear Registers<br>2.7 Reset Registers |    |

| 2.8 Manual_DC Registers                          |    |

| 2.9 Manual_PWM Registers                         | 26 |

| 2.10 Autonomous_DC Registers                     |    |

| 2.11 LED_0_Autonomous_Animation Registers        |    |

| 2.12 LED_1_Autonomous_Animation Registers        | 57 |

| 2.13 LED_2_Autonomous_Animation Registers        | 67 |

| 2.14 LED_3_Autonomous_Animation Registers        |    |

| 2.15 Flag Registers                              | 89 |

|                                                  |    |

7

# 2.1 Register Map Table

This section provides a summary of the register maps.

| _                     |         |      |           | gister Se             |             |       |               | ess Type       | Codes            |               |               |         |

|-----------------------|---------|------|-----------|-----------------------|-------------|-------|---------------|----------------|------------------|---------------|---------------|---------|

| Access Type           |         | Cod  | 9         |                       |             | Des   | cription      |                |                  |               |               |         |

| Read Type             |         |      |           |                       |             |       |               |                |                  |               |               |         |

| R                     |         | R    |           |                       |             | Read  | d             |                |                  |               |               |         |

| RC                    |         | R    |           |                       |             | Read  | d             |                |                  |               |               |         |

|                       |         | С    |           |                       | 1           | to Cl | ear           |                |                  |               |               |         |

| R-0                   |         | R    |           |                       | 1           | Read  | d             |                |                  |               |               |         |

|                       |         | -0   |           |                       |             | Retu  | ırns 0        |                |                  |               |               |         |

| Write Type            |         |      |           |                       |             |       |               |                |                  |               |               |         |

| W                     |         | W    |           |                       | 1           | Write | Э             |                |                  |               |               |         |

| W1C                   |         | W    |           |                       |             | W     |               |                |                  |               |               |         |

|                       |         | 1C   |           |                       |             | 1 to  | clear         |                |                  |               |               |         |

| Reset or Default Valu | е       |      |           |                       |             |       |               |                |                  |               |               |         |

| - <i>n</i>            |         |      |           |                       |             | Valu  | e after rese  | et or the de   | fault value      |               |               |         |

|                       |         |      |           |                       |             |       |               |                |                  |               |               |         |

| Register Acronym      | Address | Туре | D7        | D6                    | D5          |       | D4            | D3             | D2               | D1            | D0            | Default |

| Device_Enable Reg     | ister   | 1    |           |                       |             |       |               |                |                  |               | 1             |         |

| Chip_en               | 000h    | R/W  | Reserved  |                       |             |       |               |                |                  |               | chip_en       | 00h     |

| Config Registers      |         |      |           |                       |             |       |               |                |                  |               |               |         |

| Dev_Config_0          | 001h    | R/W  | Reserved  | Reserved max_curr ent |             |       |               |                |                  | 00h           |               |         |

| Dev_Config_1          | 002h    | R/W  | pwm_fre   | led_mode              | )           |       |               | Reserved       |                  |               |               | 00h     |

| Dev_Config_2          | 003h    | R/W  | Reserved  |                       |             |       |               |                |                  |               |               | 00h     |

| Dev_Config_3          | 004h    | R/W  | Reserved  |                       |             |       |               | auto_en_<br>3  | auto_en_<br>2    | auto_en_<br>1 | auto_en_<br>0 | 00h     |

| Dev_Config_4          | 005h    | R/W  | Reserved  |                       |             |       |               |                |                  |               |               | 00h     |

| Dev_Config_5          | 006h    | R/W  | Reserved  |                       |             |       |               | exp_en_3       | exp_en_2         | exp_en_1      | exp_en_0      | 00h     |

| Dev_Config_6          | 007h    | R/W  | Reserved  |                       |             |       |               |                | 1                | 1             | 1             | 00h     |

| Dev_Config_7          | 008h    | R/W  | phase_ali | gn_3                  | phase_      | alig  | n_2           | phase_ali      | gn_1             | phase_ali     | gn_0          | 00h     |

| Dev_Config_8          | 009h    | R/W  | Reserved  |                       |             |       |               |                |                  |               |               | 00h     |

| Dev_Config_9          | 00Ah    | R/W  | Reserved  |                       |             |       |               |                |                  |               |               | 00h     |

| Dev_Config_10         | 00Bh    | R/W  | Reserved  |                       |             |       |               |                |                  |               |               | 00h     |

| Dev_Config_11         | 00Ch    | R/W  | Reserved  |                       |             |       |               |                | vsync_ou<br>t_en | blank_time    | 9             | 00h     |

| Dev_Config_12         | 00Dh    | R/W  | vmid_sel  |                       | clamp_<br>I | -     | clamp_di<br>s | lod_actio<br>n | lsd_actio<br>n   | lsd_thresh    | nold          | 08h     |

| Command Registers     | S       |      |           |                       | 1           |       |               |                |                  |               |               |         |

| CMD_Update            | 010h    | W1C  | update_co | ommand                |             |       |               |                |                  |               |               | 00h     |

| CMD_Start             | 011h    | W1C  | start_com |                       |             |       |               |                |                  | 00h           |               |         |

| CMD_Stop              | 012h    | W1C  | stop_com  | mand                  |             |       |               |                |                  |               |               | 00h     |

| CMD_Pause             | 013h    | W1C  | pause_co  |                       |             |       |               |                |                  |               |               | 00h     |

| CMD_Continue          | 014h    | W1C  | continue_ | command               |             |       |               |                |                  |               |               | 00h     |

| led_enable Register   | s       | 1    |           |                       |             |       |               |                |                  | 1             |               |         |

| led_en_1              | 020h    | R/W  | Reserved  |                       |             |       |               | led_en_3       | led_en_2         | led_en_1      | led_en_0      | 00h     |

| Fault_Clear Registe   | r       | 1    | 1         |                       |             |       |               |                |                  |               |               | 1       |

| Fault_Clear           | 022h    | W1C  | Reserved  |                       |             |       |               |                | tsd_clear        | lsd_clear     | lod_clear     | 00h     |

|                       | 1       | -    | 1         |                       |             |       |               |                |                  |               |               |         |

| Register Acronym            | Address | Туре | D7            | D6       | D5        | D4    | D3          | D2        | D1      | D0     | Default |

|-----------------------------|---------|------|---------------|----------|-----------|-------|-------------|-----------|---------|--------|---------|

| Reset Register              |         |      |               |          |           |       | ·           |           | ·       | ·      | ·       |

| Reset                       | 023h    | W1C  | sw_reset      |          |           |       |             |           |         |        | 00h     |

| Manual_DC Register          | s       |      |               |          |           |       |             |           |         |        |         |

| Manual_DC_0                 | 030h    | R/W  | manual_do     | c_0      |           |       |             |           |         |        | 00h     |

| Manual_DC_1                 | 031h    | R/W  | manual_do     | c_1      |           |       |             |           |         |        | 00h     |

| Manual_DC_2                 | 032h    | R/W  | manual_do     | c_2      |           |       |             |           |         |        | 00h     |

| Manual_DC_3                 | 033h    | R/W  | manual_do     | 2_3      |           |       |             |           |         |        | 00h     |

| Manual PWM Registe          | ers     |      |               |          |           |       |             |           |         |        |         |

| Manual_PWM_0                | 040h    | R/W  | manual_p      | wm_0     |           |       |             |           |         |        | 00h     |

| Manual_PWM_1                | 041h    | R/W  | manual_p      | vm 1     |           |       |             |           |         |        | 00h     |

| <br>Manual_PWM_2            | 042h    | R/W  | manual_p      | _        |           |       |             |           |         |        | 00h     |

| <br>Manual_PWM_3            | 043h    | R/W  | <br>manual_p\ |          |           |       |             |           |         |        | 00h     |

| Autonomous_DC Re            |         |      | _1            |          |           |       |             |           |         |        |         |

| Auto_DC_0                   | 050h    | R/W  | auto dc 0     | 1        |           |       |             |           |         |        | 00h     |

| Auto_DC_1                   | 051h    | R/W  | auto_dc_0     |          |           |       |             |           |         |        | 00h     |

| Auto_DC_1<br>Auto_DC_2      | 051h    | R/W  | auto_dc_1     |          |           |       |             |           |         |        | 00h     |

| Auto_DC_2<br>Auto_DC_3      | 052h    | R/W  |               |          |           |       |             |           |         |        | 00h     |

|                             |         |      | auto_dc_3     |          |           |       |             |           |         |        | 0011    |

| LED_0_Autonomous            |         | -    |               |          |           |       |             |           |         |        | 0.01    |

| ED_0_Auto_Paus              | 080h    | R/W  | led_0_pau     | se_start | 1         |       | led_0_p     | ause_stop |         |        | 00h     |

| _ED_0_Auto_Playb<br>ack     | 081h    | R/W  | Reserved      |          | led_0_aeu | I_num | LED_0_      | _pt       |         |        | 00h     |

| _ED_0_AEU1_PWM<br>_1        | 082h    | R/W  | led_0_aeu     | 1_pwm1   |           |       |             |           |         |        | 00h     |

| _ED_0_AEU1_PWM<br>_2        | 083h    | R/W  | led_0_aeu     | 1_pwm2   |           |       |             |           |         |        | 00h     |

| _ED_0_AEU1_PWM<br>_3        | 084h    | R/W  | led_0_aeu     | 1_pwm3   |           |       |             |           |         |        | 00h     |

| LED_0_AEU1_PWM<br>_4        | 085h    | R/W  | led_0_aeu     | 1_pwm4   |           |       |             |           |         |        | 00h     |

| LED_0_AEU1_PWM<br>_5        | 086h    | R/W  | led_0_aeu     | 1_pwm5   |           |       |             |           |         |        | 00h     |

| _ED_0_AEU1_T12              | 087h    | R/W  | led_0_aeu     | 1_t2     |           |       | led_0_a     | eu1_t1    |         |        | 00h     |

| <br>_ED_0_AEU1_T34          | 088h    | R/W  | led_0_aeu     |          |           |       | <br>led_0_a |           |         |        | 00h     |

| <br>LED_0_AEU1_Play<br>back | 089h    | R/W  | Reserved      |          |           |       |             |           | led_0_a | eu1_pt | 00h     |

| LED_0_AEU2_PWM<br>_1        | 08Ah    | R/W  | led_0_aeu     | 2_pwm1   |           |       |             |           | I       |        | 00h     |

|                             | 08Bh    | R/W  | led_0_aeu     | 2_pwm2   |           |       |             |           |         |        | 00h     |

| _<br>_ED_0_AEU2_PWM<br>_3   | 08Ch    | R/W  | led_0_aeu     | 2_pwm3   |           |       |             |           |         |        | 00h     |

| <br>_ED_0_AEU2_PWM<br>_4    | 08Dh    | R/W  | led_0_aeu     | 2_pwm4   |           |       |             |           |         |        | 00h     |

| _<br>LED_0_AEU2_PWM<br>_5   | 08Eh    | R/W  | led_0_aeu     | 2_pwm5   |           |       |             |           |         |        | 00h     |

| LED_0_AEU2_T12              | 08Fh    | R/W  | led_0_aeu     | 2 t2     |           |       | led_0_a     | eu2 t1    |         |        | 00h     |

| LED_0_AEU2_T34              | 090h    | R/W  | led_0_aeu     |          |           |       | led_0_a     |           |         |        | 00h     |

| LED_0_AEU2_Play             | 091h    | R/W  | Reserved      | <u> </u> |           |       |             |           | led_0_a | eu2_pt | 00h     |

Register Maps

| Register Acronym        | Address   | Туре    | D7        | D6       | D5        | D4   | D3       | D2        | D1      | D0     | Default |

|-------------------------|-----------|---------|-----------|----------|-----------|------|----------|-----------|---------|--------|---------|

| LED_0_AEU3_PWM<br>_1    | 092h      | R/W     | led_0_aeu | 3_pwm1   |           |      |          |           |         |        | 00h     |

| LED_0_AEU3_PWM<br>_2    | 093h      | R/W     | led_0_aeu | 3_pwm2   |           |      |          |           |         |        | 00h     |

| LED_0_AEU3_PWM<br>_3    | 094h      | R/W     | led_0_aeu | 3_pwm3   |           |      |          |           |         |        | 00h     |

| LED_0_AEU3_PWM<br>_4    | 095h      | R/W     | led_0_aeu | 3_pwm4   |           |      |          |           |         |        | 00h     |

| LED_0_AEU3_PWM<br>_5    | 096h      | R/W     | led_0_aeu | 3_pwm5   |           |      |          |           |         |        | 00h     |

| LED_0_AEU3_T12          | 097h      | R/W     | led_0_aeu | 3_t2     |           |      | led_0_a  | eu3_t1    |         |        | 00h     |

| LED_0_AEU3_T34          | 098h      | R/W     | led_0_aeu | 3_t4     |           |      | led_0_a  | eu3_t3    |         |        | 00h     |

| LED_0_AEU3_Play<br>back | 099h      | R/W     | Reserved  |          |           |      | L        |           | led_0_a | eu3_pt | 00h     |

| LED_1 Autonomous        | Animation | n Regis | ters      |          |           |      |          |           |         |        | I.      |

| LED_1_Auto_Paus<br>e    | 09Ah      | R/W     | led_1_pau | se_start |           |      | led_1_pa | ause_stop |         |        | 00h     |

| LED_1_Auto_Playb<br>ack | 09Bh      | R/W     | Reserved  |          | led_1_aeu | _num | led_1_pt |           |         |        | 00h     |

| LED_1_AEU1_PWM<br>_1    | 09Ch      | R/W     | led_1_aeu | 1_pwm1   |           |      | i.       |           |         |        | 00h     |

| LED_1_AEU1_PWM<br>_2    | 09Dh      | R/W     | led_1_aeu | 1_pwm2   |           |      |          |           |         |        | 00h     |

| LED_1_AEU1_PWM<br>_3    | 09Eh      | R/W     | led_1_aeu | 1_pwm3   |           |      |          |           |         |        | 00h     |

| LED_1_AEU1_PWM<br>_4    | 09Fh      | R/W     | led_1_aeu | 1_pwm4   |           |      |          |           |         |        | 00h     |

| LED_1_AEU1_PWM<br>_5    | 0A0h      | R/W     | led_1_aeu | 1_pwm5   |           |      |          |           |         |        | 00h     |

| LED_1_AEU1_T12          | 0A1h      | R/W     | led_1_aeu | 1_t2     |           |      | led_1_a  | eu1_t1    |         |        | 00h     |

| LED_1_AEU1_T34          | 0A2h      | R/W     | led_1_aeu | 1_t4     |           |      | led_1_a  | eu1_t3    |         |        | 00h     |

| LED_1_AEU1_Play<br>back | 0A3h      | R/W     | Reserved  |          |           |      |          |           | led_1_a | eu1_pt | 00h     |

| LED_1_AEU2_PWM<br>_1    | 0A4h      | R/W     | led_1_aeu | 2_pwm1   |           |      |          |           |         |        | 00h     |

| LED_1_AEU2_PWM<br>_2    | 0A5h      | R/W     | led_1_aeu | 2_pwm2   |           |      |          |           |         |        | 00h     |

| LED_1_AEU2_PWM<br>_3    | 0A6h      | R/W     | led_1_aeu | 2_pwm3   |           |      |          |           |         |        | 00h     |

| LED_1_AEU2_PWM<br>_4    | 0A7h      | R/W     | led_1_aeu | 2_pwm4   |           |      |          |           |         |        | 00h     |

| LED_1_AEU2_PWM<br>_5    | 0A8h      | R/W     | led_1_aeu | 2_pwm5   |           |      |          |           |         |        | 00h     |

| LED_1_AEU2_T12          | 0A9h      | R/W     | led_1_aeu | 1_t2     |           |      | led_1_a  | eu1_t1    |         |        | 00h     |

| LED_1_AEU2_T34          | 0AAh      | R/W     | led_1_aeu | 1_t4     |           |      | led_1_a  | eu1_t3    |         |        | 00h     |

| LED_1_AEU2_Play<br>back | 0ABh      | R/W     | Reserved  |          |           |      |          |           | led_1_a | eu2_pt | 00h     |

| LED_1_AEU3_PWM<br>_1    | 0ACh      | R/W     | led_1_aeu | 3_pwm1   |           |      |          |           |         |        | 00h     |

| LED_1_AEU3_PWM<br>_2    | 0ADh      | R/W     | led_1_aeu | 3_pwm2   |           |      |          |           |         |        | 00h     |

| LED_1_AEU3_PWM          | 0AEh      | R/W     | led_1_aeu | 3_pwm3   |           |      |          |           |         |        | 00h     |

| Register Acronym                 | Address   | Туре    | D7        | D6        | D5        | D4    | D3      | D2        | D1      | D0     | Default |

|----------------------------------|-----------|---------|-----------|-----------|-----------|-------|---------|-----------|---------|--------|---------|

| LED_1_AEU3_PWM<br>_4             | 0AFh      | R/W     | led_1_aeu | 13_pwm4   |           | ·     | i       | i         |         |        | 00h     |

| LED_1_AEU3_PWM<br>_5             | 0B0h      | R/W     | led_1_aeu | 13_pwm5   |           |       |         |           |         |        | 00h     |

| LED_1_AEU3_T12                   | 0B1h      | R/W     | led_1_aeu | ı3_t2     |           |       | led_1_a | ieu3_t1   |         |        | 00h     |

| LED_1_AEU3_T34                   | 0B2h      | R/W     | led_1_aeu | ı3_t4     |           |       | led_1_a | ieu3_t3   |         |        | 00h     |

| LED_1_AEU3_Play<br>back          | 0B3h      | R/W     | Reserved  |           |           |       | ·       |           | led_1_a | eu3_pt | 00h     |

| LED_2 Autonomous                 | Animation | n Regis | ters      |           |           |       |         |           |         |        |         |

| LED_2_Auto_Paus<br>e             | 0B4h      | R/W     | led_2_pau | ise_start |           |       | led_2_p | ause_stop |         |        | 00h     |

| LED_2_Auto_Playb<br>ack          | 0B5h      | R/W     | Reserved  |           | led_2_aeu | u_num | led_2_p | ot        |         |        | 00h     |

| LED_2_AEU1_PWM<br>_1             |           | R/W     | led_2_aeu | 1_pwm1    |           |       |         |           |         |        | 00h     |

| LED_2_AEU1_PWM<br>_2             | 0B7h      | R/W     | led_2_aeu | 1_pwm2    |           |       |         |           |         |        | 00h     |

| LED_2_AEU1_PWM<br>_3             |           | R/W     | led_2_aeu | 1_pwm3    |           |       |         |           |         |        | 00h     |

| LED_2_AEU1_PWM<br>_ <sup>4</sup> |           | R/W     | led_2_aeu |           |           |       |         |           |         |        | 00h     |

| LED_2_AEU1_PWM<br>_5             | 0BAh      | R/W     | led_2_aeu | 1_pwm5    |           |       |         |           |         |        | 00h     |

| LED_2_AEU1_T12                   | 0BBh      | R/W     | led_2_aeu | _         |           |       | led_2_a |           |         |        | 00h     |

| LED_2_AEU1_T34                   | 0BCh      | R/W     | led_2_aeu | ı1_t4     |           |       | led_2_a | ieu1_t3   |         |        | 00h     |

| LED_2_AEU1_Play<br>back          | 0BDh      | R/W     | Reserved  |           |           |       |         |           | led_2_a | eu1_pt | 00h     |

| LED_2_AEU2_PWM<br>_1             |           | R/W     | led_2_aeu | I2_pwm1   |           |       |         |           |         |        | 00h     |

| LED_2_AEU2_PWM<br>_2             |           | R/W     | led_2_aeu |           |           |       |         |           |         |        | 00h     |

| LED_2_AEU2_PWM<br>_ <sup>3</sup> |           | R/W     | led_2_aeu |           |           |       |         |           |         |        | 00h     |

| LED_2_AEU2_PWM<br>_4             | 0C1h      | R/W     | led_2_aeu | 12_pwm4   |           |       |         |           |         |        | 00h     |

| LED_2_AEU2_PWM<br>_5             | 0C2h      | R/W     | led_2_aeu | 12_pwm5   |           |       |         |           |         |        | 00h     |

| LED_2_AEU2_T12                   | 0C3h      | R/W     | led_2_aeu | _         |           |       | led_2_a |           |         |        | 00h     |

| LED_2_AEU2_T34                   | 0C4h      | R/W     | led_2_aeu | ı2_t4     |           |       | led_2_a | ieu2_t3   |         |        | 00h     |

| LED_2_AEU2_Play<br>back          | 0C5h      | R/W     | Reserved  |           |           |       |         |           | led_2_a | eu2_pt | 00h     |

| LED_2_AEU3_PWM<br>_1             |           | R/W     | led_2_aeu |           |           |       |         |           |         |        | 00h     |

| LED_2_AEU3_PWM<br>_2             | 0C7h      | R/W     | led_2_aeu | I3_pwm2   |           |       |         |           |         |        | 00h     |

| LED_2_AEU3_PWM<br>_ <sup>3</sup> |           | R/W     | led_2_aeu | 13_pwm3   |           |       |         |           |         |        | 00h     |

| LED_2_AEU3_PWM<br>_4             | 0C9h      | R/W     | led_2_aeu | I3_pwm4   |           |       |         |           |         |        | 00h     |

| LED_2_AEU3_PWM<br>_5             | 0CAh      | R/W     | led_2_aeu | I3_pwm5   |           |       |         |           |         |        | 00h     |

| LED_2_AEU3_T12                   | 0CBh      | R/W     | led_2_aeu | ı3_t2     |           |       | led_2_a | ieu3_t1   |         |        | 00h     |

| LED_2_AEU3_T34                   | 0CCh      | R/W     | led_2_aeu | ı3_t4     |           |       | led_2_a | ieu3_t3   |         |        | 00h     |

Register Maps

| Register Acronym        | Address   | Туре  | D7        | D6       | D5        | D4    | D3        | D2       | D1             | D0                    | Default |

|-------------------------|-----------|-------|-----------|----------|-----------|-------|-----------|----------|----------------|-----------------------|---------|

| LED_2_AEU3_Play<br>back | 0CDh      | R/W   | Reserved  |          |           |       |           |          | led_2_aeu      | I3_pt                 | 00h     |

| LED_3 Autonomous        | Animatior | Regis | ters      |          |           |       |           |          | 1              |                       | -       |

| LED_3_Auto_Paus<br>e    | 0CEh      | R/W   | led_3_pau | se_start |           |       | led_3_pau | ise_stop |                |                       | 00h     |

| LED_3_Auto_Playb<br>ack | 0CFh      | R/W   | Reserved  |          | led_3_aeu | I_num | led_3_pt  |          |                |                       | 00h     |

| LED_3_AEU1_PWM<br>_1    | 0D0h      | R/W   | led_3_aeu | 1_pwm1   |           |       |           |          |                |                       | 00h     |

| LED_3_AEU1_PWM<br>_2    | 0D1h      | R/W   | led_3_aeu | 1_pwm2   |           |       |           |          |                |                       | 00h     |

| LED_3_AEU1_PWM<br>_3    | 0D2h      | R/W   | led_3_aeu | 1_pwm3   |           |       |           |          |                |                       | 00h     |

| LED_3_AEU1_PWM<br>_4    | 0D3h      | R/W   | led_3_aeu | 1_pwm4   |           |       |           |          |                |                       | 00h     |

| LED_3_AEU1_PWM<br>_5    | 0D4h      | R/W   | led_3_aeu | 1_pwm5   |           |       |           |          |                |                       | 00h     |

| LED_3_AEU1_T12          | 0D5h      | R/W   | led_3_aeu | 1_t2     |           |       | led_3_aeu | 1_t1     |                |                       | 00h     |

| LED_3_AEU1_T34          | 0D6h      | R/W   | led_3_aeu | 1_t4     |           |       | led_3_aeu | 1_t3     |                |                       | 00h     |

| LED_3_AEU1_Play<br>back | 0D7h      | R/W   | Reserved  |          |           |       |           |          | led_3_aeu      | ı1_pt                 | 00h     |

| LED_3_AEU2_PWM<br>_1    | 0D8h      | R/W   | led_3_aeu | 2_pwm1   |           |       |           |          |                |                       | 00h     |

| LED_3_AEU2_PWM<br>_2    | 0D9h      | R/W   | led_3_aeu | 2_pwm2   |           |       |           |          |                |                       | 00h     |

| LED_3_AEU2_PWM<br>_3    | 0DAh      | R/W   | led_3_aeu | 2_pwm3   |           |       |           |          |                |                       | 00h     |

| LED_3_AEU2_PWM<br>_4    | 0DBh      | R/W   | led_3_aeu | 2_pwm4   |           |       |           |          |                |                       | 00h     |

| LED_3_AEU2_PWM<br>_5    | 0DCh      | R/W   | led_3_aeu | 2_pwm5   |           |       |           |          |                |                       | 00h     |

| LED_3_AEU2_T12          | 0DDh      | R/W   | led_3_aeu | _        |           |       | led_3_aeu | _        |                |                       | 00h     |

| LED_3_AEU2_T34          | 0DEh      | R/W   | led_3_aeu | 2_t4     |           |       | led_3_aeu | 12_t3    | 1              |                       | 00h     |

| LED_3_AEU2_Play<br>back | 0DFh      | R/W   | Reserved  |          |           |       |           |          | led_3_aeu      | I2_pt                 | 00h     |

| LED_3_AEU3_PWM<br>_1    |           | R/W   | led_3_aeu |          |           |       |           |          |                |                       | 00h     |

| LED_3_AEU3_PWM<br>_2    |           | R/W   | led_3_aeu |          |           |       |           |          |                |                       | 00h     |

| LED_3_AEU3_PWM<br>_3    |           | R/W   | led_3_aeu |          |           |       |           |          |                |                       | 00h     |

| LED_3_AEU3_PWM<br>_4    |           | R/W   | led_3_aeu |          |           |       |           |          |                |                       | 00h     |

| LED_3_AEU3_PWM<br>_5    |           | R/W   | led_3_aeu | 3_pwm5   |           |       |           |          |                |                       | 00h     |

| LED_3_AEU3_T12          | 0E5h      | R/W   | led_3_aeu | _        |           |       | led_3_aeu |          |                |                       | 00h     |

| LED_3_AEU3_T34          | 0E6h      | R/W   | led_3_aeu | 3_t4     |           |       | led_3_aeu | 13_t3    | 1              |                       | 00h     |

| LED_3_AEU3_Play<br>back | 0E7h      | R/W   | Reserved  |          |           |       |           |          | led_3_aeu      | 13_pt                 | 00h     |

| Flag Registers          |           |       |           |          |           |       |           |          | 1              | 1                     |         |

| TSD_Config_Status       | 300h      | R     | Reserved  |          |           |       |           |          | tsd_Statu<br>s | config_er<br>r_status | 00h     |

| Register Acronym | Address | Туре | D7                                 | D6         | D5         | D4  | D3               | D2               | D1               | D0               | Default |

|------------------|---------|------|------------------------------------|------------|------------|-----|------------------|------------------|------------------|------------------|---------|

| LOD_Status_0     | 301h    | R    | Reserved                           |            |            | ·   | lod_statu<br>s_3 | lod_statu<br>s_2 | lod_statu<br>s_1 | lod_statu<br>s_0 | 00h     |

| LOD_Status_1     | 302h    | R    | Reserved                           |            |            |     |                  |                  | 00h              |                  |         |

| LSD_Status_0     | 303h    | R    | Reserved                           |            |            |     | lsd_statu<br>s_3 | lsd_statu<br>s_2 | lsd_statu<br>s_1 | lsd_statu<br>s_0 | 00h     |

| LSD_Status_1     | 304h    | R    | Reserved                           | Reserved   |            |     |                  |                  |                  | 00h              |         |

| Auto_PWM_0       | 305h    | R    | pwm_auto                           | _0         |            |     |                  |                  |                  |                  | 00h     |

| Auto_PWM_1       | 306h    | R    | pwm_auto                           | _1         |            |     |                  |                  |                  |                  | 00h     |

| Auto_PWM_2       | 307h    | R    | pwm_auto                           | _2         |            |     |                  |                  |                  |                  | 00h     |

| Auto_PWM_3       | 308h    | R    | pwm_auto                           | pwm_auto_3 |            |     |                  |                  |                  | 00h              |         |

| AEP_Status_0     | 315h    | R    | Reserved aep_status_1 aep_status_0 |            |            |     |                  |                  | 3Fh              |                  |         |

| AEP_Status_1     | 316h    | R    | Reserved                           |            | aep_status | s_3 |                  | aep_statu        | s_2              |                  | 3Fh     |

# 2.2 Device\_Enable Registers

Table 2-2 lists the memory-mapped registers for the Device Enable registers. All register offset addresses not listed in Table 2-2 should be considered as reserved locations and the register contents should not be modified.

| Table 2-2. DEVICE_ENABLE Registers |  |

|------------------------------------|--|

|------------------------------------|--|

| Offset | Acronym | Register Name                | Section |

|--------|---------|------------------------------|---------|

| 0h     | Chip_EN | Enable the internal circuits | Go      |

Complex bit access types are encoded to fit into small table cells. Table 2-3 shows the codes that are used for access types in this section.

| Access Type      | Code  | Description                            |

|------------------|-------|----------------------------------------|

| Read Type        |       |                                        |

| R                | R     | Read                                   |

| Write Type       |       |                                        |

| W                | W     | Write                                  |

| Reset or Default | Value |                                        |

| -n               |       | Value after reset or the default value |

# Table 2-3. Device Enable Access Type Codes

# 2.2.1 Chip\_EN Register (Offset = 0h) [Reset = 00h]

Chip\_EN is shown in Figure 2-1 and described in Table 2-4.

Return to the Summary Table.

# Figure 2-1. Chip\_EN Register

| 7        | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|----------|---|---|---|---|---|---|---|--|--|

| RESERVED |   |   |   |   |   |   |   |  |  |

| R-0h     |   |   |   |   |   |   |   |  |  |

# Table 2-4. Chip\_EN Register Field Descriptions

| Bit | Field    | Туре | Reset | Description                                                |

|-----|----------|------|-------|------------------------------------------------------------|

| 7-1 | RESERVED | R    | 0h    | Reserved                                                   |

| 0   | chip_en  | R/W  |       | Enable the internal circuits; 0h = Disable; 1h =<br>Enable |

# 2.3 Config Registers

Table 2-5 lists the memory-mapped registers for the Config registers. All register offset addresses not listed in Table 2-5 should be considered as reserved locations and the register contents should not be modified.

| Offset | Acronym      | Register Name                                                                            | Section |

|--------|--------------|------------------------------------------------------------------------------------------|---------|

| 1h     | Dev_Config_0 | Device configuration register 0, including max current<br>sinks current settings         | Go      |

| 2h     | Dev_Config_1 | Device configuration register 1, including LED configuration and PWM frequency settings  | Go      |

| 3h     | Dev_Config_2 | Device configuration register 2, reserved                                                |         |

| 4h     | Dev_Config_3 | Device configuration register 3, including autonomous enable settings for LED_0 to LED_3 | Go      |

| 5h     | Dev_Config_4 | Device configuration register 4, reserved                                                |         |

| Offset | Acronym       | Register Name                                                                                      | Section |

|--------|---------------|----------------------------------------------------------------------------------------------------|---------|

| 6h     | Dev_Config_5  | Device configuration register 5, including exponential<br>curve enable settings for LED_0 to LED_3 | Go      |

| 7h     | Dev_Config_6  | Device configuration register 6, reserved                                                          |         |

| 8h     | Dev_Config_7  | Device configuration register 7, including phase shiftt settings for LED_0 to LED_3                | Go      |

| 9h     | Dev_Config_8  | Device configuration register 8, reserved                                                          |         |

| Ah     | Dev_Config_9  | Device configuration register 9, reserved                                                          |         |

| Bh     | Dev_Config_10 | Device configuration register 10, reserved                                                         |         |

| Ch     | Dev_Config_11 | Device configuration register 11, including line change time and VSYNC settings                    | Go      |

| Dh     | Dev_Config_12 | Device configuration register 12, including threshold and action settings for LOD, LSD and clamp   | Go      |

# Table 2-5. CONFIG Registers (continued)

Complex bit access types are encoded to fit into small table cells. Table 2-6 shows the codes that are used for access types in this section.

| Access Type      | Code                   | Description                            |  |  |  |

|------------------|------------------------|----------------------------------------|--|--|--|

| Read Type        |                        |                                        |  |  |  |

| R                | R                      | Read                                   |  |  |  |

| Write Type       |                        |                                        |  |  |  |

| W                | W                      | Write                                  |  |  |  |

| Reset or Default | Reset or Default Value |                                        |  |  |  |

| -n               |                        | Value after reset or the default value |  |  |  |

# Table 2-6. Config Access Type Codes

# 2.3.1 Dev\_Config\_0 Register (Offset = 1h) [Reset = 00h]

Dev\_Config\_0 is shown in Figure 2-2 and described in Table 2-7.

Return to the Summary Table.

# Figure 2-2. Dev\_Config\_0 Register

| 7        | 7 6 5 4 3 2 1 |  |  |  |  | 0           |        |

|----------|---------------|--|--|--|--|-------------|--------|

| RESERVED |               |  |  |  |  | max_current |        |

| R-0h     |               |  |  |  |  |             | R/W-0h |

# Table 2-7. Dev\_Config\_0 Register Field Descriptions

| Bit | Field       | Туре | Reset | Description                                        |

|-----|-------------|------|-------|----------------------------------------------------|

| 7-1 | RESERVED    | R    | 0h    | Reserved                                           |

| 0   | max_current | R/W  |       | Max output current setting; 0h = 25.5mA; 1h = 51mA |

# 2.3.2 Dev\_Config\_1 Register (Offset = 2h) [Reset = 00h]

Dev\_Config\_1 is shown in Figure 2-3 and described in Table 2-8.

Return to the Summary Table.

# Figure 2-3. Dev\_Config\_1 Register

| 7 6 5 4 3 2 1 0 |   |   | 0 | _ | 0_ |   |   |   |

|-----------------|---|---|---|---|----|---|---|---|

|                 | 7 | 6 | 5 | 4 | 3  | 2 | 1 | 0 |

0

Register Maps

| Figure 2-3. Dev_Config_1 Register (continued) |         |          |          |  |

|-----------------------------------------------|---------|----------|----------|--|

|                                               | pwm_fre | led_mode | RESERVED |  |

|                                               | R/W-0h  | R/W-0h   | R-0h     |  |

| Table 2-8. Dev_ | Config_1 | <b>Register Field</b> | Descriptions |

|-----------------|----------|-----------------------|--------------|

|-----------------|----------|-----------------------|--------------|

| Bit | Field    | Туре | Reset | Description                                              |

|-----|----------|------|-------|----------------------------------------------------------|

| 7   | pwm_fre  | R/W  |       | PWM dimming frequency setting; 0h = 24kHz; 1h<br>= 12kHz |

| 6-4 | led_mode | R/W  | 0h    | LED mode configuration; 0h = Direct drive mode;          |

| 3-0 | RESERVED | R    | 0h    | Reserved                                                 |

# 2.3.3 Dev\_Config\_2 Register (Offset = 3h) [Reset = 00h]

Dev\_Config\_2 is shown in Figure 2-4 and described in Table 2-9.

Return to the Summary Table.

7

| Figure 2-4. Dev_Config_2 Register |   |   |   |   |   |  |

|-----------------------------------|---|---|---|---|---|--|

| 6                                 | 5 | 4 | 3 | 2 | 1 |  |

| RESERVED                          |   |   |   |   |   |  |

| R-0h |

|------|

|      |

# Table 2-9. Dev\_Config\_2 Register Field Descriptions

| Bit | Field    | Туре | Reset | Description |

|-----|----------|------|-------|-------------|

| 7-0 | RESERVED | R    | 0h    | Reserved    |

# 2.3.4 Dev\_Config\_3 Register (Offset = 4h) [Reset = 00h]

Dev\_Config\_3 is shown in Figure 2-5 and described in Table 2-10.

Return to the Summary Table.

# Figure 2-5. Dev\_Config\_3 Register

| 7        | 6 | 5 | 4 | 3         | 2         | 1         | 0         |

|----------|---|---|---|-----------|-----------|-----------|-----------|

| RESERVED |   |   |   | auto_en_3 | auto_en_2 | auto_en_1 | auto_en_0 |

| R-0h     |   |   |   | R/W-0h    | R/W-0h    | R/W-0h    | R/W-0h    |

# Table 2-10. Dev\_Config\_3 Register Field Descriptions

| Bit | Field     | Туре | Reset | Description                                                                                                    |  |

|-----|-----------|------|-------|----------------------------------------------------------------------------------------------------------------|--|

| 7-4 | RESERVED  | R    | 0h    | Reserved                                                                                                       |  |

| 3   | auto_en_3 | R/W  | 0h    | LED_3 autonomous control enable; 0h =<br>Disabled, LED in manual mode; 1h = Enabled,<br>LED in autonomous mode |  |

| 2   | auto_en_2 | R/W  | 0h    | LED_2 autonomous control enable; 0h =<br>Disabled, LED in manual mode; 1h = Enabled,<br>LED in autonomous mode |  |

| 1   | auto_en_1 | R/W  | 0h    | LED_1 autonomous control enable; 0h =<br>Disabled, LED in manual mode; 1h = Enabled,<br>LED in autonomous mode |  |

| 0   | auto_en_0 | R/W  | 0h    | LED_0 autonomous control enable; 0h =<br>Disabled, LED in manual mode; 1h = Enabled,<br>LED in autonomous mode |  |

# 2.3.5 Dev\_Config\_4 Register (Offset = 5h) [Reset = 00h]

Dev\_Config\_4 is shown in Figure 2-6 and described in Table 2-11.

Return to the Summary Table.

| Figure 2-6. Dev_Config_4 Register |          |  |  |  |  |  |  |

|-----------------------------------|----------|--|--|--|--|--|--|

| 7 6 5 4 3 2 1 0                   |          |  |  |  |  |  |  |

|                                   | RESERVED |  |  |  |  |  |  |

| R-0h                              |          |  |  |  |  |  |  |

# Table 2-11. Dev\_Config\_4 Register Field Descriptions

| Bit | Field    | Туре | Reset | Description |

|-----|----------|------|-------|-------------|

| 7-0 | RESERVED | R    | 0h    | Reserved    |

# 2.3.6 Dev\_Config\_5 Register (Offset = 6h) [Reset = 00h]

Dev\_Config\_5 is shown in Figure 2-7 and described in Table 2-12.

Return to the Summary Table.

# Figure 2-7. Dev\_Config\_5 Register

|      |      | U    |   | <u> </u> |          |          |          |

|------|------|------|---|----------|----------|----------|----------|

| 7    | 6    | 5    | 4 | 3        | 2        | 1        | 0        |

|      | RESE | RVED |   | exp_en_3 | exp_en_2 | exp_en_1 | exp_en_0 |

| R-0h |      |      |   | R/W-0h   | R/W-0h   | R/W-0h   | R/W-0h   |

# Table 2-12. Dev\_Config\_5 Register Field Descriptions

| Dit | E. L.    |      | Direct |                                                                                                                                                   |

|-----|----------|------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit | Field    | Туре | Reset  | Description                                                                                                                                       |

| 7-4 | RESERVED | R    | 0h     | Reserved                                                                                                                                          |

| 3   | exp_en_3 | R/W  | 0h     | LED_3 exponential dimming enable; 0h =<br>Disabled, LED PWM dimming with linear<br>curve; 1h = Enabled, LED PWM dimming with<br>exponential curve |

| 2   | exp_en_2 | R/W  | 0h     | LED_2 exponential dimming enable; 0h =<br>Disabled, LED PWM dimming with linear<br>curve; 1h = Enabled, LED PWM dimming with<br>exponential curve |

| 1   | exp_en_1 | R/W  | 0h     | LED_1 exponential dimming enable; 0h =<br>Disabled, LED PWM dimming with linear<br>curve; 1h = Enabled, LED PWM dimming with<br>exponential curve |

| 0   | exp_en_0 | R/W  | 0h     | LED_0 exponential dimming enable; 0h =<br>Disabled, LED PWM dimming with linear<br>curve; 1h = Enabled, LED PWM dimming with<br>exponential curve |

# 2.3.7 Dev\_Config\_6 Register (Offset = 7h) [Reset = 00h]

Dev\_Config\_6 is shown in Figure 2-8 and described in Table 2-13.

Return to the Summary Table.

# Figure 2-8. Dev\_Config\_6 Register 7 6 5 4 3 2 1 0 RESERVED

# Figure 2-8. Dev\_Config\_6 Register (continued)

| Table 2-13 | . Dev | Config | 6 Regist | er Field | Descriptions |

|------------|-------|--------|----------|----------|--------------|

|------------|-------|--------|----------|----------|--------------|

| Bit | Field    | Туре | Reset | Description |

|-----|----------|------|-------|-------------|

| 7-0 | RESERVED | R    | 0h    | Reserved    |

# 2.3.8 Dev\_Config\_7 Register (Offset = 8h) [Reset = 00h]

Dev\_Config\_7 is shown in Figure 2-9 and described in Table 2-14.

Return to the Summary Table.

| Figure | 2-9. | Dev | Config | 7 | Register |

|--------|------|-----|--------|---|----------|

|--------|------|-----|--------|---|----------|

| 7      | 6             | 5 | 4       | 3      | 2       | 1       | 0       |

|--------|---------------|---|---------|--------|---------|---------|---------|

| phase_ | phase_align_3 |   | align_2 | phase_ | align_1 | phase_a | ilign_0 |

| R/V    | R/W-0h R/W-0h |   | R/W     | /-0h   | R/W-    | -0h     |         |

# Table 2-14. Dev\_Config\_7 Register Field Descriptions

| Bit | Field         | Туре | Reset | Description                                                                                                        |  |  |  |

|-----|---------------|------|-------|--------------------------------------------------------------------------------------------------------------------|--|--|--|

| 7-6 | phase_align_3 | R/W  | 0h    | LED_3 PWM phase align method; 0h = Forward<br>align; 1h = Forward align; 2h = Middle align; 3h =<br>Backward align |  |  |  |

| 5-4 | phase_align_2 | R/W  | 0h    | LED_2 PWM phase align method; 0h = Forward<br>align; 1h = Forward align; 2h = Middle align; 3h =<br>Backward align |  |  |  |

| 3-2 | phase_align_1 | R/W  | 0h    | LED_1 PWM phase align method; 0h = Forward<br>align; 1h = Forward align; 2h = Middle align; 3h =<br>Backward align |  |  |  |

| 1-0 | phase_align_0 | R/W  | 0h    | LED_0 PWM phase align method; 0h = Forward<br>align; 1h = Forward align; 2h = Middle align; 3h =<br>Backward align |  |  |  |

# 2.3.9 Dev\_Config\_8 Register (Offset = 9h) [Reset = 00h]

Dev\_Config\_8 is shown in Figure 2-10 and described in Table 2-15.

Return to the Summary Table.

# Figure 2-10. Dev\_Config\_8 Register

| 7        | 6 | 5 | 4   | 3  | 2 | 1 | 0 |

|----------|---|---|-----|----|---|---|---|

| RESERVED |   |   |     |    |   |   |   |

|          |   |   | R-( | 0h |   |   |   |

## Table 2-15. Dev\_Config\_8 Register Field Descriptions

| Bit | Field    | Туре | Reset | Description |

|-----|----------|------|-------|-------------|

| 7-0 | RESERVED | R    | 0h    | Reserved    |

# 2.3.10 Dev\_Config\_9 Register (Offset = Ah) [Reset = 00h]

Dev\_Config\_9 is shown in Figure 2-11 and described in Table 2-16.

Return to the Summary Table.

# Figure 2-11. Dev\_Config\_9 Register

|   |   | • | _ | <u> </u> | 0 |   |   |

|---|---|---|---|----------|---|---|---|

| 7 | 6 | 5 | 4 | 3        | 2 | 1 | 0 |

|   |   |   |   |          |   |   |   |

# Figure 2-11. Dev\_Config\_9 Register (continued)

RESERVED

R-0h

| Table 2-16. | Dev_Config_9 | <b>Register Field D</b> | Descriptions |

|-------------|--------------|-------------------------|--------------|

|             |              |                         |              |

| Bit | Field    | Туре | Reset | Description |

|-----|----------|------|-------|-------------|

| 7-0 | RESERVED | R    | 0h    | Reserved    |

# 2.3.11 Dev\_Config\_10 Register (Offset = Bh) [Reset = 00h]

Dev\_Config\_10 is shown in Figure 2-12 and described in Table 2-17.

Return to the Summary Table.

# Figure 2-12. Dev\_Config\_10 Register

| 7 | 6        | 5 | 4 | 3 | 2 | 1 | 0 |  |

|---|----------|---|---|---|---|---|---|--|

|   | RESERVED |   |   |   |   |   |   |  |

|   | R-0h     |   |   |   |   |   |   |  |

# Table 2-17. Dev\_Config\_10 Register Field Descriptions

| Bit | Field    | Туре | Reset | Description |

|-----|----------|------|-------|-------------|

| 7-0 | RESERVED | R    | 0h    | Reserved    |

# 2.3.12 Dev\_Config\_11 Register (Offset = Ch) [Reset = 00h]

Dev\_Config\_11 is shown in Figure 2-13 and described in Table 2-18.

Return to the Summary Table.

## Figure 2-13. Dev\_Config\_11 Register

| 7        | 6 | 5 | 4 | 3            | 2      | 1    | 0 |

|----------|---|---|---|--------------|--------|------|---|

| RESERVED |   |   |   | vsync_out_en | blank_ | time |   |

| R-0h     |   |   |   | R/W-0h       | R/W-   | -0h  |   |

# Table 2-18. Dev\_Config\_11 Register Field Descriptions

| Bit | Field        | Туре | Reset | Description                                                                                        |

|-----|--------------|------|-------|----------------------------------------------------------------------------------------------------|

| 7-3 | RESERVED     | R    | 0h    | Reserved                                                                                           |

| 2   | vsync_out_en | R/W  | 0h    | Vsync used as output to export internal oscilator clock; 0h = Vsync is input; 1h = Vsync is output |

| 1-0 | blank_time   | R/W  | 0h    | Line change time; 0h = 1us; 1h = 1.3us; 2h = 1.7us; 3h = 2us                                       |

# 2.3.13 Dev\_Config\_12 Register (Offset = Dh) [Reset = 08h]

Dev\_Config\_12 is shown in Figure 2-14 and described in Table 2-19.

Return to the Summary Table.

|          |   | -         |           | <u>v</u> = | •          |          |       |

|----------|---|-----------|-----------|------------|------------|----------|-------|

| 7        | 6 | 5         | 4         | 3          | 2          | 1        | 0     |

| vmid_sel |   | clamp_sel | clamp_dis | lod_action | Isd_action | lsd_thre | shold |

| R/W-0h   |   | R/W-0h    | R/W-0h    | R/W-1h     | R/W-0h     | R/W-     | 0h    |

Register Maps

|     | Table 2-19. Dev_Config_12 Register Field Descriptions |      |       |                                                                                                                                   |  |  |  |  |  |

|-----|-------------------------------------------------------|------|-------|-----------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Bit | Field                                                 | Туре | Reset | Description                                                                                                                       |  |  |  |  |  |

| 7-6 | vmid_sel                                              | R/W  | Oh    | Clamp voltage selection; 0h = VOUT-1.1V; 1h = VOUT-1.3V; 2h = VOUT-1.5V; 3h = VOUT-1.7V                                           |  |  |  |  |  |

| 5   | clamp_sel                                             | R/W  | 0h    | Clamp behavior selection; 0h = Clamp the OUTs<br>only during line change time; 1h = Clamp the<br>OUTs once current sink turns off |  |  |  |  |  |

| 4   | clamp_dis                                             | R/W  | Oh    | Clamp behavior disable; 0h = Enale clamp; 1h = Disable clamp                                                                      |  |  |  |  |  |

| 3   | lod_action                                            | R/W  | 1h    | Action when LED open fault happens; 0h = No<br>action; 1h = Shutdown current sink                                                 |  |  |  |  |  |

| 2   | lsd_action                                            | R/W  | Oh    | Action when LED short fault happens; 0h = No action; 1h = All OUTs shut down                                                      |  |  |  |  |  |

| 1-0 | lsd_threshold                                         | R/W  | Oh    | LSD threshold; 0h = 0.35 * VOUT; 1h = 0.45 *<br>VOUT; 2h = 0.55 * VOUT; 3h = 0.65 * VOUT                                          |  |  |  |  |  |

# Table 2-19. Dev\_Config\_12 Register Field Descriptions

# 2.4 Command Registers

Table 2-20 lists the memory-mapped registers for the Command registers. All register offset addresses not listed in Table 2-20 should be considered as reserved locations and the register contents should not be modified.

| Offset | Acronym      | Register Name                         | Section |  |  |  |  |  |  |

|--------|--------------|---------------------------------------|---------|--|--|--|--|--|--|

| 10h    | CMD_Update   | Configuration update command          | Go      |  |  |  |  |  |  |

| 11h    | CMD_Start    | Autonomous animation start command    | Go      |  |  |  |  |  |  |

| 12h    | CMD_Stop     | Autonomous animation stop command     | Go      |  |  |  |  |  |  |

| 13h    | CMD_Pause    | Autonomous animation pause command    | Go      |  |  |  |  |  |  |

| 14h    | CMD_Continue | Autonomous animation continue command | Go      |  |  |  |  |  |  |

|        |              |                                       |         |  |  |  |  |  |  |

# Table 2-20. COMMAND Registers

Complex bit access types are encoded to fit into small table cells. Table 2-21 shows the codes that are used for access types in this section.

| ···· / · ··· //·· //·· |                        |                                        |  |  |  |  |  |

|------------------------|------------------------|----------------------------------------|--|--|--|--|--|

| Access Type            | Code                   | Description                            |  |  |  |  |  |

| Write Type             |                        |                                        |  |  |  |  |  |

| W1C                    | W<br>1C                | Write<br>1 to clear                    |  |  |  |  |  |

| Reset or Default       | Reset or Default Value |                                        |  |  |  |  |  |

| -n                     |                        | Value after reset or the default value |  |  |  |  |  |

# Table 2-21. Command Access Type Codes

# 2.4.1 CMD\_Update Register (Offset = 10h) [Reset = 00h]

CMD\_Update is shown in Figure 2-15 and described in Table 2-22.

Return to the Summary Table.

| Figure 2-15. CMD_Update Register |  |  |  |  |  |  |  |  |  |  |

|----------------------------------|--|--|--|--|--|--|--|--|--|--|

| 7 6 5 4 3 2 1 0                  |  |  |  |  |  |  |  |  |  |  |

| update_cmd                       |  |  |  |  |  |  |  |  |  |  |

| W1C-0h                           |  |  |  |  |  |  |  |  |  |  |

|                                  |  |  |  |  |  |  |  |  |  |  |

AND Hadets Deside

|     | Table 2-22. CMD_Update Register Field Descriptions |      |       |                                                                                                                                                        |  |  |  |  |

|-----|----------------------------------------------------|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Bit | Field                                              | Туре | Reset | Description                                                                                                                                            |  |  |  |  |

| 7-0 | update_cmd                                         | W1C  |       | Configuration update command: registers001h<br>to 00Bh will <b>ONLY</b> be effective by sending this<br>command; <b>Write 55h to send this command</b> |  |  |  |  |

#### ... .....

# 2.4.2 CMD\_Start Register (Offset = 11h) [Reset = 00h]

CMD\_Start is shown in Figure 2-16 and described in Table 2-23.

Return to the Summary Table.

| 7         | 6      | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-----------|--------|---|---|---|---|---|---|--|--|

| start_cmd |        |   |   |   |   |   |   |  |  |

|           | W1C-0h |   |   |   |   |   |   |  |  |

# Table 2-23. CMD\_Start Register Field Descriptions

| Bit | Field     | Туре | Reset | Description                                                                                                                           |

|-----|-----------|------|-------|---------------------------------------------------------------------------------------------------------------------------------------|

| 7-0 | start_cmd | W1C  |       | Send start_command to start autonomous<br>control or restart with the latest setting; <b>Write</b><br><b>FFh to send this command</b> |

# 2.4.3 CMD\_Stop Register (Offset = 12h) [Reset = 00h]

CMD\_Stop is shown in Figure 2-17 and described in Table 2-24.

Return to the Summary Table.

# Figure 2-17. CMD Stop Register

|          |        | v |   | U |   |   |   |  |

|----------|--------|---|---|---|---|---|---|--|

| 7        | 6      | 5 | 4 | 3 | 2 | 1 | 0 |  |

| stop_cmd |        |   |   |   |   |   |   |  |

|          | W1C-0h |   |   |   |   |   |   |  |

## Table 2-24, CMD Stop Register Field Descriptions

| Bit | Field    | Туре | Reset | Description                                                                                             |

|-----|----------|------|-------|---------------------------------------------------------------------------------------------------------|

| 7-0 | stop_cmd | W1C  |       | Stop LED current status immediately, and go<br>back to INITIAL state; Write AAh to send this<br>command |

# 2.4.4 CMD\_Pause Register (Offset = 13h) [Reset = 00h]

CMD\_Pause is shown in Figure 2-18 and described in Table 2-25.

Return to the Summary Table.

# Figure 2-18. CMD\_Pause Register

| 7         | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-----------|---|---|---|---|---|---|---|--|--|

| pause_cmd |   |   |   |   |   |   |   |  |  |

| W1C-0h    |   |   |   |   |   |   |   |  |  |

|     | Table 2-25. CMD_Pause Register Field Descriptions |      |       |                                                                                                                                                                                                                      |  |  |  |  |

|-----|---------------------------------------------------|------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Bit | Field                                             | Туре | Reset | Description                                                                                                                                                                                                          |  |  |  |  |

| 7-0 | pause_cmd                                         | W1C  | 0h    | Pause autonomous control at the current state,<br>keep Internal sloper register unchanged, but<br>the scan keeps going-on using the previous<br>calculated pwm data; <b>Write 33h to send this</b><br><b>command</b> |  |  |  |  |

# Table 2-25. CMD\_Pause Register Field Descriptions

# 2.4.5 CMD\_Continue Register (Offset = 14h) [Reset = 00h]

CMD\_Continue is shown in Figure 2-19 and described in Table 2-26.

Return to the Summary Table.

# Figure 2-19. CMD\_Continue Register

|              |        | • |   |   | • |   |   |  |  |

|--------------|--------|---|---|---|---|---|---|--|--|

| 7            | 6      | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

| continue_cmd |        |   |   |   |   |   |   |  |  |

|              | W1C-0h |   |   |   |   |   |   |  |  |

# Table 2-26. CMD\_Continue Register Field Descriptions

| Bit | Field        | Туре | Reset | Description                                                 |

|-----|--------------|------|-------|-------------------------------------------------------------|

| 7-0 | continue_cmd | W1C  |       | Continue autonomous control; Write CCh to send this command |

# 2.5 LED\_Enable Registers

Table 2-27 lists the memory-mapped registers for the LED\_Enable registers. All register offset addresses not listed in Table 2-27 should be considered as reserved locations and the register contents should not be modified.

# Table 2-27. LED\_ENABLE Registers

| Offs | et Acronym | Register Name                     | Section |

|------|------------|-----------------------------------|---------|

| 20ł  | LED_EN_1   | Enable the LEDs of LED_0 to LED_3 | Go      |

Complex bit access types are encoded to fit into small table cells. Table 2-28 shows the codes that are used for access types in this section.

# Table 2-28. LED\_Enable Access Type Codes

|                  | _                      | 51                                     |  |  |  |  |

|------------------|------------------------|----------------------------------------|--|--|--|--|

| Access Type      | Code                   | Description                            |  |  |  |  |

| Read Type        |                        |                                        |  |  |  |  |

| R                | R                      | Read                                   |  |  |  |  |

| Write Type       |                        |                                        |  |  |  |  |

| W                | W                      | Write                                  |  |  |  |  |

| Reset or Default | Reset or Default Value |                                        |  |  |  |  |

| -n               |                        | Value after reset or the default value |  |  |  |  |

# 2.5.1 LED\_EN\_1 Register (Offset = 20h) [Reset = 00h]

LED\_EN\_1 is shown in Figure 2-20 and described in Table 2-29.

Return to the Summary Table.

# Figure 2-20. LED\_EN\_1 Register

| 7        | 6 | 5 | 4        | 3        | 2        | 1        | 0 |  |

|----------|---|---|----------|----------|----------|----------|---|--|

| RESERVED |   |   | led_en_3 | led_en_2 | led_en_1 | led_en_0 |   |  |

22 LP5810 4-Channel RGBW LED Driver Register Map

|     | R-0h                                             |      |       | R/W-0h       | R/W-0h             | R/W-0h      |  |  |  |

|-----|--------------------------------------------------|------|-------|--------------|--------------------|-------------|--|--|--|

|     | Table 2-29. LED_EN_1 Register Field Descriptions |      |       |              |                    |             |  |  |  |

| Bit | Field                                            | Туре | Reset | Description  |                    |             |  |  |  |

| 7-4 | RESERVED                                         | R    | 0h    | Reserved     |                    |             |  |  |  |

| 3   | led_en_3                                         | R/W  | 0h    | LED_3 Enable | ; 0h = Disabled; 1 | h = Enabled |  |  |  |

| 2   | led_en_2                                         | R/W  | 0h    | LED_2 Enable | ; 0h = Disabled; 1 | h = Enabled |  |  |  |

| 1   | led_en_1                                         | R/W  | 0h    | LED_1 Enable | ; 0h = Disabled; 1 | h = Enabled |  |  |  |

| 0   | led_en_0                                         | R/W  | 0h    | LED_0 Enable | ; 0h = Disabled; 1 | h = Enabled |  |  |  |

Figure 2-20. LED\_EN\_1 Register (continued)

# 2.6 Fault\_Clear Registers

Table 2-30 lists the memory-mapped registers for the Fault\_Clear registers. All register offset addresses not listed in Table 2-30 should be considered as reserved locations and the register contents should not be modified.

| Table 2-30. FAULT_CLEAR Registers |             |                             |         |  |  |

|-----------------------------------|-------------|-----------------------------|---------|--|--|

| Offset                            | Acronym     | Register Name               | Section |  |  |

| 22h                               | Fault_Clear | Clear the LOD/LSD/TSD flats | Go      |  |  |

Complex bit access types are encoded to fit into small table cells. Table 2-31 shows the codes that are used for access types in this section.

| Table 2-31. Taut_Olear Access Type Codes |                        |                                        |  |  |  |  |

|------------------------------------------|------------------------|----------------------------------------|--|--|--|--|

| Access Type                              | Code                   | Description                            |  |  |  |  |

| Read Type                                |                        |                                        |  |  |  |  |

| R R                                      |                        | Read                                   |  |  |  |  |

| Write Type                               |                        |                                        |  |  |  |  |

| W                                        | W                      | Write                                  |  |  |  |  |

| W1C                                      | W<br>1C                | Write<br>1 to clear                    |  |  |  |  |

| Reset or Default                         | Reset or Default Value |                                        |  |  |  |  |

| -n                                       |                        | Value after reset or the default value |  |  |  |  |

# Table 2-31, Fault Clear Access Type Codes

# 2.6.1 Fault\_Clear Register (Offset = 22h) [Reset = 00h]

Fault\_Clear is shown in Figure 2-21 and described in Table 2-32.

Return to the Summary Table.

| Figure | 2-21. | Fault | Clear | Register |

|--------|-------|-------|-------|----------|

|        |       |       |       |          |

| 7        | 6 | 5    | 4 | 3 | 2         | 1         | 0         |

|----------|---|------|---|---|-----------|-----------|-----------|

| RESERVED |   |      |   |   | tsd_clear | lsd_clear | lod_clear |

|          |   | R-0h |   |   | W1C-0h    | W1C-0h    | W1C-0h    |

| Table 2-32. Fault_Clear Register Field Descriptions |           |      |       |                                                          |  |  |  |

|-----------------------------------------------------|-----------|------|-------|----------------------------------------------------------|--|--|--|

| Bit                                                 | Field     | Туре | Reset | Description                                              |  |  |  |

| 7-3                                                 | RESERVED  | R    | 0h    | Reserved                                                 |  |  |  |

| 2                                                   | tsd_clear | W1C  | 0h    | TSD Fault Status Clear; Write 1 to clear and read back 0 |  |  |  |

| 1                                                   | lsd_clear | W1C  | 0h    | LSD Fault Status Clear; Write 1 to clear and read back 0 |  |  |  |

# Table 2-32 Fault Clear Register Field Descriptions

| Table 2-32. Fault | Clear Register | Field Descri | ntions | (continued) | <b>`</b> |

|-------------------|----------------|--------------|--------|-------------|----------|

| Table 2-32. Fault | Clear Register | FIEID Desch  | JUDIIS | (continueu) | ,        |

| Bit | Field     | Туре | Reset | Description                                              |

|-----|-----------|------|-------|----------------------------------------------------------|

| 0   | lod_clear | W1C  | 0h    | LOD Fault Status Clear; Write 1 to clear and read back 0 |

# 2.7 Reset Registers

Table 2-33 lists the memory-mapped registers for the Reset registers. All register offset addresses not listed in

Table 2-33 should be considered as reserved locations and the register contents should not be modified.

# Table 2-33. RESET Registers

| Offset | Acronym | Register Name  | Section |

|--------|---------|----------------|---------|

| 23h    | Reset   | Software reset | Go      |

Complex bit access types are encoded to fit into small table cells. Table 2-34 shows the codes that are used for access types in this section.

| Access Type      | Code    | Description                            |  |  |  |  |  |

|------------------|---------|----------------------------------------|--|--|--|--|--|

| Write Type       |         |                                        |  |  |  |  |  |

| W1C              | W<br>1C | Write<br>1 to clear                    |  |  |  |  |  |

| Reset or Default | Value   |                                        |  |  |  |  |  |

| -n               |         | Value after reset or the default value |  |  |  |  |  |

# Table 2-34. Reset Access Type Codes

# 2.7.1 Reset Register (Offset = 23h) [Reset = 00h]