# Jacinto7 AM6x, TDA4x, and DRA8x High-Speed Interface **Design Guidelines**

Embedded Processor Applications

#### **ABSTRACT**

As modern bus interface frequencies scale higher, care must be taken in the design and printed circuit board (PCB) layout phase to help provide a robust design.

### **Table of Contents**

| 1 Introduction                                                             | 3  |

|----------------------------------------------------------------------------|----|

| 1.1 Overview                                                               | 3  |

| 1.2 Supporting Documentation                                               | 3  |

| 2 High-Speed Interface Design Guidance                                     | 4  |

| 2.1 Trace Impedance                                                        | 4  |

| 2.2 Trace Lengths                                                          | 4  |

| 2.3 Differential Signal Length Matching                                    | 4  |

| 2.4 Signal Reference Planes                                                |    |

| 2.5 Differential Signal Spacing                                            | 7  |

| 2.6 Additional Differential Signal Rules                                   | 8  |

| 2.7 Symmetry in the Differential Pairs                                     |    |

| 2.8 Connectors and Receptacles                                             |    |

| 2.9 Via Discontinuity Mitigation                                           | 10 |

| 2.10 Back-Drill Via Stubs                                                  | 11 |

| 2.11 Via Anti-Pad Diameter                                                 |    |

| 2.12 Equalize Via Count                                                    | 11 |

| 2.13 Surface-Mount Device Pad Discontinuity Mitigation                     | 12 |

| 2.14 Signal Bending                                                        |    |

| 2.15 ESD and EMI Considerations                                            |    |

| 2.16 ESD and EMI Layout Rules                                              |    |

| 3 Interface-Specific Design Guidance                                       |    |

| 3.1 USB Board Design and Layout Guidelines                                 |    |

| 3.2 DisplayPort Board Design and Layout Guidelines                         |    |

| 3.3 PCIe Board Design and Layout Guidelines                                |    |

| 3.4 MIPI <sup>®</sup> D-PHY (CSI2, DSI) Board Design and Layout Guidelines |    |

| 3.5 UFS Board Design and Layout Guidelines                                 | 25 |

| 3.6 Q/SGMII Board Design and Layout Guidelines                             |    |

| 4 Board Design Simulations                                                 |    |

| 4.1 Board Model Extraction                                                 |    |

| 4.2 Board-Model Validation                                                 |    |

| 4.3 S-Parameter Inspection                                                 |    |

| 4.4 Time Domain Reflectometry (TDR) Analysis                               |    |

| 4.5 Simulation Integrity Analysis                                          |    |

| 4.6 Reviewing Simulation Results                                           |    |

| 5 References                                                               |    |

| 6 Revision History                                                         | 32 |

### Trademarks www.ti.com

## **List of Figures**

| Figure 2-1. Differential Pair Length Matching                         |                 |

|-----------------------------------------------------------------------|-----------------|

| Figure 2-2. Incorrect Plane Void Routing                              | 5               |

| Figure 2-3. Correct Plane Void Routing                                | 5               |

| Figure 2-4. Incorrect Plane-Split Signal Routing                      | 6               |

| Figure 2-5. Stitching Capacitor Placement                             |                 |

| Figure 2-6. Overlapped Planes                                         |                 |

| Figure 2-7. Stitching Vias                                            |                 |

| Figure 2-8. Example of Differential Pair Spacing                      |                 |

| Figure 2-9. Differential Pair Symmetry                                |                 |

| Figure 2-10. USB Through-Hole Receptacle Connection                   | 9               |

| Figure 2-11. Via Length (Long Stub)                                   | 10              |

| Figure 2-12. Via Length (Short Stub)                                  | 10              |

| Figure 2-13. Example of Via Anti-Pad                                  | 11              |

| Figure 2-14. AC-Coupling Placement                                    | 12              |

| Figure 2-15. Reference Plane Voiding of Surface-Mount Devices         |                 |

| Figure 2-16. Signal Bending Rules                                     | 13              |

| Figure 2-17. Flow-Through Routing                                     | 14              |

| Figure 3-1. USB Interface High-Level Schematic                        | 15              |

| Figure 3-2. USB 3.1 Super Speed Placement Diagram                     |                 |

| Figure 3-3. USB 3.1 Example "carve GND" Layout                        | 18              |

| Figure 3-4. DisplayPort Interface High Level Schematic                |                 |

| Figure 3-5. DisplayPort Placement                                     | 19              |

| Figure 3-6. Example "carve GND" Layout                                |                 |

| Figure 3-7. PCIe Interface High Level Schematic                       | 21              |

| Figure 3-8. CSI-2 <sup>®</sup> High-Level Schematic                   |                 |

| Figure 3-9. DSI High-Level Schematic                                  |                 |

| Figure 3-10. UFS Interface High Level Schematic                       |                 |

| Figure 3-11. SGMII Interface High Level Schematic                     |                 |

| Figure 4-1. TDR Plot Example With Impedance Mismatch                  |                 |

| Figure 4-2. Signal Integrity Analysis Setup - Channel Simulation      |                 |

| Figure 4-3. Bathtub Curve Overlay                                     | 31              |

| List of Tables                                                        |                 |

| List of Tables  Table 3-1. USB AC Coupling Capacitors Requirements    | 16              |

| Table 3-2. USB Component Reference                                    |                 |

| Table 3-3. USB3.1 (Super Speed) Routing Specifications                | 17              |

| Table 3-4. USB2.0 Routing Specifications                              |                 |

| Table 3-5. DP AC Coupling Capacitors Requirements                     |                 |

| Table 3-6. DP Component Reference                                     |                 |

| Table 3-7. DP Routing Specifications                                  |                 |

| Table 3-8. REFCLKP, REFCLKN Requirements in External LVDS REFCLK Mode |                 |

| Table 3-9. REFCLKP, REFCLKN Requirements in Output REFCLK Mode        |                 |

| Table 3-10. PCIe AC Coupling Capacitors Requirements                  |                 |

| Table 3-11. PCI-E Routing Specifications                              |                 |

| Table 3-12. PCI-E Routing Specifications                              |                 |

| Table 3-13. UFS Routing Specifications                                |                 |

| Table 3-14. Q/SGMII AC Coupling Capacitors Requirements               |                 |

| Table 3-15. G/SGMII Routing Specifications                            | <mark>28</mark> |

| Table 4-1. Eye Mask Specifications for Different Standards            | 31              |

## **Trademarks**

CSI-2®, DSI®, and MIPI® are registered trademarks of MIPI Alliance.

All trademarks are the property of their respective owners.

www.ti.com Introduction

### 1 Introduction

### 1.1 Overview

This application report can help system designers understand PCB layout options and best practices when designing platforms with high-speed interfaces. This document is intended for audiences familiar with PCB manufacturing, layout, and design.

### 1.2 Supporting Documentation

This document supports the following devices:

- J7200

- DRA821

- J721E

- TDA4VM

- DRA829

- J721S2

- AM68x

- TDA4VE

- TDA4AL

- TDA4VL

- J722S

- AM67x

- TDA4VEN

- TDA4AEN

- J742S2

- TDA4VPE

- TDA4APE

- J784S4

- AM69x

- TDA4VH

- TDA4AH

- TDA4VP

- TDA4AP

For AM6x parts not listed (for example, AM644x, AM62x), see the application notes provided on those product pages, for example: *High-Speed Interface Layout Guidelines*.

## 2 High-Speed Interface Design Guidance

A primary concern when designing a system is accommodating and isolating high-speed signals. As high-speed signals are most likely to impact or be impacted by other signals, the signals must be laid out early in the PCB design process to make sure that prescribed routing rules can be followed.

#### 2.1 Trace Impedance

High-speed signals trace impedance needs to designed to minimize the reflections in traces. The high speed protocol that is being designed for determines what the single and differential trace Impedance the traces need to meet as well as the tolerance for the impedance (50  $\Omega$  ±15%). To have designs be robust from PCB manufacturing errors and defects design the traces impedance be as close to the recommended value. The geometry of the traces, the permittivity of the PCB material and the layers surrounding the trace all impact the impedance of the signal trace.

In general, closely coupled differential signal traces are not an advantage on PCBs. When differential signals are closely coupled, tight spacing and width control is necessary. Very small width and spacing variations affect impedance dramatically, so tight impedance control can be more problematic to maintain in production. For PCBs with very tight space limitations (which are usually small) this can work, but for most PCBs, the loosely coupled option is probably best.

Loosely coupled PCB differential signals make impedance control much easier. Wider traces and spacing make obstacle avoidance easier (because each trace is not so fixed in position relative to the other), and trace width variations do not affect impedance as much, therefore, it is easier to maintain an accurate impedance over the length of the signal. For longer routes, the wider traces also show reduced skin effect and often result in better signal integrity with a larger eye diagram opening.

#### 2.2 Trace Lengths

As with all high-speed signals, keep total trace length for signal pairs to a minimum. For trace length requirements for each protocol and device, see later sections in this document.

### 2.3 Differential Signal Length Matching

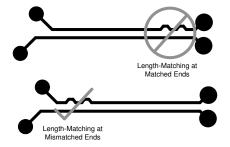

Match the etch lengths of the relevant differential pair traces. Intra-pair skew is the term used to define the difference between the etch length of the + and – lane of a differential pair. Inter-pair skew is used to describe the difference between the etch lengths of a differential pair from another differential pair of the same group. The etch length of the differential pair groups do not need to match. For example the etch lengths of USB 3.0 TX and RX do not need to match. There are also standards that do not have a Interpair skew requirement because the different lanes do not have to be the same length. When matching the intra-pair skew of the high-speed signals, add serpentine routing to match the lengths as close to the mismatched ends as possible, see Figure 2-1.

Figure 2-1. Differential Pair Length Matching

#### 2.4 Signal Reference Planes

An electrical circuit must always be a closed loop system. With DC, the return current takes the way back with the lowest resistance for DC signals. At higher frequencies, the return current flows along the lowest impedance path, this lowest impedance path is usually the reference plane adjacent to the signal. For this reason it is always best to have a ground plane or power plane on the layer above or below a signal layer. This solid return path helps to reduce impedance changes and decrease EMI issues.

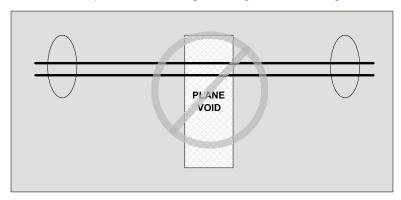

High-speed signals should be routed over a solid GND reference plane and not across a plane split or a void in the reference plane unless absolutely necessary. TI does not recommend high-speed signal references to power planes.

Routing across a plane split or a void in the reference plane forces return high-frequency current to flow around the split or void. This can result in the following conditions:

- · Excess radiated emissions from an unbalanced current flow

- · Delays in signal propagation delays due to increased series inductance

- · Interference with adjacent signals

- Degraded signal integrity (that is, more jitter and reduced signal amplitude)

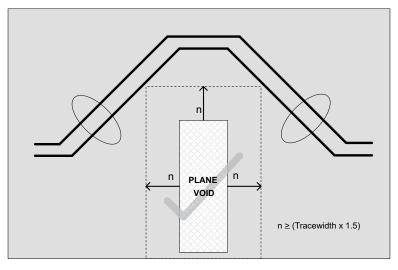

For examples of correct and incorrect plane void routing, see Figure 2-2 and Figure 2-3.

Figure 2-2. Incorrect Plane Void Routing

Figure 2-3. Correct Plane Void Routing

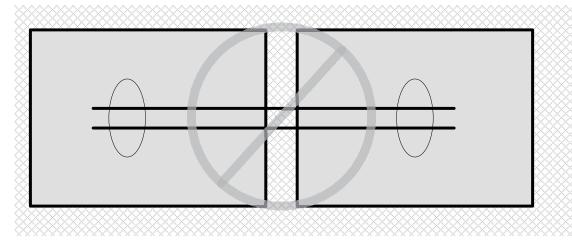

If routing over a plane-split is completely unavoidable, place stitching capacitors across the split to provide a return path for the high-frequency current. These stitching capacitors minimize the current loop area and any impedance discontinuity created by crossing the split. These capacitors should be 1µF or lower and placed as close as possible to the plane crossing. For examples of incorrect plane-split routing and correct stitch capacitor placement, see Figure 2-4 and Figure 2-5.

Figure 2-4. Incorrect Plane-Split Signal Routing

Figure 2-5. Stitching Capacitor Placement

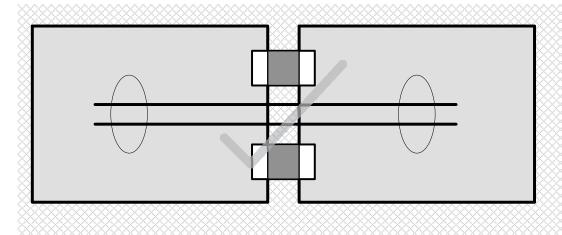

When planning a PCB stackup, make sure that planes that do not reference each other are not overlapped because this produces unwanted capacitance between the overlapping areas. To see an example of how this capacitance can pass RF emissions from one plane to the other, see Figure 2-6.

Figure 2-6. Overlapped Planes

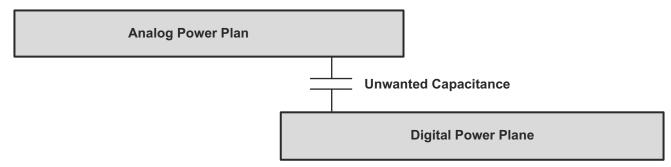

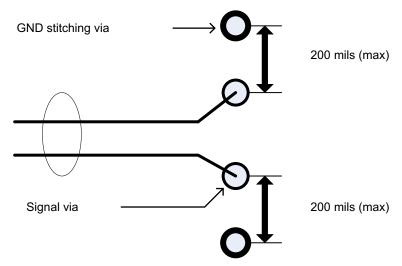

The entirety of any high-speed signal trace should maintain the same GND reference from origination to termination. If unable to maintain the same GND reference, via-stitch both GND planes together to provide continuous grounding and uniform impedance. Place these stitching vias symmetrically within 200mils (center-to-center, closer is better) of the signal transition vias. For an example of stitching vias, see Figure 2-7.

Figure 2-7. Stitching Vias

TI does not recommend high-speed signal references to power planes unless it is completely unavoidable. If it is unavoidable it is best to use AC coupling capacitors and ground vias to allow the return signal to have a path back from the sink to the source.

### 2.5 Differential Signal Spacing

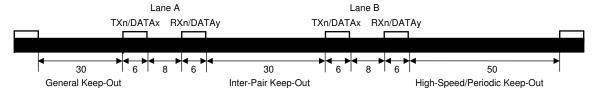

To minimize crosstalk in high-speed interface implementations, the spacing between the signal pairs must be a minimum of 5 times the width of the trace. This spacing is referred to as the 5W rule. A PCB design with a calculated trace width of 6mils requires a minimum of 30mils spacing between high-speed differential pairs. Also, maintain a minimum keep-out area of 30mils to any other signal throughout the length of the trace. Where the high-speed differential pairs abut a clock or a periodic signal, increase this keep-out to a minimum of 50mils to provide proper isolation. For examples of high-speed differential signal spacing, see Figure 2-8.

Figure 2-8. Example of Differential Pair Spacing

### 2.6 Additional Differential Signal Rules

- · Do not place probe or test points on any high-speed differential signal.

- Do not route high-speed traces under or near crystals, oscillators, clock signal generators, switching power regulators, mounting holes, magnetic devices, or ICs that use or duplicate clock signals.

- After BGA breakout, keep high-speed differential signals clear of the SoC because high current transients produced during internal state transitions can be difficult to filter out.

- When possible, route high-speed differential pair signals on the top or bottom layer of the PCB with an

adjacent GND layer. TI does not recommend stripline routing of the high-speed differential signals. (or

Stripline routing is recommended for all high-speed SerDes signals in the design. This provides better

controlled impedance. Also the signal quality degradation due to EMI is minimized by fabricating traces in

between ground planes).

- Make sure that high-speed differential signals are routed ≥ 90mils from the edge of the reference plane.

- Make sure that high-speed differential signals are routed at least 1.5W (calculated trace-width × 1.5) away from voids in the reference plane. This rule does not apply where SMD pads on high-speed differential signals are voided.

- Maintain constant trace width after the SoC BGA escape to avoid impedance mismatches in the transmission lines.

- Maximize differential pair-to-pair spacing when possible (loosely coupled).

### 2.7 Symmetry in the Differential Pairs

Route all high-speed differential pairs together symmetrically and parallel to each other. Deviating from this requirement occurs naturally during package escape and when routing to connector pins. These deviations must be as short as possible and package break-out must occur within 0.25 inches of the package.

Figure 2-9. Differential Pair Symmetry

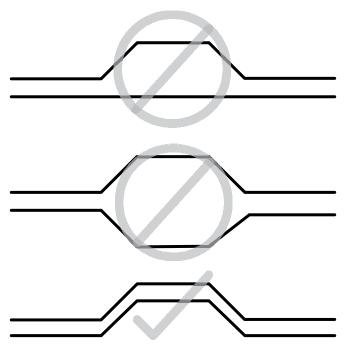

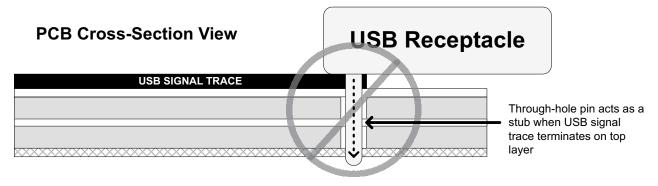

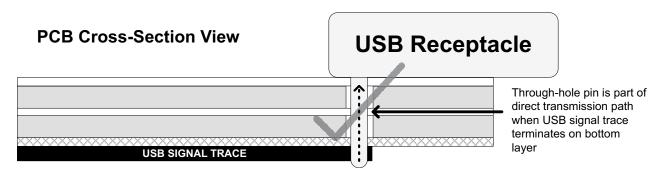

### 2.8 Connectors and Receptacles

When implementing a through-hole receptacle (like a USB Standard-A), TI recommends making high-speed differential signal connections to the receptacle on the bottom layer of the PCB. Making these connections on the bottom layer of the PCB prevents the through-hole pin from acting as a stub in the transmission path. For surface-mount receptacles such as USB Micro-B and Micro-AB, make high-speed differential signal connections on the top layer. Making these connections on the top layer eliminates the need for vias in the transmission path. For examples of USB through-hole receptacle connections, see Figure 2-10.

Figure 2-10. USB Through-Hole Receptacle Connection

### 2.9 Via Discontinuity Mitigation

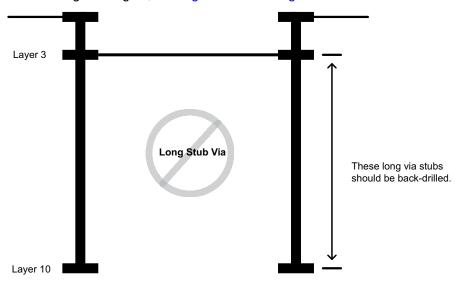

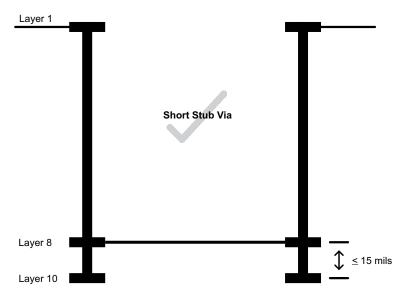

A via presents a short section of change in geometry to a trace and can appear as a capacitive discontinuity, an inductive discontinuity, or both. These discontinuities result in reflections and some degradation of a signal as the signal travels through the via. Reduce the overall via stub length to minimize the negative impacts of vias (and associated via stubs).

Because longer via stubs resonate at lower frequencies and increase insertion loss, keep these stubs as short as possible. In most cases, the stub portion of the via present significantly more signal degradation than the signal portion of the via. TI recommends keeping via stubs to less than 15mils. Longer stubs must be back-drilled.

For examples of short and long via lengths, see Figure 2-11 and Figure 2-12.

Figure 2-11. Via Length (Long Stub)

Figure 2-12. Via Length (Short Stub)

10

#### 2.10 Back-Drill Via Stubs

Back-drilling is a PCB manufacturing process in which the undesired conductive plating in the stub section of a via is removed. To back-drill, use a drill bit slightly larger in diameter than the drill bit used to create the original via hole. This requires the anti-pad diameter of the via to be increase to fit the drill size (for those layers that are to be removed), to make sure other trace or planes are not affected with via is drilled. When via transitions result in stubs longer than 15mils, back-drill the resulting stubs to reduce insertion losses and to make sure that they do not resonate.

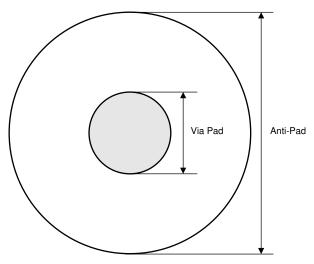

#### 2.11 Via Anti-Pad Diameter

Via transitions can be significant sources of impedance variation along the trace. The anti-pad size of the via across different layers also needs to be adjusted to make sure that the impedance is maintained at a uniform value. Too large an anti-pad leads to an inductive effect and a corresponding increase in the trace impedance, while too small an anti-pad similarly results in a capacitive effect and a dip in the overall trace impedance. The copper clearance, indicated by this anti-pad, must be met on all layers where the via exists, including both routing layer and plane layers. The traces connecting to the via barrel contain the only copper allowed in this area; non-functional or unconnected via pads are not permitted. For an example of a via anti-pad diameter, see Figure 2-13.

Figure 2-13. Example of Via Anti-Pad

### 2.12 Equalize Via Count

If using vias is necessary on a high-speed differential signal trace, make sure that the via count on each member of the differential pair is equal and that the vias are as equally spaced as possible. It is important to make sure that the different lanes that lengths need to match have the same amount of vias on the lines. Take into account the length of the vias when verifying parameters such as inter-pair skew.

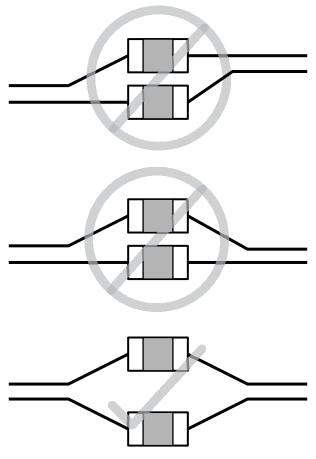

### 2.13 Surface-Mount Device Pad Discontinuity Mitigation

Avoid including surface-mount devices (SMDs) on high-speed signal traces because these devices introduce discontinuities that can negatively affect signal quality. When SMDs are required on the signal traces (for example, the USB SuperSpeed transmit AC coupling capacitors) the maximum permitted component size is 0603. TI strongly recommends using 0402 or smaller. Place these components symmetrically during the layout process to provide the best possible signal quality and to minimize reflection. For examples of correct and incorrect AC coupling capacitor placement, see Figure 2-14.

Figure 2-14. AC-Coupling Placement

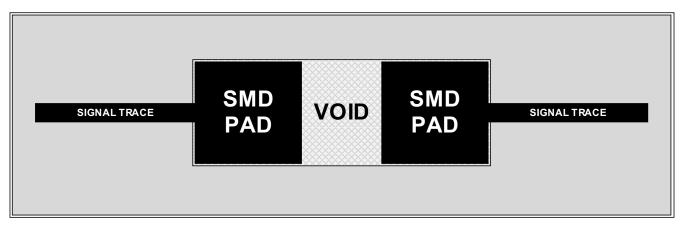

To minimize the discontinuities associated with the placement of these components on the differential signal traces, TI recommends voiding the SMD mounting pads of the reference plane by 100%. Make sure this void is at least two PCB layers deep. For an example of a reference plane voiding of surface mount devices, see Figure 2-15.

Figure 2-15. Reference Plane Voiding of Surface-Mount Devices

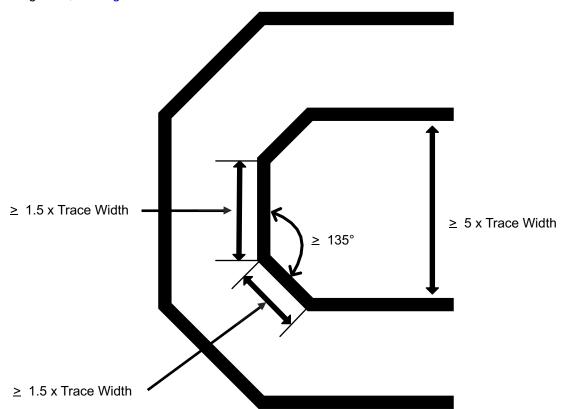

### 2.14 Signal Bending

Avoid the introduction of bends into high-speed differential signals. When bending is required, maintain a bend angle greater than 135° to make sure that the bend is as loose as a possible. For an example of high-speed signal bending rules, see Figure 2-16.

Figure 2-16. Signal Bending Rules

### 2.15 ESD and EMI Considerations

When choosing ESD and EMI components, TI recommends selecting devices that permit flow-through routing of the USB differential signal pair because these devices provide the cleanest routing. For example, the TI TPD4EUSB30 can be combined with the TI TPD2EUSB30 to provide flow-through ESD protection for both USB2 and USB3 differential signals without the need for bends in the signal pairs. For an example of flow-through routing, see Figure 2-17.

Figure 2-17. Flow-Through Routing

### 2.16 ESD and EMI Layout Rules

- Place ESD and EMI protection devices as close as possible to the connector.

- · Keep any unprotected traces away from protected traces to minimize EMI coupling.

- Incorporate 60% voids under the ESD and EMI component signal pads to reduce losses.

- Use 0402 0Ω resistors for common-mode filter (CMF) no-stuff options because larger components typically introduce more loss that the CMF.

- Place any required signal pair AC coupling capacitors on the protected side of the CMF and as close as possible to the CMF.

- If vias are needed to transition to the CMF layer, make sure that the vias are as close as possible to the CMF.

- Keep the overall routing of AC coupling capacitors + CMF + ESD protection as short and as close as possible to the connector.

### 3 Interface-Specific Design Guidance

There are many differences in the various high-speed standards that need to be taken into account when designing the layout of a system. These differences include parameters like data-rates and frequency, AC coupling capacitors, inter-pair skew, intra-pair skew and trace impedance. This chapter includes different sections for each of the different high-speed standards. These sections are to be used as guidelines and are not always exact values.

### 3.1 USB Board Design and Layout Guidelines

This section discusses guidelines when designing a universal serial bus (USB) system. USB interfaces are commonly used for both onboard and off-board communication, thus designs vary. This guide is not intended to cover all design possibilities, but to provide general recommendations. The design rules stated within this document are targeted at DEVICE mode electrical compliance. HOST mode, systems (or both) that do not include the 3m USB cable and far-end 11 inch PCB trace required by DEVICE mode compliance testing may not need the complete list of optimizations shown in this document; however, applying these optimizations to HOST mode systems leads to the best possible DEVICE mode performance.

The use of USB-compatible bridges and switches is allowed for interfacing with more than one other processor or USB device.

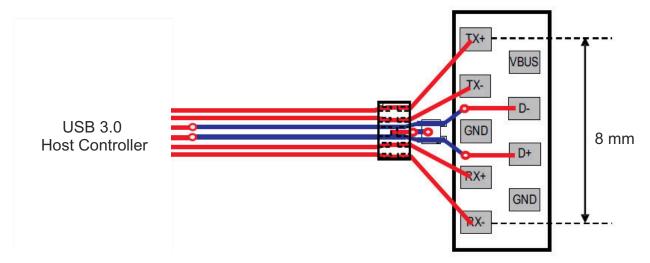

#### 3.1.1 USB Interface Schematic

The USB interface schematics vary, but general connectivity is straightforward and consistent between implementations. Figure 3-1 illustrates a USB interface supporting super speed. The USB interface of the device can include addition signals such as usb\_id, usb\_vbus, and usb\_drvvbus that are not discussed here. These signals are slow speed interfaces, and nothing special is required for PCB layout of these signals.

Figure 3-1. USB Interface High-Level Schematic

#### 3.1.1.1 Support Components

AC coupling capacitors are required on the transmit Super Speed data pairs. Table 3-1 shows the requirements for these capacitors.

Table 3-1. USB AC Coupling Capacitors Requirements

| Parameter                               | MIN | TYP  | MAX  | Unit        |

|-----------------------------------------|-----|------|------|-------------|

| PCIe AC coupling capacitor value        | 175 | 220  | 265  | nF          |

| PCIe AC coupling capacitor package size |     | 0402 | 0603 | EIA (1),(2) |

- (1) EIA LxW units, for example, a 0402 is a 40 × 20mils surface mount capacitor.

- (2) Design the physical size of the capacitor as small as practical. Use the same size on both lines in each pair placed side by side.

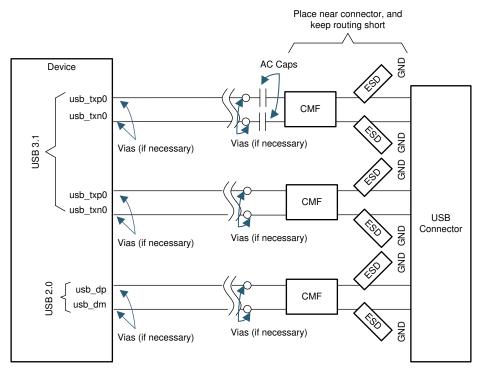

A typical USB interface may also common mode chokes for suppression of high-frequency noise. Because USB can interface to off-board peripherals, ESD protection is also included in the example.

Table 3-2. USB Component Reference

| Device | Supplier | Part Number   | Comment                   |

|--------|----------|---------------|---------------------------|

| ESD    | TI       | TDP1E05U06    | Minimize Capacitance      |

| CMF    | Murata   | DLW21SZ900HQ2 | Support Target Data Rates |

Figure 3-2 shows the placement diagram for USB 3.1 Super Speed signals.

Figure 3-2. USB 3.1 Super Speed Placement Diagram

#### 3.1.2 Routing Specifications

These parameters are recommendations only, intended to get the design close to success prior to simulation. To make sure the PCB design meets all requirements, it is required that the design be simulated and those results compared with the simulation results defined in Section 4.

Table 3-3. USB3.1 (Super Speed) Routing Specifications

| Parameter                                               | MIN  | TYP  | MAX                 | Unit  |

|---------------------------------------------------------|------|------|---------------------|-------|

| USB3.1 Gen1 Operating Speed                             |      |      | 2.5 <sup>(1)</sup>  | GHz   |

| (Super Speed signals)                                   |      |      |                     |       |

| USB3.1 Signal Trace Length                              |      |      | 5000 <sup>(2)</sup> | Mils  |

| USB3.1 Differential Pair Skew                           |      |      | 1                   | ps    |

| USB3.1 Differential Impedance                           | 85.5 | 90   | 94.5                | Ω     |

| Number of stubs allowed on USB3.1 traces                |      |      | 0                   | stubs |

| Number of vias on each USB3.1 trace                     |      |      | 2                   | Vias  |

| Via Stub Length (3)                                     |      | 20   |                     | Mils  |

| USB3.1 Differential Pair to any other Trace Spacing (4) | 2×DS | 3×DS |                     |       |

- (1) For supported data rates, see the device-specific data manual.

- (2) Max value is based upon conservative signal integrity approach. This value can be extended only if detailed signal integrity analysis confirms the desired operation.

- (3) Via stub control can be required when operating at higher data rates.

- (4) DS = differential spacing of the traces. Exceptions can be necessary in the SoC package BGA area.

Table 3-4. USB2.0 Routing Specifications

| idalo o il committationo |        |                |                                              |  |

|--------------------------|--------|----------------|----------------------------------------------|--|

| MIN                      | TYP    | MAX            | Unit                                         |  |

|                          |        | 240            | MHz                                          |  |

|                          |        | 7000 (1)       | Mils                                         |  |

|                          |        | 5              | ps                                           |  |

| 81                       | 90     | 99             | Ω                                            |  |

|                          |        | 0              | stubs                                        |  |

|                          |        | 4              | Vias                                         |  |

| 2×DS                     | 3×DS   |                |                                              |  |

|                          | MIN 81 | MIN TYP  81 90 | MIN TYP MAX  240  7000 (1)  5  81 90 99  0 4 |  |

- (1) Max value is based upon conservative signal integrity approach. This value can be extended only if detailed signal integrity analysis confirms the desired operation.

- (2) DS = differential spacing of the traces. Exceptions can be necessary in the SoC package BGA area.

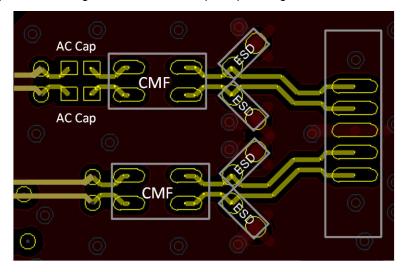

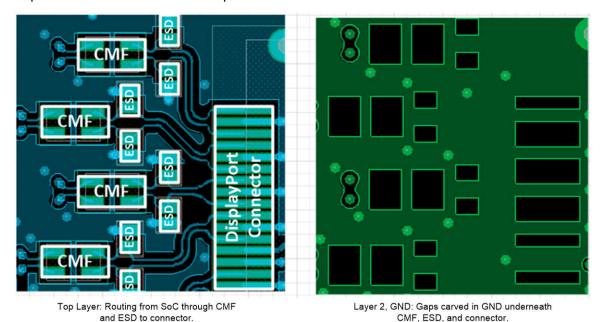

Component pads create impedance discontinuities due to the increased widths of the pads. In an effort to minimize impedance discontinuities, voids are created in the reference plane beneath the component pads. Figure 3-3 presents an example layout, demonstrating the "carve GND" concept. Before and after effects of the reference plane voids can be seen in TDR plots and simulation results.

Figure 3-3. USB 3.1 Example "carve GND" Layout

### 3.2 DisplayPort Board Design and Layout Guidelines

The DisplayPort (DP) interfaces on the device are compliant with the DP 1.3 specification. The DP signals are high-speed differential pairs, and care must be taken in the PCB layout of these signals to provide good signal integrity.

#### 3.2.1 DP Interface Schematic

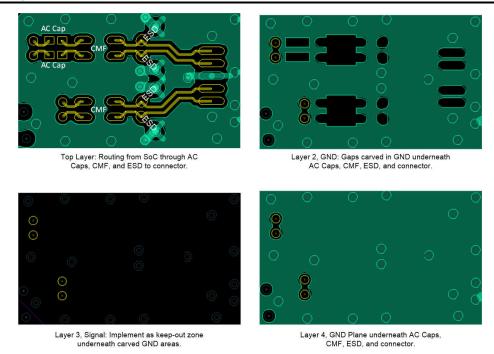

The DP interface schematics vary, depending on the target peripheral implemented. General connectivity is straightforward and consistent between implementations. Figure 3-4 shows a typical DP interface schematic.

Figure 3-4. DisplayPort Interface High Level Schematic

#### 3.2.1.1 Support Components

AC coupling capacitors are required on all the DP data pairs. Table 3-5 shows the requirements for these capacitors.

**Table 3-5. DP AC Coupling Capacitors Requirements**

| Parameter                               | MIN | TYP  | MAX  | Unit                                |

|-----------------------------------------|-----|------|------|-------------------------------------|

| PCIe AC coupling capacitor value        | 175 | 220  | 265  | nF                                  |

| PCIe AC coupling capacitor package size |     | 0402 | 0603 | EIA <sup>(1)</sup> , <sup>(2)</sup> |

- (1) EIA LxW units, for example, a 0402 is a 40 × 20mils surface mount capacitor.

- (2) Make the physical size of the capacitor as small as practical. Use the same size on both lines in each pair placed side by side.

A typical DP interface may also common mode chokes for suppression of high-frequency noise. Because DP can interface to external monitors, ESD protection is also included in the example.

**Table 3-6. DP Component Reference**

| Device | Supplier | Part Number   | Comment                   |

|--------|----------|---------------|---------------------------|

| ESD    | ті       | TDP1E05U06    | Minimize Capacitance      |

| CMF    | Murata   | DLW21SZ900HQ2 | Support Target Data Rates |

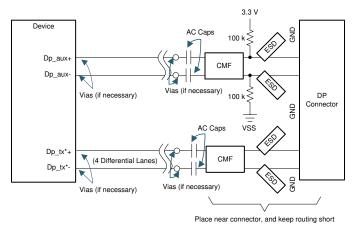

Figure 3-5 presents the placement diagram for the DisplayPort interface.

Figure 3-5. DisplayPort Placement

### 3.2.2 Routing Specifications

These parameters are recommendations only, intended to get the design close to success prior to simulation. To make sure the PCB design meets all requirements, it is required the design be simulated and those results compared with the simulation results defined in Section 4.

Table 3-7. DP Routing Specifications

| Table 6 7: Dr. Routing Operations |     |                     |                                                     |  |  |  |

|-----------------------------------|-----|---------------------|-----------------------------------------------------|--|--|--|

| MIN                               | TYP | MAX                 | Unit                                                |  |  |  |

|                                   |     | 4.05 <sup>(1)</sup> | GHz                                                 |  |  |  |

|                                   |     | 4000 <sup>(2)</sup> | Mils                                                |  |  |  |

|                                   |     | 1                   | ps                                                  |  |  |  |

|                                   |     | 1250                | ps                                                  |  |  |  |

| 90                                | 100 | 110                 | Ω                                                   |  |  |  |

|                                   |     | 0                   | stubs                                               |  |  |  |

|                                   |     | 2                   | Vias                                                |  |  |  |

|                                   | 20  |                     | Mils                                                |  |  |  |

| 2×DS (4)                          |     |                     |                                                     |  |  |  |

|                                   | 90  | 90 100<br>20        | MIN TYP MAX 4.05 (1) 4000 (2) 1 1250 90 100 110 0 2 |  |  |  |

- (1) For supported data rates, see the device-specific data manual.

- (2) Max value is based upon conservative signal integrity approach. This value can be extended only if detailed signal integrity analysis confirms the desired operation.

- (3) Via stub control can be required when operating at higher data rates.

- (4) DS = differential spacing of the traces, Exceptions can be necessary in the SoC package BGA area.

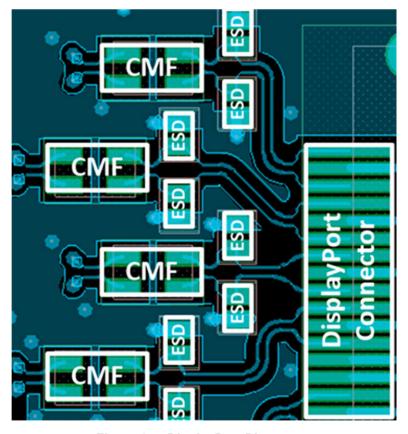

Component pads create impedance discontinuities due to the increased widths of the pads. In an effort to minimize impedance discontinuities, voids are created in the reference plane beneath the component pads. Figure 3-6 presents an example layout, demonstrating the "carve GND" concept. Before and after effects of the reference plane voids can be seen in TDR plots and simulation results.

Figure 3-6. Example "carve GND" Layout

### 3.3 PCle Board Design and Layout Guidelines

The PCIe interface on the device is compliant with the PCIe revision 3.0 specification. Refer to the PCIe specifications for all the described connections. Those recommendations are more descriptive and exhaustive than what is possible in this application note. The PCIe Motherboard Checklist 1.0 document is also available from PCI-SIG (www.pcisig.com).

The following sections contain suggestions for any PCIe connection that is *not* described in the official PCIe specification, such as an onboard Device-to-Device or Device-to-other PCIe compliant processor connection.

The use of PCIe compatible bridges and switches is allowed for interfacing with more than one other processor or PCIe device.

#### 3.3.1 PCIe Interface Schematic

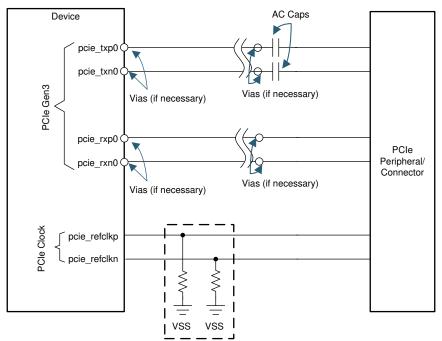

The PCIe interface schematics vary, depending on the number of lanes implemented and where the reference clock is generated internally or externally. General connectivity is straightforward and consistent between implementations. Figure 3-7 illustrates a single lane, common RefClk Rx clock architecture with device generating the RefClk (output mode).

PCIe clock shown in output clock mode. Termination resistors are to be removed for input clock mode.

Figure 3-7. PCIe Interface High Level Schematic

#### Note

AC coupling capacitors are not shown on the receive data pairs as these capacitors are typically located on the transmit end of the PCIe differential pair.

#### 3.3.1.1 Polarity Inversion

The PCIe specification requires polarity inversion support. This means for layout purposes, polarity is unimportant because each signal can change the polarity on the die inside the chip. This means polarity within a lane is unimportant for layout.

#### 3.3.1.2 Lane Swap

The PCI interface supports lane swapping, meaning Lane 0 of one device can be connected to Lane 1 of second device. (This requires both the TX and RX signal to remain assigned to same lane). This means for layout purposes, lane assignment is unimportant because each lane can change the assignment on the die inside the chip. This means lane assignment is unimportant for layout.

#### 3.3.1.3 REFCLK Connections

Common REFCLK Rx Architecture is required to be used for the device PCle interface. Specifically, two modes of Common REFCLK Rx Architecture are supported:

- External REFCLK Mode: An common external 100MHz clock source is distributed to both the device and the link partner

- Output REFCLK Mode: A 100MHz HCSL clock source is output by the device and used by the link partner

In External REFCLK Mode, provide a high-quality, low-jitter, differential HCSL 100MHz clock source compliant to the PCle REFCLK AC Specifications on the refclkp and refclkn inputs of the device. Alternatively, an LVDS clock source can be used with the following additional requirements:

- Populate the external AC coupling capacitors described in Table 3-8 at the refclkp and refclkn inputs.

- Follow all termination requirements (parallel 100Ω termination) from the clock source manufacturer.

In Output REFCLK Mode, the 100MHz clock from the device can be output on the refclkp and refclkn pins of the device and used as the HCSL REFCLK by the link partner. External near-side termination to ground described in Table 3-8 is required on both of the refclk outputs in this mode.

Table 3-8. REFCLKP, REFCLKN Requirements in External LVDS REFCLK Mode

| Parameter                                           | MIN | TYP  | MAX  | Unit                                |

|-----------------------------------------------------|-----|------|------|-------------------------------------|

| refclkp, refclkn AC coupling capacitor value        |     | 100  |      | nF                                  |

| refclkp, refclkn AC coupling capacitor package size |     | 0402 | 0603 | EIA <sup>(1)</sup> , <sup>(2)</sup> |

- (1) EIA LxW units, for example, a 0402 is a 40 × 20mils surface mount capacitor.

- (2) Make the physical size of the capacitor as small as practical. Use the same size on both lines in each pair placed side by side.

Table 3-9. REFCLKP, REFCLKN Requirements in Output REFCLK Mode

| Parameter                                              | MIN  | TYP | MAX  | Unit |

|--------------------------------------------------------|------|-----|------|------|

| refclkp, refclkn near-side termination to ground value | 47.5 | 50  | 52.5 | Ω    |

#### 3.3.1.4 Coupling Capacitors

AC coupling capacitors are required on the transmit data pair. Table 3-10 shows the requirements for these capacitors.

**Table 3-10. PCIe AC Coupling Capacitors Requirements**

| Parameter                                           | MIN | TYP  | MAX  | Unit                                |

|-----------------------------------------------------|-----|------|------|-------------------------------------|

| refclkp, refclkn AC coupling capacitor value        |     | 100  |      | nF                                  |

| refclkp, refclkn AC coupling capacitor package size |     | 0402 | 0603 | EIA <sup>(1)</sup> , <sup>(2)</sup> |

- (1) EIA LxW units, for example, a 0402 is a 40 × 20mils surface mount capacitor.

- (2) Make the physical size of the capacitor as small as practical. Use the same size on both lines in each pair placed side by side.

### 3.3.2 Routing Specifications

These parameters are recommendations only, intended to get the design close to success prior to simulation. To make sure the PCB design meets all requirements, is required the design be simulated and those results compared with the simulation results defined in Section 4.

Table 3-11. PCI-E Routing Specifications

| Parameter                                         | MIN      | TYP                                              | MAX                 | Unit  |  |

|---------------------------------------------------|----------|--------------------------------------------------|---------------------|-------|--|

| PCIe Operating Speed                              |          |                                                  | 4 (1)               | GHz   |  |

| PCIe Signal Trace Length                          |          |                                                  | 5000 <sup>(2)</sup> | Mils  |  |

| PCIe Differential Pair Skew                       |          |                                                  | 1                   | ps    |  |

| PCIe Lane Skew (example PCIe_TX0 to PCIe_TX1)     | No match | No matching needed (de-skew built into receiver) |                     |       |  |

| PCIe Differential Impedance                       | 72.5     | 85                                               | 97.5                | Ω     |  |

| PCIe Single-ended Impedance                       | 38       | 45                                               | 52                  | Ω     |  |

| PCIe RefClk Differential Impedance                | 85       | 100                                              | 115                 | Ω     |  |

| Number of stubs allowed on PCIe traces            |          |                                                  | 0                   | stubs |  |

| Number of vias on each PCle trace                 |          |                                                  | 2                   | Vias  |  |

| Via Stub Length (3)                               |          | 20                                               |                     | Mils  |  |

| PCIe Differential Pair to any other Trace Spacing | 2×DS (4) |                                                  |                     |       |  |

- (1) For supported data rates, see the device-specific data manual.

- (2) Max value is based upon conservative signal integrity approach. This value can be extended only if detailed signal integrity analysis confirms the desired operation.

- (3) Via stub control can be required when operating at higher data rates.

- (4) DS = differential spacing of the traces, exceptions can be necessary in the SoC package BGA area.

## 3.4 MIPI® D-PHY (CSI2, DSI) Board Design and Layout Guidelines

The Camera Serial Interface (CSI-2®) and Display Serial Interface (DSI®) on the device are compliant with the MIPI® CSI, DSI 1.3 specification. For all connections that are described in the specification (specifically the Interconnect and Lane Configuration and Annex B Interconnect Design Guidelines chapters) see the MIPI specifications.

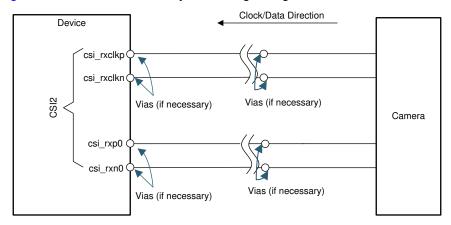

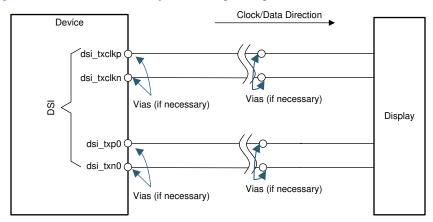

DSI is a data transmit interface, typically used to interface with a display panel. CSI-2 is a data received interface, typically used to interface with a remote camera. From an implementation perspective, the interfaces are very similar and thus are lumped together in this section.

#### 3.4.1 CSI-2®, DSI® Interface Schematic

The CSI-2 schematics vary, depending on the number of lanes implemented. Depending upon device, each CSI-2 can include up to four data lanes. General connectivity is straightforward and consistent between implementations. Figure 3-8 illustrates a CSI-2 system using a single lane.

Figure 3-8. CSI-2® High-Level Schematic

The DSI schematics vary, depending on the number of lanes implemented. Depending upon device, each DSI can include up to four data lanes. General connectivity is straightforward and consistent between implementations. Figure 3-9 illustrates a DSI system using a single lane.

Figure 3-9. DSI High-Level Schematic

#### 3.4.2 Routing Specifications

These parameters are recommendations only, intended to get the design close to success prior to simulation. To ensure the PCB design meets all requirements, it is required the design be simulated and those results compared with the simulation results defined in Section 4.

Table 3-12. PCI-E Routing Specifications

| innie o i i i i i i i i i i i i i i i i i i           |                                                  |     |                     |        |  |

|-------------------------------------------------------|--------------------------------------------------|-----|---------------------|--------|--|

| Parameter                                             | MIN                                              | TYP | MAX                 | Unit   |  |

| CSI2/DSI Operating Speed                              |                                                  |     | 1.25 <sup>(1)</sup> | GHz    |  |

| CSI2/DSI Signal Trace Length                          |                                                  |     | 10 <sup>(2)</sup>   | Inches |  |

| CSI2/DSI Differential Pair Skew                       | Have to satisfy mode-conversion S parameters (3) |     |                     |        |  |

| CSI2/DSI Lane Skew                                    |                                                  |     |                     |        |  |

| (example DSI_TX0 to DSI_TX1)                          |                                                  |     | 40 (4)              | ps     |  |

| CSI2/DSI Differential Impedance (5)                   | 85                                               | 100 | 115                 | Ω      |  |

| CSI2/DSI Single-ended Impedance                       |                                                  | 50  |                     | Ω      |  |

| Number of stubs allowed on CSI2/DSI traces            |                                                  |     | 0                   | stubs  |  |

| Number of vias on each CSI2/DSI trace                 |                                                  |     | 2                   | Vias   |  |

| CSI2/DSI Differential Pair to any other Trace Spacing | 2×DS (6)                                         |     |                     |        |  |

- (1) For supported data rates, see the device-specific data manual.

- (2) MAX value is based upon conservative signal integrity approach. This value can be extended only if detailed signal integrity analysis confirms the desired operation.

- (3) Defined in MIPI D-PHY spec, includes sdc12, scd21, scd12, scd21, scd11, scd22, and sdc22. General estimate is UI / 50 (where UI = 400ps for 1.25GHz).

- (4) Defined by MIPI spec as 0.1 × UI (where UI = 400ps for 1.25GHz).

- (5) Because the MIPI signals are used for low-power, single-ended signaling in addition to their high-speed differential implementation, the pairs must be loosely coupled.

- (6) DS = differential spacing of the traces, exceptions can be necessary in the SoC package BGA area.

### 3.4.3 Frequency-Domain Specification Guidelines

After the PCB design is implemented, the S-parameters of the PCB differential lines are extracted with a 3D Maxwell Equation Solver such as the high-frequency structure simulator (HFSS) or equivalent, and compared to the frequency-domain specification as defined in *Section 7* of the *MIPI Alliance Specification for D-PHY Version v1-01-00\_r0-03*. If the PCB satisfies the frequency-domain specification, the design is finished. Otherwise, the design needs to be improved.

#### 3.5 UFS Board Design and Layout Guidelines

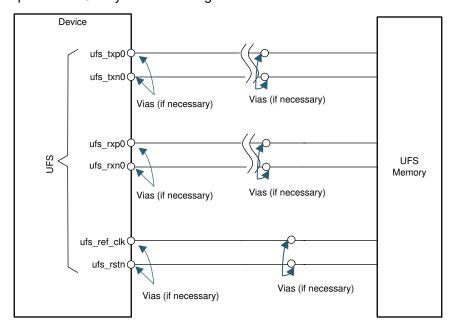

This section discusses guidelines when designing a universal flash storage (UFS) system. The UFS interfaces on the device are compliant with the UFS 2.1 specification. UFS interfaces are commonly used for either embedded or removable memory storage access.

#### 3.5.1 UFS Interface Schematic

The UFS interface schematics vary, depending on the number of lanes implemented, as depending if the memory is embedded or removable. Depending upon the device, each UFS interface can include up to two data lanes (each direction). General connectivity is straightforward and consistent between implementations. Figure 3-10 illustrates a UFS system using a single lane. The TX and RX signals are implemented as differential pairs. The REF\_CLK and RSTN signals are single-ended signals. These single ended are slow speed interfaces, and nothing special is required for PCB layout of these signals.

Figure 3-10. UFS Interface High Level Schematic

### 3.5.2 Routing Specifications

These parameters are recommendations only, intended to get the design close to success prior to simulation. To make sure the PCB design meets all requirements, it is required the design be simulated and those results compared with the simulation results defined in Section 4.

| Table 3-13. Of 3 Routing Specifications                   |          |     |          |       |

|-----------------------------------------------------------|----------|-----|----------|-------|

| Parameter                                                 | MIN      | TYP | MAX      | Unit  |

| UFS Operating Speed                                       |          |     | 2.9 (1)  | GHz   |

| UFS Signal Trace Length                                   |          |     | 4000 (2) | Mils  |

| UFS Differential Pair Skew                                |          |     | 2        | ps    |

| UFS Lane Skew <sup>(3)</sup> (example UFS_TX0 to UFS_TX1) |          |     | 300      | ps    |

| UFS Differential Impedance                                | 85       | 100 | 115      | Ω     |

| Number of stubs allowed on UFS traces                     |          |     | 0        | stubs |

| Number of vias on each UFS trace                          |          |     | 2        | Vias  |

| Via Stub Length <sup>(4)</sup>                            |          | 20  |          | Mils  |

| UFS Differential Pair to any other Trace Spacing          | 2×DS (5) |     |          |       |

**Table 3-13. UFS Routing Specifications**

- (1) For supported data rates, see the device-specific data manual.

- (2) MAX value is based upon conservative signal integrity approach. This value can be extended only if detailed signal integrity analysis confirms the desired operation.

- (3) The single ended traces have no skew requirement relative to differential pairs or each other.

- (4) Via stub control can be required when operating at higher data rates.

- (5) DS = differential spacing of the traces, exceptions can be necessary in the SoC package BGA area.

### 3.6 Q/SGMII Board Design and Layout Guidelines

This section discusses guidelines when designing a system that includes serial Gigabit Ethernet. Serial Gigabit Media Independent Interface (SGMII) interfaces on the device are commonly used for communication with Ethernet PHY devices. Quad-Ethernet (QSGMII) is the combination of four Ethernet PHYs onto a single serial stream.

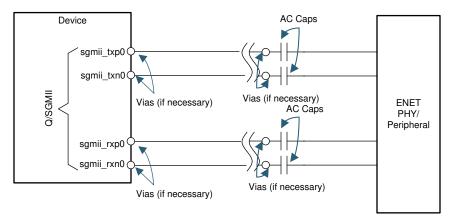

#### 3.6.1 Q/SGMII Interface Schematic

The Q/SGMII interface connectivity is straightforward and consistent between implementations. Figure 3-11 illustrates a Q/SGMII system. Ethernet PHY designs include other signals like MDIO that are not included in this guideline. These single ended are slow speed interfaces, and nothing special is required for PCB layout of these signals.

Figure 3-11. SGMII Interface High Level Schematic

#### 3.6.1.1 Coupling Capacitors

AC coupling capacitors are required on the transmit and receive data pair. Table 3-14 shows the requirements for these capacitors.

Table 3-14. Q/SGMII AC Coupling Capacitors Requirements

| Parameter                               | MIN | TYP  | MAX | Unit                                |

|-----------------------------------------|-----|------|-----|-------------------------------------|

| PCIe AC coupling capacitor value        |     | 100  |     | nF                                  |

| PCIe AC coupling capacitor package size |     | 0402 |     | EIA <sup>(1)</sup> , <sup>(2)</sup> |

- (1) EIA LxW units, for example, a 0402 is a 40 × 20mils surface mount capacitor.

- (2) Make the physical size of the capacitor as small as practical. Use the same size on both lines in each pair placed side by side.

#### 3.6.2 Routing Specifications

These parameters are recommendations only, intended to get the design close to success prior to simulation. To make sure the PCB design meets all requirements, it is required the design be simulated and those results compared with the simulation results defined in Section 4.

Table 3-15. G/SGMII Routing Specifications

| Parameter                                            | MIN      | TYP | MAX                 | Unit  |

|------------------------------------------------------|----------|-----|---------------------|-------|

| Q/SGMII Operating Speed                              |          |     | 2.5 <sup>(1)</sup>  | GHz   |

| Q/SGMII Signal Trace Length                          |          |     | 5000 <sup>(2)</sup> | Mils  |

| Q/SGMII Differential Pair Skew                       |          |     | 2                   | ps    |

| Q/SGMII Differential Impedance                       | 85       | 100 | 115                 | Ω     |

| Number of stubs allowed on Q/SGMII traces            |          |     | 0                   | stubs |

| Number of vias on each Q/SGMII trace                 |          |     | 2                   | Vias  |

| Via Stub Length (3)                                  |          | 20  |                     | Mils  |

| Q/SGMII Differential Pair to any other Trace Spacing | 2×DS (4) |     |                     |       |

- (1) For supported data rates, see the device-specific data manual.

- (2) MAX value is based upon conservative signal integrity approach. This value can be extended only if detailed signal integrity analysis confirms the desired operation.

- (3) Via stub control can be required when operating at higher data.

- (4) DS = differential spacing of the UFS traces. Exceptions can be necessary in the SoC package BGA area.

### 4 Board Design Simulations

This section is intended to provide an overview of the basic system-level board extraction, simulation, and analysis methodologies for high-speed serial interfaces. This is an essential step to ensure the PCB design meets all the requirements to operate the targeted speeds.

#### 4.1 Board Model Extraction

The board level extraction guidelines listed below are intended to work in any EDA extraction tool and are not tool-specific. It is important to follow the steps outlined in Section 4.2 through Section 4.4 immediately after completing touchstone model extractions. The design should be checked with these steps prior to running IBIS simulations.

- For high speed serial interface extractions, there is no need to extract power and signal nets together in a 3D-EM solver. Simulations are only intended for Signal Integrity.

- Use wide-band models. It is recommended to extract from DC to at least till 6x the Nyquist frequency (for USB3.1 Gen 1, extract the model at least till 15GHz).

- Check the board stack-up for accurate layer thickness and material properties.

- It is recommended to use Djordjevic-Sarkar models for the dielectric material definition.

- Use accurate etch profiles and surface roughness for the signal traces across all layers in the stack-up.

- If the board layout is cut prior to extraction (to reduce simulation time), please define a cut boundary that is at least 0.25 inch away from the signal and power nets.

- · Check the via padstack definitions

- Ensure that the non-functional internal layer pads on signal vias are modeled the same way they would be fabricated.

- These non-functional internal layer pads on signal vias are not recommended by TI

- Use Spice/S-parameter models (typically available from the vendor) for modeling all passives in the system

#### 4.2 Board-Model Validation

The extracted board models need to be checked for the following properties:

- Passivity: This ensures that the board model is a passive network and does not generate energy.

- Causality: This ensures that the board model obeys the causal relationship (output follows input).

These checks can be performed in any standard EDA simulator or extraction engine.

28

### 4.3 S-Parameter Inspection

Once the extracted S-parameters have been verified as causal and passive, the S-parameter plots should be inspected. It is recommended to check for the following:

- Insertion Loss: The single-ended insertion loss is recommended to stay within 0 to 10dB up to 3 times

the Nyquist frequency of operation. For example, if the target frequency is 8Gbps (4GHz Nyquist), the

single-ended insertion loss should stay under 10dB up to 12GHz.

- Return Loss: The single-ended return loss is recommended to be less than 15dB up to 3 times the Nyquist frequency.

- Near and Far end crosstalk (FEXT/NEXT): The FEXT and NEXT are recommended to be under 25dB for frequencies up to 3 times the Nyquist frequency

### 4.4 Time Domain Reflectometry (TDR) Analysis

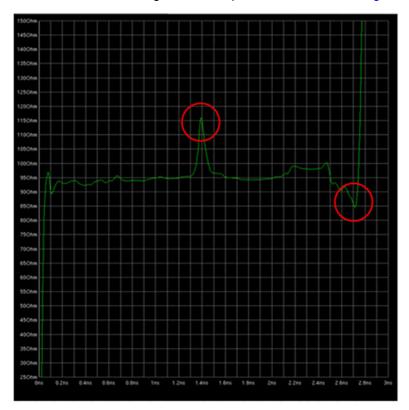

As a lot of the design fixes are targeted towards maintaining uniform trace impedance, an important analysis method used in assessing the quality of the design is the Time Domain Reflectometry (TDR) Analysis. This plots the impedance of a trace as a function of its length. An example of this is shown in Figure 4-1.

Figure 4-1. TDR Plot Example With Impedance Mismatch

As shown in Figure 4-1 (TDR plot example), the TDR plot highlights impedance discontinuities in the trace from one end to the other. This method depends on a reflected waveform from the far-end of the trace. The delay in the plot corresponding to a particular point in the trace actually corresponds to 2 times the distance of that point from the source, owing to the round trip time. This needs to be factored in for assessing the source of impedance discontinuities.

The TDR plot can be generated by reading in the S-parameter models generated by the extraction tool and assessing them in "Time-Domain" mode. A standard EDA simulator such as HyperLynx can perform this function. It is recommended to optimize the design to within a ± 5% deviation from the nominal trace impedance.

Board Design Simulations Www.ti.com

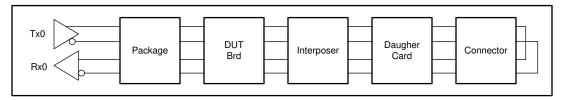

### 4.5 Simulation Integrity Analysis

The general methodology for evaluating signal integrity for high-speed SERDES interfaces is illustrated in Figure 4-2. This involves running a channel simulation for the serial link. The methodology uses IBIS-AMI (Algorithmic Modeling Interface) models for the Tx/Rx blocks. The basic setup and settings documented here can be used to validate all SerDes links and also across a variety of EDA Signal Integrity simulators. This channel simulation should be performed as a signoff check for all high-speed Serial Link interfaces.

Figure 4-2. Signal Integrity Analysis Setup - Channel Simulation

#### 4.5.1 Simulator Settings and Model Usage

The following things need to be kept in mind while performing channel simulation:

- Odd mode crosstalk is used to define aggressor and victim switching in opposite directions. This is required if multiple lanes are simulated.

- An important note to keep in mind is that the jitter and noise of Tx/Rx blocks should not be double counted.

As the IBIS-AMI models already have the various jitter sources incorporated, the option to include additional jitter in these blocks must be turned off in the EDA simulation engine of choice.

### 4.5.2 Simulation Parameters

The serial link simulations involve a parametric sweep:

- Corners: The IBIS-AMI models for Tx/Rx are characterized as Fast/Typ/Slow corners. The different Deterministic and Random Jitter budgets are built in to the models using these corners.

- Transmitter Presets: These are specific to each standard and control the coefficients in the transmitter DFE

(Decision Feedback Equalizer). These presets also model the level of de-emphasis in the transmit amplifier

which are required to equalize the overall system-level response across different frequencies and counteract

the impact of ISI (Inter-symbol interference). It is recommended using a parametric sweep and simulate for all

different transmitter presets for a given Serial Link protocol. This is due to the fact that the best eye observed

can be highly dependent on the system impulse response and therefore different presets could yield the best

results on different systems.

- Data Patterns: It is recommended to use PRBS23 or PRBS31 patterns to validate the system, in order to excite larger levels of ISI.

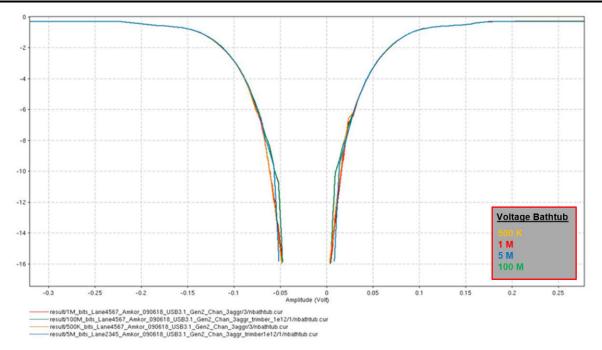

#### 4.5.3 Simulation Methodology

For interfaces where the eye mask is specified in terms of a BER target it is recommended to run the initial channel simulations for around 100K bits and observe the extrapolated bathtub curves for the corresponding target BER, as reported by the simulator. Another simulation for around 500K and 1M bits can be rerun and the bathtub curves can be overlaid to observe the impact of running for larger bit sequences. An example of voltage bathtub curves overlaid is shown in Figure 4-3. Similar overlay can be made for the jitter bathtub curves.

30

Figure 4-3. Bathtub Curve Overlay

Typically, all the ISI should be accounted for within the first 100K bits of the simulation and beyond this point, all bathtub curves should converge if the Random Jitter (Rj) in the models is sufficiently small. It is recommended to confirm this convergence up front by running at least one set of system-level channel simulations each for 100K, 500K and 1M bit sequences. If the voltage and jitter bathtub curves from each of these simulations are almost identical, the remainder of the simulations can be run at 100K bits to optimize run times.

For interfaces where the eye mask is not specified for any particular BER target, a 100K bit simulation should suffice.

### 4.6 Reviewing Simulation Results

The results generated by the channel simulations outlined in the preceding sections are compared against an eye mask spec. This eye mask is summarized in Table 4-1. This is used as a pass/fail check for the system. Note some protocol are supported on different buffer type. See device data manual pin attributes to determine the buffer type for each IO.

Eye Width (pS) **Protocol Buffer Type** (mV) PCIe Gen3/4 SierraPhy 70 5 Post-equalization eye mask. BER Target 1E-12 **USB3.1** SierraPhy 70 5 DP/eDP N/A N/A TorrentPhy TP3\_EQ eye mask (Section 4.6.1 of eDP\_v1.4b\_E1 specification) BER Target 1E-09 SierraPhy XFI 5 Post-equalization eye mask. BER Target 1E-12 70 QSGMII 70 5 SierraPhy **TorrentPhy** 50 25

5

25

N/A

0.7\*UI

0.6\*UI

Eye Height

70

50

300mV/700

mV

± 50mV

± 45mV

Table 4-1. Eye Mask Specifications for Different Standards

SierraPhy

TorrentPhy

D-Phy

M-Phy

SGMII

**UFS**

CSI (Rx)/DSI (Tx)

Remote/Local post-EQ

Complete Loopback post-EQ

300mV at the equalizer input; 700mV at the equalizer output

References www.ti.com

### 5 References

- Texas Instruments: High-Speed Layout Guidelines for Signal Conditioners and USB Hubs

- Texas Instruments: High-Speed Interface Layout Guidelines

## **6 Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| C | Changes from Revision * (December 2019) to Revision A (June 2024) | Page |

|---|-------------------------------------------------------------------|------|

| • | Updated title of the document by adding additional devices        | 1    |

| • | Added Section 1.2                                                 | 3    |

|   |                                                                   |      |

### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2024, Texas Instruments Incorporated