DAC8551-Q1, DAC6551-Q1

SLASEB8C - FEBRUARY 2016 - REVISED NOVEMBER 2016

# DACx551-Q1 Automotive 16-, 12-Bit, Ultralow-Glitch, Voltage-Output DAC

## **Features**

- **Qualified for Automotive Applications**

- AEC-Q100 Qualified With the Following Results:

- Device Temperature Grade 1: -40°C to 125°C Ambient Operating Temperature Range

- Device HBM ESD Classification Level 2

- Device CDM ESD Classification Level C4B

- Relative Accuracy:

- DAC8551-Q1 (16-Bit): 4 LSB INL

- DAC6551-Q1 (12-Bit): 0.3 LSB INL

- Ultralow Glitch Impulse: 0.1 nV-s

- Settling Time: 8 µs to ±0.003% FSR

- Power Supply: 3 V to 5.5 V

- Power-On Reset to Zero Scale

- MicroPower Operation: 160 μA at 5 V

- Low-Power Serial Interface With Schmitt-Triggered Inputs

- On-Chip Output Buffer Amplifier With Rail-to-Rail Operation

- Power-Down Capability

- **Binary Input**

- SYNC Interrupt Facility

- Available in a Tiny VSSOP-8 Package

## **Applications**

- Automotive Radar

- **Automotive Sensors**

## 3 Description

The DAC8551-Q1 and DAC6551-Q1 are small, lowpower, voltage-output, 16- and 12-bit digital-to-analog (DACs) qualified converters for applications. The DACx551-Q1 devices provide good linearity and minimize undesired code-to-code transient voltages. The devices use a versatile 3-wire serial interface that operates at clock rates to 30 MHz and is compatible with standard SPI, QSPI, and digital signal-processor Microwire, (DSP) interfaces.

The DACx551-Q1 devices require an external reference voltage to set the output range. The devices incorporate a power-on-reset circuit that ensures the DAC output powers up at 0 V and remains there until a valid write to the device takes place. The devices contain a power-down feature, accessed over the serial interface, that reduces the current consumption to 800 nA at 5 V.

The DACx551-Q1 devices power consumption is only 800 μW at 5 V, reducing to less than 4 μW in powerdown mode. The DACx551-Q1 devices are available in a VSSOP-8 package.

## Device Information<sup>(1)</sup>

| PART NUMBER              | PACKAGE   | BODY SIZE (NOM)   |

|--------------------------|-----------|-------------------|

| DAC8551-Q1<br>DAC6551-Q1 | VSSOP (8) | 3.00 mm × 3.00 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

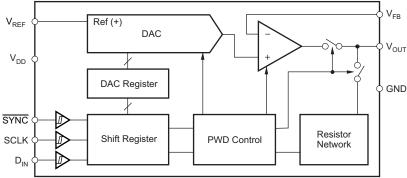

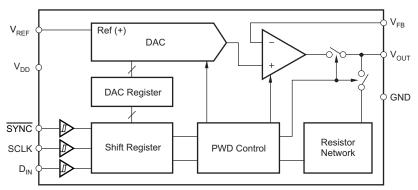

#### **Functional Block Diagram**

Copyright © 2016, Texas Instruments Incorporated

# **Table of Contents**

| 1 | Features 1                           |    | 7.4 Device Functional Modes                         | 15                |

|---|--------------------------------------|----|-----------------------------------------------------|-------------------|

| 2 | Applications 1                       |    | 7.5 Programming                                     | 16                |

| 3 | Description 1                        | 8  | Application and Implementation                      | . 17              |

| 4 | Revision History2                    |    | 8.1 Application Information                         | 17                |

| 5 | Pin Configuration and Functions 4    |    | 8.2 Typical Applications                            | 17                |

| 6 | Specifications4                      |    | 8.3 System Examples                                 | 20                |

| • | 6.1 Absolute Maximum Ratings         | 9  | Power Supply Recommendations                        | . 21              |

|   | 6.2 ESD Ratings                      | 10 | Layout                                              | . 21              |

|   | 6.3 Recommended Operating Conditions |    | 10.1 Layout Guidelines                              | <mark>2</mark> 1  |

|   | 6.4 Thermal Information              |    | 10.2 Layout Example                                 | <mark>2</mark> 1  |

|   | 6.5 Electrical Characteristics       | 11 | Device and Documentation Support                    | . 22              |

|   | 6.6 Timing Requirements              |    | 11.1 Documentation Support                          | 22                |

|   | 6.7 Switching Characteristics        |    | 11.2 Receiving Notification of Documentation Update | s <mark>22</mark> |

|   | 6.8 Typical Characteristics 8        |    | 11.3 Community Resources                            | 22                |

| 7 | Detailed Description 13              |    | 11.4 Trademarks                                     | 22                |

| - | 7.1 Overview                         |    | 11.5 Electrostatic Discharge Caution                | 22                |

|   | 7.2 Functional Block Diagram         |    | 11.6 Glossary                                       | 22                |

|   | 7.3 Feature Description              | 12 | Mechanical, Packaging, and Orderable Information    | . 22              |

# 4 Revision History

| C | changes from Revision B (November 2016) to Revision C                                                                                                                          | Page |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| • | Added device DAC6551-Q1 to the data sheet                                                                                                                                      |      |

| • | Changed the data sheet Title From: DAC8551-Q1 Automotive 16-Bit To: DACx551-Q1 Automotive 16-, 12-Bit                                                                          |      |

| • | Changed Relative Accuracy in the Features section                                                                                                                              |      |

| • | Updated the Description to include the DAC6551-Q1 device                                                                                                                       |      |

| • | Added DAC6551-Q1 to the Thermal Table                                                                                                                                          | !    |

| • | Added separate lines for the DAC6551-Q1 and DAC8551-Q1 devices for Resolution, Relative accuracy, and Differential nonlinearity in the <i>Electrical Characteristics</i> table | !    |

| • | Changed Note 1 of the Electrical Characteristics table                                                                                                                         |      |

| • | Updated the Overview section to include the DAC6551-Q1 device                                                                                                                  | 13   |

| • | Changed Equation 1                                                                                                                                                             | 13   |

| • | Changed the definitions of in the "where:" statement for Equation 1                                                                                                            | 1    |

| • | Deleted a sentence from the Resistor String section: "Monotonicity is ennsured because of the string resistor archietecture."                                                  | 1    |

| • | Added Figure 31                                                                                                                                                                | 10   |

| • | Updated the Application Information section to include the DAC6551-Q1 device                                                                                                   | 1    |

| • | Updated the Using the REF02 As a Power Supply for the DACx551-Q1 Device section to include the DAC6551-Q                                                                       | 1    |

|   | device                                                                                                                                                                         | 19   |

| • | Updated the System Examples section to include the DAC6551-Q1 device                                                                                                           | 20   |

| • | Updated the Power Supply Recommendations section to include the DAC6551-Q1 device                                                                                              | 2    |

| • | Updated the Layout Guidelines section to include the DAC6551-Q1 device                                                                                                         | 2    |

| Cr | nanges from Revision A (March 2016) to Revision B                                                                                  | Page           |

|----|------------------------------------------------------------------------------------------------------------------------------------|----------------|

| •  | Changed Relative Accuracy in the Features section                                                                                  | 1              |

| •  | Changed power supply voltage in the Features section                                                                               | 1              |

| •  | Changed voltage for V <sub>DD</sub> in the <i>Pin Functions</i> table                                                              | 4              |

| •  | Changed supply voltage in the Recommended Operating Conditions table                                                               | 5              |

| •  | Changed values in the <i>Thermal Information</i> table                                                                             | 5              |

| •  | Changed supply voltage in the conditions statement of the <i>Electrical Characteristics</i> table                                  | 5              |

| •  | Removed two rows and all test conditions in the LOGIC INPUTS section of the Electrical Characteristics table                       | 6              |

| •  | Changed supply voltage in the POWER REQUIREMENTS section of the Electrical Characteristics table                                   | 6              |

| •  | Changed test conditions for supply current in the POWER REQUIREMENTS section of the Electrical Characteristics table               |                |

| •  | Changed V <sub>DD</sub> in the condition statement and test conditions of the <i>Timing Requirements</i> <sup>(1)(2)</sup> section | <mark>7</mark> |

| •  | Changed MIN value for SCLK low time in the <i>Timing Requirements</i> <sup>(1)(2)</sup> section                                    | 7              |

| •  | Added text in the Application Information section                                                                                  | 17             |

| •  | Changed supply voltage in the <i>Power Supply Recommendations</i> section                                                          | 21             |

| •  | Added new Receiving Notification of Documentation Updates section                                                                  | 22             |

|    |                                                                                                                                    |                |

| Cr | nanges from Original (February 2016) to Revision A                                                                                 | Page           |

| •  | Changed data sheet from PRODUCT PREVIEW to PRODUCTON DATA                                                                          | 1              |

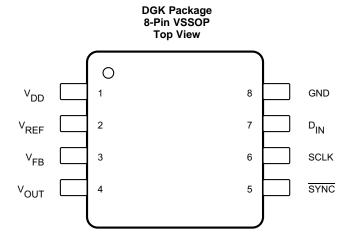

## 5 Pin Configuration and Functions

**Pin Functions**

| PIN              |     | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME             | NO. | ITPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| D <sub>IN</sub>  | 7   | I    | Serial data input. Data is clocked into the 24-bit input shift register on each falling edge of the serial clock input. Schmitt-trigger logic input.                                                                                                                                                                                                                                                                                                                   |

| GND              | 8   | GND  | Ground reference point for all circuitry on the device                                                                                                                                                                                                                                                                                                                                                                                                                 |

| SCLK             | 6   | I    | Serial clock input. Data can be transferred at rates up to 30 MHz. Schmitt-trigger logic input.                                                                                                                                                                                                                                                                                                                                                                        |

| SYNC             | 5   | I    | Level-triggered control input (active-low). This is the frame synchronization signal for the input data. SYNC going low enables the input shift register, and data is transferred in on the falling edges of the following clocks. The DAC is updated following the 24th clock (unless SYNC is taken high before this edge, in which case the rising edge of SYNC acts as an interrupt, and the write sequence is ignored by the device). Schmitt-trigger logic input. |

| $V_{DD}$         | 1   | PWR  | Power supply input, 3 V to 5.5 V                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| $V_{FB}$         | 3   | I    | Feedback connection for the output amplifier. For voltage output operation, tie to V <sub>OUT</sub> externally.                                                                                                                                                                                                                                                                                                                                                        |

| V <sub>OUT</sub> | 4   | 0    | Analog output voltage from DAC. The output amplifier has rail-to-rail operation.                                                                                                                                                                                                                                                                                                                                                                                       |

| $V_{REF}$        | 2   | I    | Reference voltage input                                                                                                                                                                                                                                                                                                                                                                                                                                                |

## 6 Specifications

## 6.1 Absolute Maximum Ratings

over operating ambient temperature range (unless otherwise noted)(1)

|                                                              | MIN  | MAX            | UNIT |

|--------------------------------------------------------------|------|----------------|------|

| V <sub>DD</sub> to GND                                       | -0.3 | 6              | V    |

| Digital input voltage to GND D <sub>IN</sub> , SCLK and SYNC | -0.3 | $V_{DD} + 0.3$ | V    |

| V <sub>OUT</sub> to GND                                      | -0.3 | $V_{DD} + 0.3$ | V    |

| V <sub>REF</sub> to GND                                      | -0.3 | $V_{DD} + 0.3$ | V    |

| V <sub>FB</sub> to GND                                       | -0.3 | $V_{DD} + 0.3$ | V    |

| Junction temperature range, T <sub>J</sub> max               | -65  | 150            | °C   |

| Storage temperature, T <sub>stg</sub>                        | -65  | 150            | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 6.2 ESD Ratings

|                    |                         |                                                         |                              | VALUE | UNIT |

|--------------------|-------------------------|---------------------------------------------------------|------------------------------|-------|------|

|                    |                         | Human-body model (HBM), per AEC Q100-002 <sup>(1)</sup> |                              | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per AEC                     | All pins                     | ±500  | V    |

| ( - /              | Q100-011                | Q100-011                                                | Corner pins (1, 4, 5, and 8) | ±750  |      |

<sup>(1)</sup> AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

## 6.3 Recommended Operating Conditions

over operating ambient temperature range (unless otherwise noted)

|                |                           |                                 | MIN | NOM              | MAX      | UNIT |

|----------------|---------------------------|---------------------------------|-----|------------------|----------|------|

| POW            | ER SUPPLY                 |                                 | ·   |                  | ·        |      |

|                | Supply voltage            | V <sub>DD</sub> to GND          | 3   |                  | 5.5      | V    |

| DIGIT          | AL INPUTS                 |                                 |     |                  |          |      |

|                | Digital input voltage     | D <sub>IN</sub> , SCLK and SYNC | 0   |                  | $V_{DD}$ | V    |

| REFE           | RENCE INPUT               |                                 |     |                  |          |      |

| $V_{REF}$      | Reference input voltage   |                                 | 0   |                  | $V_{DD}$ | V    |

| AMPI           | LIFIER FEEDBACK INPUT     |                                 | •   |                  | •        |      |

| $V_{FB}$       | Output amplifier feedback | input                           |     | V <sub>OUT</sub> |          | V    |

| TEMF           | PERATURE RANGE            |                                 |     |                  |          |      |

| T <sub>A</sub> | Operating ambient temper  | rature                          | -40 |                  | 125      | °C   |

#### 6.4 Thermal Information

|                      | 74)                                          | DAC8551-Q1<br>DAC6551-Q1 |      |

|----------------------|----------------------------------------------|--------------------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | DGK (VSSOP)              | UNIT |

|                      |                                              | 8 PINS                   |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 173.7                    | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 65.4                     | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 94.2                     | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 10.2                     | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 92.7                     | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

### 6.5 Electrical Characteristics

$V_{DD}$  = 3 V to 5.5 V,  $V_{REF}$  =  $V_{DD}$  and  $T_A$  = -40°C to 125°C, unless otherwise noted.

| PARAMETER                         | TEST CONDITIONS | MIN TY | P MAX      | UNIT             |

|-----------------------------------|-----------------|--------|------------|------------------|

| STATIC PERFORMANCE <sup>(1)</sup> |                 |        |            |                  |

| Resolution                        | DAC8551-Q1      | 16     |            | Bits             |

|                                   | DAC6551-Q1      | 12     |            | DIIS             |

| Relative accuracy                 | DAC8551-Q1      | =      | ±4 ±16     | LSB              |

| Relative accuracy                 | DAC6551-Q1      | ±0     | .3 ±1      | LOD              |

| Differential nonlinearity         | DAC8551-Q1      | ±0.0   | 35 ±2      | LSB              |

| Differential nonlinearity         | DAC6551-Q1      | ±0.0   | )2 ±1      | LOD              |

| Offset error                      |                 | =      | ±1 ±15     | mV               |

| Full-scale error                  |                 | ±0.0   | )5 ±0.5    | % of FSR         |

| Gain error                        |                 | ±0.0   | )2 ±0.2    | % of FSR         |

| Offset error drift                |                 | :      | ±5         | μV/°C            |

| Gain temperature coefficient      |                 | -      | <u>-</u> 1 | ppm of<br>FSR/°C |

(1) Linearity calculated using a reduced code range of 485 to 64,741 (16-bit); 30 to 4,046 (12-bit); output unloaded.

## **Electrical Characteristics (continued)**

$V_{DD}$  = 3 V to 5.5 V,  $V_{REF}$  =  $V_{DD}$  and  $T_A$  = -40°C to 125°C, unless otherwise noted.

|                   | PARAMETER                        | TEST CONDITIONS                                                                                                                            | MIN                 | TYP  | MAX                 | UNIT |

|-------------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|---------------------|------|

| PSRR              | Power-supply rejection ratio     | $R_L = 2 \text{ k}\Omega$ , $C_L = 200 \text{ pF}$                                                                                         |                     | 0.75 |                     | mV/V |

| OUTPU             | T CHARACTERISTICS <sup>(2)</sup> |                                                                                                                                            |                     |      |                     |      |

|                   | Output voltage range             |                                                                                                                                            | 0                   |      | $V_{REF}$           | V    |

|                   | Output voltage settling time     | To $\pm 0.003\%$ FSR, 0200h to FD00h R <sub>L</sub> = 2 k $\Omega$ , 0 pF < C <sub>L</sub> < 200 pF                                        |                     | 8    |                     | μS   |

|                   | Slew rate                        |                                                                                                                                            |                     | 1.4  |                     | V/μs |

|                   | Capacitive load stability        | R <sub>L</sub> = ∞                                                                                                                         |                     | 470  |                     | pF   |

|                   | Capacitive load stability        | $R_L = 2 k\Omega$                                                                                                                          |                     | 1000 |                     | pF   |

|                   | Code change glitch impulse       | 1 LSB change around major carry                                                                                                            |                     | 0.1  |                     | nV-s |

|                   | Digital feedthrough              | 50 kΩ series resistance on digital lines                                                                                                   |                     | 0.1  |                     | nV-s |

|                   | DC output impedance              | At mid-code input                                                                                                                          |                     | 1    |                     | Ω    |

|                   | Short-circuit current            | V <sub>DD</sub> = 3 V to 5.5 V                                                                                                             |                     | 35   |                     | mA   |

| AC PER            | RFORMANCE                        |                                                                                                                                            |                     |      |                     |      |

| SNR               | Signal-to-noise ratio            |                                                                                                                                            |                     | 84   |                     | dB   |

| THD               | Total harmonic distortion        | BW = 20 kHz, V <sub>DD</sub> = 5 V, V <sub>REF</sub> = 4.5 V, f <sub>OUT</sub> = 1 kHz                                                     |                     | -80  |                     | dB   |

| SFDR              | Spurious-free dynamic range      | First 19 harmonics removed for SNR calculation                                                                                             |                     | 84   |                     | dB   |

| SINAD             | Signal to noise and distortion   |                                                                                                                                            |                     | 76   |                     | dB   |

| REFER             | ENCE INPUT                       |                                                                                                                                            | <u> </u>            |      |                     |      |

|                   |                                  | $V_{REF} = V_{DD} = 5.5 \text{ V}$                                                                                                         |                     | 50   |                     |      |

|                   | Reference current                | $V_{REF} = V_{DD} = 3.6 \text{ V}$                                                                                                         |                     | 25   |                     | μΑ   |

|                   | Reference input range            |                                                                                                                                            | 0                   |      | $V_{DD}$            | V    |

|                   | Reference input impedance        |                                                                                                                                            |                     | 125  |                     | kΩ   |

| LOGIC             | INPUTS <sup>(2)</sup>            |                                                                                                                                            |                     |      |                     |      |

| Input cu          | ırrent                           |                                                                                                                                            |                     | ±1   |                     | μА   |

| V <sub>IN</sub> L | Input low voltage                |                                                                                                                                            |                     |      | 0.3×V <sub>DD</sub> | V    |

| V <sub>IN</sub> H | Input high voltage               |                                                                                                                                            | 0.7×V <sub>DD</sub> |      |                     | V    |

|                   | Pin capacitance                  |                                                                                                                                            |                     | 3    |                     | pF   |

| POWER             | R REQUIREMENTS                   |                                                                                                                                            |                     |      | <u> </u>            |      |

| $V_{DD}$          | Supply voltage                   |                                                                                                                                            | 3                   |      | 5.5                 | V    |

| 00                | 11.7                             | Normal mode, midscale code, no load, does not include reference current. $V_{IH}$ = $V_{DD}$ and $V_{IL}$ = GND, $V_{DD}$ = 3.6 V to 5.5 V |                     | 160  | 250                 |      |

| I <sub>DD</sub>   | Supply current                   | Normal mode, midscale code, no load, does not include reference current. $V_{IH}$ = $V_{DD}$ and $V_{IL}$ = GND, $V_{DD}$ = 3 V to 3.6 V   |                     | 110  | 240                 | μΑ   |

|                   |                                  | All power-down modes, $V_{IH}$ = $V_{DD}$ and $V_{IL}$ = GND, $V_{DD}$ = 3.6 V to 5.5 V                                                    |                     | 0.8  | 3                   |      |

|                   |                                  | All power-down modes, $V_{IH} = V_{DD}$ and $V_{IL} = GND$ , $V_{DD} = 3 \text{ V to } 3.6 \text{ V}$                                      |                     | 0.5  | 3                   |      |

| POWER             | REFFICIENCY                      |                                                                                                                                            |                     |      |                     |      |

|                   | $I_{OUT} / I_{DD}$               | $I_{LOAD} = 2 \text{ mA}, V_{DD} = 5 \text{ V}$                                                                                            |                     | 89%  |                     |      |

| TEMPE             | RATURE RANGE                     |                                                                                                                                            |                     |      |                     |      |

| T <sub>A</sub>    | Ambient temperature              |                                                                                                                                            | -40                 |      | 125                 | °C   |

<sup>(2)</sup> Specified by design and characterization; not production tested.

Submit Documentation Feedback

Copyright © 2016, Texas Instruments Incorporated

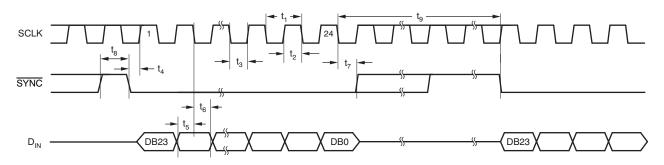

## 6.6 Timing Requirements (1)(2)

$V_{DD}$  = 3 V to 5.5 V and  $T_A$  = -40°C to 125°C, unless otherwise noted.

|                   | PARAMETER                                     | TEST CONDITIONS                            | MIN | NOM | MAX | UNIT   |

|-------------------|-----------------------------------------------|--------------------------------------------|-----|-----|-----|--------|

| 4                 | Corial alask fraguency                        | V <sub>DD</sub> = 3 V to 3.6 V             |     |     | 25  | NAL I- |

| f <sub>SCLK</sub> | Serial clock frequency                        | $V_{DD} = 3.6 \text{ V to } 5.5 \text{ V}$ |     |     | 30  | MHz    |

|                   | SCLV avalatima                                | V <sub>DD</sub> = 3 V to 3.6 V             | 40  |     |     |        |

| t <sub>1</sub>    | SCLK cycle time                               | $V_{DD} = 3.6 \text{ V to } 5.5 \text{ V}$ | 34  |     |     | ns     |

|                   | CCI I/ high time                              | $V_{DD} = 3 \text{ V to } 3.6 \text{ V}$   | 13  |     |     |        |

| t <sub>2</sub>    | SCLK high time                                | $V_{DD} = 3.6 \text{ V to } 5.5 \text{ V}$ | 13  |     |     | ns     |

|                   | SCLK low time                                 | $V_{DD} = 3 \text{ V to } 3.6 \text{ V}$   | 13  |     | n   |        |

| t <sub>3</sub>    | SCLK low time                                 | $V_{DD} = 3.6 \text{ V to } 5.5 \text{ V}$ | 13  |     |     | ns     |

|                   | CVAIC to CCLIV sision and an active time      | V <sub>DD</sub> = 3 V to 3.6 V             | 0   |     |     |        |

| t <sub>4</sub>    | SYNC to SCLK rising edge setup time           | V <sub>DD</sub> = 3.6 V to 5.5 V           | 0   |     |     | ns     |

|                   | Data action time                              | V <sub>DD</sub> = 3 V to 3.6 V             | 5   |     |     |        |

| t <sub>5</sub>    | Data setup time                               | $V_{DD} = 3.6 \text{ V to } 5.5 \text{ V}$ | 5   |     |     | ns     |

|                   | Data hald time                                | V <sub>DD</sub> = 3 V to 3.6 V             | 5   |     |     |        |

| t <sub>6</sub>    | Data hold time                                | $V_{DD} = 3.6 \text{ V to } 5.5 \text{ V}$ | 5   |     |     | ns     |

|                   | OATE COLIV falling a dea to CVNO vising a dea | V <sub>DD</sub> = 3 V to 3.6 V             | 0   |     |     |        |

| t <sub>7</sub>    | 24th SCLK falling edge to SYNC rising edge    | $V_{DD} = 3.6 \text{ V to } 5.5 \text{ V}$ | 0   |     | ns  | ns     |

|                   | Minimum CVNC high time                        | V <sub>DD</sub> = 3 V to 3.6 V             | 50  |     |     |        |

| t <sub>8</sub>    | Minimum SYNC high time                        | V <sub>DD</sub> = 3.6 V to 5.5 V           | 34  |     |     | ns     |

| t <sub>9</sub>    | 24th SCLK falling edge to SYNC falling edge   | V <sub>DD</sub> = 3 V to 5.5 V             | 50  |     |     | ns     |

All input signals are specified with  $t_R$  =  $t_F$  = 5 ns (10% to 90% of  $V_{DD}$ ) and timed from a voltage level of ( $V_{IL}$  +  $V_{IH}$ ) / 2. See the Serial-Write-Operation Timing Diagram.

## 6.7 Switching Characteristics

over operating ambient temperature range (unless otherwise noted)

| PARAMETER     | TEST CONDITIONS                                        | MIN | TYP | MAX | UNIT |

|---------------|--------------------------------------------------------|-----|-----|-----|------|

| Dower up time | Coming out of power-down mode, $V_{DD} = 5 \text{ V}$  |     |     |     |      |

| Power-up time | Coming out of power-down mode, V <sub>DD</sub> = 3.3 V |     | 5   |     | μs   |

Figure 1. Serial-Write-Operation Timing Diagram

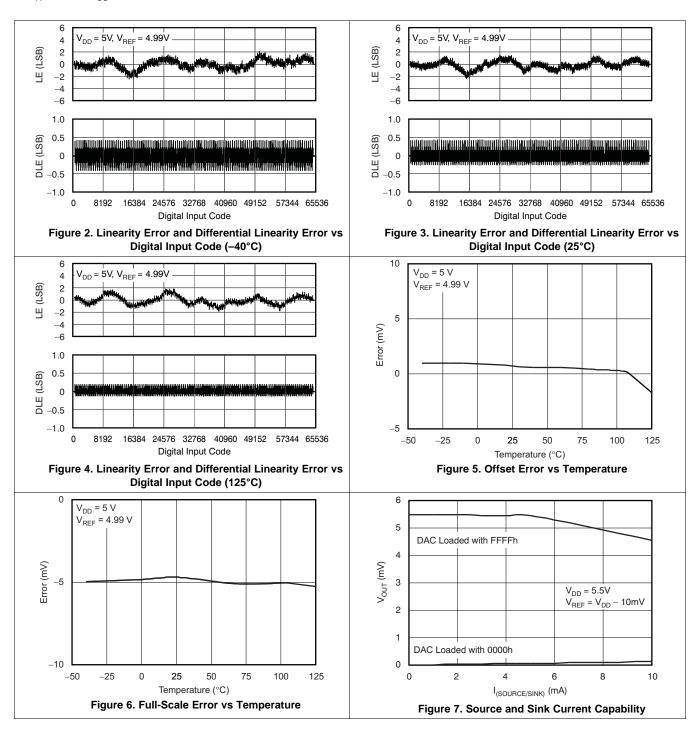

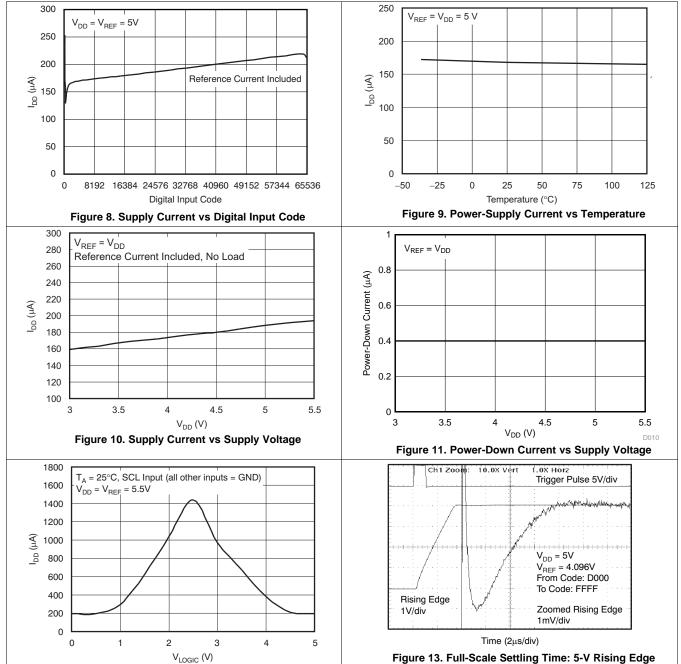

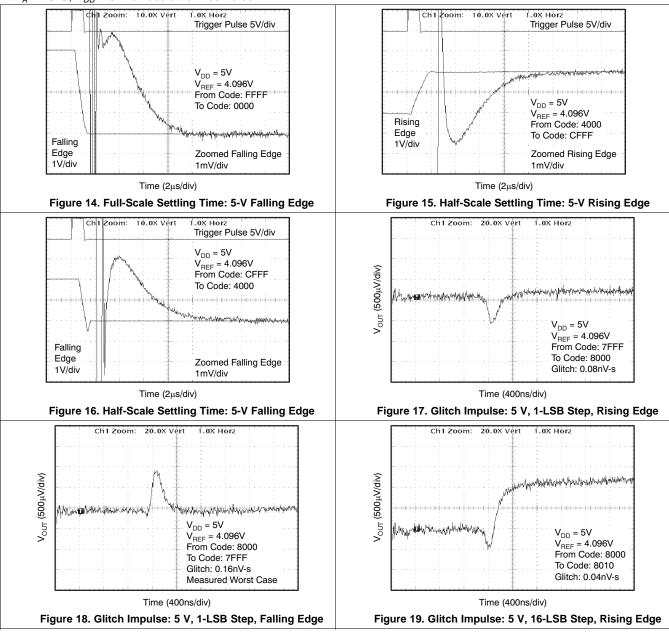

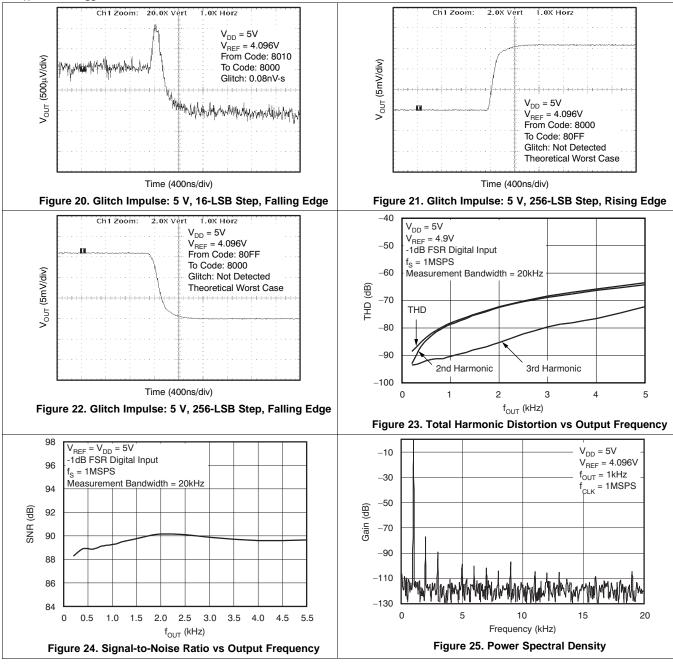

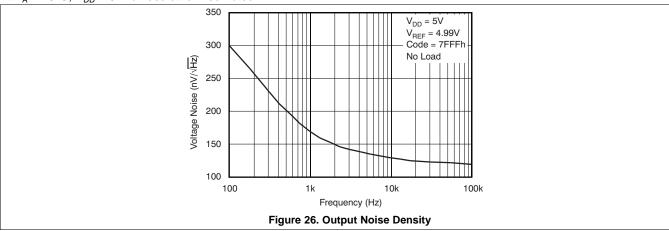

## 6.8 Typical Characteristics

At  $T_A = 25$ °C,  $V_{DD} = 5$  V unless otherwise noted.

At  $T_A = 25$ °C,  $V_{DD} = 5$  V unless otherwise noted.

Figure 12. Supply Current vs Logic Input Voltage

At  $T_A = 25$ °C,  $V_{DD} = 5$  V unless otherwise noted.

Submit Documentation Feedback

Copyright © 2016, Texas Instruments Incorporated

At  $T_A = 25$ °C,  $V_{DD} = 5$  V unless otherwise noted.

At  $T_A = 25$ °C,  $V_{DD} = 5$  V unless otherwise noted.

## 7 Detailed Description

#### 7.1 Overview

The DAC8551-Q1 and DAC6551-Q1 are small, low-power, voltage-output, 16- and 12-bit digital-to-analog converters (DACs) qualified for automotive applications. The DACx551-Q1 devices provide good linearity and minimize undesired code-to-code transient voltages. The devices use a versatile 3-wire serial interface that operates at clock rates to 30 MHz and is compatible with standard SPI, QSPI, Microwire, and digital signal processor (DSP) interfaces.

The DACx551-Q1 devices require an external reference voltage to set the output range. The devices incorporate a power-on-reset circuit that ensures the DAC output powers up at 0 V and remains there until a valid write to the device takes place. The devices contain a power-down feature, accessed over the serial interface, that reduces the current consumption to 800 nA at 5 V.

The DACx551-Q1 devices power consumption is only 800  $\mu$ W at 5 V, reducing to less than 4  $\mu$ W in power-down mode. The DACx551-Q1 devices are available in a VSSOP-8 package.

#### 7.2 Functional Block Diagram

Copyright © 2016, Texas Instruments Incorporated

### 7.3 Feature Description

#### 7.3.1 DAC Section

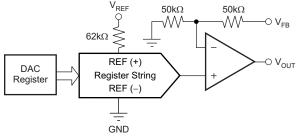

The DACx551-Q1 architecture consists of a string DAC followed by an output buffer amplifier. Figure 27 shows a block diagram of the DAC architecture.

Copyright © 2016, Texas Instruments Incorporated

Figure 27. DACx551-Q1 Architecture

The input coding to the DACx551-Q1 is straight binary, so the ideal output voltage is given by:

$$V_{OUT} = \frac{D_{IN}}{2^{n-1}} \times V_{REF} \tag{1}$$

Copyright © 2016, Texas Instruments Incorporated

#### **Feature Description (continued)**

#### where:

- n = resolution in bits; 12 (DAC6551-Q1) or 16 (DAC8551-Q1)

- D<sub>IN</sub> = decimal equivalent of the binary code that is loaded to the DAC register; it can range from 0 to 2<sup>n-1</sup>.

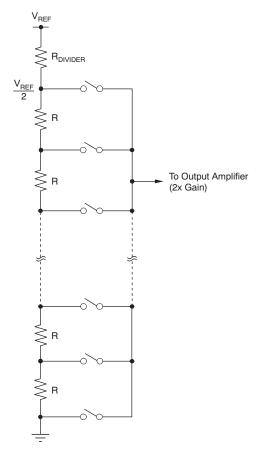

#### 7.3.1.1 Resistor String

The resistor string section is shown in Figure 28. It is simply a string of resistors, each of value R. The code loaded into the DAC register determines at which node on the string the voltage is tapped off to be fed into the output amplifier by closing one of the switches connecting the string to the amplifier.

Figure 28. Resistor String

#### 7.3.1.2 Output Amplifier

The output buffer amplifier is capable of generating rail-to-rail voltages on its output, giving an output range of 0 V to  $V_{DD}$ . It is capable of driving a load of 2  $k\Omega$  in parallel with 1000 pF to GND. The source and sink capabilities of the output amplifier can be seen in the *Typical Characteristics*. The slew rate is 1.4 V/ $\mu$ s with a full-scale setting time of 8  $\mu$ s with the output unloaded.

The inverting input of the output amplifier is brought out to the  $V_{FB}$  pin. This configuration allows for better accuracy in critical applications by tying the  $V_{FB}$  point and the amplifier output together directly at the load. Other signal conditioning circuitry may also be connected between these points for specific applications.

#### 7.3.2 Power-On Reset

The DACx551-Q1 contains a power-on-reset circuit that controls the output voltage during power up. On power up, the DAC registers are filled with zeros and the output voltages are 0 V; they remain that way until a valid write sequence is made to the DAC. The power-on reset is useful in applications where it is important to know the state of the output of the DAC while it is in the process of powering up.

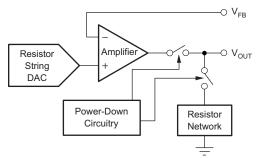

#### 7.4 Device Functional Modes

#### 7.4.1 Power-Down Modes

The DACx551-Q1 supports four separate modes of operation. These modes are programmable by setting two bits (PD1 and PD0) in the control register. Table 1 shows how the state of the bits corresponds to the mode of operation of the device.

**Table 1. Operating Modes**

| PD1 (DB17) | PD0 (DB16) | OPERATING MODE                 |

|------------|------------|--------------------------------|

| 0          | 0          | Normal operation               |

| _          | _          | Power-down modes               |

| 0          | 1          | Output typically 1 kΩ to GND   |

| 1          | 0          | Output typically 100 kΩ to GND |

| 1          | 1          | High-Z                         |

When both bits are set to 0, the device works normally with its typical current consumption of 160  $\mu$ A at 5 V. However, for the three power-down modes, the supply current falls to 800 nA at 5 V. Not only does the supply current fall, but the output stage is also internally switched from the output of the amplifier to a resistor network of known values. This configuration has the advantage that the output impedance of the device is known while it is in power-down mode. There are three different options. The output is connected internally to GND through a 1-k $\Omega$  resistor, a 100-k $\Omega$  resistor, or it is left open-circuited (High-Z). The output stage is illustrated in Figure 29.

Copyright © 2016, Texas Instruments Incorporated

Figure 29. Output Stage During Power Down

All analog circuitry is shut down when the power-down mode is activated. However, the contents of the DAC register are unaffected when in power down. The time to exit power-down is typically 2.5  $\mu$ s for  $V_{DD} = 5$  V, and 5  $\mu$ s for  $V_{DD} = 3$  V. See the *Typical Characteristics* for more information.

Copyright © 2016, Texas Instruments Incorporated

## 7.5 Programming

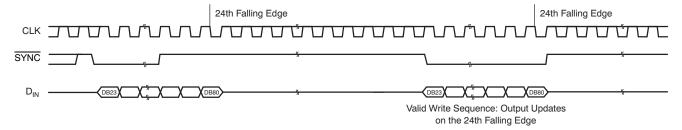

The DAC8551-Q1 and DAC6551-Q1 devices have a 3-wire serial interface ( $\overline{\text{SYNC}}$ , SCLK, and D<sub>IN</sub>), which is compatible with SPI, QSPI, and Microwire interface standards, as well as most DSPs. See the *Serial Write Operation Timing Diagram* section for an example of a typical write sequence.

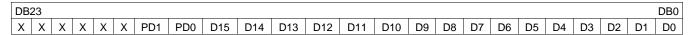

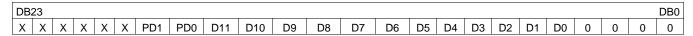

The input shift register is 24 bits wide, as shown in Figure 30 and Figure 31. The first six bits are *don't care* bits. The next two bits (PD1 and PD0) are control bits that control which mode of operation the part is in (normal mode or any one of three power-down modes). A more complete description of the various modes is located in the *Power-Down Modes* section. The next 16 bits are the left aligned data bits. These bits are transferred to the DAC register on the 24th falling edge of SCLK.

Figure 30. DAC8551-Q1 Data-Input Register Format

Figure 31. DAC6551-Q1 Data-Input Register Format

The write sequence begins by bringing the  $\overline{\text{SYNC}}$  line low. Data from the D<sub>IN</sub> line are clocked into the 24-bit shift register on each falling edge of SCLK. The serial clock frequency can be as high as 30 MHz, making the devices compatible with high-speed DSPs. On the 24th falling edge of the serial clock, the last data bit is clocked in and the programmed function is executed (that is, a change in DAC register contents and/or a change in the mode of operation).

At this point, the SYNC line may be kept low or brought high. In either case, it must be brought high for a minimum of 33 ns before the next write sequence so that a falling edge of SYNC can initiate the next write sequence. As previously mentioned, it must be brought high again just before the next write sequence.

#### 7.5.1 SYNC Interrupt

In a normal write sequence, the SYNC line is kept low for at least 24 falling edges of SCLK, and the DAC is updated on the 24th falling edge. However, if SYNC is brought high before the 24th falling edge, it acts as an interrupt to the write sequence. The shift register is reset, and the write sequence is seen as invalid. Neither an update of the DAC register contents nor a change in the operating mode occurs, as shown in Figure 32.

Figure 32. SYNC Interrupt Facility

6 Submit Documentation Feedback

Copyright © 2016, Texas Instruments Incorporated

## 8 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

## 8.1 Application Information

The DAC8551-Q1 and DAC6551-Q1 devices are AEC-Q100 qualified, low-power, ultralow-glitch, 16-bit and 12-bit DACs, respectively. The wide temperature range, low-power consumption and very low glitch of the devices make them a great choice for automotive applications such as radar and sensor conditioning.

## 8.2 Typical Applications

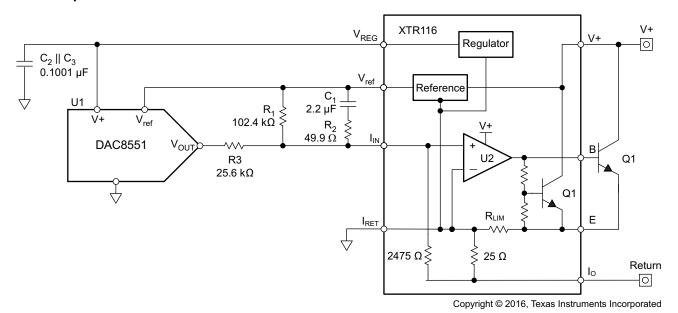

#### 8.2.1 Loop-Powered 2-Wire 4-mA to 20-mA Transmitter With XTR116

Figure 33. Loop-Powered Transmitter

#### 8.2.1.1 Design Requirements

This design is commonly referred to as a loop-powered, or 2-wire, 4 mA to 20 mA transmitter. The transmitter has only two external input terminals: a supply connection and an output, or return, connection. The transmitter communicates back to its host, typically a PLC analog input module, by precisely controlling the magnitude of its return current. In order to conform to the 4 mA to 20 mA communication standard, the complete transmitter must consume less than 4 mA of current. The DAC8551-Q1 device enables the accurate control of the loop current from 4 mA to 20 mA in 16-bit steps.

#### 8.2.1.2 Detailed Design Procedure

Although it is possible to recreate the loop-powered circuit using discrete components, the XTR116 provides simplicity and improved performance due to the matched internal resistors. The output current can be modified if necessary by looking using Equation 2.

$$I_{OUT}(Code) = \left(\frac{V_{ref} \times Code}{2^{N} \times R_{3}} + \frac{V_{REG}}{R_{1}}\right) \times \left(1 + \frac{2475 \Omega}{25 \Omega}\right)$$

(2)

## **Typical Applications (continued)**

For more details of this application, see 2-wire, 4-20mA Transmitter, EMC/EMI Tested Reference Design (TIDUAO7). It covers in detail the design of this circuit as well as how to protect it from EMC/EMI tests.

### 8.2.1.3 Application Curves

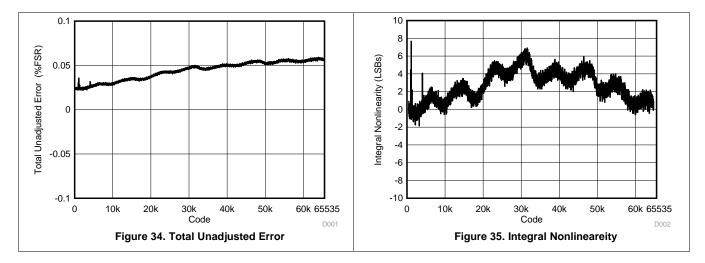

Total unadjusted error (TUE) is a good estimate for the performance of the output as shown in Figure 34. The linearity of the output or INL is in Figure 35.

## 8.2.2 Bipolar Operation Using the DAC8551-Q1 Device

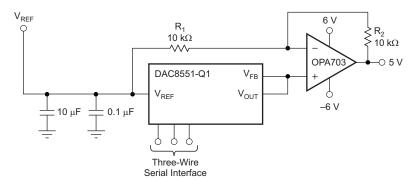

The DAC8551-Q1 device has been designed for single-supply operation, but a bipolar output range is also possible using the circuit in Figure 36. The circuit shown gives an output voltage range of ±V<sub>REF</sub>. Rail-to-rail operation at the amplifier output is achievable using an OPA703 as the output amplifier.

Figure 36. Bipolar Output Range

The output voltage for any input code can be calculated as follows:

$$V_{O} = \left[ V_{REF} \times \left( \frac{D}{65536} \right) \times \left( \frac{R_1 + R_2}{R_1} \right) - V_{REF} \times \left( \frac{R_2}{R_1} \right) \right]$$

(3)

where D represents the input code in decimal (0-65,535)

with  $V_{REF} = 5V$ ,  $R_1 = R_2 = 10 \text{ k}\Omega$ .

$$V_{O} = \left(\frac{10 \times D}{65536}\right) - 5 \text{ V}$$

(4)

Using this example, an output voltage range of  $\pm 5$  V with 0000h corresponding to a -5 V output and FFFFh corresponding to a 5 V output can be achieved. Similarly, using  $V_{REF} = 2.5$  V, a  $\pm 2.5$  V output voltage range can be achieved.

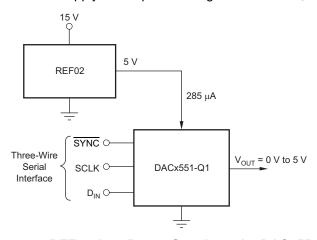

#### 8.2.3 Using the REF02 As a Power Supply for the DACx551-Q1

Due to the extremely low supply current required by the DACx551-Q1, an alternative option is to use a precision reference such as the REF02 device to supply the required voltage to the device, as illustrated in Figure 37.

Figure 37. REF02 As a Power Supply to the DACx551-Q1

This configuration is especially useful if the power supply is quite noisy or if the system supply voltages are at some value other than 5 V. The REF02 device outputs a steady supply voltage for the device. If the REF02 device is used, the current it must supply to the device is 200  $\mu$ A. This configuration is with no load on the output of the DAC. When a DAC output is loaded, the REF02 also must supply the current to the load.

The total current required (with a 5  $k\Omega$  load on the DAC output) is:

$$200\mu A + \frac{5V}{5k\Omega} = 1.2mA \tag{5}$$

The load regulation of the REF02 is typically 0.005%/mA, resulting in an error of 299  $\mu$ V for the 1.2 mA current drawn from it. This value corresponds to a 3.9 LSB error.

Copyright © 2016, Texas Instruments Incorporated

## 8.3 System Examples

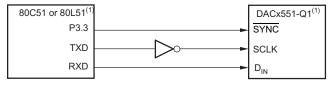

#### 8.3.1 Interface From the DACx551-Q1 to 8051

See Figure 38 for a serial interface between the DACx551-Q1 and a typical 8051-type microcontroller. The setup for the interface is as follows: TXD of the 8051 drives SCLK of the DACx551-Q1, whereas RXD drives the serial data line of the device. The SYNC signal is derived from a bit-programmable pin on the port of the 8051. In this case, port line P3.3 is used. When data are to be transmitted to the DACx551-Q1, P3.3 is taken low. The 8051 transmits data in 8-bit bytes; thus, only eight falling clock edges occur in the transmit cycle. To load data to the DAC, P3.3 is left low after the first eight bits are transmitted, then a second write cycle is initiated to transmit the second byte of data. P3.3 is taken high following the completion of the third write cycle. The 8051 outputs the serial data in a format that has the LSB first. The DACx551-Q1 requires data with the MSB as the first bit received. Therefore, the 8051 transmit routine must take this into account, and *mirror* the data as needed.

NOTE: (1) Additional pins omitted for clarity.

Figure 38. Interface From the DACx551-Q1 to 80C51 or 80L51

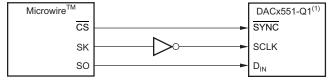

#### 8.3.2 Interface From the DACx551-Q1 to Microwire

Figure 39 shows an interface between the DACx551-Q1 and any Microwire-compatible device. Serial data are shifted out on the falling edge of the serial clock and is clocked into the DACx551-Q1 on the rising edge of the SK signal.

NOTE: (1) Additional pins omitted for clarity.

Figure 39. Interface From the DACx551-Q1 to Microwire

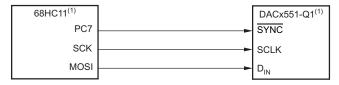

#### 8.3.3 Interface From the DACx551-Q1 to 68HC11

Figure 40 shows a serial interface between the DACx551-Q1 and the 68HC11 microcontroller. SCK of the 68HC11 drives SCLK of the DACx551-Q1, whereas the MOSI output drives the serial data line of the DAC. The SYNC signal is derived from a port line (PC7), similar to the 8051 diagram.

NOTE: (1) Additional pins omitted for clarity.

Figure 40. Interface From the DACx551-Q1 to 68HC11

The 68HC11 should be configured so that its CPOL bit is 0 and its CPHA bit is 1. This configuration causes data appearing on the MOSI output to be valid on the falling edge of SCK. When data are being transmitted to the DAC, the SYNC line is held low (PC7). Serial data from the 68HC11 are transmitted in 8-bit bytes with only eight falling clock edges occurring in the transmit cycle. (Data are transmitted MSB first.) In order to load data to the DACx551-Q1, PC7 is left low after the first eight bits are transferred, then a second and third serial write operation are performed to the DAC. PC7 is taken high at the end of this procedure.

Product Folder Links: DAC8551-Q1 DAC6551-Q1

## 9 Power Supply Recommendations

The DACx551-Q1 can operate within the specified supply voltage range of 3 V to 5.5 V. The power applied to  $V_{DD}$  should be well-regulated and low-noise. Switching power supplies and dc/dc converters often have high-frequency glitches or spikes riding on the output voltage. In addition, digital components can create similar high-frequency spikes. This noise can easily couple into the DAC output voltage through various paths between the power connections and analog output. In order to further minimize noise from the power supply, a strong recommendation is to include a 1- $\mu$ F to 10- $\mu$ F capacitor and 0.1- $\mu$ F bypass capacitor. The current consumption on the  $V_{DD}$  pin, the short-circuit current limit, and the load current for the device is listed in the Electrical Characteristics table. The power supply must meet the aforementioned current requirements.

## 10 Layout

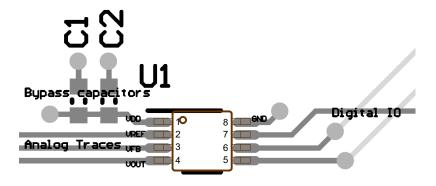

## 10.1 Layout Guidelines

A precision analog component requires careful layout, adequate bypassing, and clean, well-regulated power supplies.

The DACx551-Q1 offers single-supply operation, and is often used in close proximity with digital logic, microcontrollers, microprocessors, and digital signal processors. The more digital logic present in the design and the higher the switching speed, the more difficult it is to keep digital noise from appearing at the output.

Due to the single ground pin of the DACx551-Q1, all return currents, including digital and analog return currents for the DAC, must flow through a single point. Ideally, GND would be connected directly to an analog ground plane. This plane would be separate from the ground connection for the digital components until they were connected at the power-entry point of the system.

As with the GND connection,  $V_{DD}$  should be connected to a power-supply plane or trace that is separate from the connection for digital logic until they are connected at the power-entry point. In addition, a 1  $\mu$ F to 10  $\mu$ F capacitor and 0.1  $\mu$ F bypass capacitor are strongly recommended. In some situations, additional bypassing may be required, such as a 100  $\mu$ F electrolytic capacitor or even a *Pi* filter made up of inductors and capacitors—all designed to essentially low-pass filter the 5 V supply, removing the high-frequency noise.

#### 10.2 Layout Example

Figure 41. Layout Diagram

## 11 Device and Documentation Support

### 11.1 Documentation Support

#### 11.1.1 Related Documentation

2-wire, 4-20mA Transmitter, EMC/EMI Tested Reference Design (TIDUAO7)

## 11.2 Receiving Notification of Documentation Updates

To receive notification of documentation updates, navigate to the device product folder on ti.com. In the upper right corner, click on Alert me to register and receive a weekly digest of any product information that has changed. For change details, review the revision history included in any revised document.

## 11.3 Community Resources

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

TI E2E™ Online Community TI's Engineer-to-Engineer (E2E) Community. Created to foster collaboration among engineers. At e2e.ti.com, you can ask questions, share knowledge, explore ideas and help solve problems with fellow engineers.

Design Support TI's Design Support Quickly find helpful E2E forums along with design support tools and contact information for technical support.

#### 11.4 Trademarks

E2E is a trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

#### 11.5 Electrostatic Discharge Caution

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

#### 11.6 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

## 12 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the mostcurrent data available for the designated devices. This data is subject to change without notice and without revision of this document. For browser-based versions of this data sheet, see the left-hand navigation pane.

Product Folder Links: DAC8551-Q1 DAC6551-Q1

22

www.ti.com 1-Mar-2025

#### PACKAGING INFORMATION

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp       | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|--------|--------------|--------------------|------|----------------|--------------|-------------------------------|---------------------|--------------|-------------------------|---------|

| DAC6551AQDGKRQ1  | ACTIVE | VSSOP        | DGK                | 8    | 2500           | RoHS & Green | NIPDAUAG                      | Level-2-260C-1 YEAR | -40 to 125   | D61Q                    | Samples |

| DAC8551AQDGKRQ1  | ACTIVE | VSSOP        | DGK                | 8    | 2500           | RoHS & Green | NIPDAU   NIPDAUAG             | Level-2-260C-1 YEAR | -40 to 125   | D81Q                    | Samples |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

**Green:** TI defines "Green" to mean the content of Chlorine (Cl) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# **PACKAGE OPTION ADDENDUM**

www.ti.com 1-Mar-2025

#### OTHER QUALIFIED VERSIONS OF DAC8551-Q1:

NOTE: Qualified Version Definitions:

• Catalog - TI's standard catalog product

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 10-Jan-2024

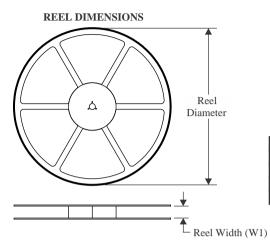

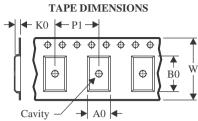

## TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

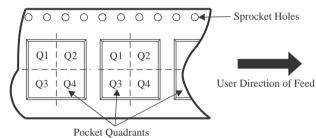

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device          |       | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-----------------|-------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| DAC6551AQDGKRQ1 | VSSOP | DGK                | 8 | 2500 | 330.0                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 10-Jan-2024

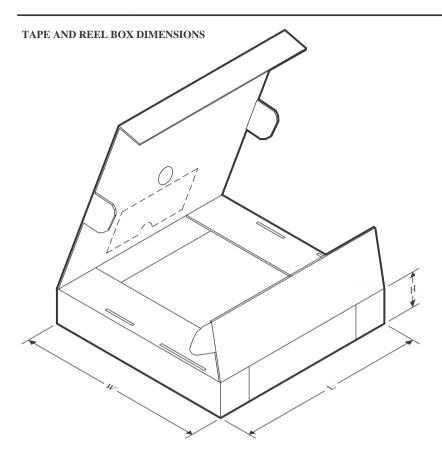

### \*All dimensions are nominal

| Device          | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |  |

|-----------------|--------------|-----------------|------|------|-------------|------------|-------------|--|

| DAC6551AQDGKRQ1 | VSSOP        | DGK             | 8    | 2500 | 350.0       | 350.0      | 43.0        |  |

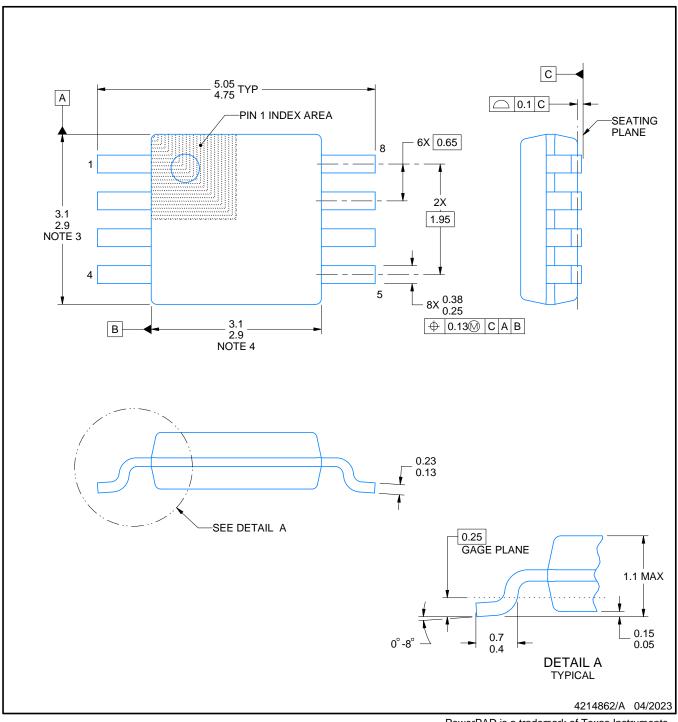

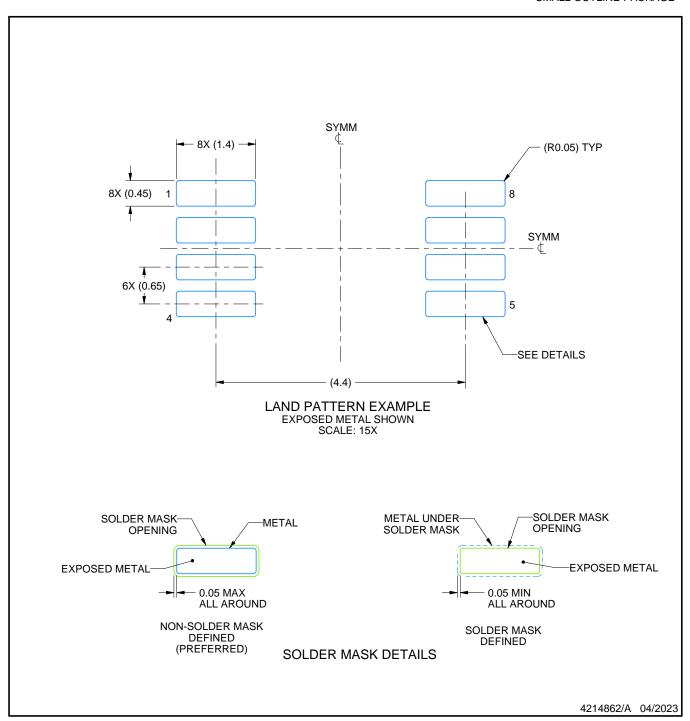

SMALL OUTLINE PACKAGE

#### NOTES:

PowerPAD is a trademark of Texas Instruments.

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm per side.

- 4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side.

- 5. Reference JEDEC registration MO-187.

SMALL OUTLINE PACKAGE

NOTES: (continued)

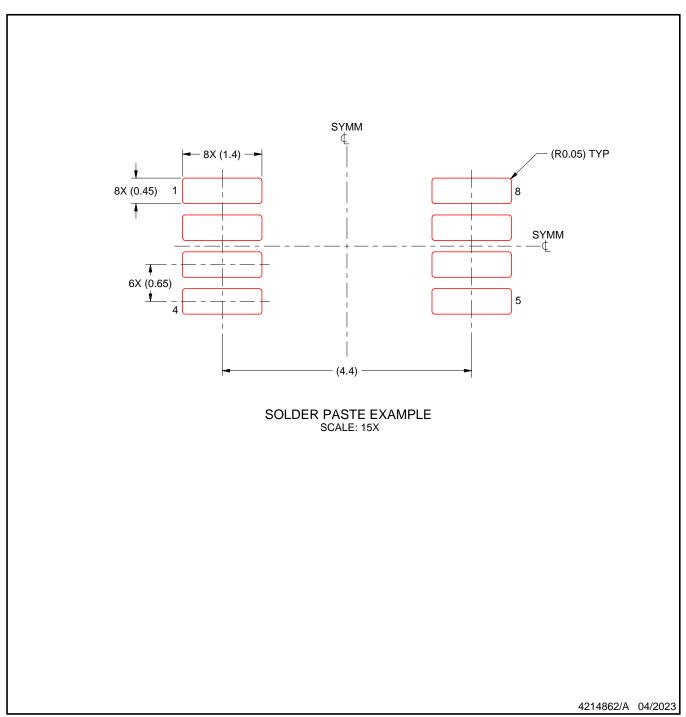

- 6. Publication IPC-7351 may have alternate designs.

- 7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

- 8. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

- 9. Size of metal pad may vary due to creepage requirement.

SMALL OUTLINE PACKAGE

NOTES: (continued)

- 11. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 12. Board assembly site may have different recommendations for stencil design.

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2025. Texas Instruments Incorporated