# **Fully Integrated Power Management with Switch Mode Charger**

Check for Samples: TWL6030

### **FEATURES**

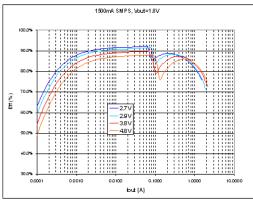

- · Seven highly efficient 6-MHz buck converters

- Two 0.6 to 2.1 V @ 1.6 A

- Five 0.6 to 2.1 V @ 1.0 A

- 11 General-purpose LDOs

- Six 1.0 to 3.3 V @ 0.2 A with battery or preregulated supply (One can be used as a vibrator driver.)

- One 1.0 to 3.3 V @ 50 mA with battery or preregulated supply

- One low noise 1.0 to 3.3 V @ 50 mA with battery or preregulated supply

- 3.3 V @ 35 mA USB LDO

- One LDO for TWL6030 internal use

- One LDO for internal and external use

- USB OTG module

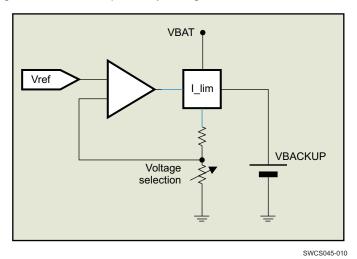

- Backup battery charger

- 10-bit ADC with 17 input channels

- 13-bit Coulomb counter with four programmable integration periods

- Low power consumption

- 5 µA in backup mode

- 20 µA in wait-on mode

- 110 µA in deep sleep, with two DCDCs active

- RTC with alarm wake-up mechanism

- SIM and MMC card detections

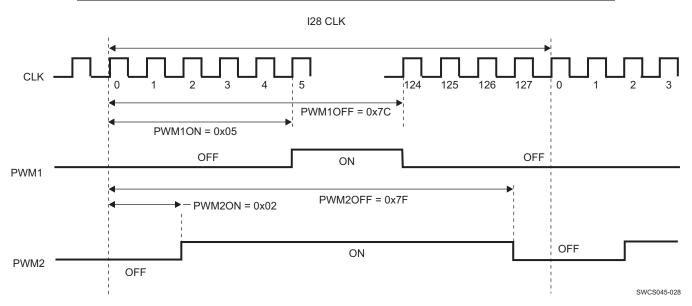

- Two digital PWM outputs

- Thermal monitoring

- High-temperature warning

- Thermal shutdown

#### Control

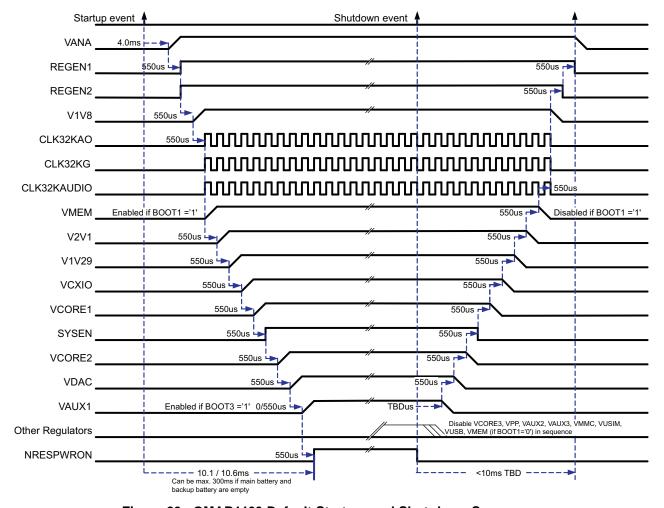

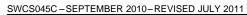

- Configurable power-up and power-down sequences (EPROM programmable)

- Three output signals that can be included in the start-up sequence

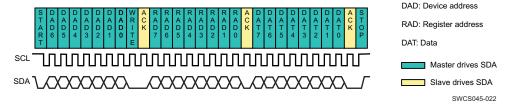

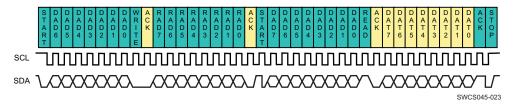

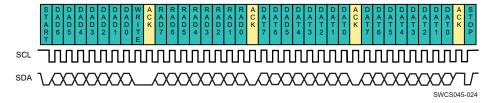

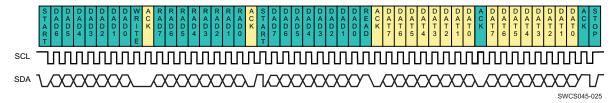

- Two I<sup>2</sup>C™ interfaces

- All resources configurable by I<sup>2</sup>C

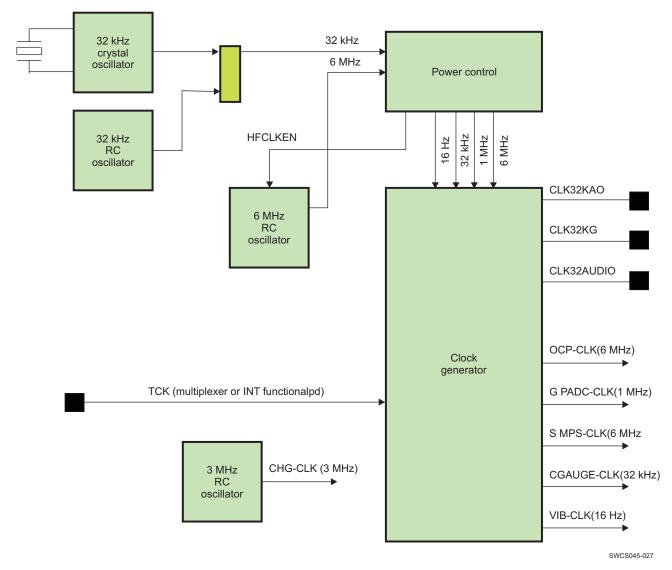

- Clock management 32-kHz output

- Battery charger 1.5 A

- Charger for single-cell Li-lon and Li-Polymer battery packs

- Switched mode charger with integrated power FET for up to 1.5-A current

- High-accuracy voltage and current regulation

- Safety timer and reset control

- Thermal regulation protection

- Input/output overvoltage protection

- Charging indicator LED driver

- Boost mode operation for USB OTG

- Compliant with:

- USB 2.0

- OTG and EH 2.0

- YD/T 1591-2006

- USB battery charging 1.1 and 1.2

- Japanese battery charging requirements

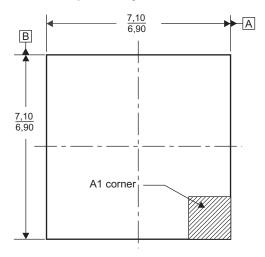

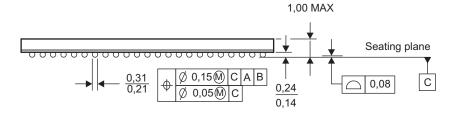

- Package 7 mm x 7 mm 187-pin nFBGA

### **APPLICATIONS**

- · Mobile phones and smart phones

- Gaming handsets

- Portable media players

- Portable navigation systems

- Handheld devices

- Tablets

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

SmartReflex is a trademark of Texas Instruments.

MIPI is a registered trademark of Mobil Industry Processor Interface.

#### DESCRIPTION

The TWL6030 device is an integrated power-management integrated circuit (IC) for applications powered by a rechargeable battery. The device provides seven configurable step-down converters with up to 1.6A capability for memory, processor core, I/O, auxiliary, preregulation for LDOs, etc. The device also contains 11 LDO regulators that can be supplied from a battery or a preregulated supply. Power-up/power-down controller is configurable and can support any power-up/power-down sequences (EPROM based). The real-time clock (RTC) provides a 32-kHz output buffer, second/minute/hour/day/month/year information, and alarm wake up. The TWL6030 supports 32-kHz clock generation based on a crystal oscillator. The device integrates a switched-mode charger allowing faster battery charge, higher efficiency, and less power dissipation.

The TWL6030 device generates power supplies for OMAP™ 4 processors and operates together with the TWL6040 device, which includes all audio and related detection features. For audio IC parameters, see the TWL6040 datasheet. In addition, the TWL6030 device can be used as a power management multichannel IC (PMIC) for several other processors, thanks to the programmable startup/shutdown controller and default supply voltage levels. The TWL6030 is available in an nFBGA package, 7.0 mm x 7.0 mm, with a 0.4-mm ball pitch.

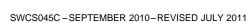

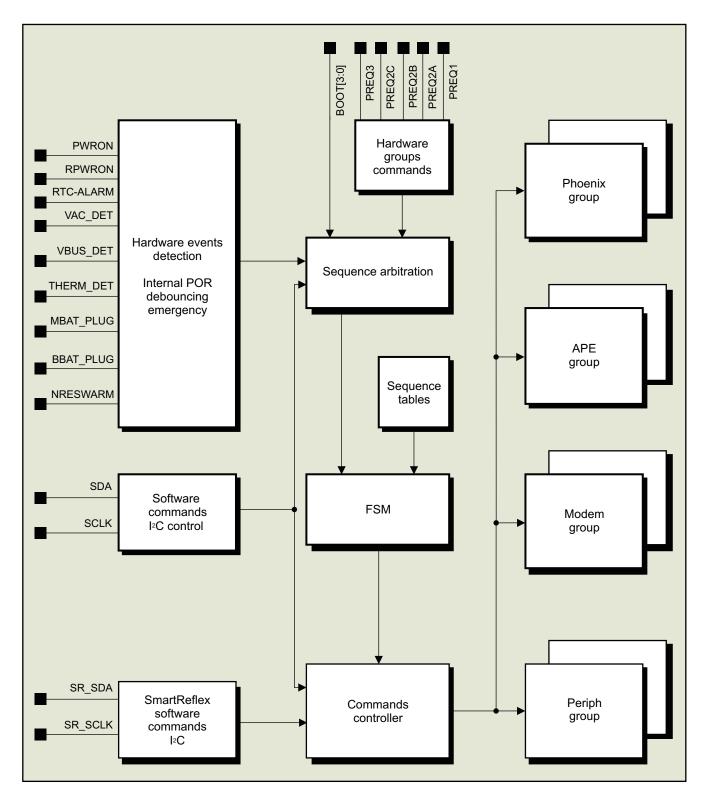

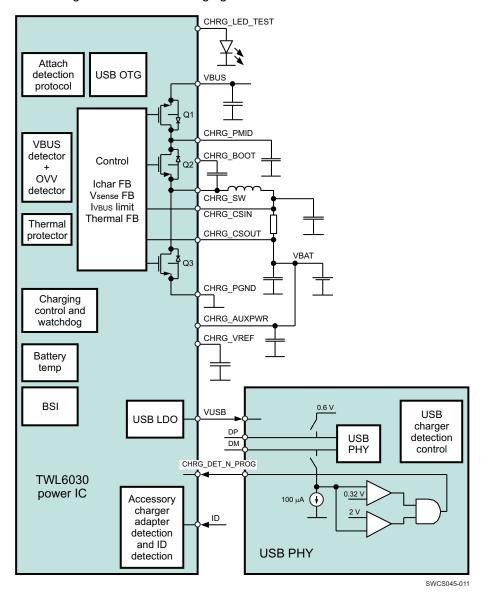

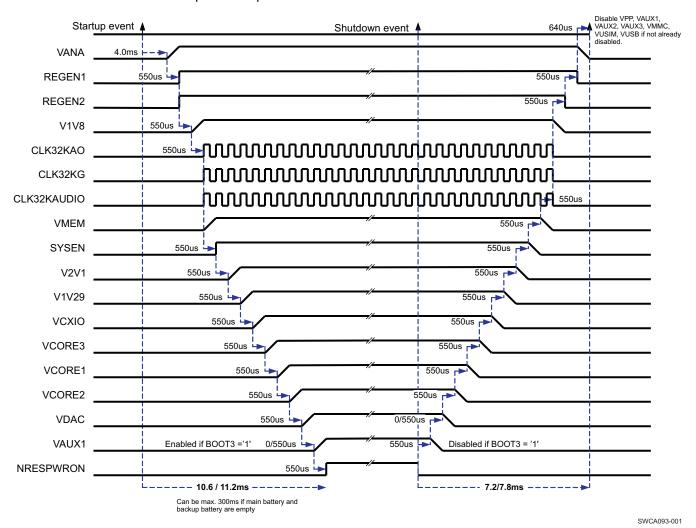

Figure 1 shows the TWL6030 block diagram.

# **Table 1. Part Number Differentiation**

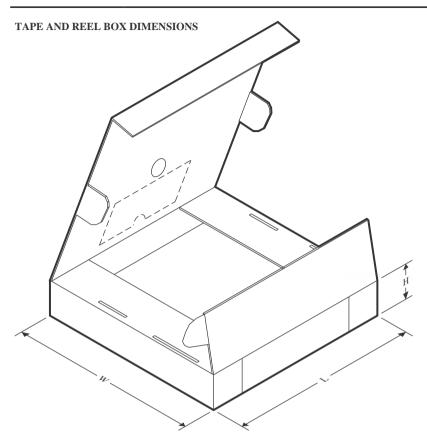

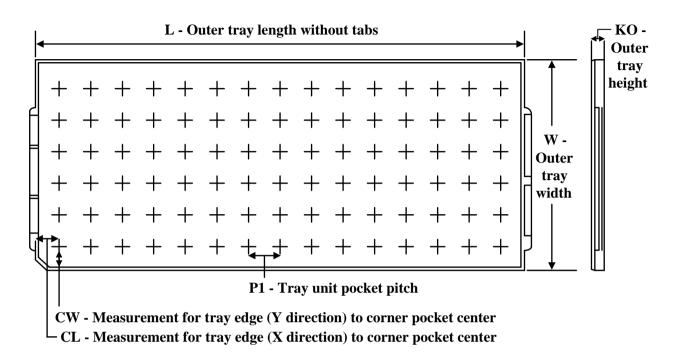

| PART NUMBER | ORDERING           | OMAP VERSION  | PRIMARY<br>WATCHDOG | HW CHARGER<br>WATCHDOG | TRANSPORT MEDIA QUANTITY |

|-------------|--------------------|---------------|---------------------|------------------------|--------------------------|

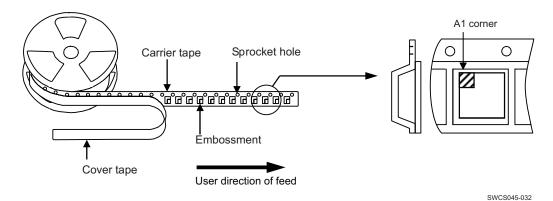

| TWL6030     | TWL6030B107CMRR    | OMAP4430      | Disabled            | Disabled               | Tape and reel, 2500      |

| TWL6030     | TWL6030B107CMR     | OMAP4430      | Disabled            | Disabled               | Trays, 260               |

| TWL6030     | (P)TWL6030B1AECMRR | OMAP4430      | Disabled            | Enabled                | Tape and reel, 2500      |

| TWL6030     | (P)TWL6030B1AECMR  | OMAP4430      | Disabled            | Enabled                | Trays, 260               |

| TWL6030     | (P)TWL6030B1A0CMRR | OMAP4430      | Enabled             | Enabled                | Tape and reel, 2500      |

| TWL6030     | (P)TWL6030B1A0CMR  | OMAP4430      | Enabled             | Enabled                | Trays, 260               |

| TWL6030     | TWL6030B1A4CMRR    | OMAP4460/4470 | Disabled            | Disabled               | Tape and reel, 2500      |

| TWL6030     | TWL6030B1A4CMR     | OMAP4460/4470 | Disabled            | Disabled               | Trays, 260               |

| TWL6030     | (P)TWL6030B1AFCMRR | OMAP4460/4470 | Disabled            | Enabled                | Tape and reel, 2500      |

| TWL6030     | (P)TWL6030B1AFCMR  | OMAP4460/4470 | Disabled            | Enabled                | Trays, 260               |

| TWL6030     | (P)TWL6030B1AACMRR | OMAP4460/4470 | Enabled             | Enabled                | Tape and reel, 2500      |

| TWL6030     | (P)TWL6030B1AACMR  | OMAP4460/4470 | Enabled             | Enabled                | Trays, 260               |

### **DEVICE INFORMATION**

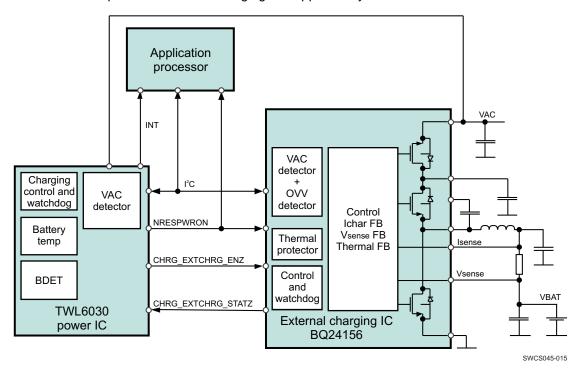

Figure 1. TWL6030 Block Diagram

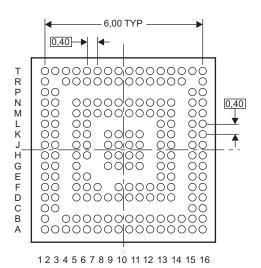

Table 2 presents the ball description of the TWL6030 device. Figure 2 shows the ball mapping from the top view.

# **Table 2. Ball Description**

| NAME                   | BALL                                                                      | TYPE    | I/O <sup>(1)</sup> | DESCRIPTION                                                                                                    | CONNECTION IF                                                     | PU/PD <sup>(2)</sup> |  |

|------------------------|---------------------------------------------------------------------------|---------|--------------------|----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|----------------------|--|

| CHARGER                |                                                                           |         |                    |                                                                                                                | 1101 0025                                                         |                      |  |

| CHRG_AUXPWR            | E6                                                                        | Analog  | 1                  | Switched charger auxiliary power supply, connected to the battery pack to provide power in high-impedance mode | Ground                                                            | _                    |  |

| CHRG_BOOT              | G2                                                                        | Analog  | 0                  | Switched charger boot-strapped capacitor for the high-side MOSFET gate driver                                  | Floating                                                          | _                    |  |

| CHRG_CSIN              | E4                                                                        | Analog  | I                  | Switched charger current-sense input                                                                           | Ground                                                            |                      |  |

| CHRG_CSOUT             | RG_CSOUT D4 Analog I Switched charger battery voltage/current sense input |         | Ground             |                                                                                                                |                                                                   |                      |  |

| CHRG_DET_N             | E5                                                                        | Analog  | I                  | USB charging port detection signal from USB PHY                                                                | Ground                                                            |                      |  |

| CHRG_EXTCHRG_EN Z      | J7                                                                        | Digital | 0                  | Output control signal to an external VAC charger                                                               | Floating                                                          |                      |  |

| CHRG_EXTCHRG_ST<br>ATZ | H7                                                                        | Digital | ı                  | External charger status input pin                                                                              | Floating or tied to<br>VRTC (fixed<br>internal pullup to<br>VRTC) | *PU<br>70–190 kΩ     |  |

| CHRG_LED_IN            | D6                                                                        | Power   | 1                  | LED indicator input supply                                                                                     | Ground                                                            |                      |  |

| CHRG_LED_TEST          | D5                                                                        | Analog  | I/O                | External LED driver output/dedicated charger TEST ball                                                         | Ground or floating                                                |                      |  |

| CHRG_PGND_B1           | A5                                                                        |         |                    |                                                                                                                |                                                                   |                      |  |

| CHRG_PGND_B2           | A6                                                                        |         |                    |                                                                                                                |                                                                   |                      |  |

| CHRG_PGND_B3           | B6                                                                        | Ground  | I                  | Switched charger power ground                                                                                  | Ground                                                            | _                    |  |

| CHRG_PGND_B4           | B5                                                                        |         |                    |                                                                                                                |                                                                   |                      |  |

| CHRG_PMID_B1           | E1                                                                        |         |                    |                                                                                                                |                                                                   |                      |  |

| CHRG_PMID_B2           | F1                                                                        | A 1     |                    | Switched charger connection point between                                                                      | =, .,                                                             |                      |  |

| CHRG_PMID_B3           | E2                                                                        | Analog  | 0                  | reverse blocking MOSFET and high-side switching MOSFET                                                         | Floating                                                          | _                    |  |

| CHRG_PMID_B4           | F2                                                                        |         |                    | 5                                                                                                              |                                                                   |                      |  |

| CHRG_SW_B1             | А3                                                                        |         |                    |                                                                                                                |                                                                   |                      |  |

| CHRG_SW_B2             | A4                                                                        | D       |                    | Switched charger internal switch to output                                                                     | Flooring                                                          |                      |  |

| CHRG_SW_B3             | B4                                                                        | Power   | 0                  | inductor connection                                                                                            | Floating                                                          | _                    |  |

| CHRG_SW_B4             | В3                                                                        |         |                    |                                                                                                                |                                                                   |                      |  |

| CHRG_VREF              | F5                                                                        | Analog  | 0                  | Switched charger internal bias regulator voltage                                                               | Floating                                                          | _                    |  |

| VAC                    | F4                                                                        | Power   |                    | Input supply from an external VAC charger                                                                      | Ground (if not used in BBS)                                       | _                    |  |

| VBUS_B1                | C1                                                                        |         |                    |                                                                                                                | Ground (Must be                                                   |                      |  |

| VBUS_B2                | D1                                                                        |         |                    |                                                                                                                | connected to<br>VBUS if VBUS                                      |                      |  |

| VBUS_B3                | C2                                                                        | Power   | I/O                | VBUS input voltage, USB battery charger power                                                                  | detection from                                                    | _                    |  |

| VBUS_B4                | D2                                                                        |         |                    | supply                                                                                                         | PMIC is needed;<br>for example, for<br>USB bootupt)               |                      |  |

| POWER SUPPLIES         |                                                                           |         | _                  |                                                                                                                |                                                                   |                      |  |

<sup>(1)</sup> I = Input; O = Output

(2) PU/PD shows the pullup/down resistors on digital input lines. An asterisk indicates the default option.

| NAME         | BALL | TYPE      | I/O <sup>(1)</sup> | DESCRIPTION                                                                 | CONNECTION IF NOT USED                                               | PU/PD <sup>(2)</sup> |

|--------------|------|-----------|--------------------|-----------------------------------------------------------------------------|----------------------------------------------------------------------|----------------------|

| GND_ANA_B1   | N8   |           |                    |                                                                             |                                                                      |                      |

| GND_ANA_B2   | M10  |           |                    |                                                                             |                                                                      |                      |

| GND_ANA_B3   | E11  |           |                    |                                                                             |                                                                      |                      |

| GND_ANA_B4   | L13  | Ground    | I                  | Analog power ground                                                         | Ground                                                               | _                    |

| GND_ANA_B5   | D9   |           |                    |                                                                             |                                                                      |                      |

| GND_ANA_B6   | H4   |           |                    |                                                                             |                                                                      |                      |

| GND_ANA_B7   | G7   |           |                    |                                                                             |                                                                      |                      |

| GND_DIG_VIO  | M8   | Ground    | I                  | VIO digital ground                                                          | Ground                                                               | -                    |

| GND_DIG_VRTC | G4   | Ground    | I                  | VRTC digital ground                                                         | Ground                                                               | -                    |

| PBKG_B11     | T1   |           |                    |                                                                             |                                                                      |                      |

| PBKG_B12     | T2   |           |                    |                                                                             |                                                                      |                      |

| PBKG_B13     | R1   |           |                    |                                                                             |                                                                      |                      |

| PBKG_B2      | H5   |           |                    |                                                                             |                                                                      |                      |

| PBKG_B31     | T16  |           |                    |                                                                             |                                                                      |                      |

| PBKG_B32     | T15  |           |                    |                                                                             |                                                                      |                      |

| PBKG_B33     | R16  | Substrate | I                  | Substrate ground                                                            | Ground                                                               | _                    |

| PBKG_B41     | A1   |           |                    |                                                                             |                                                                      |                      |

| PBKG_B42     | A2   |           |                    |                                                                             |                                                                      |                      |

| PBKG_B43     | B1   |           |                    |                                                                             |                                                                      |                      |

| PBKG_B51     | A16  |           |                    |                                                                             |                                                                      |                      |

| PBKG_B53     | B16  |           |                    |                                                                             |                                                                      |                      |

| VDD_B1       | N9   |           |                    |                                                                             |                                                                      |                      |

| VDD_B2       | G13  | _         |                    |                                                                             |                                                                      |                      |

| VDD_B3       | В9   | Power     | I                  | Analog input voltage supply                                                 | N/A                                                                  | _                    |

| VDD_B4       | L4   |           |                    |                                                                             |                                                                      |                      |

| VIO          | M9   | Power     | I                  | The TWL6030 device digital I/O input supply voltage (1.8 V)                 | N/A                                                                  | -                    |

| VPROG        | G10  | Power     | I                  | EPROM programming voltage                                                   | Ground                                                               | -                    |

| VBACKUP      | E10  | Analog    | I                  | Backup battery input voltage                                                | Ground (prefered) or Floating                                        | _                    |

| VBAT         | B13  | Power     | I                  | Battery voltage sense line                                                  | N/A                                                                  | _                    |

| CLOCKING     | *    |           | •                  |                                                                             |                                                                      |                      |

| CLK32KAO     | H10  | Digital   | 0                  | 32-kHz digital output clock always on when VIO input supply is present      | Floating                                                             | -                    |

| CLK32KAUDIO  | E9   | Digital   | 0                  | 32-kHz digital gated output clock toward the audio device                   | Floating                                                             | -                    |

| CLK32KG      | J10  | Digital   | 0                  | 32-kHz digital gated output clock controlled by software                    | Floating                                                             | П                    |

| OSC32KCAP    | E8   | Analog    | 0                  | VRTC power supply external filtering cap for the 32-kHz crystal oscillator  | Floating                                                             | П                    |

| OSC32KIN     | A10  | Analog    | I                  | 32-kHz crystal oscillator input or digital clock input                      | Digital clock<br>input,analog clock<br>input                         | -                    |

| OSC32KOUT    | A8   | Analog    | 0                  | 32-kHz crystal oscillator output or floating in case of digital clock input | Floating when digital clock input, capacitor when analog clock input | _                    |

| REFERENCES   | 1    | 1         |                    |                                                                             |                                                                      |                      |

| IREF         | H12  | Analog    | I/O                | Reference current generation                                                | N/A                                                                  | _                    |

| NAME           | BALL | TYPE    | I/O <sup>(1)</sup> | DESCRIPTION                                                                                                       | CONNECTION IF NOT USED                                                                               | PU/PD <sup>(2)</sup>  |

|----------------|------|---------|--------------------|-------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-----------------------|

| REFGND_B1      | A9   | Ground  | ı                  | System reference ground                                                                                           | Ground                                                                                               |                       |

| REFGND_B2      | F12  | Ground  | !                  | dystem reference ground                                                                                           | Ground                                                                                               |                       |

| VBG            | G12  | Analog  | 0                  | Band gap output reference voltage                                                                                 | N/A                                                                                                  | -                     |

| TESTING        |      |         |                    |                                                                                                                   |                                                                                                      |                       |

| TESTEN         | J8   | Digital | I                  | Test mode enable                                                                                                  | Ground (fixed internal pulldown to ground)                                                           | *PD<br>170–950 kΩ     |

| TESTV          | A15  | Analog  | 0                  | Internal voltages sense line                                                                                      | Floating                                                                                             |                       |

| SYSTEM CONTROL |      |         |                    | ,                                                                                                                 |                                                                                                      |                       |

| CTLI2C_SCL     | M4   | Digital | I/O                | Control I <sup>2</sup> C serial clock (I <sup>2</sup> C voltage level is set by an external pullup.)              | N/A                                                                                                  | PU<br>0.46–1.76<br>kΩ |

| CTLI2C_SDA     | N4   | Digital | I/O                | Control I <sup>2</sup> C serial bidirectional data (I <sup>2</sup> C voltage level is set by an external pullup.) | N/A                                                                                                  | PU<br>0.46–1.76<br>kΩ |

| INT            | K10  | Digital | 0                  | Maskable interrupt output request to the host processor                                                           | Floating                                                                                             | _                     |

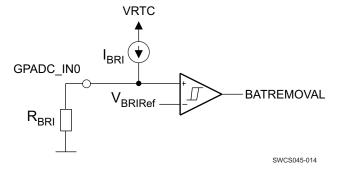

| BATREMOVAL     | L12  | Digital | 0                  | Battery removal indicator                                                                                         | Floating                                                                                             |                       |

| BOOT0          | H8   | Digital | I                  | Boot ball 0 for power-up sequence selection                                                                       | Ground or VRTC                                                                                       |                       |

| BOOT1          | G8   | Digital | I                  | Boot ball 1 for power-up sequence selection                                                                       | Ground or VRTC                                                                                       |                       |

| BOOT2          | G9   | Digital | I                  | Boot ball 2 for power-up sequence selection                                                                       | Ground or VRTC                                                                                       |                       |

| BOOT3          | H9   | Digital | I                  | Boot ball 3 for power-up sequence selection                                                                       | Ground or VRTC                                                                                       |                       |

| NRESPWRON      | N5   | Digital | 0                  | System reset/power on output                                                                                      | Floating                                                                                             | *PU<br>70–190 kΩ      |

| NRESWARM       | M5   | Digital | 1                  | Warm reset input                                                                                                  | Floating (fixed internal pullup to VIO)                                                              | PU<br>170–950 kΩ      |

| PREQ1          | J9   | Digital | ı                  | Peripheral 1 power request input                                                                                  | Floating (use of internal PU/PD) or tied to common ground or VIO (depending on selected sensitivity) | PU/*PD<br>170–950 kΩ  |

| PREQ2A         | K9   | Digital | I                  | Peripheral 2A power request input                                                                                 | Floating (use of internal PU/PD) or tied to common ground or VIO (depending on selected sensitivity) | PU/*PD<br>170–950 kΩ  |

| PREQ2B         | K8   | Digital | I                  | Peripheral 2B power request input                                                                                 | Floating (use of internal PU/PD) or tied to common ground or VIO (depending on selected sensitivity) | PU/*PD<br>170–950 kΩ  |

| PREQ2C         | M7   | Digital | I                  | Peripheral 2C power request input                                                                                 | Floating (use of internal PU/PD) or tied to common ground or VIO (depending on selected sensitivity) | PU/*PD<br>170–950 kΩ  |

| PREQ3    Perpheral 3 power request input   Ground or VID (depending on selected sensitivity)   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950   170–950                                                                                            | NAME           | BALL | TYPE    | I/O <sup>(1)</sup> | DESCRIPTION                                | CONNECTION IF NOT USED                                                             | PU/PD <sup>(2)</sup> |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------|---------|--------------------|--------------------------------------------|------------------------------------------------------------------------------------|----------------------|

| PWM2         M12         Digital         O         Pulse width modulation 2         Floating         —           PWRON         L5         Digital         I         External on-button switch-on event (primary input to Isunch system wakeup)         N/A         56-3701           REGEN1         K7         Digital         O         External regulator enable 1         Floating         —           REGEN2         J5         Digital         O         External regulator enable 2         Floating         —           RPWRON         K5         Digital         O         External regulator enable 2         Floating (fixed internal pull-up to vision of internal pull-up to vision of the pull                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | PREQ3          | N6   | Digital | 1                  | Peripheral 3 power request input           | internal PU/PD) or<br>tied to common<br>ground or VIO<br>(depending on<br>selected | PU/*PD<br>170–950 kΩ |

| PWRON L5 Digital I External on-button switch-on event (primary input 55–370)  REGEN1 K7 Digital O External regulator enable 1 Floating —  REGEN2 J5 Digital O External regulator enable 2 Floating —  REGEN2 RFWRON R5 Digital O External regulator enable 2 Floating —  RPWRON R5 Digital O External regulator enable 2 Floating (internal pull-up to VBAT)  SYSEN M6 Digital O External system wakeup)  SYSEN M6 Digital O External system enable Floating (internal pull-up to VBAT)  SYSEN M6 Digital O External system enable Floating internal pull-up to VBAT)  SYSEN M6 Digital I O External system enable Floating —  SRIZC_SCL M13 Digital I/O SmartReflex in PC serial clock (iPC voltage level is set by an external pullup.)  SRIZC_SCL M13 Digital I/O SmartReflex in PC serial clock (iPC voltage level is set by an external pullup.)  SRIZC_SDA N13 Analog I/O SmartReflex in PC serial clock (iPC voltage set by an external pullup.)  SMAC STATE STAT                                                                                        | PWM1           | M11  | Digital | 0                  |                                            | Floating                                                                           | _                    |

| REGEN1 K7 Digital 0 External regulator enable 1 Floating — REGEN2 J5 Digital 0 External regulator enable 2 Floating — RPWRON K5 Digital 0 External regulator enable 2 Floating — RPWRON K5 Digital 1 External remote switch-on event (secondary input folaunch system wakeup)  SYSEN M6 Digital 1 Secure mode input. Allow IPC access to secure registers.  RRECURE N2 Digital I/O Secure mode input. Allow IPC access to secure registers.  RRIZC_SCL M13 Digital I/O Secure mode input. Allow IPC access to secure registers.  RRIZC_SCL M13 Digital I/O SmartReflex M1/C serial clock (IPC voltage level is set by an external pullup.)  RRIZC_SDA N13 Analog I/O SmartReflex M1/C serial data (IPC voltage set by an external pullup.)  RRIZC_SDA N13 Digital I/O SmartReflex M1/C serial data (IPC voltage set by an external pullup.)  RRIZC_SDA N14 Digital I/O USB connector identification signal Ploating (Internal pullup to VUSB)  RMMC N11 Digital I/O USB connector identification signal Ploating (Internal pullup to VUSB)  RMMC N11 Digital I/O USB connector identification and extraction detection to descrivate the VMMC LDO  RMMC N11 Digital I/O USB connector identification and extraction detection to organized to VIO or pullidown to VIO or pullidown to Organized (Internal pullup to VUSB)  RMMC N12 Power I/O SiM card insertion and extraction detection to VIO or pullidown to Organized (Internal pullup to VUSB)  RMMC N12 Power I/O Output voltage for VANA regulator N1A —  VANA N1A N1A Power I/O Output voltage for VANA regulator Ploating (Internal pullup to VUSB)  VANA N1A N1A Power I/O Output voltage for VANA regulator Ploating —  VAUX1 N1A N1A Power I/O Output voltage for VANA regulator Ploating —  VAUX1 N1A N1A Power I/O Output voltage for VANA regulator Ploating —  VAUX1 N1A N1A Power I/O Output voltage for VANA regulator Ploating —  VAUX1 N1A N1A Power I/O Output voltage for VANA regulator Ploating —  VAUX1 N1A N1A Power I/O Output voltage for VANA regulator Ploating —  VAUX1 N1A N1A Power I/O Output voltage for VANA regulator N1A N1A Ploating —                                                                                        | PWM2           | M12  | Digital | 0                  | Pulse width modulation 2                   | Floating                                                                           | _                    |

| REGEN2 J5 Digital O External regulator enable 2 Floating Power O Output voltage for VANA regulator Power O Output voltage for VANA regulator Power O Output voltage for VANA regulator Power O Power O Output voltage for VANA regulator Power O Power O Output voltage for VANA regulator Power O Power O Output voltage for VAUX2 regulator Pleating O Power O Output voltage for VAUX2 regulator Pleating O Power O Output voltage for VAUX2 regulator Pleating O Power O Output voltage for VAUX2 regulator Pleating O Power O Output voltage for VAUX2 regulator Pleating O Power O Output voltage for VAUX2 regulator Pleating O Power O Output voltage for VAUX2 regulator Pleating O Power O Output voltage for VAUX2 regulator Pleating O Power O Output voltage for VAUX3 regulator Pleating O Power O Output voltage for VAUX3 regulator Pleating O Power O Output voltage for VAUX3 regulator Pleating O Power O Output voltage for VAUX3 regulator Pleating O Power O Output voltage for VAUX3 regulator Pleating O Power O Output voltage for VAUX3 regulator Pleating O Power O Output voltage for VAUX4 regulator Pleating O Power O Output voltage for VAUX4 regulator Pleating O Power O Output voltage for VAUX5 regulator Pleating O Power O Output voltage for VAUX5 regulator Pleating O Power O Output voltage for VAUX5 regulator Pleating O Power O Output voltage for VAUX6 regulator Pleating O Power O Output voltage for VAUX6 regulator Pleating O Power O Output voltage for VAUX6 regulator Pleating O Power O Output voltage for VAUX6 regulator Pleating O Power O Output voltage for VAUX6 regulator Pleating O Power O Output voltage for VAUX6 regulator Pleating O Power O Output voltage for VAUX6 regulator Pleating O Power O Output voltage for VAUX6 regulator Pleating O Power O Output voltage for VAUX6 regulator Pleating O Power O Output voltage for VAUX6 regulator Pleating O Power O Output voltage for VAUX6 regulator Pleating O Power O Output voltage for VAUX6 regulator Pleating O Power O Output voltage for VAUX6 regulator Pleating O Power O Output voltage for                                                                                         | PWRON          | L5   | Digital | I                  |                                            | N/A                                                                                | *PU<br>55–370 kΩ     |

| RPWRON K5 Digital I External remote switch-on event (secondary input infernal pullup to 55-370)  SYSEN M6 Digital O External system enable Floating (lixed infernal pullup to 155-370)  SYSEN M6 Digital I Secure mode input. Allow I <sup>2</sup> C access to secure Floating Floating Floating Floating III Secure mode input. Allow I <sup>2</sup> C access to secure Ground or floating Plugsters.  SRI2C_SCL M13 Digital I/O SmartReflex I <sup>2</sup> C serial clock (I <sup>2</sup> C voltage level is set by an external pullup.)  SRI2C_SDA N13 Analog I/O SmartReflex I <sup>2</sup> C serial data (I <sup>2</sup> C voltage set by an external pullup.)  BRI2C_SDA N13 Analog I/O SmartReflex I <sup>2</sup> C serial data (I <sup>2</sup> C voltage set by an external pullup.)  DETECTION  ID E12 Digital I/O USB connector identification signal Floating (Internal pullup to VIO or pullown to Plugoround III Digital II MMC card insertion and extraction detection to VIO or pullown to Plugoround III Digital II SIM card insertion and extraction detection to VIO or pullown to Plugoround III Digital II SIM card insertion and extraction detection to VIO or pullown to Plugoround III Digital II SIM card insertion and extraction detection to VIO or pullown to Plugoround III Digital II SIM card insertion and extraction detection to VIO or pullown to Plugoround III Digital II SIM card insertion and extraction detection to VIO or pullown to Plugoround III Digital II SIM card insertion and extraction detection to VIO or pullown to Plugoround III Digital III Di | REGEN1         | K7   | Digital | 0                  | External regulator enable 1                | Floating                                                                           | _                    |

| RPWRON K5 Digital I blaunch system wakeup) internal pull-up to VBAT   55–370   55–370   55–370   55–370   55–370   55–370   55–370   55–370   55–370   55–370   55–370   55–370   55–370   55–370   55–370   55–370   55–370   55–370   55–370   55–370   55–370   55–370   55–370   55–370   55–370   55–370   55–370   55–370   55–370   55–370   55–370   55–370   55–370   55–370   55–370   55–370   55–370   55–370   55–370   55–370   55–370   55–370   55–370   55–370   55–370   55–370   55–370   55–370   55–370   55–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–370   50–3                                                                                         | REGEN2         | J5   | Digital | 0                  | External regulator enable 2                | Floating                                                                           | _                    |

| MSECURE  N2 Digital  I Secure mode input. Allow I²C access to secure registers.  RIZC_SCL  M13 Digital  I/O SmartReflex™ I²C serial clock (I²C voltage level is set by an external pullup.)  RRIZC_SDA  N13 Analog  I/O SmartReflex™ I²C serial clock (I²C voltage level is set by an external pullup.)  RRIZC_SDA  N13 Analog  I/O SmartReflex I²C serial clock (I²C voltage set by an vicio set by an external pullup.)  RRIZC_SDA  N13 Analog  I/O SmartReflex I²C serial clock (I²C voltage set by an vicio set by an external pullup.)  RRIZC_SDA  N13 Analog  I/O SmartReflex I²C serial clock (I²C voltage set by an vicio set by an external pullup.)  PUPLO Color Detection  ID E12 Digital  I/O USB connector identification signal  Floating (Internal pullup to VUSB) pull-up to VUSB)  Internal pullup to VUSB)  PUP-IYO (Yo or pulldown to ground)  PUP-IYO (Yo or pulldown                                                                                         | RPWRON         | K5   | Digital | 1                  |                                            | internal pull-up to                                                                | *PU<br>55–370 kΩ     |

| SRI2C_SCL M13 Digital I/O SmartReflex PC serial clock (I²C voltage level is set by an external pullup.)  RRI2C_SDA N13 Analog I/O SmartReflex PC serial data (I²C voltage set by an external pullup.)  DETECTION  ID E12 Digital I/O USB connector identification signal Floating (Internal pullup to deactivate the VMMC LDO pullup.)  MMC N11 Digital I USB connector identification signal Floating (Internal pullup to vIO or pulldown to deactivate the VMMC LDO provided to vIO or pulldown to ground pround pround provided to vIO or pulldown to ground pround pround pround pround provided to vIO or pulldown to ground provided to vIO or pulldown to ground pround proun                                                                                        | SYSEN          | M6   | Digital | 0                  | External system enable                     | Floating                                                                           | _                    |

| SRI2C_SCL M13 Digital I/O SmartRellex III PC senal clock (IFC Voltage level vivo VIO VIO RD VIO VIO RD VIO VIO VIO RD VIO VIO VIO VIO VIO VIO RD VIO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | MSECURE        | N2   | Digital | ı                  |                                            | Ground or floating                                                                 | *PD<br>170–950 kΩ    |

| SRI2C_SDA   N13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | SRI2C_SCL      | M13  | Digital | I/O                |                                            |                                                                                    | 0.46-1.76            |

| DETECTION  ID E12 Digital I/O USB connector identification signal Floating (Internal pull-up to VUSB)  MMC N11 Digital I MMC card insertion and extraction detection to deactivate the VMMC LDO  SIM N12 Power I SIM card insertion and extraction detection to deactivate the VMMC LDO  SIM N12 Power I SIM card insertion and extraction detection to deactivate the VUSIM LDO  SIM N12 Power I SIM card insertion and extraction detection to ground violo or pulldown to violo vi                                                                                        | SRI2C_SDA      | N13  | Analog  | I/O                |                                            |                                                                                    | 0.46-1.76            |

| MMC N11 Digital I MMC card insertion and extraction detection to deactivate the VMMC LDO Internal pullup to VIO or pulldown to ground ground ground to VIO or pulldown to VIO or vIO or vIO or pulldown to VIO or                                                                                        | DETECTION      |      |         |                    | I                                          |                                                                                    |                      |

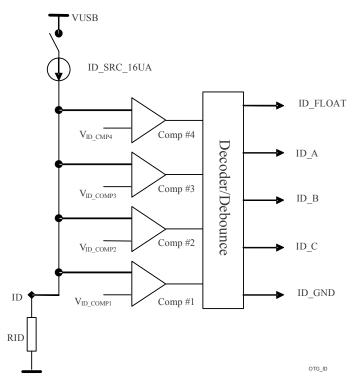

| MMC N11 Digital I deactivate the VMMC LDO VIO or pulldown to ground varieties and extraction detection to deactivate the VMMC LDO viologround viologro                                                                                        | ID             | E12  | Digital | I/O                | USB connector identification signal        |                                                                                    | -                    |

| SIM SIM SIM SIM SIM SIM Card Insertion and extraction detection to ground beactivate the VUSIM LDO  LDO REGULATORS  VANA B10 Power O Output voltage for VANA regulator N/A Supply of output stage of VANA regulator VBAT Supply of output stage of VAUX1 regulator VBAT Supply of output stage of VAUX1 regulator VBAT Supply of output stage of VAUX2 regulator VBAT Supply of output stage of VAUX2 regulator VBAT Supply of output stage of VAUX2 regulator VBAT Supply of output stage of VAUX3 regulator VBAT Supply of output stage of VDAC regulator VBAT Supply of output stage of VDAC regulator VBAT Supply OUTPUT Supply Su                                                                                        | MMC            | N11  | Digital | ı                  |                                            | VIO or pulldown to                                                                 | PU/*PD<br>70–190 kΩ  |

| VANA B10 Power O Output voltage for VANA regulator N/A — VANA_IN D10 Power I Supply of output stage of VANA regulator VBAT — VAUX1 T8 Power O Output voltage for VAUX1 regulator Floating — VAUX1_IN N7 Power I Supply of output stage of VAUX1 regulator VBAT — VAUX2 T9 Power O Output voltage for VAUX2 regulator Floating — VAUX2_IN N10 Power I Supply of output stage of VAUX2 regulator VBAT — VAUX3 R9 Power O Output voltage for VAUX3 regulator VBAT — VAUX3_IN R8 Power I Supply of output stage of VAUX3 regulator (vibrator driver output) VAUX3_IN R8 Power I Supply of output stage of VAUX3 regulator VBAT — VCXIO F15 Power O Output voltage for VCXIO regulator Floating — VCXIO_IN F13 Power I Supply of output stage of VCXIO regulator VBAT — VDAC G15 Power O Output voltage for VDAC regulator Floating — VDAC_IN H13 Power I Supply of output stage of VDAC regulator VBAT — VMMC J13 Power O Output voltage for VMMC regulator Floating — VMMC_IN J12 Power I Supply 1 of output stage of VMMC regulator VBAT — VPP_IN J4 Power I Supply of output stage of VPP regulator Floating — VPP_IN J4 Power I Supply of output stage of VPP regulator Floating — VPP_IN J4 Power I Supply of output stage of VPP regulator VBAT —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | SIM            | N12  | Power   | -                  |                                            | VIO or pulldown to                                                                 | PU/*PD<br>70–190 kΩ  |

| VANA_IN       D10       Power       I       Supply of output stage of VANA regulator       VBAT       —         VAUX1       T8       Power       O       Output voltage for VAUX1 regulator       Floating       —         VAUX2_IN       N7       Power       O       Output voltage for VAUX2 regulator       VBAT       —         VAUX2_IN       N10       Power       I       Supply of output stage of VAUX2 regulator       VBAT       —         VAUX3       R9       Power       O       Output voltage for VAUX3 regulator (vibrator driver output)       Floating       —         VAUX3_IN       R8       Power       I       Supply of output stage of VAUX3 regulator       VBAT       —         VCXIO       F15       Power       O       Output voltage for VCXIO regulator       Floating       —         VCXIO_IN       F13       Power       I       Supply of output stage of VCXIO regulator       VBAT       —         VDAC_IN       H13       Power       O       Output voltage for VDAC regulator       VBAT       —         VMMC_IN       J12       Power       I       Supply of output stage of VMMC regulator       VBAT       —         VPP_IN       K4       Power       I       Supply of outp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | LDO REGULATORS |      |         | 1                  |                                            |                                                                                    | II.                  |

| VAUX1       T8       Power       O       Output voltage for VAUX1 regulator       Floating       —         VAUX1_IN       N7       Power       I       Supply of output stage of VAUX1 regulator       VBAT       —         VAUX2       T9       Power       O       Output voltage for VAUX2 regulator       Floating       —         VAUX2_IN       N10       Power       I       Supply of output stage of VAUX2 regulator       VBAT       —         VAUX3       R9       Power       O       Output voltage for VAUX3 regulator (vibrator driver output)       Floating       —         VAUX3_IN       R8       Power       I       Supply of output stage of VAUX3 regulator       VBAT       —         VCXIO       F15       Power       O       Output voltage for VCXIO regulator       Floating       —         VCXIO_IN       F13       Power       I       Supply of output stage of VCXIO regulator       VBAT       —         VDAC_IN       H13       Power       O       Output voltage for VDAC regulator       VBAT       —         VMMC_IN       J12       Power       I       Supply of output stage of VMMC regulator       VBAT       —         VPP_IN       K4       Power       I       Supply of ou                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | VANA           | B10  | Power   | 0                  | Output voltage for VANA regulator          | N/A                                                                                | _                    |

| VAUX1_INN7PowerISupply of output stage of VAUX1 regulatorVBAT—VAUX2T9PowerOOutput voltage for VAUX2 regulatorFloating—VAUX2_INN10PowerISupply of output stage of VAUX2 regulatorVBAT—VAUX3R9PowerOOutput voltage for VAUX3 regulator (vibrator driver output)Floating—VAUX3_INR8PowerISupply of output stage of VAUX3 regulatorVBAT—VCXIOF15PowerOOutput voltage for VCXIO regulatorFloating—VCXIO_INF13PowerISupply of output stage of VCXIO regulatorVBAT—VDACG15PowerOOutput voltage for VDAC regulatorFloating—VDAC_INH13PowerISupply of output stage of VDAC regulatorVBAT—VMMCJ13PowerOOutput voltage for VMMC regulatorFloating—VMMC_INJ12PowerISupply 1 of output stage of VMMC regulatorVBAT—VPPK4PowerOOutput voltage for VPP regulatorFloating—VPP_INJ4PowerISupply of output stage of VPP regulatorVBAT—                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | VANA_IN        | D10  | Power   | ı                  | Supply of output stage of VANA regulator   | VBAT                                                                               | _                    |

| VAUX2T9PowerOOutput voltage for VAUX2 regulatorFloating—VAUX2_INN10PowerISupply of output stage of VAUX2 regulatorVBAT—VAUX3R9PowerOOutput voltage for VAUX3 regulator (vibrator driver output)Floating—VAUX3_INR8PowerISupply of output stage of VAUX3 regulatorVBAT—VCXIOF15PowerOOutput voltage for VCXIO regulatorFloating—VCXIO_INF13PowerISupply of output stage of VCXIO regulatorVBAT—VDACG15PowerOOutput voltage for VDAC regulatorFloating—VDAC_INH13PowerISupply of output stage of VDAC regulatorVBAT—VMMCJ13PowerOOutput voltage for VMMC regulatorFloating—VMMC_INJ12PowerISupply 1 of output stage of VMMC regulatorVBAT—VPPK4PowerOOutput voltage for VPP regulatorFloating—VPP_INJ4PowerISupply of output stage of VPP regulatorVBAT—                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | VAUX1          | T8   | Power   | 0                  | Output voltage for VAUX1 regulator         | Floating                                                                           | _                    |

| VAUX2_IN       N10       Power       I       Supply of output stage of VAUX2 regulator       VBAT       —         VAUX3       R9       Power       O       Output voltage for VAUX3 regulator (vibrator driver output)       Floating       —         VAUX3_IN       R8       Power       I       Supply of output stage of VAUX3 regulator       VBAT       —         VCXIO       F15       Power       O       Output voltage for VCXIO regulator       Floating       —         VCXIO_IN       F13       Power       I       Supply of output stage of VCXIO regulator       VBAT       —         VDAC       G15       Power       O       Output voltage for VDAC regulator       Floating       —         VDAC_IN       H13       Power       I       Supply of output stage of VDAC regulator       VBAT       —         VMMC       J13       Power       O       Output voltage for VMMC regulator       Floating       —         VMMC_IN       J12       Power       I       Supply 1 of output stage of VPP regulator       VBAT       —         VPP_IN       J4       Power       I       Supply of output stage of VPP regulator       VBAT       —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | VAUX1_IN       | N7   | Power   | ı                  | Supply of output stage of VAUX1 regulator  | VBAT                                                                               | _                    |

| VAUX3       R9       Power O driver output)       O dutput voltage for VAUX3 regulator (vibrator driver output)       Floating       —         VAUX3_IN       R8       Power I Supply of output stage of VAUX3 regulator       VBAT       —         VCXIO       F15       Power O Output voltage for VCXIO regulator       Floating       —         VCXIO_IN       F13       Power I Supply of output stage of VCXIO regulator       VBAT       —         VDAC       G15       Power O Output voltage for VDAC regulator       Floating       —         VDAC_IN       H13       Power I Supply of output stage of VDAC regulator       VBAT       —         VMMC       J13       Power O Output voltage for VMMC regulator       Floating       —         VMMC_IN       J12       Power I Supply 1 of output stage of VMMC regulator       VBAT       —         VPP       K4       Power O Output voltage for VPP regulator       Floating       —         VPP_IN       J4       Power I Supply of output stage of VPP regulator       VBAT       —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | VAUX2          | Т9   | Power   | 0                  | Output voltage for VAUX2 regulator         | Floating                                                                           | _                    |

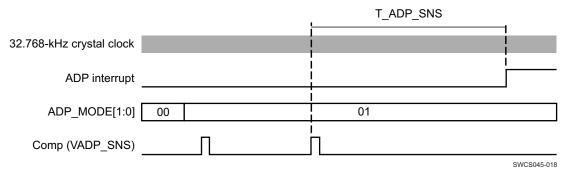

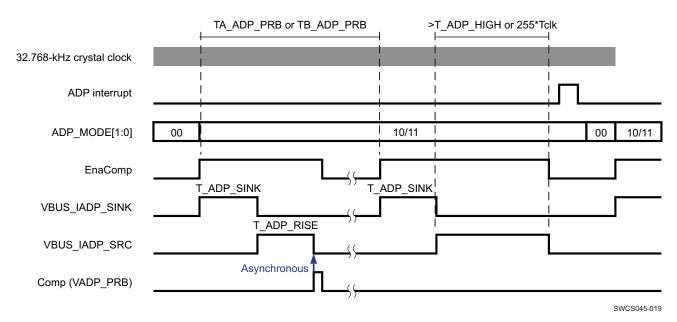

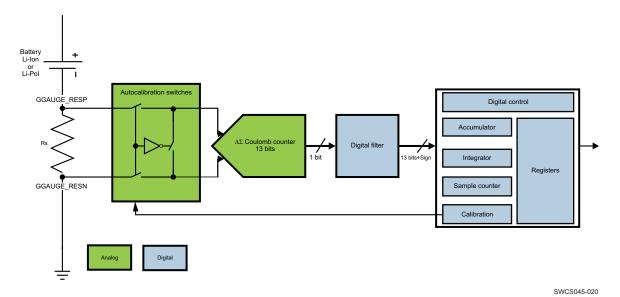

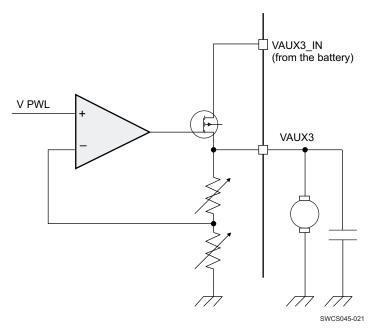

| VAUX3_IN  R8  Power  I Supply of output stage of VAUX3 regulator  VBAT  - VCXIO  F15  Power  O Output voltage for VCXIO regulator  VBAT  - VCXIO_IN  F13  Power  I Supply of output stage of VCXIO regulator  VBAT  - VDAC  G15  Power  O Output voltage for VDAC regulator  VBAT  - VDAC_IN  H13  Power  I Supply of output stage of VDAC regulator  VBAT  - VMMC  J13  Power  O Output voltage for VDAC regulator  VBAT  - VMMC  J13  Power  O Output voltage for VMMC regulator  Floating  - VMMC_IN  J12  Power  I Supply 1 of output stage of VMMC regulator  VBAT  - VPP  K4  Power  O Output voltage for VPP regulator  Floating  - VPP_IN  J4  Power  I Supply of output stage of VPP regulator  VBAT  -  VPP regulator  VBAT  -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | VAUX2_IN       | N10  | Power   | I                  | Supply of output stage of VAUX2 regulator  | VBAT                                                                               | _                    |