# Errata IWRL6843/44 Device Silicon Errata Silicon Revisions ES1.0

## **Table of Contents**

| 1 Introduction                                         | 2 |

|--------------------------------------------------------|---|

| 2 Device Nomenclature                                  | 2 |

| 3 Device Markings                                      |   |

| 4 Advisory to Silicon Variant / Revision Map           |   |

| 5 Known Design Exceptions to Functional Specifications |   |

| 6 Trademarks                                           |   |

| Revision History                                       | 9 |

|                                                        |   |

# **1** Introduction

This document describes the known exceptions to the functional and performance specifications to TI CMOS Radar Devices (IWRL684x )

### **2 Device Nomenclature**

To designate the stages in the product development cycle, TI assigns prefixes to the part numbers of Radar / mmWave sensor devices. Each of the Radar devices has one of the two prefixes: XIx or IWRLx (for example: **IWRL6844DBGANC**). These prefixes represent evolutionary stages of product development from engineering prototypes (XAL/XIL) through fully qualified production devices (IWRL).

Device development evolutionary flow:

- XIL Experimental device that is not necessarily representative of the final device's electrical specifications and may not use production assembly flow.

- IWRL Production version of the silicon die that is fully qualified.

XIL devices are shipped with the following disclaimer:

"Developmental product is intended for internal evaluation purposes."

Texas Instruments recommends that these devices not to be used in any production system as their expected end –use failure rate is still undefined.

## **3 Device Markings**

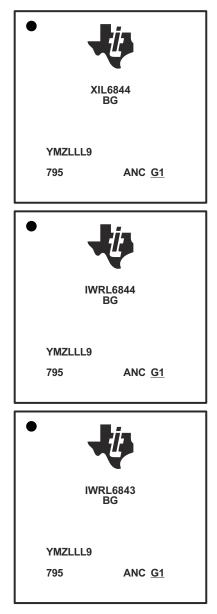

Figure 3-1 shows an example of the IWRL684x Radar Device's package symbolization.

This identifying number contains the following information:

- Line 1: TI Logo

- Line 1: Device Number

- Line 2: Safety Level and Security Grade

- Q = Non-Functional Safety

- B = ASIL-B capable

- G = General

- S = Secure

- Line 3: Lot Trace Code

- YM = Year/Month Code

- Z- Assembly Site Code

- LLL = Assembly Lot

- 9= Primary Site Code

- Line 4:

- 795 = Device Identifier

- ANC = Package Identifier

- G1 = "Green" Package Build (must be underlined)

# 4 Advisory to Silicon Variant / Revision Map

| Advisory<br>Number       | Advisory Title                                                                        | IWRL684x |  |  |  |

|--------------------------|---------------------------------------------------------------------------------------|----------|--|--|--|

|                          | Advisory Title                                                                        |          |  |  |  |

| Analog / Millimeter Wave |                                                                                       |          |  |  |  |

| ANA #51                  | Continuous Wave Streaming CZ mode: Sudden jump in RX output codes every 20.97152 msec | x        |  |  |  |

|                          | Digital Subsystem                                                                     |          |  |  |  |

| DIG #17                  | HWA CFAR CA engine is not working if dynamic clock gating is enabled                  | x        |  |  |  |

#### Table 4-1. Advisory to Silicon Variant / Revision Map

# **5 Known Design Exceptions to Functional Specifications**

#### Continuous Wave Streaming CZ mode: Sudden jump in RX output codes every ANA #51 20.97152 msec **Revision(s)** Affected IWRL684x ES1.0 **Details** On Continuous Wave Streaming CZ mode, the Rx data shows a sudden jump in output codes every 20.97152 milliseconds. This is not an issue in the Radar Functional mode when chirps are used. However, this issue will be seen when testing Rx chain in lab using continuous stream mode. Workaround In order to use Continuous stream (CW) mode for testing, it is recommended to start data capturing from the first sample itself to make sure the glitch occurs at deterministic samples. Please follow the below sequence to achieve this: Configure the LVDS (Low Voltage Differential Signaling) ٠ Arm the DCA1000 (Data capture card) Enable the continuous stream mode. The glitch will not be seen with this sequence. For example, if the user analyzes first

20ms of data or between 21 and 41ms.

SWRZ156 – DECEMBER 2024 Submit Document Feedback

| DIG #17              | HWA CFAR CA engine is not working if dynamic clock gating is enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Revision(s) Affected | d IWRL684x ES1.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| Details              | Dynamic clock gating feature is added in IP for power savings. Idea is to enable clock to the FFT/CFAR-CA/CFAR-OS engine only when the respective engine is needed to be active based on the mode of operation. However, when CFAR CA engine is enabled and dynamic clock gating is set, the clock to one of the logic in the engine gets gated. Due to this, the data transfer to the logic internal to the CFAR-CA engine gets hampered. Hence, we do not get any valid data in the output of the CFAR CA engine. |  |  |  |

| Workaround           | Disable the dynamic clock gating feature when CFAR CA mode of operation is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

#### 6 Trademarks

All trademarks are the property of their respective owners.

# **Revision History**

| DATE          | REVISION | NOTES |

|---------------|----------|-------|

| December 2024 | *        | 1.0   |

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2024, Texas Instruments Incorporated