# Clocking the RF ADC: Should you worry about jitter or phase noise?

## By Thomas Neu

System Engineer, High-Speed Products

#### Introduction

A critical specification of a receiver is the blocker specification. It determines the weakest signal power level that can be successfully detected in the presence of an in-band interferer/blocker. To determine the receiver performance during a blocking event, system designers have to analyze various noise sources of the receiver, including the clock noise contribution of the data converter .

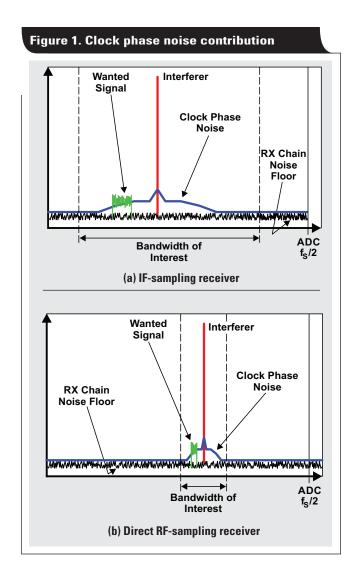

In a traditional heterodyne receiver, the noise contribution of the data-converter clock is typically derived in the time domain using integrated jitter numbers. In a direct RF-sampling architecture (Figure 1), the actual signal bandwidth may be much smaller than the Nyquist zone of the analog-to-digital converter (ADC). Rather than integrating the phase-noise contribution of the clock across the entire Nyquist zone, it may make more sense to work directly with frequency offset-dependent phase noise in the frequency domain. Even though the time-domain approach is simpler, it may result in an unrealistic and impractical clock-noise requirement.

Since recent introduction of high-performance, direct RF-sampling converters, such as the ADC12J4000 and ADC32RF45, customers frequently ask about external phase-noise requirements for the ADC sampling clock. The answer depends on the customer's requirements for receiver performance, as well as several additional factors that impact the clock noise of data converters. These include ADC aperture jitter, clock amplitude or slew rate, signal input frequency and input-signal amplitude, to name a few. This article shows how to derive the noise contribution in the frequency domain and compares it to a traditional calculation approach of time-domain jitter.

# ADC noise analysis in the frequency domain

The data-converter noise contribution in the frequency domain can be analyzed using the following five steps. Simplified diagrams normalized to the input signal frequency are added for better illustration.

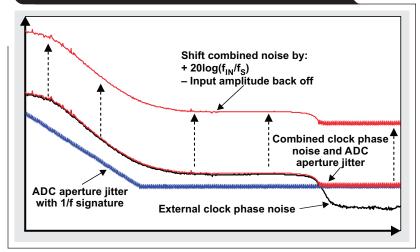

1. Obtain the external-clock phase noise ( $PN_E$ ) and ADC aperture jitter ( $PN_A$ ) in the frequency domain in dBc/Hz. The frequency bin sizes and steps need to be identical. The clock phase-noise data is typically given in a log-type format. If the ADC aperture jitter is not assumed flat across frequency, some data interpolation may be necessary to match the phase-noise data format. As discussed earlier, the ADC aperture jitter is clock-amplitude dependent, which needs to be considered as well.

2.  $PN_C$  is the combined external-clock phase noise and the ADC aperture jitter that is calculated with Equation 1 and shown in Figure 2. The top red curve shows the shift that adjusts it for signal-amplitude back-off as calculated in step 3.

$$PN_{C} = 20log \left[ \sqrt{\left(10^{\frac{PN_{E}}{20}}\right)^{2} + \left(10^{\frac{PN_{A}}{20}}\right)^{2}} \right] dBc/Hz \qquad (1)$$

3. Equation 2 accounts for the signal input-frequency shifting of the combined clock noise.

$$PN_{f_{IN}} = PN_{C} + 20log\left(\frac{f_{IN}}{f_{S}}\right)$$

(2)

where  $f_{\rm IN}$  is the signal input frequency and  $f_{\rm S}$  is the ADC sampling rate. As the signal input frequency increases, the signal-to-noise (SNR) degradation due to clock noise also increases.

- 4. It is also important to account for the amplitude of the input signal. Reducing the signal amplitude in respect to the ADC full-scale directly reduces the clock noise contribution. For example, a 3-dB back-off ( $A_{IN} = -3 \ dBFS$ ) reduces the noise power in each frequency bin by 3 dB.

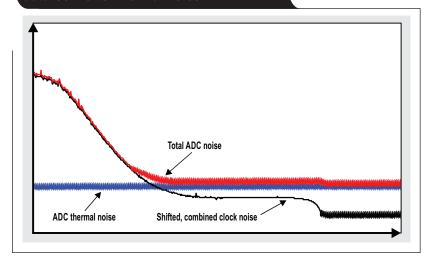

- 5. The final step is to combine the shifted clock noise with the inherent thermal noise of the data converter. This results in the expected total noise contribution from the ADC for specific frequency offsets from the input signal as illustrated in Figure 3.

The final ADC noise in Figure 3 explains several use cases. For example, for high input frequencies in undersampling scenarios (where  $\rm f_S=3$  GSPS,  $\rm f_{IN}=1.8$  GHz), the clock noise contribution is increased. This pushes the close-in phase noise from the clock above the ADC's thermal noise floor.

Figure 2. Data converter noise after combining ADC aperture jitter with the external clock phase noise

Figure 3. Total ADC noise after adding the data-converter thermal noise

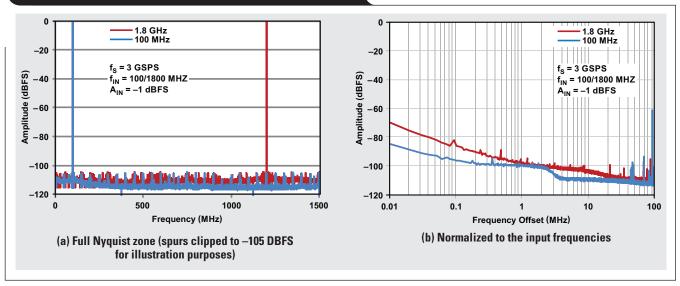

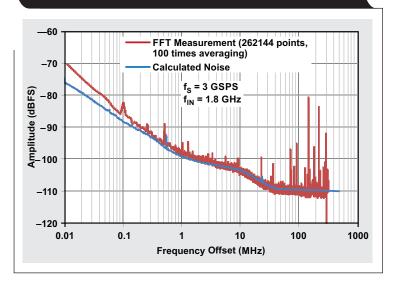

Figure 4. Fast Fourier transform (FFT) noise comparison

As a result, the ADC experiences SNR degradation because of clock jitter, which is clearly visible in Figure 4. In Figure 4a, the red curve with a 1.8-GHz input signal shows larger close-in noise, as well as a distant noise floor compared to the 100-MHz curve. Both are due to the ADC aperture jitter increasing in magnitude because of higher input frequency.

Figure 4b shows the phase-noise signature (frequency corner  $\approx 3$  MHz) of the input signal itself in the blue curve. While it does not experience any amplitude shift, it disappears in the clock noise in the 1.8-GHz scenario.

#### **Calculation versus measurement**

How well can the data-converter noise be predicted with this frequency-domain analysis? The noise calculation was performed for the previous measurement using the aperture-jitter information of the ADC32RF45, along with the phase-noise information of both the clock and input signal generators. The results in Figure 5 show a very close match where other degradations, such as power-supply noise and temperature effects, were not included. In this way, the system designer can estimate the ADC clock-noise contribution at a specific frequency offset.

Figure 5. Noise comparison between FFT measurement and calculated data converter noise

# Time domain versus frequency domain?

System engineers are used to operating in the time domain with the simple jitter equation of  $SNR_{Jitter} = 20log(2\pi f_{IN} \times t_{Jitter}). \ Table \ 1 \ compares \ the frequency-domain approach illustrated in this article against the traditional time-domain method.$

Table 1. Analysis comparison of clock-noise contribution in ADCs

| Step | Time-domain analysis                                                                                                                                                                                                                                                                    | Frequency-domain analysis                                                                                                                                                                                                                                                                 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | Obtain jitter by integrating the external clock phase noise over desired bandwidth: $t_E = \frac{\sqrt{2JPN_E}}{2\pi f_S} \tag{3}$ where PN <sub>E</sub> = External clock phase noise, and $f_S$ = ADC sampling rate                                                                    | Obtain external clock-phase noise in dBc/Hz. Convert ADC aperture jitter into phase noise in dBc/Hz with integration bandwidth of double the ADC sampling rate. Can be assumed flat across Nyquist zone unless specific information about 1/f behavior is available, as on the ADC32RF45. |

| 2    | Combine external with ADC internal aperture jitter: $t_J = \sqrt{t_E^2 + t_A^2} \qquad (4)$ Assuming the ADC aperture is in fact also noise integrated over a bandwidth $t_J = \frac{1}{2\pi f_S} \times \sqrt{\left(\sqrt{2J}PN_E\right)^2 + \left(\sqrt{2J}PN_A\right)^2} \qquad (5)$ | Combine external clock phase noise with ADC internal aperture phase noise. This is calculated per frequency bin. $PN_{C} = 20 log \sqrt{\left(10^{\frac{PN_{E}}{20}}\right)^{2} + \left(10^{\frac{PN_{A}}{20}}\right)^{2}} $ (9)                                                          |

| 3    | Calculate SNR degradation due to jitter and input frequency: $ PN_{Thermal} = SNR_{Thermal} + 10log(f_S/2)                                    $                                                                                                                                         | Shift combined phase noise by input frequency: $PN_{f_{ N}} = PN_{C} + 20log\left(\frac{f_{ N}}{f_{S}}\right) \tag{10}$                                                                                                                                                                   |

| 4    | Adjust for signal input amplitude: Subtract ADC back-off (in dB) from the SNR <sub>Jitter</sub> value.                                                                                                                                                                                  | Adjust for signal input amplitude: Subtract input signal back-off from the phase-noise amplitude for each individual frequency bin.                                                                                                                                                       |

| 5    | Combine result from Step 4 with ADC thermal noise: $SNR = 20 \log \left[ \sqrt{ \left( \frac{SNR_{Jitter}}{20} \right)^2 + \left( \frac{SNR_{Thermal}}{20} \right)^2} \right] $ (8)                                                                                                     | Combine result from Step 4 with ADC thermal noise: $Noise_{bin} = 20 log \sqrt{\left(10^{\frac{PN_{f_{i_N}}}{20}}\right)^2 + \left(10^{\frac{PN_{Thermal}}{20}}\right)^2} \tag{11}$ where $PN_{Thermal} = SNR_{Thermal} + 10 log (f_S/2)$                                                 |

| 6    | (Intentionally left blank)                                                                                                                                                                                                                                                              | Compare with actual measured FFT data. Scale noise per bin with FFT bin size:  Noise <sub>FFT</sub> = Noise <sub>bin</sub> + 10log(binsize) (12)                                                                                                                                          |

#### Conclusion

Evaluating the noise contribution from an RF-sampling data converter gives the system designer a very powerful tool when analyzing system-interferer specifications. The side-by-side comparison shows that both time- and frequency-domain methods are using the same information. However, the frequency-domain analysis preserves crucial application-specific information for frequency offset and may be much better suited for working with modern, high-performance RF-sampling converters such as the ADC32RF45.

#### **Related Web sites**

Product information: ADC12J4000 ADC32RF45

# TI Worldwide Technical Support

# **TI Support**

Thank you for your business. Find the answer to your support need or get in touch with our support center at

www.ti.com/support

China: http://www.ti.com.cn/guidedsupport/cn/docs/supporthome.tsp

Japan: http://www.tij.co.jp/guidedsupport/jp/docs/supporthome.tsp

## **Technical support forums**

Search through millions of technical questions and answers at TI's E2E™ Community (engineer-to-engineer) at

e2e.ti.com

China: http://www.deyisupport.com/ Japan: http://e2e.ti.com/group/jp/

# **TI Training**

From technology fundamentals to advanced implementation, we offer on-demand and live training to help bring your next-generation designs to life. Get started now at

training.ti.com

China: http://www.ti.com.cn/general/cn/docs/gencontent.tsp?contentId=71968

Japan: https://training.ti.com/jp

Important Notice: The products and services of Texas Instruments Incorporated and its subsidiaries described herein are sold subject to Tl's standard terms and conditions of sale. Customers are advised to obtain the most current and complete information about Tl products and services before placing orders. Tl assumes no liability for applications assistance, customer's applications or product designs, software performance, or infringement of patents. The publication of information regarding any other company's products or services does not constitute Tl's approval, warranty or endorsement thereof.

A011617

E2E is a trademark of Texas Instruments. All other trademarks are the property of their respective owners.

SLYT705

#### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications that include TI products, you will thoroughly test such applications and the functionality of such TI products as used in such applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your non-compliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/sampterms.htm">http://www.ti.com/sc/docs/sampterms.htm</a>).

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2017, Texas Instruments Incorporated